Errata 01

Contents

Figures

Tables

Release History

1 Introduction

1.1 Scope

1.2 Purpose

2 Terminology

2.1 Use of Special Terms

2.2 Definitions

2.3 Abbreviations

2.4 Acronyms

3 References

4 D-PHY Overview

4.1 Summary of PHY Functionality

4.2 Mandatory Functionality

5 Architecture

5.1 Lane Modules

5.2 Master and Slave

5.3 High Frequency Clock Generation

5.4 Clock Lane, Data Lanes and the PHY-Protocol Interface

5.5 Selectable Lane Options

5.6 Lane Module Types

5.6.1 Unidirectional Data Lane

5.6.2 Bi-directional Data Lanes

5.6.2.1 Bi-directional Data Lane without High-Speed Reverse Communication

5.6.2.2 Bi-directional Data Lane with High-Speed Reverse Communication

5.6.3 Clock Lane

5.7 Configurations

5.7.1 Unidirectional Configurations

5.7.1.1 PHY Configuration with a Single Data Lane

5.7.1.2 PHY Configuration with Multiple Data Lanes

5.7.1.3 Dual-Simplex (Two Directions with Unidirectional Lanes)

5.7.2 Bi-Directional Half-Duplex Configurations

5.7.2.1 PHY Configurations with a Single Data Lane

5.7.2.2 PHY Configurations with Multiple Data Lanes

5.7.3 Mixed Data Lane Configurations

6 Global Operation

6.1 Transmission Data Structure

6.1.1 Data Units

6.1.2 Bit order, Serialization, and De-Serialization

6.1.3 Encoding and Decoding

6.1.4 Data Buffering

6.2 Lane States and Line Levels

6.3 Operating Modes: Control, High-Speed, and Escape

6.4 High-Speed Data Transmission

6.4.1 Burst Payload Data

6.4.2 Start-of-Transmission

6.4.3 End-of-Transmission

6.4.4 HS Data Transmission Burst

6.5 Bi-directional Data Lane Turnaround

6.6 Escape Mode

6.6.1 Remote Triggers

6.6.2 Low-Power Data Transmission

6.6.3 Ultra-Low Power State

6.6.4 Escape Mode State Machine

6.7 High-Speed Clock Transmission

6.8 Clock Lane Ultra-Low Power State

6.9 Global Operation Timing Parameters

6.10 System Power States

6.11 Initialization

6.12 Calibration

6.13 Alternate Calibration Sequence

6.14 Preamble Sequence

6.15 HS-Idle State

6.16 Sync Patterns

6.17 Global Operation Flow Diagram

6.18 Data Rate Dependent Parameters (informative)

6.18.1 Parameters Containing Only UI Values

6.18.2 Parameters Containing Time and UI values

6.18.3 Parameters Containing Only Time Values

6.18.4 Parameters Containing Only Time Values That Are Not Data Rate Dependent

6.19 Interoperability

7 Fault Detection

7.1 Contention Detection

7.2 Sequence Error Detection

7.2.1 SoT Error

7.2.2 SoT Sync Error

7.2.3 EoT Sync Error

7.2.4 Escape Mode Entry Command Error

7.2.5 LP Transmission Sync Error

7.2.6 False Control Error

7.3 Protocol Watchdog Timers (informative)

7.3.1 HS RX Timeout

7.3.2 HS TX Timeout

7.3.3 Escape Mode Timeout

7.3.4 Escape Mode Silence Timeout

7.3.5 Turnaround Errors

8 Interconnect and Lane Configuration

8.1 Lane Configuration

8.2 Boundary Conditions

8.3 Definitions

8.4 S-parameter Specifications

8.5 Characterization Conditions

8.6 Interconnect Specifications

8.6.1 Differential Characteristics

8.6.1.1 Differential Insertion Loss for Data Rate ≥ 80 Mbps and ≤ 1.5 Gbps

8.6.1.2 Differential Insertion Loss for Data Rate > 1.5 Gbps and ≤ 4.5 Gbps

8.6.1.3 Differential Reflection Loss for Data Rate ≥ 80 Mbps and ≤ 1.5 Gbps

8.6.1.4 Differential Reflection Loss for Data Rate >1.5 Gbps and ≤ 4.5 Gbps

8.6.2 Common-mode Characteristics

8.6.3 Intra-Lane Cross-Coupling

8.6.4 Mode-Conversion Limits

8.6.5 Inter-Lane Cross-Coupling

8.6.6 Inter-Lane Static Skew

8.7 Driver and Receiver Characteristics

8.7.1 Differential Characteristics

8.7.2 Common-Mode Characteristics

8.7.3 Mode-Conversion Limits

9 Electrical Characteristics

9.1 Driver Characteristics

9.1.1 High-Speed Transmitter

9.1.1.1 Differential & Common Mode Swing

9.1.1.2 Differential Voltage Mismatch

9.1.1.3 Static Common Mode Mismatch & Transient Common Mode Voltage

9.1.1.4 Output Resistance

9.1.1.5 Rise/Fall Times

9.1.1.6 Half Swing Mode

9.1.1.7 De-emphasis

9.1.2 Low-Power Transmitter

9.2 Receiver Characteristics

9.2.1 High-Speed Receiver

9.2.2 Low-Power Receiver

9.3 Line Contention Detection

9.4 Input Characteristics

10 High-Speed Data-Clock Timing

10.1 High-Speed Clock Timing

10.2 Forward High-Speed Data Transmission Timing

10.2.1 Data-Clock Timing Specifications

10.2.1.1 Data Rate ≥ 0.08 Gbps and ≤ 1 Gbps

10.2.1.2 Data Rate > 1 Gbps and ≤ 1.5 Gbps

10.2.1.3 Data Rate > 1.5 Gbps and ≤ 4.5 Gbps

10.2.2 Normative Spread Spectrum Clocking (SSC)

10.2.3 Transmitter Eye Diagram Specification

10.2.4 Receiver Eye Diagram Specification

10.3 Reverse High-Speed Data Transmission Timing

10.4 Operating Modes: Data Rate and Channel Support Guidance

11 Regulatory Requirements

12 Built-In HS Test Mode (Informative)

12.1 Introduction

12.2 Entering the HS Test Mode

12.3 HS Test Mode

12.4 Special Case: Multi-Lane Testing

12.5 Exiting from HS Test Mode

Annex A Logical PHY-Protocol Interface Description (informative)

A.1 Signal Description

A.2 High-Speed Transmit from the Master Side

A.3 High-Speed Receive at the Slave Side

A.4 High-Speed Transmit from the Slave Side

A.5 High-Speed Receive at the Master Side

A.6 Low-Power Data Transmission

A.7 Low-Power Data Reception

A.8 Turn-around

A.9 Calibration

A.10 High Speed Receive in HS-Idle State

A.11 Optical Link Support

A.11.1 System Setup

A.11.2 Serializer and De-Serializer Block Diagrams

A.11.3 Timing Constraints

A.11.4 System Constraints

A.11.4.1 Bus Turnaround

A.11.4.2 Equalization (De-emphasis), Deskewing, and Spread Spectrum Clocking

A.11.4.3 TWAIT-OPTICAL

A.12 Higher Data Rate Operation

Annex B Interconnect Design Guidelines (informative)

B.1 Practical Distances

B.2 RF Frequency Bands: Interference

B.3 Transmission Line Design

B.4 Reference Layer

B.5 Printed-Circuit Board

B.6 Flex-foils

B.7 Series Resistance

B.8 Connectors

Annex C 8b9b Line Coding for D-PHY (normative)

C.1 Line Coding Features

C.1.1 Enabled Features for the Protocol

C.1.2 Enabled Features for the PHY

C.2 Coding Scheme

C.2.1 8b9b Coding Properties

C.2.2 Data Codes: Basic Code Set

C.2.3 Comma Codes: Unique Exception Codes

C.2.4 Control Codes: Regular Exception Codes

C.2.5 Complete Coding Scheme

C.3 Operation with the D-PHY

C.3.1 Payload: Data and Control

C.3.1.1 Idle/Sync Comma Symbols

C.3.1.2 Protocol Marker Comma Symbol

C.3.1.3 EoT Marker

C.3.2 Details for HS Transmission

C.3.2.1 SoT

C.3.2.2 HS Transmission Payload

C.3.2.3 EoT

C.3.3 Details for LP Transmission

C.3.3.1 SoT

C.3.3.2 LP Transmission Payload

C.3.3.3 EoT

C.4 Error Signaling

C.5 Extended PPI

C.6 Complete Code Set

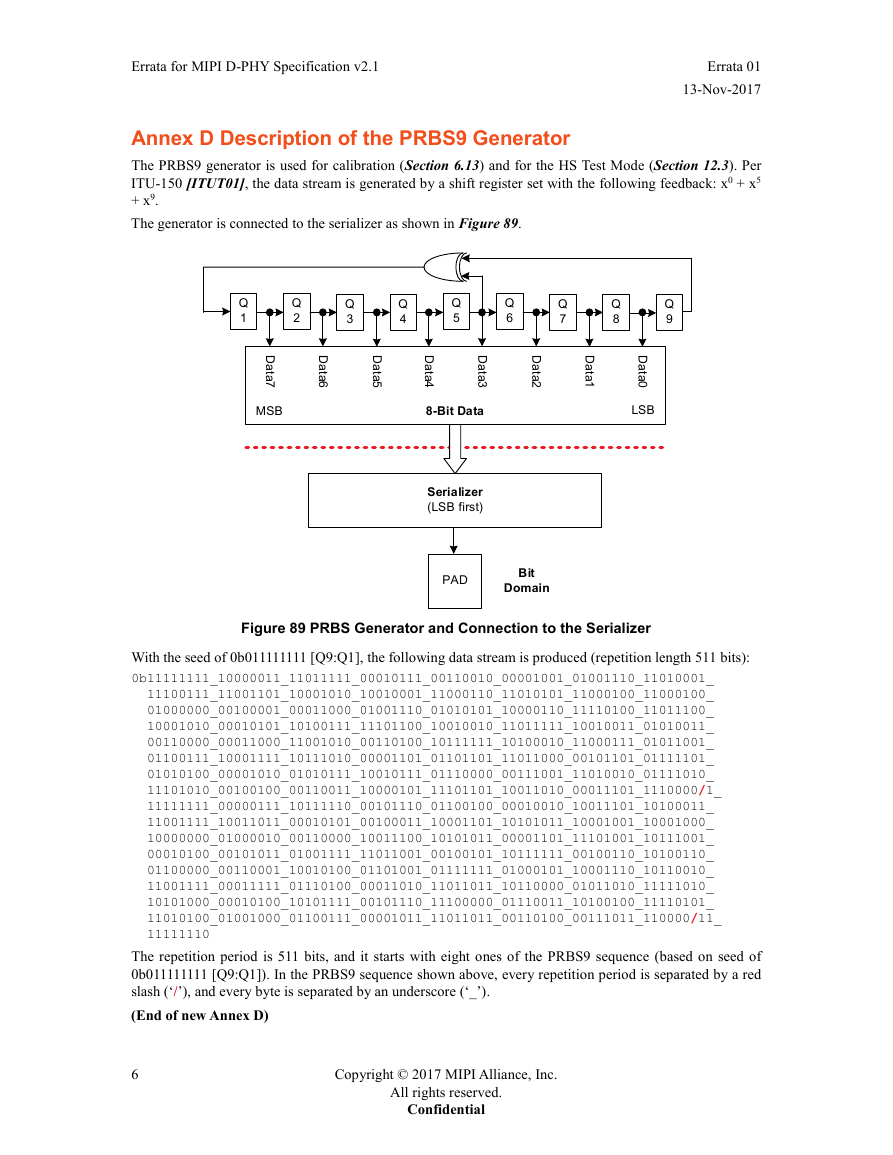

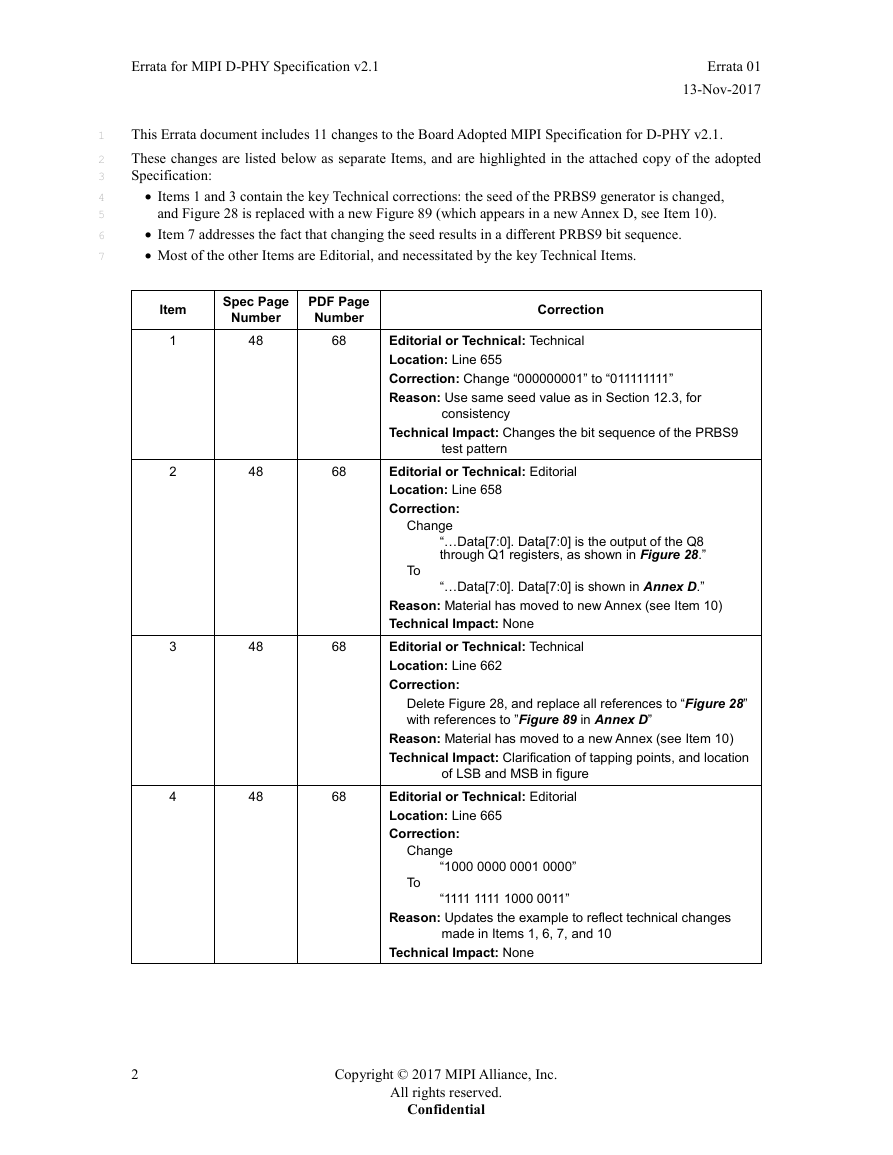

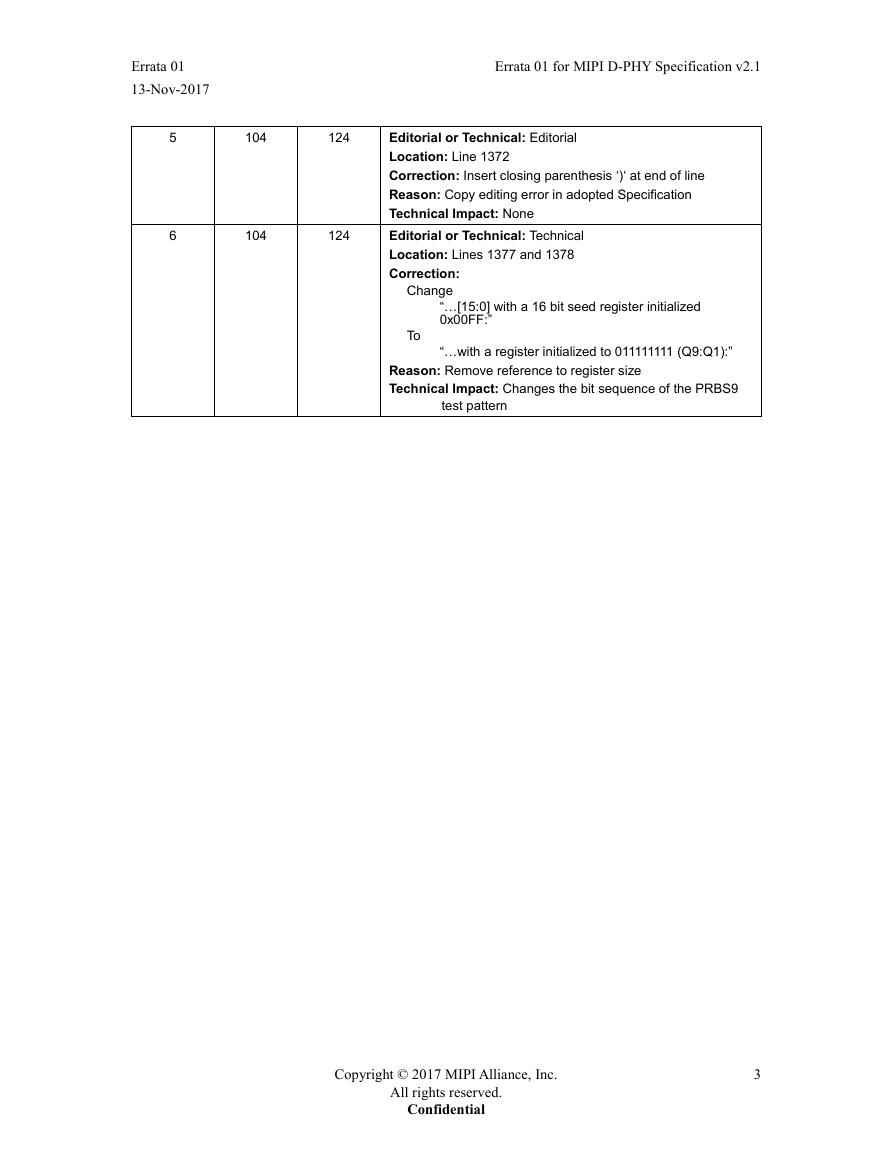

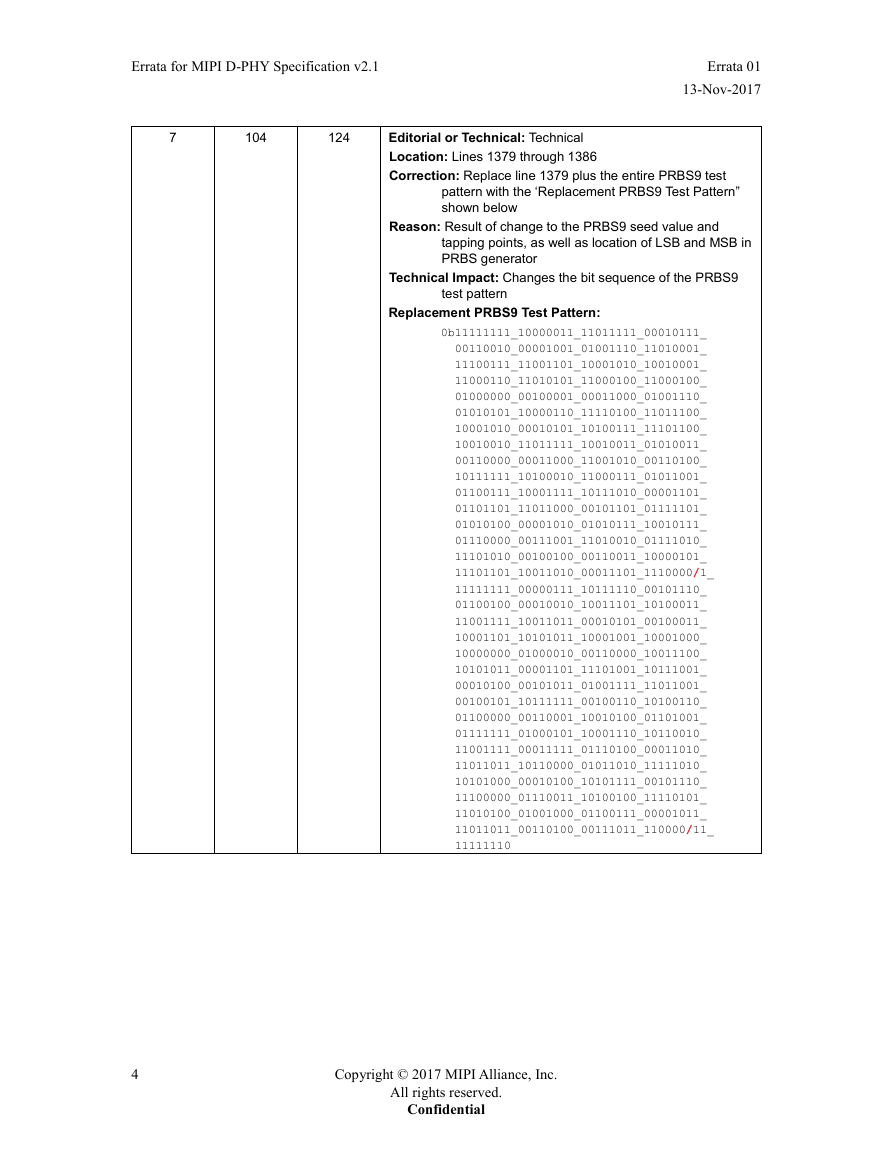

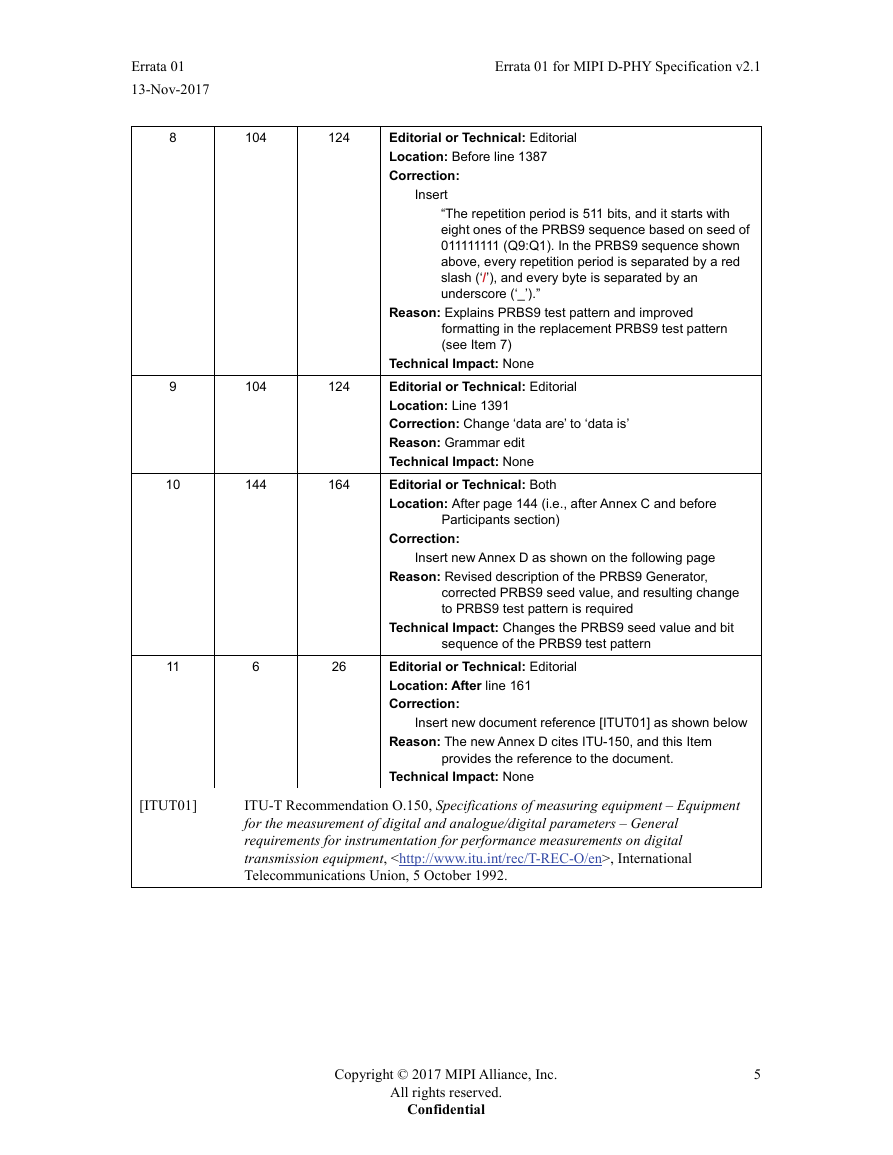

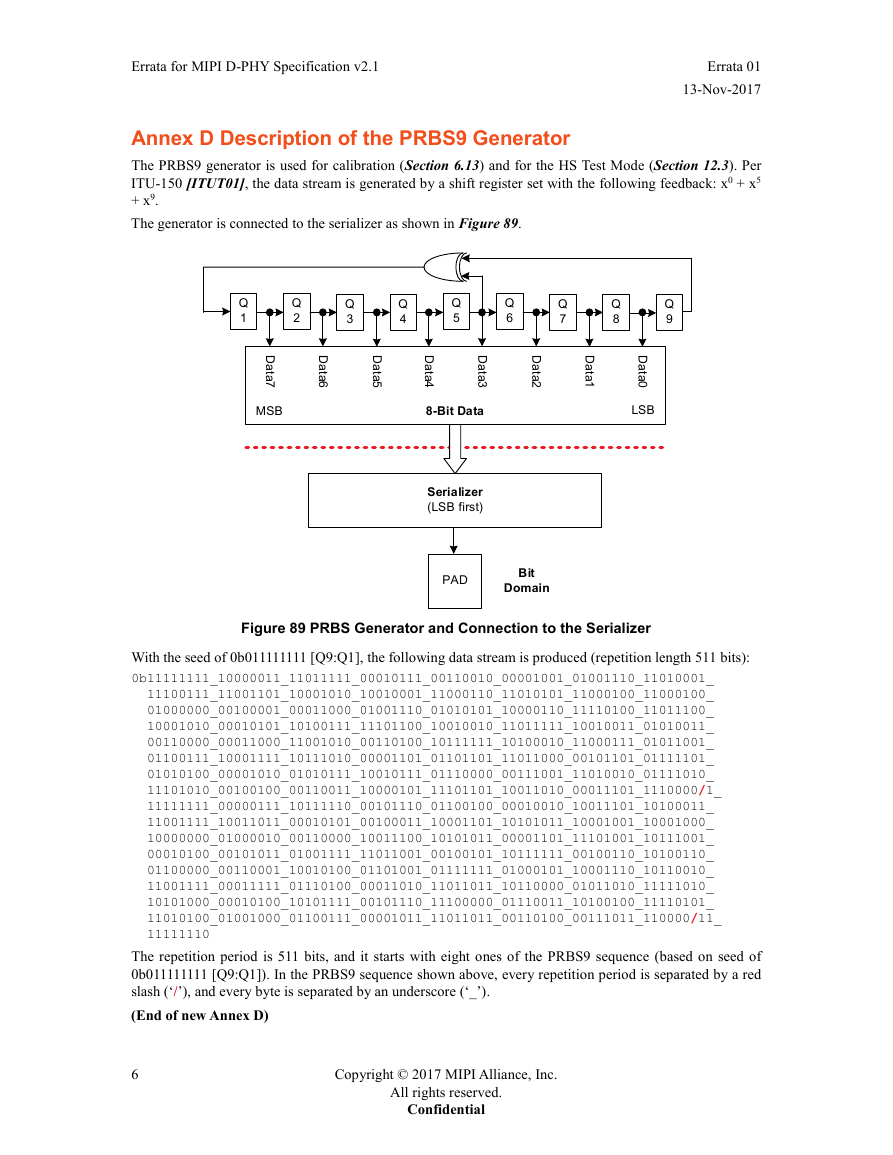

Annex D Description of the PRBS9 Generator

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc