Arm® Cortex®-M3 DesignStart™ FPGA-Xilinx edition User Guide

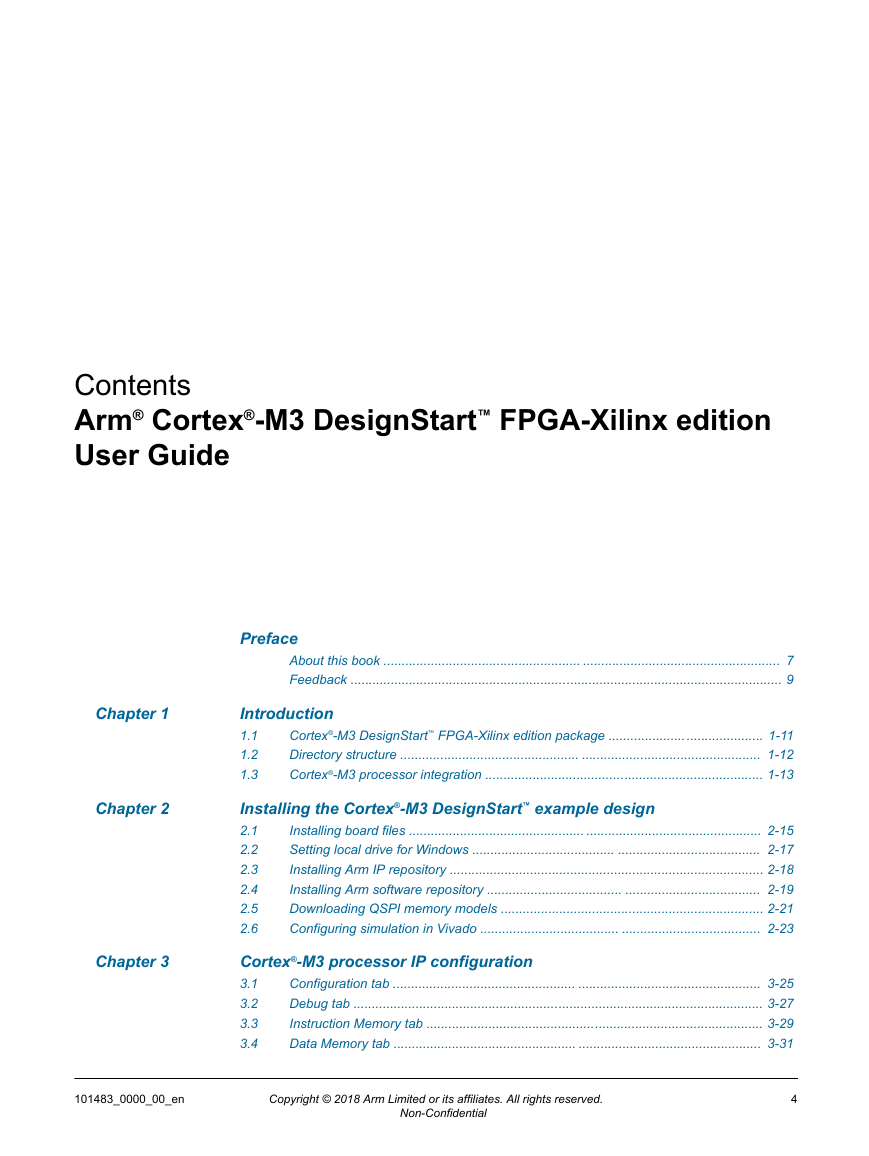

Table of Contents

Preface

About this book

Product revision status

Intended audience

Using this book

Glossary

Typographic conventions

Additional reading

Feedback

Feedback on this product

Feedback on content

1 : Introduction

1.1 : Cortex®-M3 DesignStart™ FPGA-Xilinx edition package

1.2 : Directory structure

1.3 : Cortex®-M3 processor integration

2 : Installing the Cortex®-M3 DesignStart™ example design

2.1 : Installing board files

2.2 : Setting local drive for Windows

2.3 : Installing Arm IP repository

2.4 : Installing Arm software repository

2.5 : Downloading QSPI memory models

2.5.1 : Micron QSPI model

2.5.2 : Cypress QSPI model

2.6 : Configuring simulation in Vivado

3 : Cortex®-M3 processor IP configuration

3.1 : Configuration tab

3.2 : Debug tab

3.3 : Instruction Memory tab

3.4 : Data Memory tab

3.5 : Cortex®-M3 processor signals

4 : Working with the Cortex®-M3 DesignStart™ example design

4.1 : Editing the A7 example design

4.2 : Debug

4.3 : Memory map

4.4 : QSPI multiplexing for the V2C-DAPLink board

4.5 : Interrupt mapping

4.6 : Constraints

4.7 : Loading the pre-built bitstream

4.8 : Loading the flash file

4.9 : Bit file regeneration

4.10 : Simulation

4.10.1 : Testbench conditionals

4.10.2 : Executing code from QSPI

4.10.3 : Wave files

5 : V2C-DAPLink board

5.1 : V2C-DAPLink adaptor board features

5.2 : V2C-DAPLink configuration

5.3 : Flash download requirements

5.4 : V2C-DAPLink board layout

5.5 : Conditions to enable the DAP interface

5.6 : DAP drivers

5.7 : Programming the V2C-DAPLink QSPI using drag and drop

5.8 : Using the μVision debugger to communicate through V2C-DAPLink

5.9 : Using the μVision debugger to download projects through the flash programming utility

5.10 : Recovering the DAP connection

6 : Example software design

6.1 : Example software design for Arty A7

6.2 : Example software design directory structure

6.3 : Example design reference files

6.4 : Generating the Arty A7 board support package

6.5 : Building the example software design

6.5.1 : Software design post processing

6.6 : Software update flow

6.6.1 : Generating the MMI file

6.6.2 : Generating bit and flash files

6.6.3 : Programming

A : Revisions

A.1 : Revisions

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc