吉林农业大学本科毕业设计

吉 林 农 业 大 学

本 科 毕 业 设 计

论文题目: 基于FPGA的SDRAM控制器的设计与实现

学生姓名:

专业年级:电子信息科学与技

指导教师: 职称 助 教

2008 年 6 月 2 日

1

�

吉林农业大学本科毕业设计

目 录

题目···························································································································Ⅰ

摘要及关键词···········································································································Ⅰ

1 前言························································································································1

2 SDRAM控制器的介绍与设计···············································································1

2.1 SDRAM 地址结构·······························································································5

2.2 SDRAM 的指令···································································································5

2.3 SDRAM初始化操作····························································································5

2.4 SDRAM 读写操作·······························································································6

2.5 SDRAM 操作终止·······························································································6

2.6 SDRAM工作原理································································································7

2.7 SDRAM 控制器方案···························································································9

2.7.1 接口信号介绍··································································································10

2.7.2 接口控制模块··································································································11

2.7.3 命令生成模块··································································································12

2.8 SDRAM 控制器的设计····················································································15

2.9 SDRAM控制器的具体实现···············································································17

3 FPGA介绍与设计··································································································21

3.1 FPGA芯片介绍···································································································21

3.2 在FPGA中设计和实现SDRAM控制器····························································22

4.总结························································································································24

参考文献···················································································································26

致 谢·························································································································27

附 录一·····················································································································29

附 录二·····················································································································30

2

�

吉林农业大学本科毕业设计

1 前 言

SDRAM的特点是大容量和高速度。其单片容量可达 256 Mb或更高,工作速

度可达 100~200 MHz以上,但是其控制方式比EDO/FPDRAM复杂得多。目前,

许多嵌入式设备的大容量存储器都采用SDRAM来实现。在设计中采用SDRAM

存储器时,大多都是用专用芯片完成其控制电路。但是,当我们对SDRAM存储

器进行特殊应用时,就需要自己设计控制电路了[1]。

SDRAM 是 Synchronous Dynamic Random Access Memory(同步动态随机存

储器)的简称,是前几年普遍使用的内存形式。SDRAM 采用 3.3v 工作电压,带

宽 64 位,SDRAM 将 CPU 与 RAM 通过一个相同的时钟锁在一起,使 RAM 和

CPU 能够共享一个时钟周期,以相同的速度同步工作,与 EDO 内存相比速度能

提高 50%。SDRAM 基于双存储体结构,内含两个交错的存储阵列,当 CPU 从

一个存储体或阵列访问数据时,另一个就已为读写数据做好了准备,通过这两个

存储阵列的紧密切换,读取效率就能得到成倍的提高。SDRAM 不仅可用作主存,

在显示卡上的显存方面也有广泛应用。SDRAM 曾经是长时间使用的主流内存,

从 430TX 芯片组到 845 芯片组都支持 SDRAM。但随着 DDR SDRAM 的普及,

SDRAM 也正在慢慢退出主流市场。

2 SDRAM控制器的介绍与设计

SDRAM: Synchronous Dynamic Random Access Memory,同步动态随机存取

存储器,同步是指Memory工作需要步时钟,内部的命令的发送与数据的传输都

以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数

据不是线性依次存储,而是由指定地址进行数据读写[2]。

SDRAM从发展到现在已经经历了四代,分别是:第一代SDR SDRAM,第

二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM.第一代与第二

代SDRAM均采用单端(Single-Ended)时钟信号,第三代与第四代由于工作频率

比较快,所以采用可降低干扰的差分时钟信号作为同步时钟。SDR SDRAM的时

钟频率就是数据存储的频率,第一代内存用时钟频率命名,如pc100,pc133 则

表明时钟信号为 100 或 133MHz,数据读写速率也为 100 或 133MHz。之后的第

二,三,四代DDR(Double Data Rate)内存则采用数据读写速率作为命名标准,

并且在前面加上表示其DDR代数的符号,PC-即DDR,PC2=DDR2,PC3=DDR3。

如PC2700 是DDR333,其工作频率是 333/2=166MHz,2700 表示带宽为 2.7G。

DDR的读写频率从DDR200 到DDR400,DDR2 从DDR2-400 到DDR2-800,DDR3

从DDR3-800 到DDR3-1666。很多人将SDRAM错误的理解为第一代也就是 SDR

SDRAM,并且作为名词解释,皆属误导。DDR SDRAM是“Double Data Rate

SDRAM”的缩写,即“双倍速率同步动态随机存储器”。与早期的SDRAM相比,

DDR SDRAM内存可在时钟脉冲的上升和下降沿同时传输信号,这意味着在相同

3

�

吉林农业大学本科毕业设计

的工作频率下,DDR SDRAM的理论传输速率为SDRAM的两倍[3]。例如:同为

133MHz的工作频率,SDRAM内存可以实现 1.06GB/s数据带宽,而DDR SDRAM

则达到了 2.1GB/s,这种DDR SDRAM内存便被称为DDR 266 或PC2100,前者代

表等效工作频率,后者表明了数据带宽。 DDR2 SDRAM则在DDR SDRAM的基

础上再次进行了改进,它同样可在时钟脉冲的上升和下降沿同时传输信号,但采

用了 4bit数据预读取方式,使得数据传输速率在DDR SDRAM的基础上翻番。例

如:同为 133MHz工作频率,DDR SDRAM可实现 2.1GB/s数据带宽,而DDR2

SDRAM则达到 4.2GB/s, 也被称为DDR2 533 或PC2 4200 内存。

SDRAM 内存访问采用突发(burst)模式,它和原理是,SDRAM 在现有的

标准动态存储器中加入同步控制逻辑(一个状态机),利用一个单一的系统时钟同

步所有的地址数据和控制信号。使用 SDRAM 不但能提高系统表现,还能简化设

计、提供高速的数据传输。 在功能上,它类似常规的 DRAM,也需时钟进行刷

新。 可以说,SDRAM 是一种改善了结构的增强型 DRAM。然而,SDRAM 是

如何利用它的同步特性而适应高速系统的需要的呢?我们知道,原先我们使用的

动态存储器技术都是建立在异步控制基础上的。系统在使用这些异步动态存储器

时需插入一些等待状态来适应异步动态存储器的本身需要,这时,指令的执行时

间往往是由内存的速度、而非系统本身能够达到的最高速率来决定。例如,当将

连续数据存入 CACHE 时,一个速度为 60ns 的快页内存需要 40ns 的页循环时间;

当系统速度运行在 100MHz 时(一个时钟周期 10ns),每执行一次数据存取,即需

要等待 4 个时钟周期!而使用 SDRAM,由于其同步特性,则可避免这一时。

SDRAM 结构的另一大特点是其支持 DRAM 的两列地址同时打开。两个打开的

存储体间的内存存取可以交叉进行,一般的如预置或激活列可以隐藏在存储体存

取过程中,即允许在一个存储体读或写的同时,令一存储体进行预置。按此进行,

100MHz 的无缝数据速率可在整个器件读或写中实现。因为 SDRAM 的速度约束

着系统的时钟速度,它的速度是由 MHz 或 ns 来计算的。 SDRAM 的速度至少

不能慢于系统的时钟速度,SDRAM 的访问通常发生在四个连续的突发周期,第

一个突发周期需要 4 个系统时钟周期,第二到第四个突发周期只需要 1 个系统时

钟周期。顺便提一下 BEDO(Burst EDO)也就是突发 EDO 内存。实际上其原理

和性能是和 SDRAM 差不多的,因为 Intel 的芯片组支持 SDRAM,由于 INTEL

的市场领导地位帮助 SDRAM 成为市场的标准。新的内存标准在新的世纪到来

之时,也带来了计算机硬件的重大改变。计算机的制造工艺发展到已经可以把微

处理器(CPU)的时钟频率提高的一千兆的边缘。相应的内存也必须跟得上处理

器的速度才行。现在有两个新的标准,DDR SDRAM 内存和 Rambus 内存。它们

之间的竞争将会成为 PC 内存市场竞争的核心。

DDR SDRAM 代表着一条内存逐渐演化的道路。Rambus 则代表着计算机设

计上的重大变革。从更远一点的角度看。DDR SDRAM 是一个开放的标准。然

4

�

吉林农业大学本科毕业设计

而 Rambus 则是一种专利。它们之间的胜利者将会对计算机制造业产生重大而深

远的影响。PC133 SDRAM:PC133 SDRAM 基本上只是 PC100 SDRAM 的延伸,

不论在 DRAM 制造、封装、模组、连接器方面,都延续旧有规范,它们的生产

设备相同,因此生产成本也几乎与 PC100 SDRAM 相同。严格来说,两者的差别

仅在于相同制程技术下,所多的一道「筛选」程序,将速度可达 133MHz 的颗粒

挑选出来而已。若配合可支持 133MHz 外频的芯片组,并提高 CPU 的前端总线

频率(Front Side Bus)到 133MHz,便能将 DRAM 带宽提高到 1GB/sec 以上,

从而提高整体系统性能。

DDR-SDRAM : DDR SDRAM ( Double Data Rate DRAM ) 或 称 之 为

SDRAMⅡ,由于 DDR 在时钟的上升及下降的边缘都可以传输资料,从而使得

实际带宽增加两倍,大幅提升了其性能/成本比。就实际功能比较来看,由 PC133

所衍生出的第二代 PC266 DDR SRAM(133MHz 时钟×2 倍数据传输=266MHz

带宽),不仅在 InQuest 最新测试报告中显示其性能平均高出 Rambus 24.4%,在

Micron 的测试中,其性能亦优于其他的高频宽解决方案,充份显示出 DDR 在性

能上已足以和 Rambus 相抗衡的程度。

SDRAM 内存 :自Intel Celeron系列以及AMD K6 处理器以及相关的主板芯

片组推出后,EDO DRAM内存性能再也无法满足需要了,内存技术必须彻底得

到个革新才能满足新一代CPU 架构的需求,此时内存开始进入比较经典的

SDRAM时代。 第一代SDRAM 内存为PC66 规范,但很快由于Intel 和AMD的

频率之争将CPU外频提升到了 100MHz,所以PC66 内存很快就被PC100 内存取

代,接着 133MHz 外频的PIII以及K7 时代的来临,PC133 规范也以相同的方式

进一步提升SDRAM 的整体性能,带宽提高到 1GB/sec以上。由于SDRAM 的带

宽为 64bit,正好对应CPU 的 64bit 数据总线宽度,因此它只需要一条内存便可

工作,便捷性进一步提高[5]。在性能方面,由于其输入输出信号保持与系统外频

同步,因此速度明显超越EDO 内存。 不可否认的是,SDRAM 内存由早期的

66MHz,发展后来的 100MHz、133MHz,尽管没能彻底解决内存带宽的瓶颈问

题,但此时CPU超频已经成为DIY用户永恒的话题,所以不少用户将品牌好的

PC100 品牌内存超频到 133MHz使用以获得CPU超频成功,值得一提的是,为了

方便一些超频用户需求,市场上出现了一些PC150、PC166 规范的内存。 曲高

和寡——Rambus DRAM内存 :尽管SDRAM PC133 内存的带宽可提高带宽到

1064MB/S,加上Intel已经开始着手最新的Pentium 4 计划,所以SDRAM PC133

内存不能满足日后的发展需求,此时,Intel为了达到独占市场的目的,与Rambus

联合在PC市场推广Rambus DRAM内存(称为RDRAM内存)。与SDRAM不同的

是,其采用了新一代高速简单内存架构,基于一种类RISC(Reduced Instruction Set

Computing,精简指令集计算机)理论,这个理论可以减少数据的复杂性,使得整

个系统性能得到提高。

5

�

吉林农业大学本科毕业设计

SDR不等于SDRAM。Pin:模组或芯片与外部电路电路连接用的金属引脚,而

模组的pin就是常说的“金手指”。SIMM:Sigle In-line Memory Module,单列内存模

组。内存模组就是我们常说的内存条,所谓单列是指模组电路板与主板插槽的接

口只有一列引脚(虽然两侧都有金手指)。DIMM:Double In-line Memory Module,

双列内存模组。是我们常见的模组类型,所谓双列是指模组电路板与主板插槽的

接口有两列引脚,模组电路板两侧的金手指对应一列引脚。RDIMM:registered

DIMM,带寄存器的双线内存模块SO-DIMM:笔记本常用的内存模组。

工作电压:

SDR:3.3V

DDR:2.5V

DDR2:1.8V

DDR3:1.5V

SDRAM 的特点是大容量和高速度。其单片容量可达 256Mb 或更高,工作

速度可达 100-200MHz 以上,是其控制方式比 EDO/FPDRAM 复杂得多。目前,

许多嵌入式设备的大容量存储器都采用 SDRAM 来实现。在设计中采用 SDRAM

存储器时,大多都是用专用芯片完成其控制电路。但是,当我们对 SDRAM 存储

器进行特殊应用时,就需要自己设计控制电路了。

SDRAM 具有多种工作模式,内部操作是一个复杂的状态机。SDRAM 器件

的管脚分为以下几类:

(1)控制信号包括片选,时钟,时钟使能,行列地址选择,读写选择,数据

有效。

(2)地址时分复用管脚,控制输入的地址为行地址或列地址。

(3)数据双向管脚。SDRAM 的所有操作都同步于时钟。根据时钟上升沿时

控制管脚和地址输入的状态,可以产生多种输入令:

①模式寄存器设置命令;

②激活命令;

③预充命令;

④读命令;

⑤写命令;

⑥带预充的读命令;

⑦带预充的写命令;

⑧自动刷新命令;另外还有空操作命令。

根据输入命令,SDRAM 状态在内部状态间转移。

SDRAM 控制器一般有两种实现方法:一种是采用专用控制芯片;另一种是用

FPGA 进行控制。由于目前 FPGA 技术比较成熟、编程方便、控制灵活,而且可

以通过软件实现各种接口功能,在高速视频信号数据传输系统中采用 FPGA 进行

6

�

吉林农业大学本科毕业设计

控制比较合适。采用 FPGA 进行控制比较合适。

2.1 SDRAM 地址结构

SDRAM的存储地址分为页(bank)地址,行(row)地址和列(column)地

址。例如一个 8MByte的SDRAM,被分为 4 个bank,即 1 个bank为 2MByte,每

个bank包括 12 行 8 列[6]。

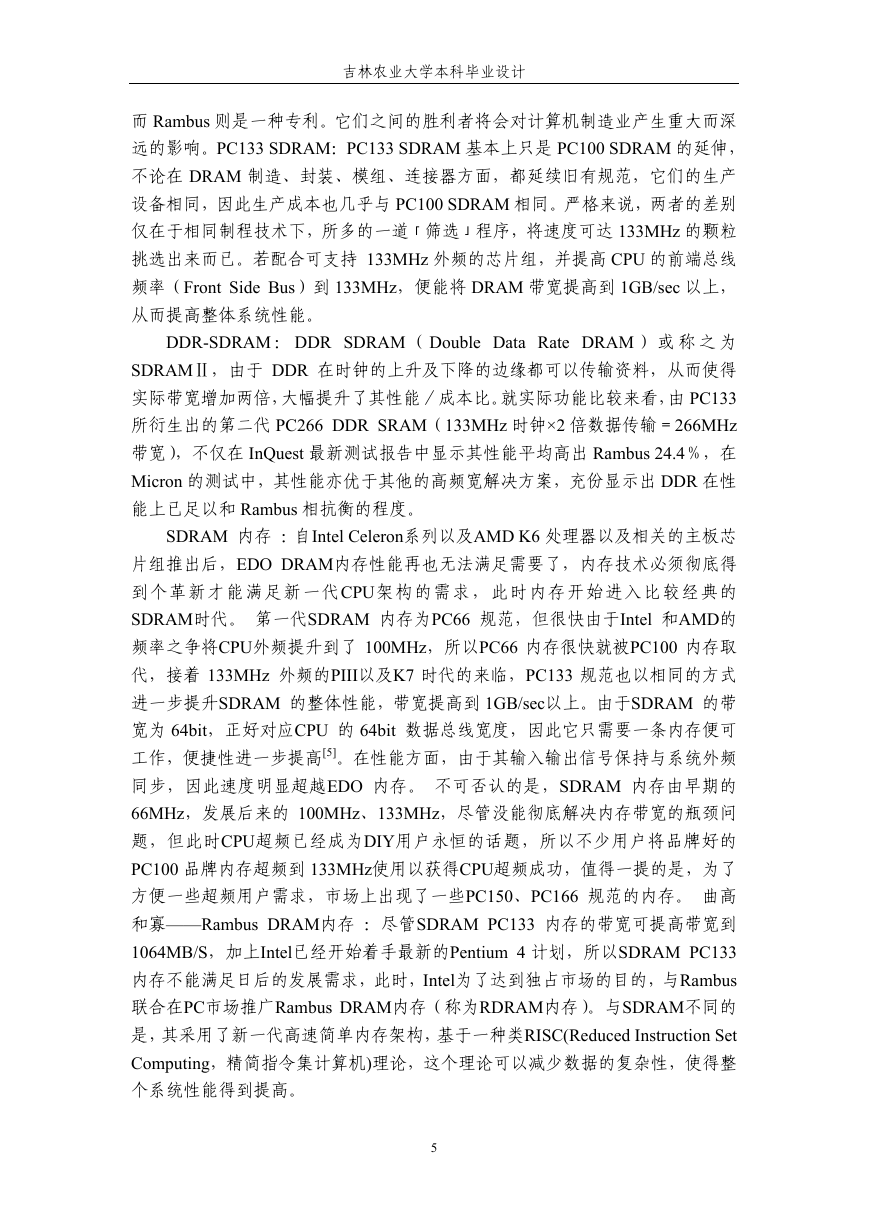

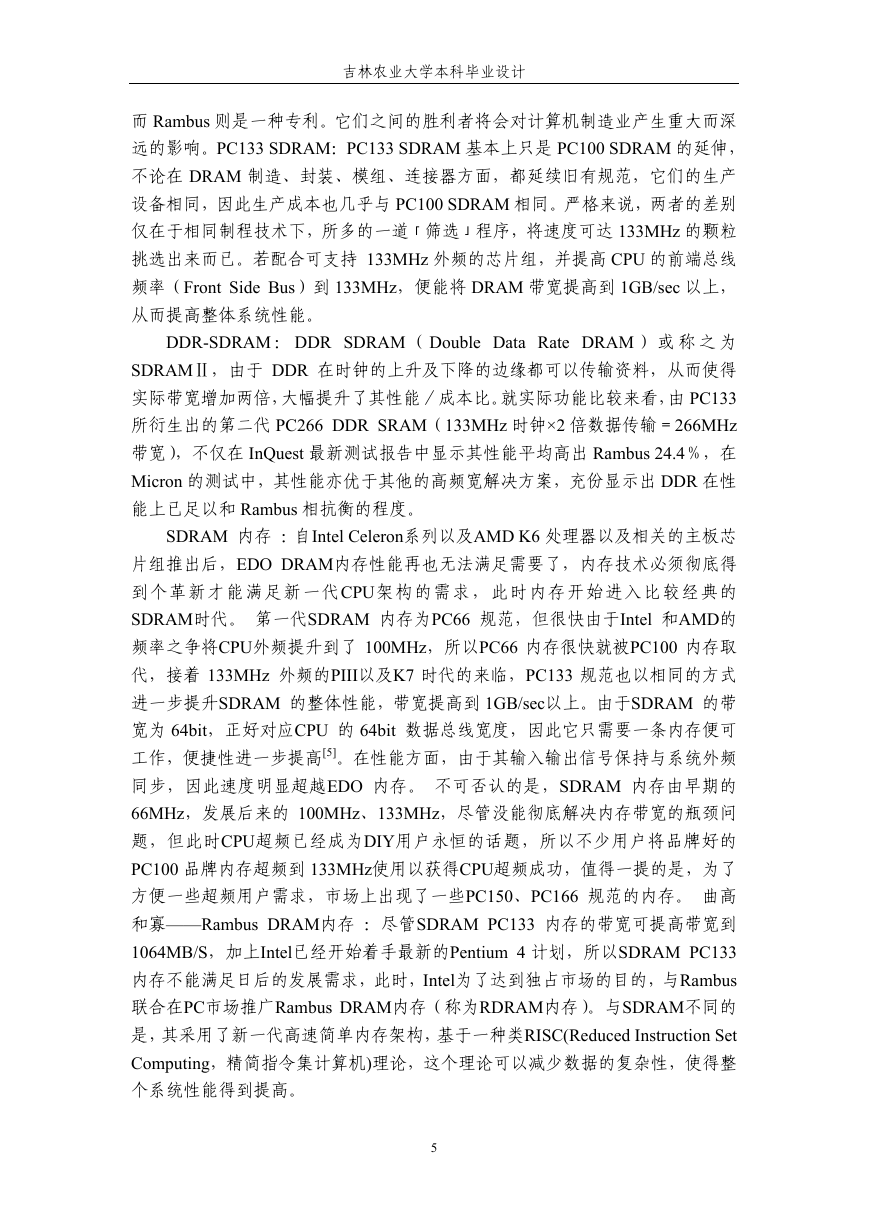

2.2 SDRAM 的指令

SDRAM 的一系列指令如表 1 所示,每个指令最终都是通过控制 RAS、CAS、

WE 信号来实现。通常对 SDRAM 的操作过程如下:

命令

空操作

页操作

读操作

写操作

突发操作终止

预充电

配置模式寄存

缩写

NOP

ACT

RD

WR

BT

PCH

LMR

表 1 SDRAM 命令

Table 1 SDRAM order

RAS

CAS

WE

H

L

H

H

H

L

L

H

H

L

L

H

H

L

H

H

H

L

L

L

L

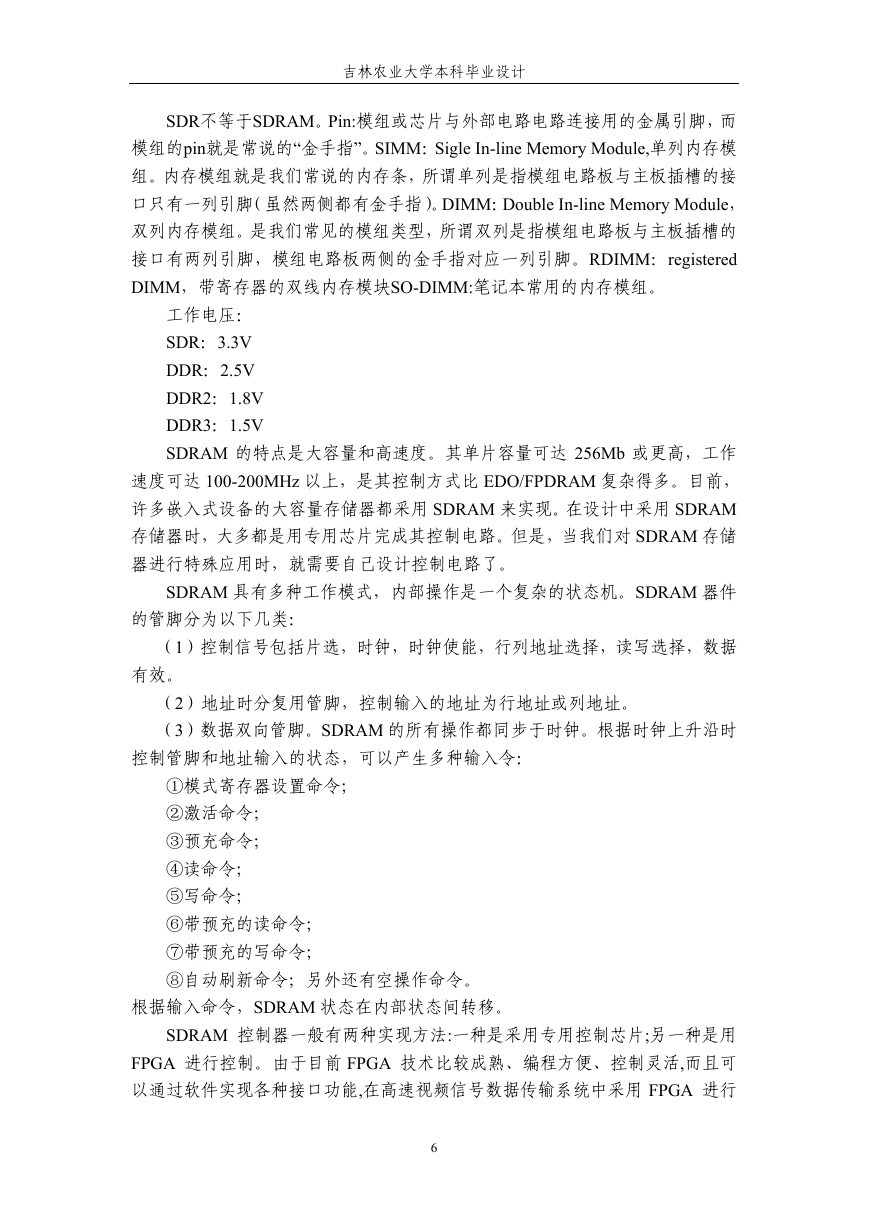

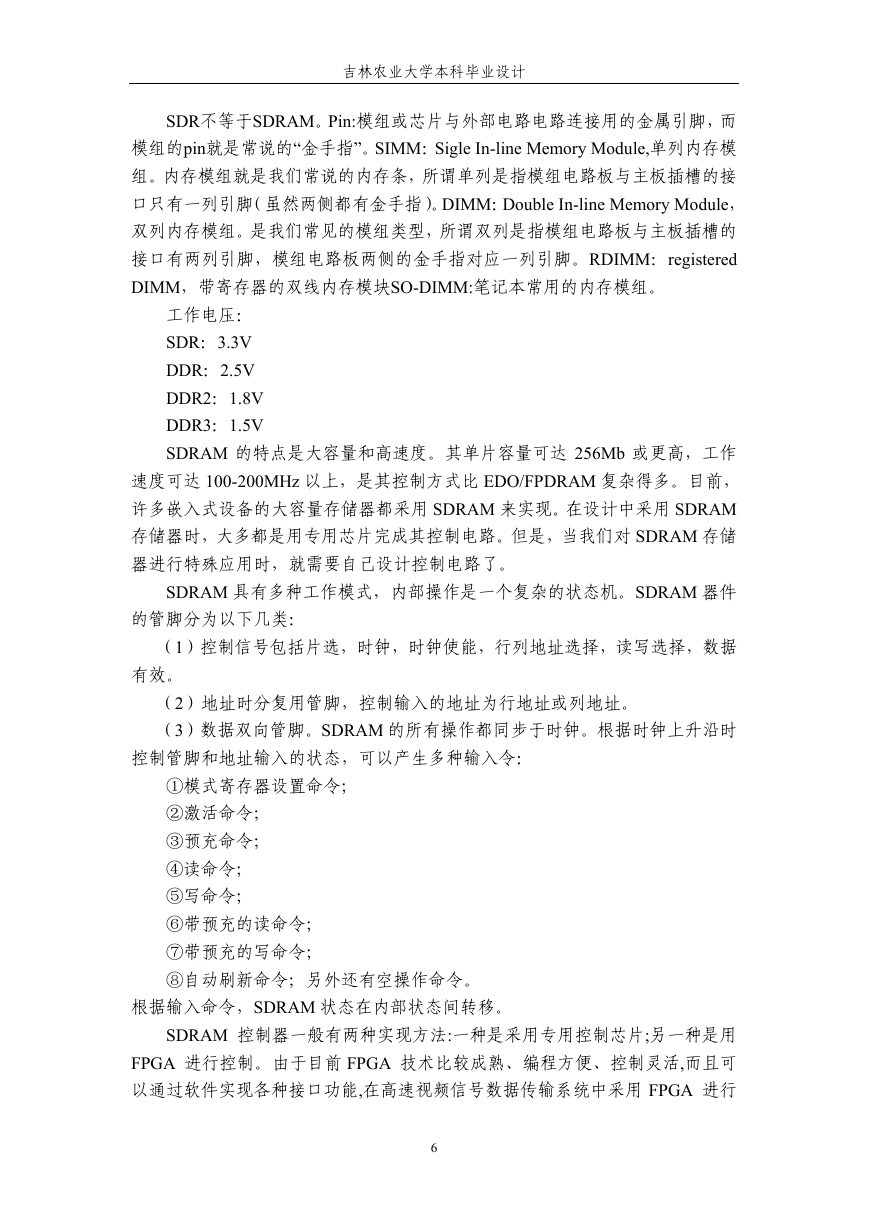

2.3 SDRAM 初始化操作

上电后至少等待 100ns,然后至少执行 1 条空操作;对所有页执行预充电操

作;向各页发出两条刷新操作指令;最后执行 SDRAM 工作模式的设定 LMR 命

令用来配置 SDRAM 工作模式寄存器,SDRAM 工作寄存器如表 2 所示。其中

A11~A10 是用户保留位;A9 用来配置写突发模式;A8~A7 是操作模式,通常

为“00”,代表标准操作模式;A6~A4 设置 CAS 延迟时间;A3 决定突发操作模式

是顺序还是间隔型;最后的三位 A2~A0 用来配置突发长度。

A11

A10

A9

表 2 SDRAM 工作寄存器

Table 2 SDRAM working register

A4

A8

A7

A6

A5

A3

A2 A1 A0

7

�

吉林农业大学本科毕业设计

Reserve

Write burst

Operating

Latency mode

mode

mode

Burst length

Burst

type

2.4 SDRAM 读、写操作

根据实际应用的需要,发出读、写指令。SDRAM可实现突发式读写,支持的

突发长度可配置为 1 个、2 个、4 个、8 个数据周期或者页模式[7]。并且突发的模

式可以配置为顺序或者间隔型。对SDRAM进行访问的最主要操作就是读RD和写WR

操作。SDRAM在进行读写操作时,必须要先进行页激活ACT操作,以保证存储单元

是打开的,以便从中读取地址或者写入地址,关闭存储单元通过预充电PHC命令

实现。在进行写操作时,内部的列地址和数据就会被寄存;进行读操作时,内部

地址被寄存,等待CAS 延迟时间(通常为 1~3 个时钟周期)后,读出的数据出

现在数据总线上。

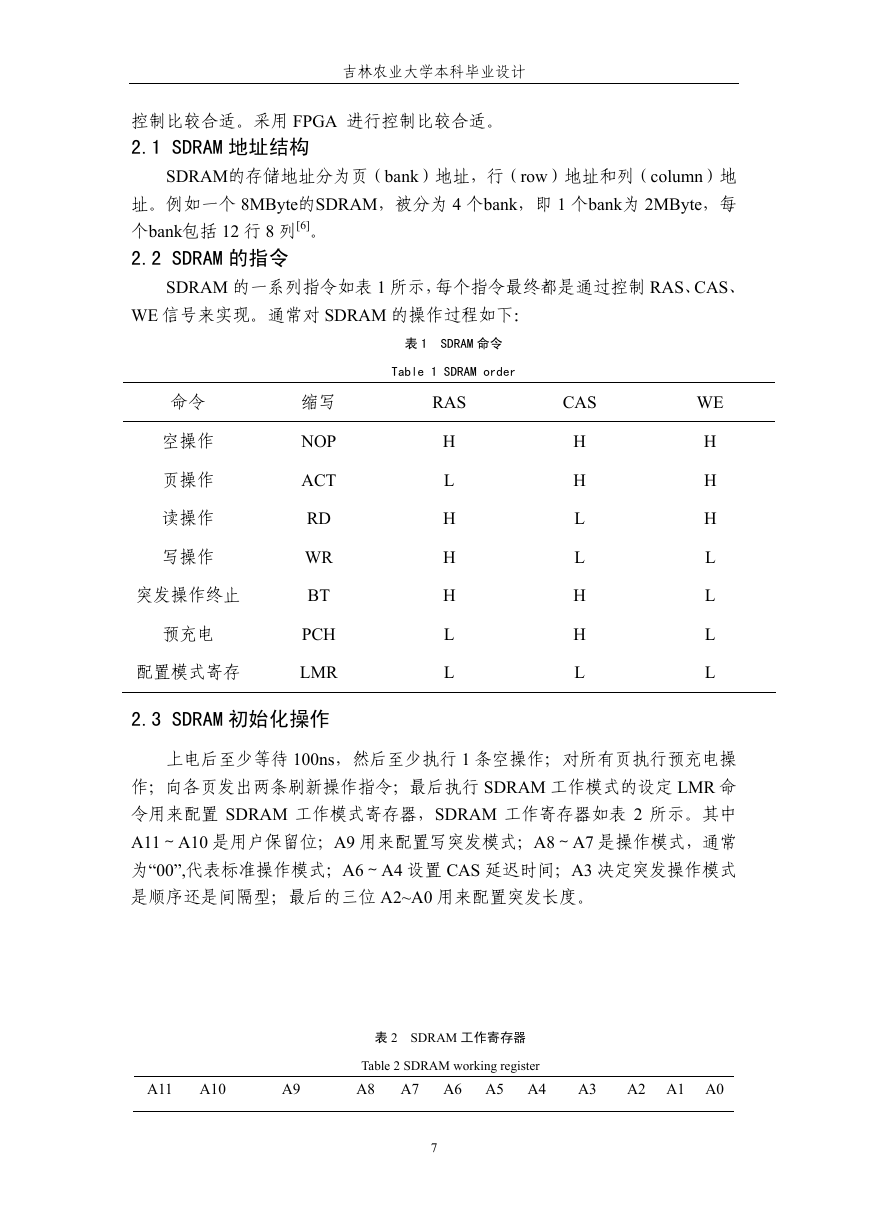

2.5 SDRAM 操作终止

当SDRAM接收到读、写指令后,开始进行顺次的读写操作,直到达到突发

长度或者突发终止指令BT出现。 SDRAM 基本操作原理:SDRAM的控制是根据

时钟上升沿时刻控制信号的不同 组 合实 现的 。控制SD RA M的 基 本操 作包括 :

初始化 、刷 新 、块激活 、读写 访 问 、预充 电等 。以 现代司的H Y57V281620 H CS T2H

( 2MB ×16 bit ×4 ba nks)为例 , 简要介绍 一下SD RA M的 操作[1,2] 。

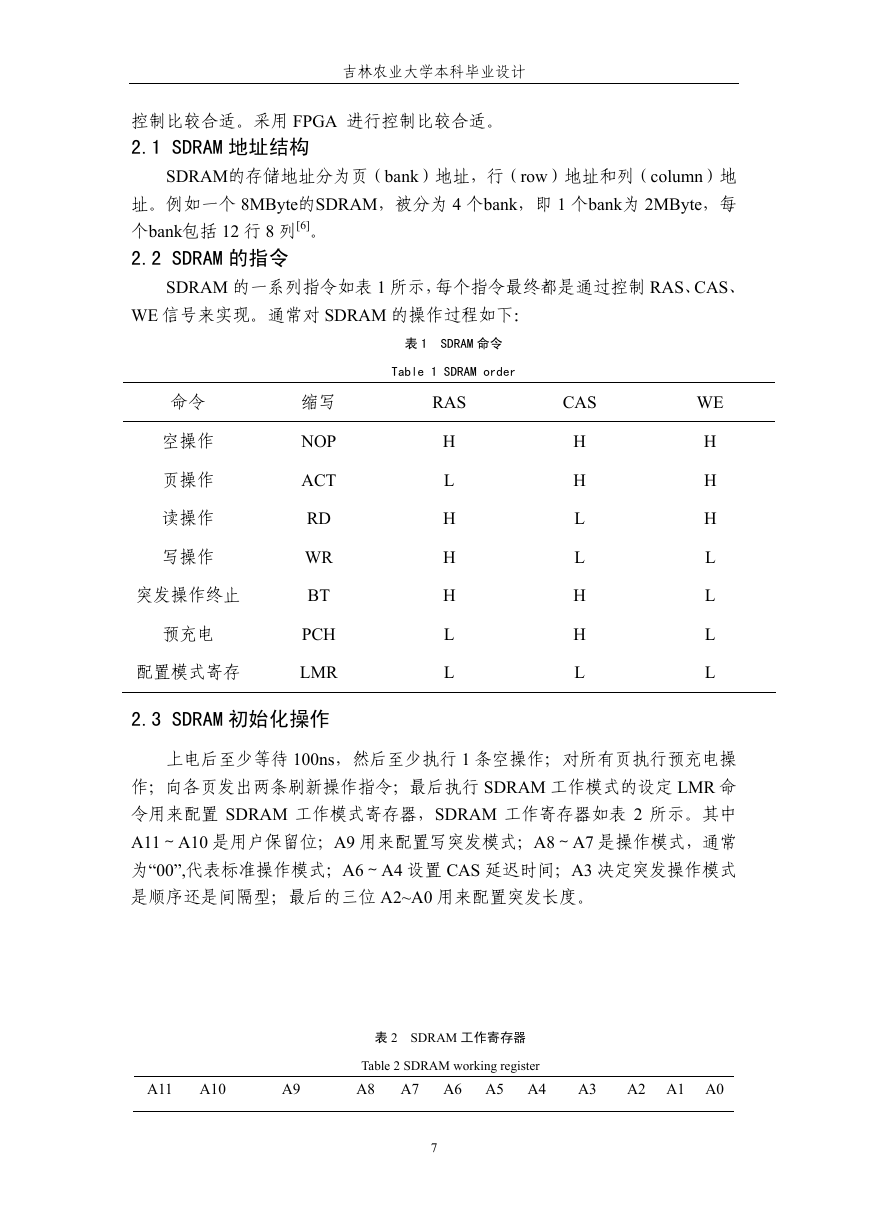

SDRAM 的初始化 (见图1) ,模式设置 (见图2) 操作过程如下 。

(1)在 电 源 管 脚 上 电(电 压 不 得 超 过 标 称 值 的0.3V) 并且CLK时钟稳定

后经过 200 μs 延迟 ,执行一次 Command Inhibit 或 N O P 命令 (该命令在延迟

周期的后期发出) 且 CKE 信号为高 。

(2)对所有的块进行预充电 ( Precharge All) ,所有的块都进入空闲 ( Idle)

状态 。

(3)预 充 电 后 执 行 两 个 自动刷新 ( Auto Refresh) 命令 ,然后 发出模

式设置命 令来设 置 模式寄存器 (Loa d M R) 。由于上 电后 模式 寄 存 器 的状

态是不确定的 ,所以在进行 SD RA M 操作之前一定要 先设置模式寄存器 。

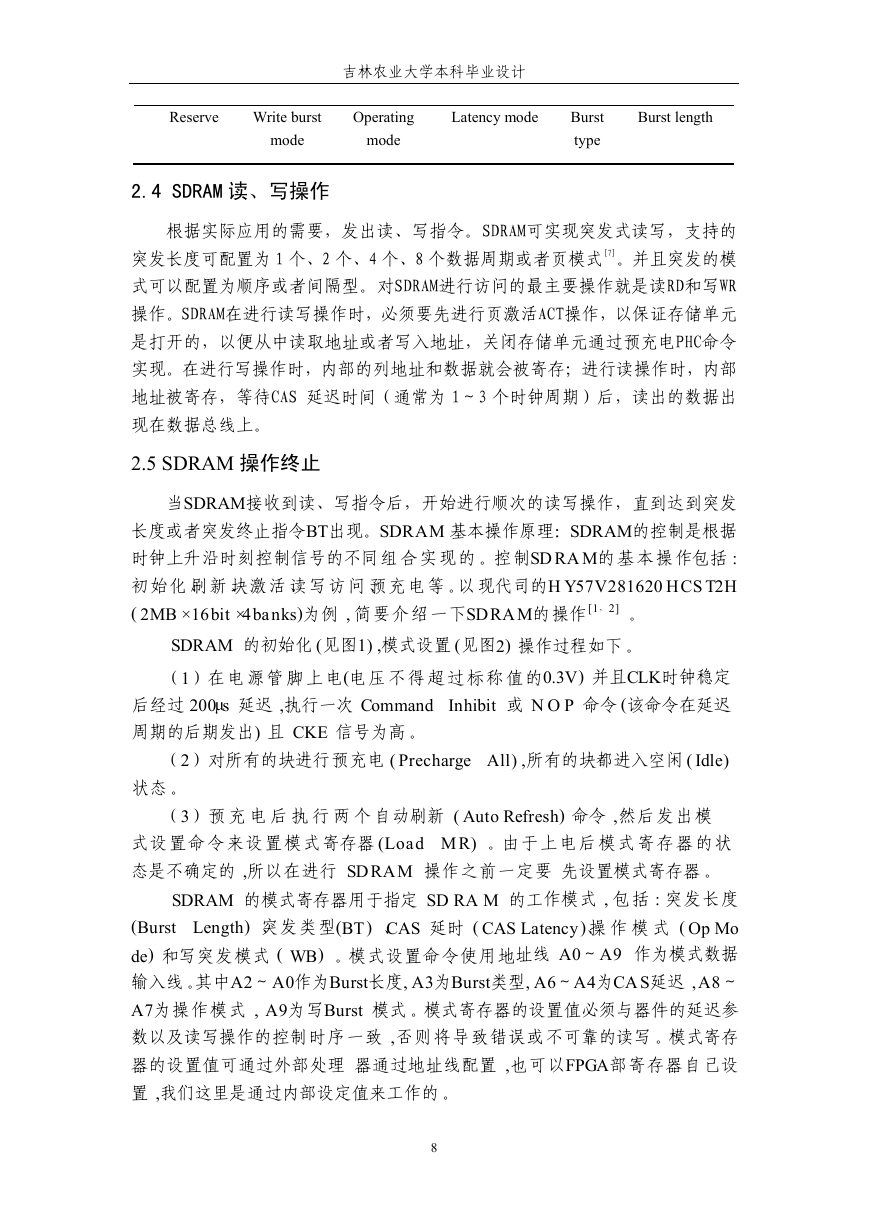

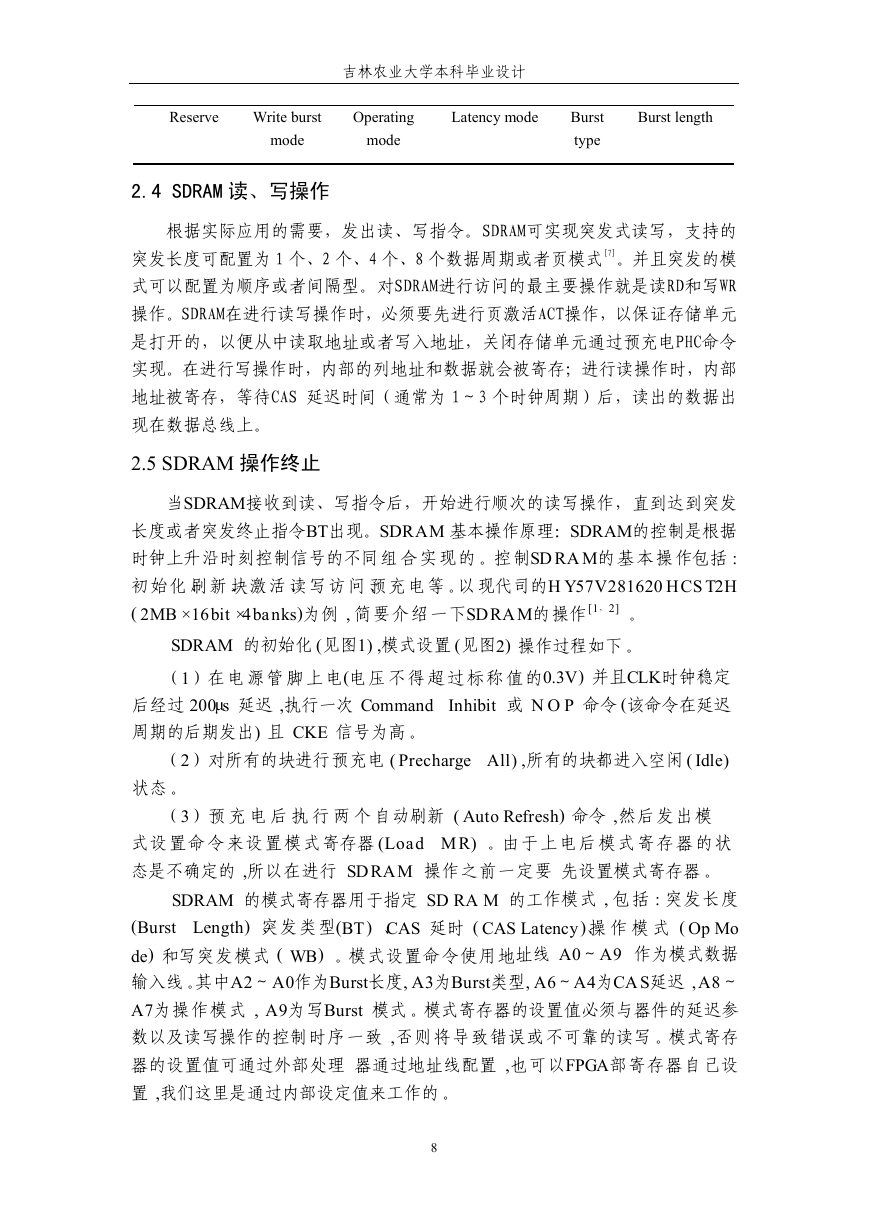

SDRAM 的模式寄存器用于指定 SD RA M 的工作模式 , 包括 : 突发长度

(Burst Length) 、突发类 型(BT ) 、CAS 延时 ( CAS Latency )、操 作 模 式 ( Op Mo

de) 和写突发模式 ( WB) 。模式设置命令使用地址线 A0~A9 作为模式数据

输入线 。其中A2~A0作为Burst长度, A3为Burst类型, A6~A4为CA S延迟 , A8~

A7为操作模式 , A9为写Burst 模式 。模式寄存器的设置值必须与器件的延迟参

数以及读写操作的控制时序一致 ,否则将导致错误或不可靠的读写 。模式寄存

器的设置值可通过外部处理 器通过地址线配置 ,也可以FPGA部寄存器自己设

置 ,我们这里是通过内部设定值来工作的 。

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc