Title Page - SPRU592E

Read This First

About This Manual

Notational Conventions

Related Documentation From Texas Instruments

Trademarks

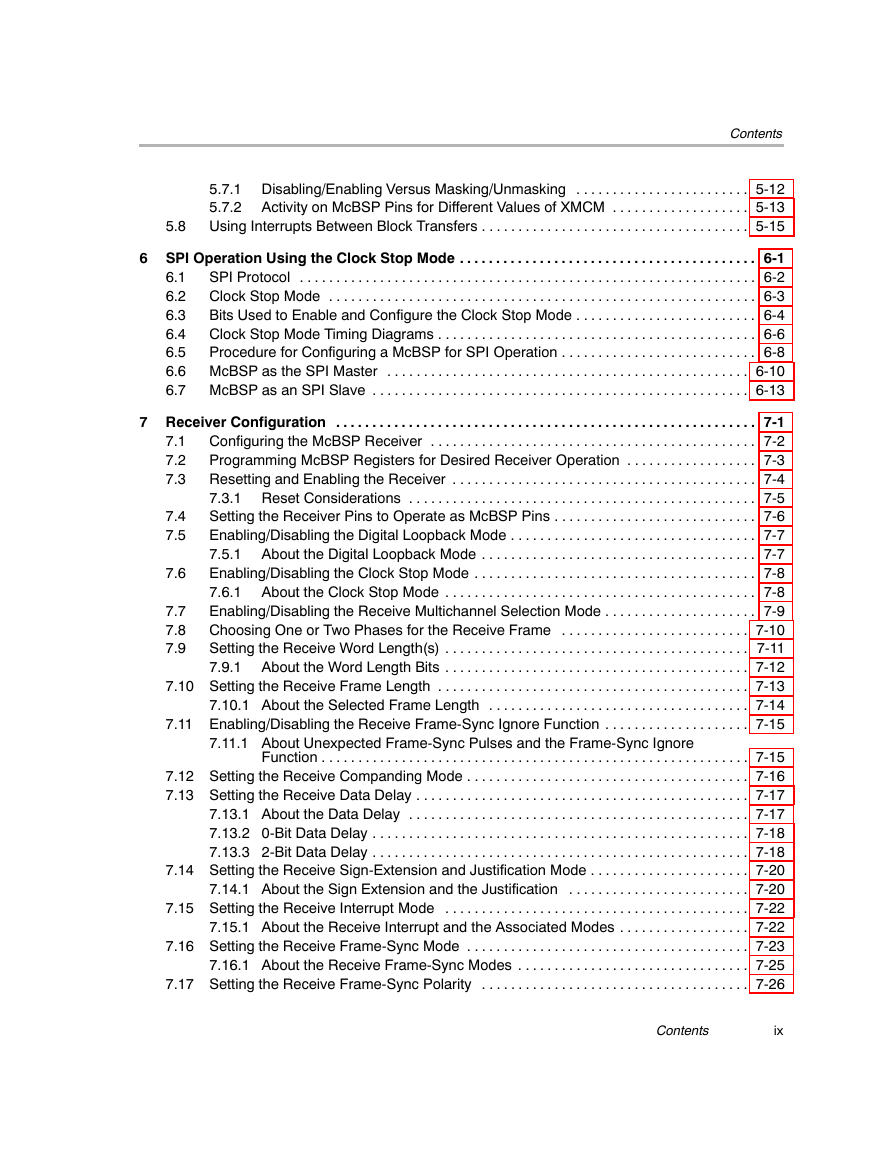

Contents

Figures

Tables

Chapter 1: Introduction to the McBSP

1.1 Introduction

1.2 Key Features of the McBSP

1.3 Block Diagram of the McBSP

1.4 McBSP Pins

Chapter 2: McBSP Operation

2.1 Data Transfer Process of a McBSP

2.1.1 Data Transfer Process for Word Length of 8, 12, or 16 Bits

2.1.2 Data Transfer Process for Word Length of 20, 24, or 32 Bits

2.2 Companding (Compressing and Expanding) Data

2.2.1 Companding Formats

2.2.2 Capability to Compand Internal Data

2.2.3 Reversing Bit Order: Option to Transfer LSB First

2.3 Clocking and Framing Data

2.3.1 Clocking

2.3.2 Serial Words

2.3.3 Frames and Frame Synchronization

2.3.4 Detecting Frame-Sync Pulses, Even in the Reset State

2.3.5 Ignoring Unexpected Frame-Sync Pulses

2.3.6 Frame Frequency

2.3.7 Maximum Frame Frequency

2.4 Frame Phases

2.4.1 Number of Phases, Words, and Bits Per Frame

2.4.2 Single-Phase Frame Example

2.4.3 Dual-Phase Frame Example

2.4.4 Implementing the AC97 Standard With a Dual-Phase Frame

2.5 McBSP Reception

2.6 McBSP Transmission

2.7 Interrupts and DMA Events Generated by a McBSP

Chapter 3: Sample Rate Generator of the McBSP

3.1 Sample Rate Generator

3.2 Clock Generation in the Sample Rate Generator

3.2.1 Choosing an Input Clock

3.2.2 Choosing a Polarity for the Input Clock

3.2.3 Choosing a Frequency for the Output Clock (CLKG)

3.2.4 Keeping CLKG Synchronized to an External Input Clock

3.3 Frame Sync Generation in the Sample Rate Generator

3.3.1 Choosing the Width of the Frame-Sync Pulse on FSG

3.3.2 Controlling the Period Between the Starting Edges of Frame-Sync Pulses on FSG

3.4 Synchronizing Sample Rate Generator Outputs to an External Clock

3.4.1 Synchronization Examples

3.5 Reset and Initialization Procedure for the Sample Rate Generator

3.6 Sample Rate Generator Clocking Examples

3.6.1 Double-Rate ST-Bus Clock

3.6.2 Single-Rate ST-Bus Clock

3.6.3 Other Double-Rate Clock

Chapter 4: McBSP Exception/Error Conditions

4.1 McBSP Exception/Error Conditions

4.2 Overrun in the Receiver

4.2.1 Example of the Overrun Condition

4.2.2 Example of Preventing the Overrun Condition

4.3 Unexpected Receive Frame-Sync Pulse

4.3.1 Possible Responses to Receive Frame-Sync Pulses

4.3.2 Example of an Unexpected Receive Frame-Sync Pulse

4.3.3 Preventing Unexpected Receive Frame-Sync Pulses

4.4 Overwrite in the Transmitter

4.4.1 Example of the Overwrite Condition

4.4.2 Preventing Overwrites

4.5 Underflow in the Transmitter

4.5.1 Example of the Underflow Condition

4.5.2 Example of Preventing the Underflow Condition

4.6 Unexpected Transmit Frame-Sync Pulse

4.6.1 Possible Responses to Transmit Frame-Sync Pulses

4.6.2 Example of an Unexpected Transmit Frame-Sync Pulse

4.6.3 Preventing Unexpected Transmit Frame-Sync Pulses

Chapter 5: Multichannel Selection Modes

5.1 Channels, Blocks, and Partitions

5.2 Multichannel Selection

5.3 Configuring a Frame for Multichannel Selection

5.4 Using Two Partitions

5.4.1 Assigning Blocks to Partitions A and B

5.4.2 Reassigning Blocks During Reception/Transmission

5.5 Using Eight Partitions

5.6 Receive Multichannel Selection Mode

5.7 Transmit Multichannel Selection Mode

5.7.1 Disabling/Enabling Versus Masking/Unmasking

5.7.2 Activity on McBSP Pins for Different Values of XMCM

5.8 Using Interrupts Between Block Transfers

Chapter 6: SPI Operation Using the Clock Stop Mode

6.1 SPI Protocol

6.2 Clock Stop Mode

6.3 Bits Used to Enable and Configure the Clock Stop Mode

6.4 Clock Stop Mode Timing Diagrams

6.5 Procedure for Configuring a McBSP for SPI Operation

6.6 McBSP as the SPI Master

6.7 McBSP as an SPI Slave

Chapter 7: Receiver Configuration

7.1 Configuring the McBSP Receiver

7.2 Programming McBSP Registers for Desired Receiver Operation

7.3 Resetting and Enabling the Receiver

7.3.1 Reset Considerations

7.4 Setting the Receiver Pins to Operate as McBSP Pins

7.5 Enabling/Disabling the Digital Loopback Mode

7.5.1 About the Digital Loopback Mode

7.6 Enabling/Disabling the Clock Stop Mode

7.6.1 About the Clock Stop Mode

7.7 Enabling/Disabling the Receive Multichannel Selection Mode

7.8 Choosing One or Two Phases for the Receive Frame

7.9 Setting the Receive Word Length(s)

7.9.1 About the Word Length Bits

7.10 Setting the Receive Frame Length

7.10.1 About the Selected Frame Length

7.11 Enabling/Disabling the Receive Frame-Sync Ignore Function

7.11.1 About Unexpected Frame-Sync Pulses and the Frame-Sync Ignore Function

7.12 Setting the Receive Companding Mode

7.13 Setting the Receive Data Delay

7.13.1 About the Data Delay

7.13.2 0-Bit Data Delay

7.13.3 2-Bit Data Delay

7.14 Setting the Receive Sign-Extension and Justification Mode

7.14.1 About the Sign Extension and the Justification

7.15 Setting the Receive Interrupt Mode

7.15.1 About the Receive Interrupt and the Associated Modes

7.16 Setting the Receive Frame-Sync Mode

7.16.1 About the Receive Frame-Sync Modes

7.17 Setting the Receive Frame-Sync Polarity

7.17.1 About Frame Sync Pulses, Clock Signals, and Their Polarities

7.18 Setting the SRG Frame-Sync Period and Pulse Width

7.18.1 About the Frame-Sync Period and the Frame-Sync Pulse Width

7.19 Setting the Receive Clock Mode

7.19.1 Selecting a Source for the Receive Clock and a Data Direction for the CLKR Pin

7.20 Setting the Receive Clock Polarity

7.20.1 About Frame Sync Pulses, Clock Signals, and Their Polarities

7.21 Setting the SRG Clock Divide-Down Value

7.21.1 About the Sample Rate Generator Clock Divider

7.22 Setting the SRG Clock Synchronization Mode

7.23 Setting the SRG Clock Mode (Choosing an Input Clock)

7.23.1 About the SRG Clock Mode

7.24 Setting the SRG Input Clock Polarity

7.24.1 Using CLKSP/CLKXP/CLKRP to Choose an Input Clock Polarity

Chapter 8: Transmitter Configuration

8.1 Configuring the Transmitter

8.2 Programming McBSP Registers for Desired Transmitter Operation

8.3 Resetting and Enabling the Transmitter

8.3.1 Reset Considerations

8.4 Setting the Transmitter Pins to Operate as McBSP Pins

8.5 Enabling/Disabling the Digital Loopback Mode

8.5.1 About the Digital Loopback Mode

8.6 Enabling/Disabling the Clock Stop Mode

8.6.1 About the Clock Stop Mode

8.7 Enabling/Disabling Transmit Multichannel Selection

8.8 Choosing One or Two Phases for the Transmit Frame

8.9 Setting the Transmit Word Length(s)

8.9.1 About the Word Length Bits

8.10 Setting the Transmit Frame Length

8.10.1 About the Selected Frame Length

8.11 Enabling/Disabling the Transmit Frame-Sync Ignore Function

8.11.1 About Unexpected Frame-Sync Pulses and the Frame-Sync Ignore Function

8.12 Setting the Transmit Companding Mode

8.13 Setting the Transmit Data Delay

8.13.1 About the Data Delay

8.13.2 0-Bit Data Delay

8.13.3 2-Bit Data Delay

8.14 Setting the Transmit DXENA Mode

8.14.1 About the DXENA Mode

8.15 Setting the Transmit Interrupt Mode

8.15.1 About the Transmitter Interrupt and the Associated Modes

8.16 Setting the Transmit Frame-Sync Mode

8.16.1 About the Transmit Frame-Sync Modes

8.16.2 Other Considerations

8.17 Setting the Transmit Frame-Sync Polarity

8.17.1 About Frame Sync Pulses, Clock Signals, and Their Polarities

8.18 Setting the SRG Frame-Sync Period and Pulse Width

8.18.1 About the Frame-Sync Period and the Frame-Sync Pulse Width

8.19 Setting the Transmit Clock Mode

8.19.1 Selecting a Source for the Transmit Clock and a Data Direction for the CLKX Pin

8.19.2 Other Considerations

8.20 Setting the Transmit Clock Polarity

8.20.1 About Frame Sync Pulses, Clock Signals, and Their Polarities

8.21 Setting the SRG Clock Divide-Down Value

8.21.1 About the Sample Rate Generator Clock Divider

8.22 Setting the SRG Clock Synchronization Mode

8.23 Setting the SRG Clock Mode (Choosing an Input Clock)

8.23.1 About the SRG Clock Mode

8.24 Setting the SRG Input Clock Polarity

8.24.1 Using CLKSP/CLKXP/CLKRP to Choose an Input Clock Polarity

Chapter 9: General-Purpose I/O on the McBSP Pins

9.1 Using the McBSP Pins for GPIO

Chapter 10: Emulation, Power, and Reset Considerations

10.1 McBSP Emulation Mode

10.2 McBSP Power Management on the TMS320VC5503/5507/5509 and TMS320VC5510 Devices

10.3 McBSP Power Management on the TMS320VC5501 and TMS320VC5502 Devices

10.4 Resetting and Initializing a McBSP

10.4.1 McBSP Pin States: DSP Reset Versus Receiver/Transmitter Reset

10.4.2 DSP Reset, McBSP Reset, and Sample Rate Generator Reset

10.4.3 McBSP Initialization Procedure

10.4.4 Resetting the Transmitter While the Receiver is Running

Chapter 11: Data Packing Examples

11.1 Data Packing Using Frame Length and Word Length

11.2 Data Packing Using Word Length and the Frame-Sync Ignore Function

Chapter 12: McBSP Registers

12.1 Data Receive Registers (DRR1 and DRR2)

12.1.1 How Data Travels From the Data Receive (DR) Pin to the DRRs

12.2 Data Transmit Registers (DXR1 and DXR2)

12.2.1 How Data Travels From the DXRs to the Data Transmit (DX) Pin

12.3 Serial Port Control Registers (SPCR1 and SPCR2)

12.4 Receive Control Registers (RCR1 and RCR2)

12.5 Transmit Control Registers (XCR1 and XCR2)

12.6 Sample Rate Generator Registers (SRGR1 and SRGR2)

12.7 Multichannel Control Registers (MCR1 and MCR2)

12.8 Pin Control Register (PCR)

12.9 Receive Channel Enable Registers (RCERA-RCERH)

12.9.1 RCERs Used in the Receive Multichannel Selection Mode

12.10 Transmit Channel Enable Registers (XCERA-XCERH)

12.10.1 XCERs Used in a Transmit Multichannel Selection Mode

Chapter 13: McBSP Register Worksheet

13.1 General Control Registers

13.2 Multichannel Selection Control Registers

Appendix A: Revision History

Index

A

B

C

D

E

F

G

H

I

J

K

L

M

N

O

P

R

S

T

U

W

X

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc