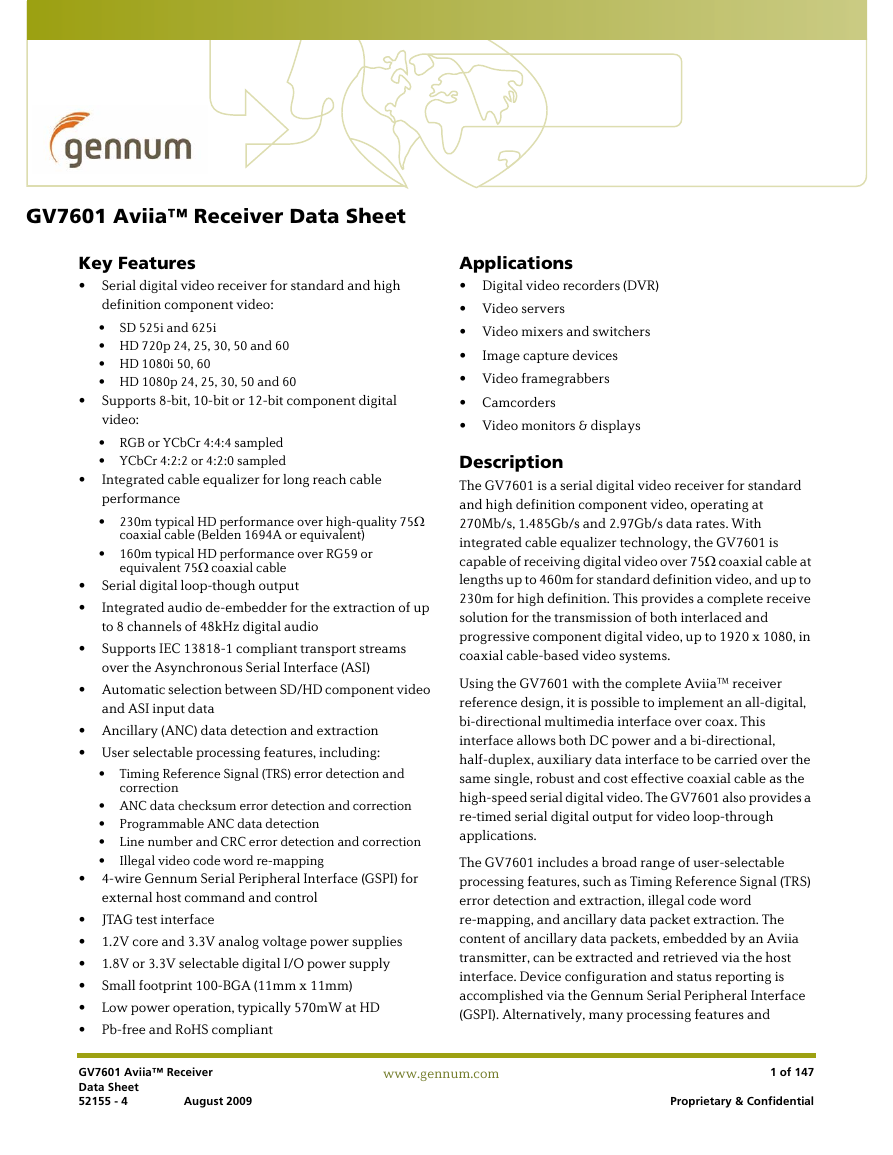

Key Features

Applications

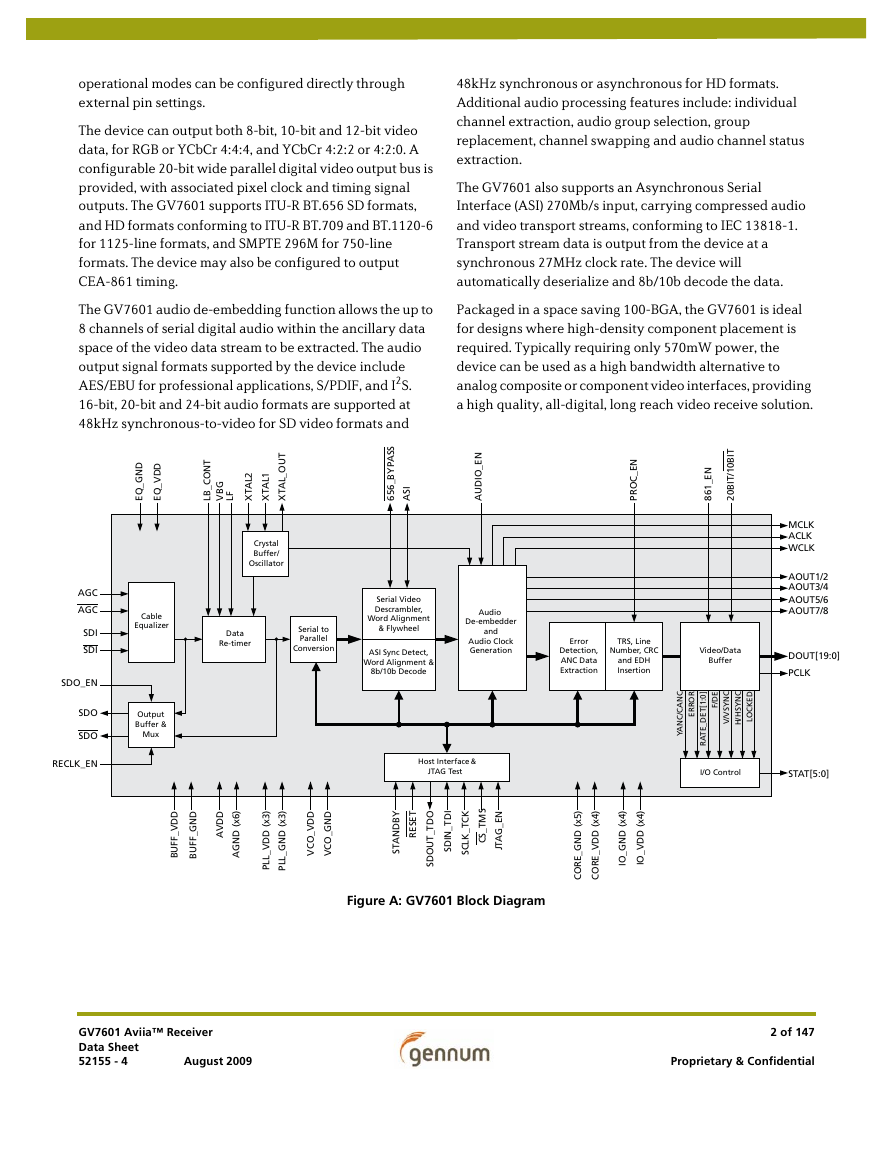

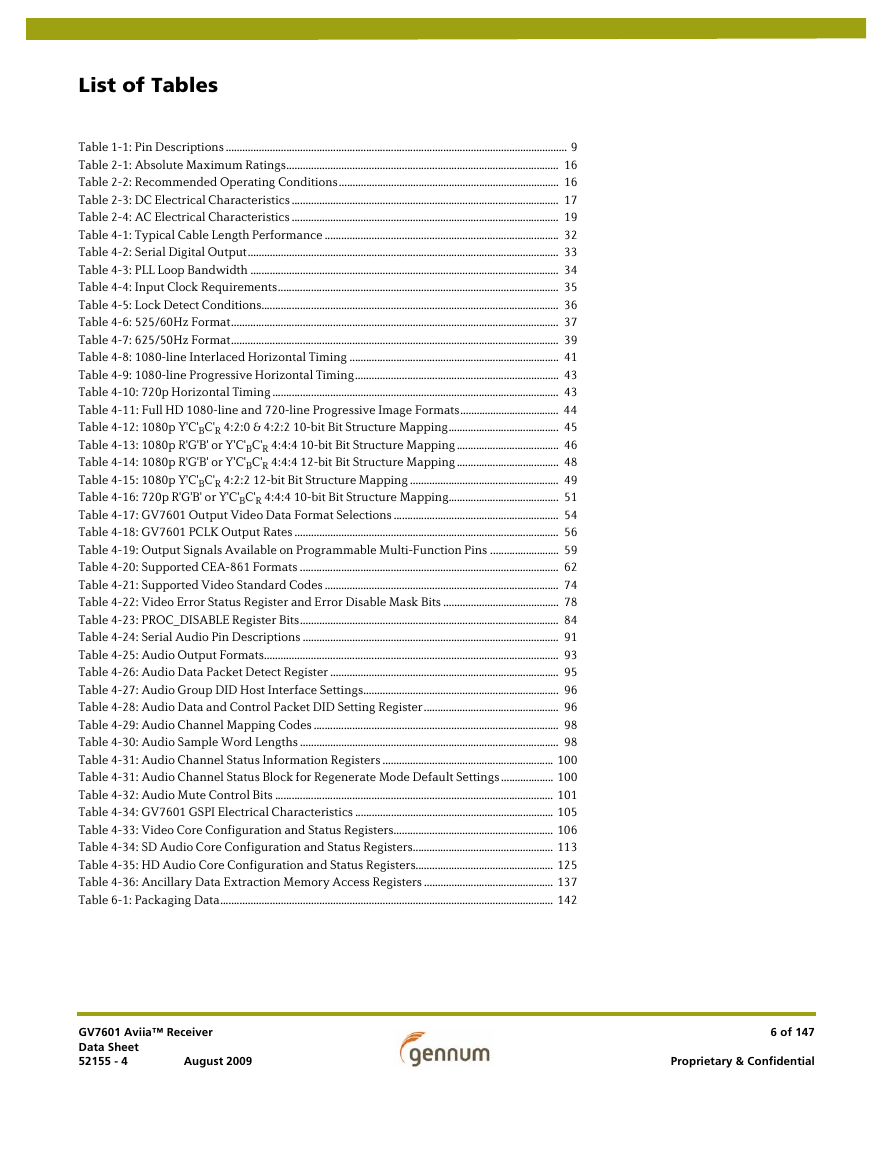

Description

1. Pin Out

1.1 Pin Assignment

1.2 Pin Descriptions

2. Electrical Characteristics

2.1 Absolute Maximum Ratings

2.2 Recommended Operating Conditions

2.3 DC Electrical Characteristics

2.4 AC Electrical Characteristics

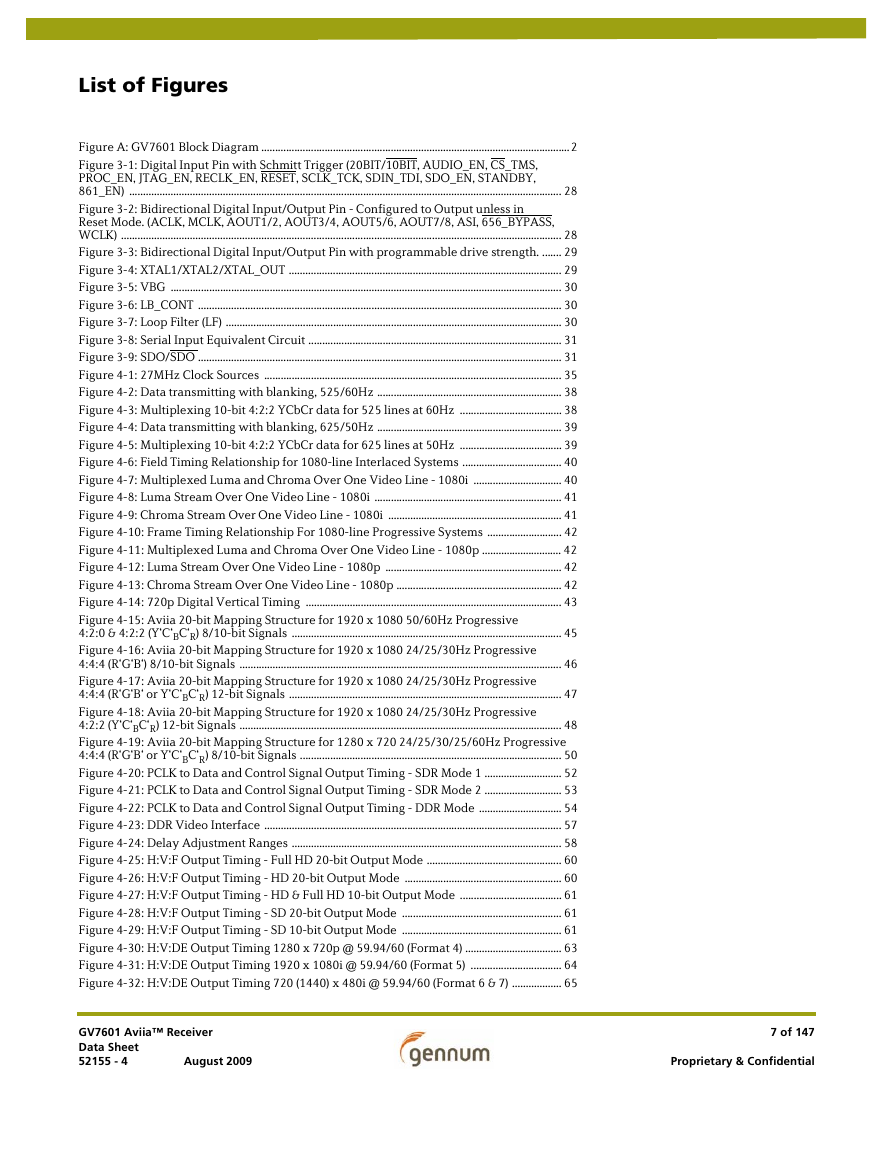

3. Input/Output Circuits

4. Detailed Description

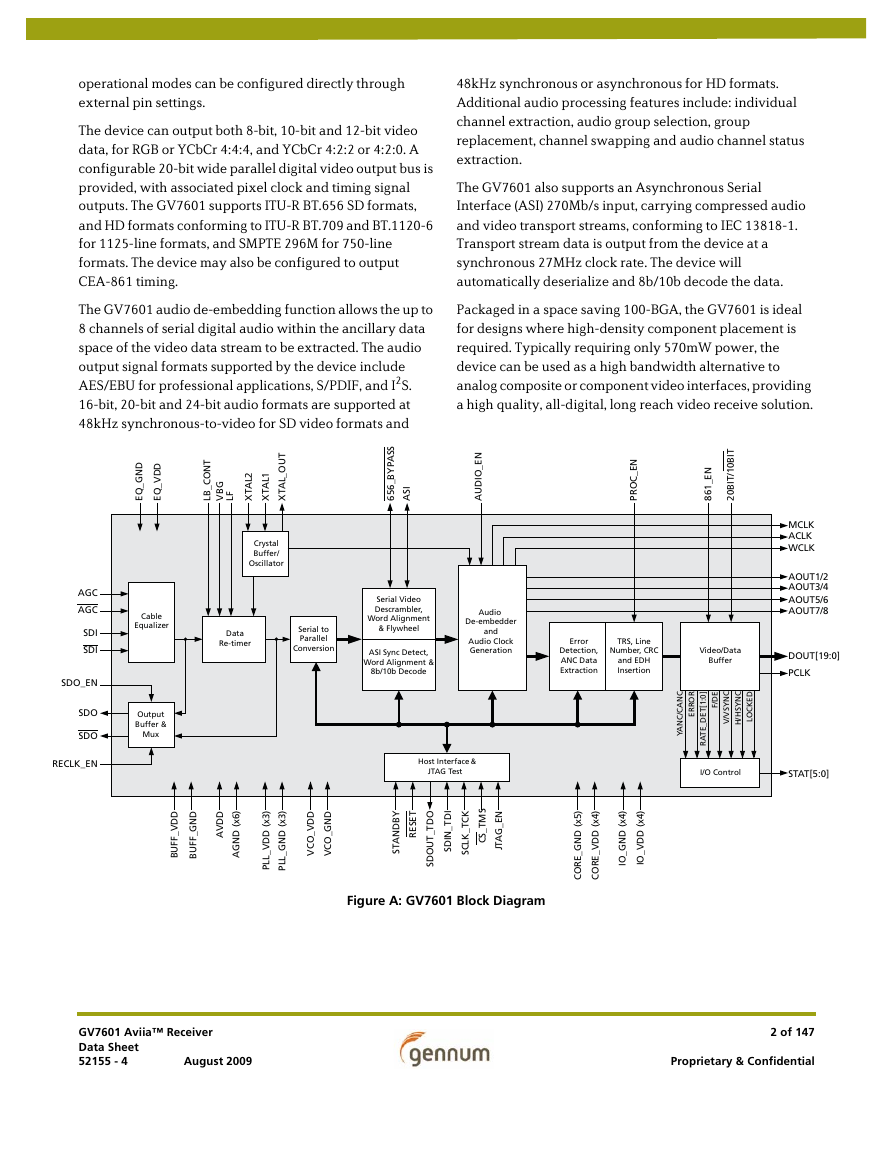

4.1 Functional Overview

4.2 Serial Digital Input

4.3 Serial Digital Output

4.4 Serial Digital Reclocker

4.4.1 Reclocker PLL Loop Bandwidth

4.5 External Crystal/Reference Clock

4.6 Lock Detect

4.6.1 Asynchronous Lock

4.6.2 Signal Interruption

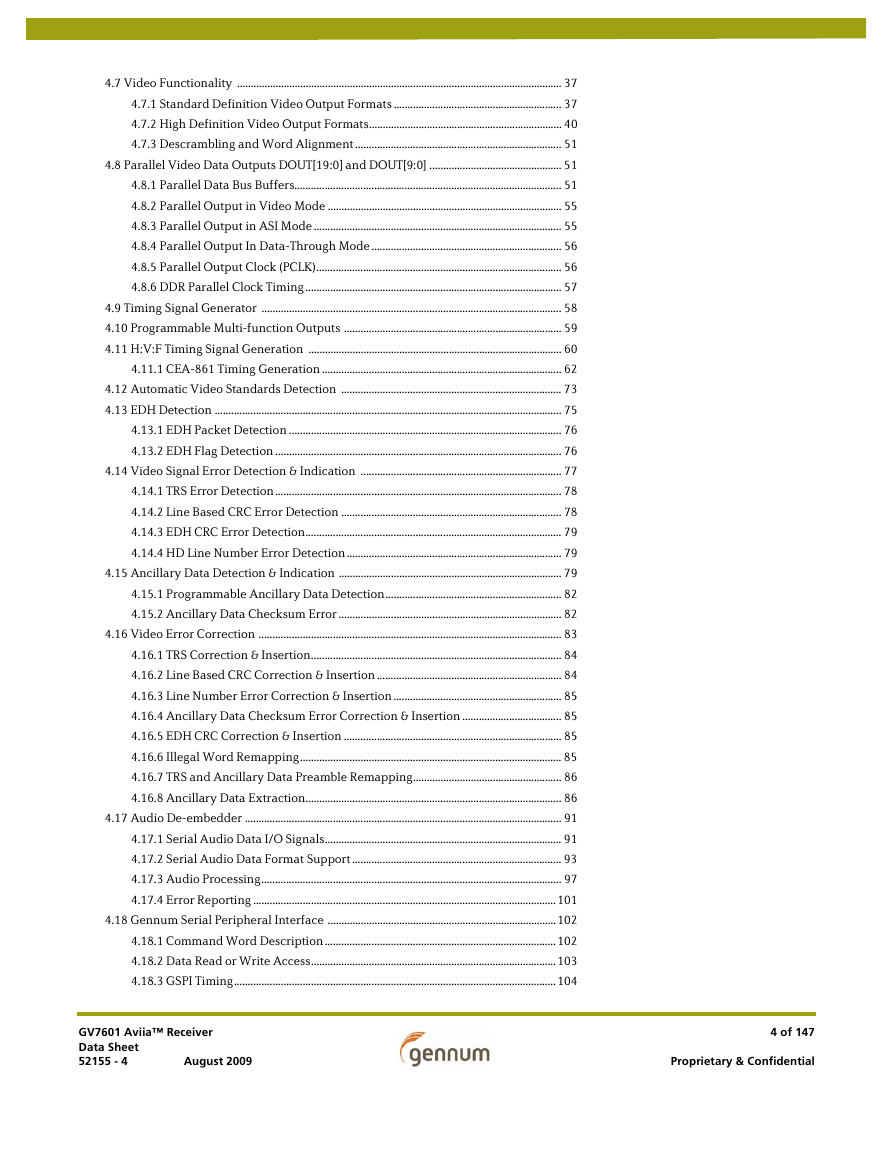

4.7 Video Functionality

4.7.1 Standard Definition Video Output Formats

4.7.2 High Definition Video Output Formats

4.7.3 Descrambling and Word Alignment

4.8 Parallel Video Data Outputs DOUT[19:0] and DOUT[9:0]

4.8.1 Parallel Data Bus Buffers

4.8.2 Parallel Output in Video Mode

4.8.3 Parallel Output in ASI Mode

4.8.4 Parallel Output In Data-Through Mode

4.8.5 Parallel Output Clock (PCLK)

4.8.6 DDR Parallel Clock Timing

4.9 Timing Signal Generator

4.10 Programmable Multi-function Outputs

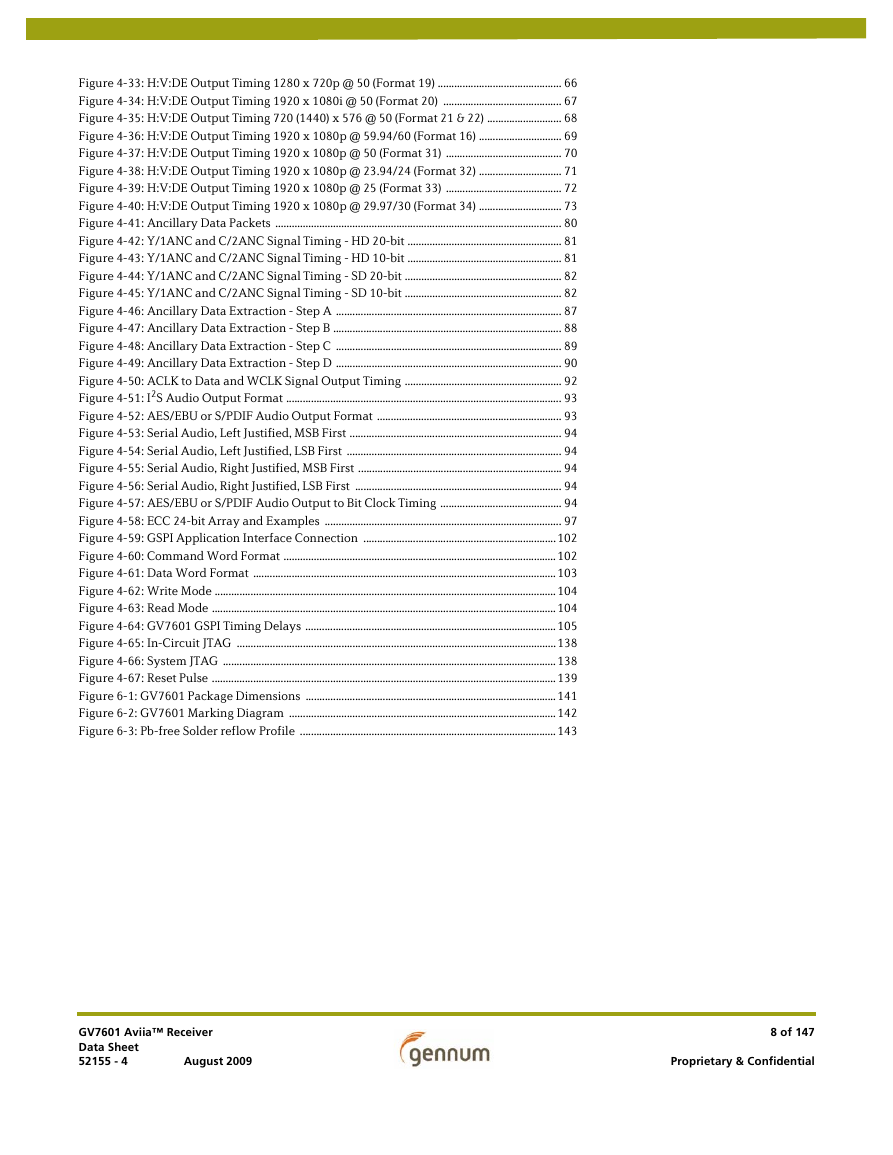

4.11 H:V:F Timing Signal Generation

4.11.1 CEA-861 Timing Generation

4.12 Automatic Video Standards Detection

4.13 EDH Detection

4.13.1 EDH Packet Detection

4.13.2 EDH Flag Detection

4.14 Video Signal Error Detection & Indication

4.14.1 TRS Error Detection

4.14.2 Line Based CRC Error Detection

4.14.3 EDH CRC Error Detection

4.14.4 HD Line Number Error Detection

4.15 Ancillary Data Detection & Indication

4.15.1 Programmable Ancillary Data Detection

4.15.2 Ancillary Data Checksum Error

4.16 Video Error Correction

4.16.1 TRS Correction & Insertion

4.16.2 Line Based CRC Correction & Insertion

4.16.3 Line Number Error Correction & Insertion

4.16.4 Ancillary Data Checksum Error Correction & Insertion

4.16.5 EDH CRC Correction & Insertion

4.16.6 Illegal Word Remapping

4.16.7 TRS and Ancillary Data Preamble Remapping

4.16.8 Ancillary Data Extraction

4.17 Audio De-embedder

4.17.1 Serial Audio Data I/O Signals

4.17.2 Serial Audio Data Format Support

4.17.3 Audio Processing

4.17.4 Error Reporting

4.18 Gennum Serial Peripheral Interface

4.18.1 Command Word Description

4.18.2 Data Read or Write Access

4.18.3 GSPI Timing

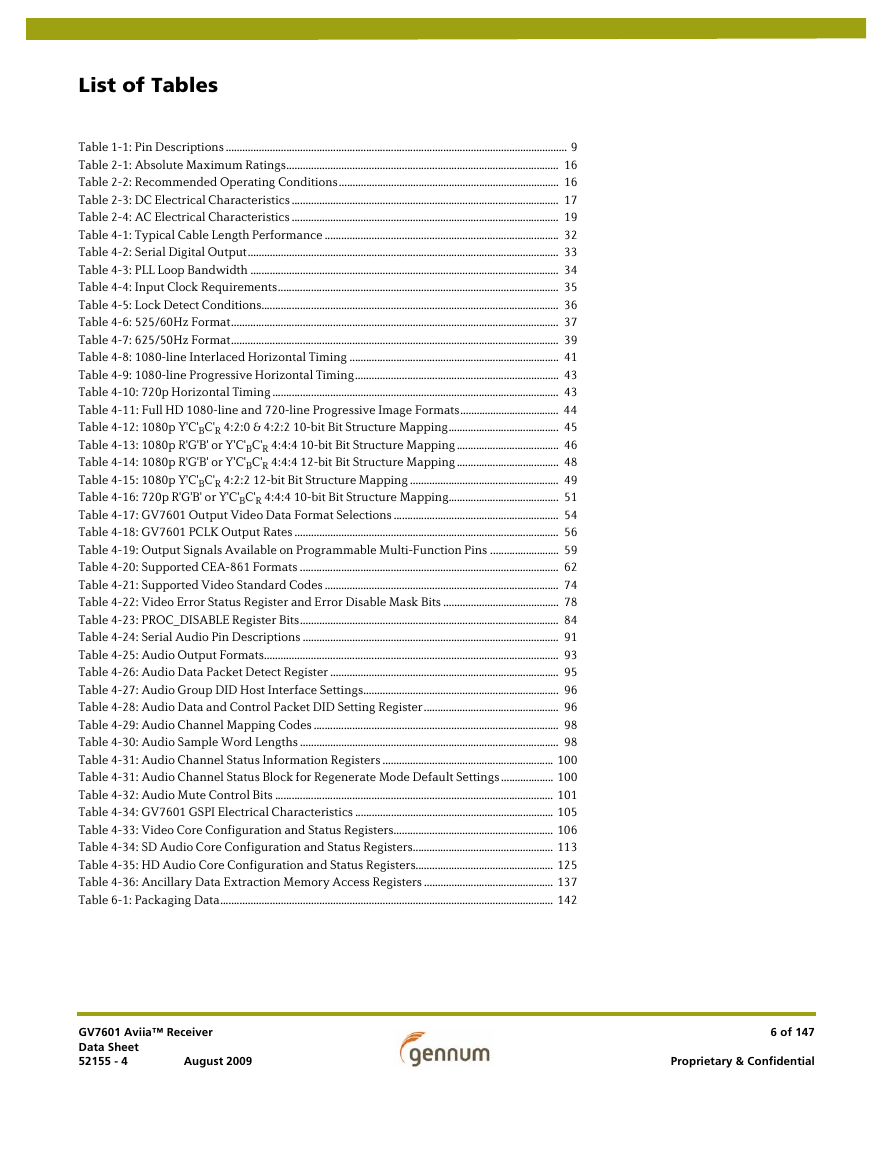

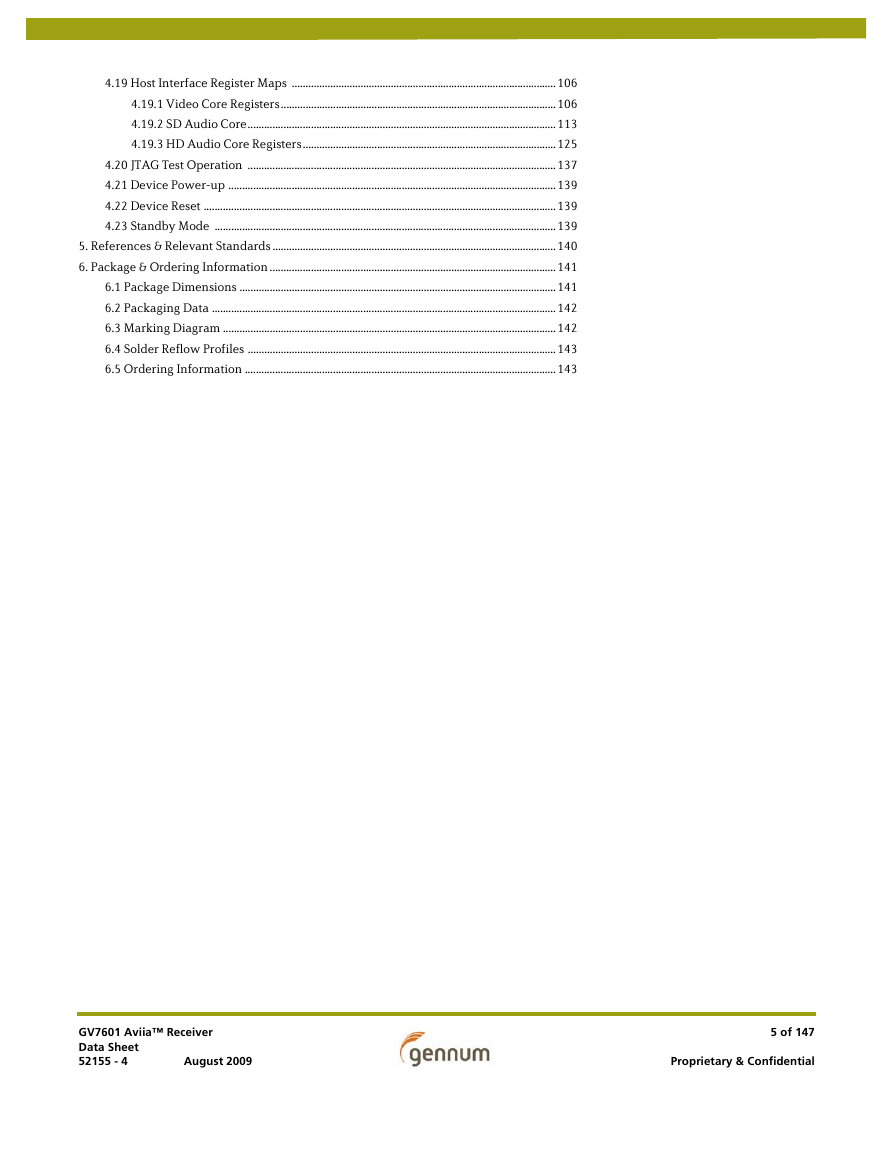

4.19 Host Interface Register Maps

4.19.1 Video Core Registers

4.19.2 SD Audio Core

4.19.3 HD Audio Core Registers

4.20 JTAG Test Operation

4.21 Device Power-up

4.22 Device Reset

4.23 Standby Mode

5. References & Relevant Standards

6. Package & Ordering Information

6.1 Package Dimensions

6.2 Packaging Data

6.3 Marking Diagram

6.4 Solder Reflow Profiles

6.5 Ordering Information

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc