AR0230CS: 1/2.7-Inch 2.1 Mp/Full HD Digital Image Sensor

Features

1/2.7-Inch 2.1 Mp/Full HD Digital Image Sensor

AR0230CS Datasheet, Rev. 8

For the latest datasheet, please visit www.onsemi.com

Features

• Superior low-light performance

Latest 3.0 m pixel with ON Semiconductor

DR-Pix™ technology with Dual Conversion Gain

Full HD support at up to 1080P 60 fps for superior

video performance

Linear or high dynamic range capture

Optional adaptive local tone mapping (ALTM)

Pixel or Line interleaved T1/T2 output

Support for external mechanical shutter

On-chip phase-locked loop (PLL) oscillator

Integrated position-based color and lens shading

correction

Slave mode for precise frame-rate control

Stereo/3D camera support

Statistics engine

Data interfaces: four-lane serial high-speed pixel

interface (HiSPi) differential signaling (SLVS and

HiVCM), or parallel

Auto black level calibration

High-speed configurable context switching

Temperature sensor

Applications

Video surveillance

1080p60 (Surveillance) video applications

High dynamic range imaging

General Description

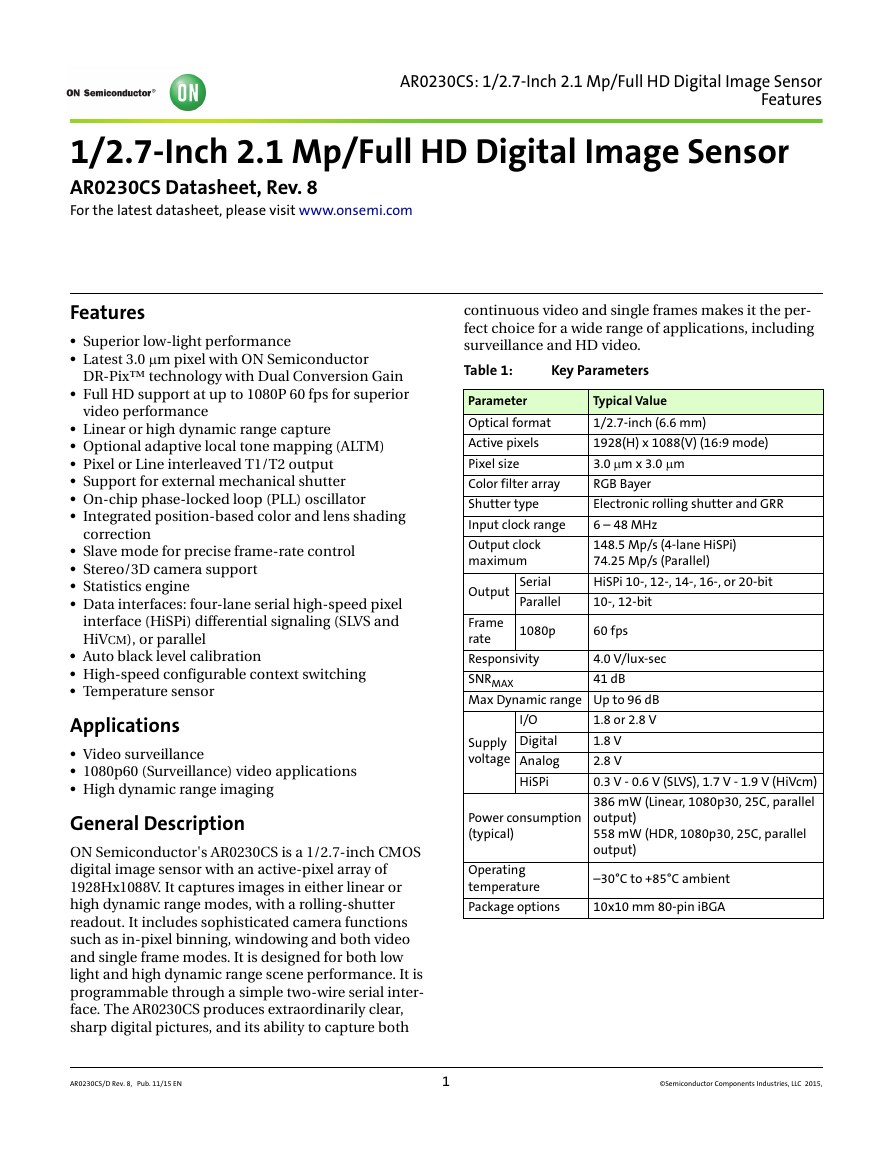

ON Semiconductor's AR0230CS is a 1/2.7-inch CMOS

digital image sensor with an active-pixel array of

1928Hx1088V. It captures images in either linear or

high dynamic range modes, with a rolling-shutter

readout. It includes sophisticated camera functions

such as in-pixel binning, windowing and both video

and single frame modes. It is designed for both low

light and high dynamic range scene performance. It is

programmable through a simple two-wire serial inter-

face. The AR0230CS produces extraordinarily clear,

sharp digital pictures, and its ability to capture both

continuous video and single frames makes it the per-

fect choice for a wide range of applications, including

surveillance and HD video.

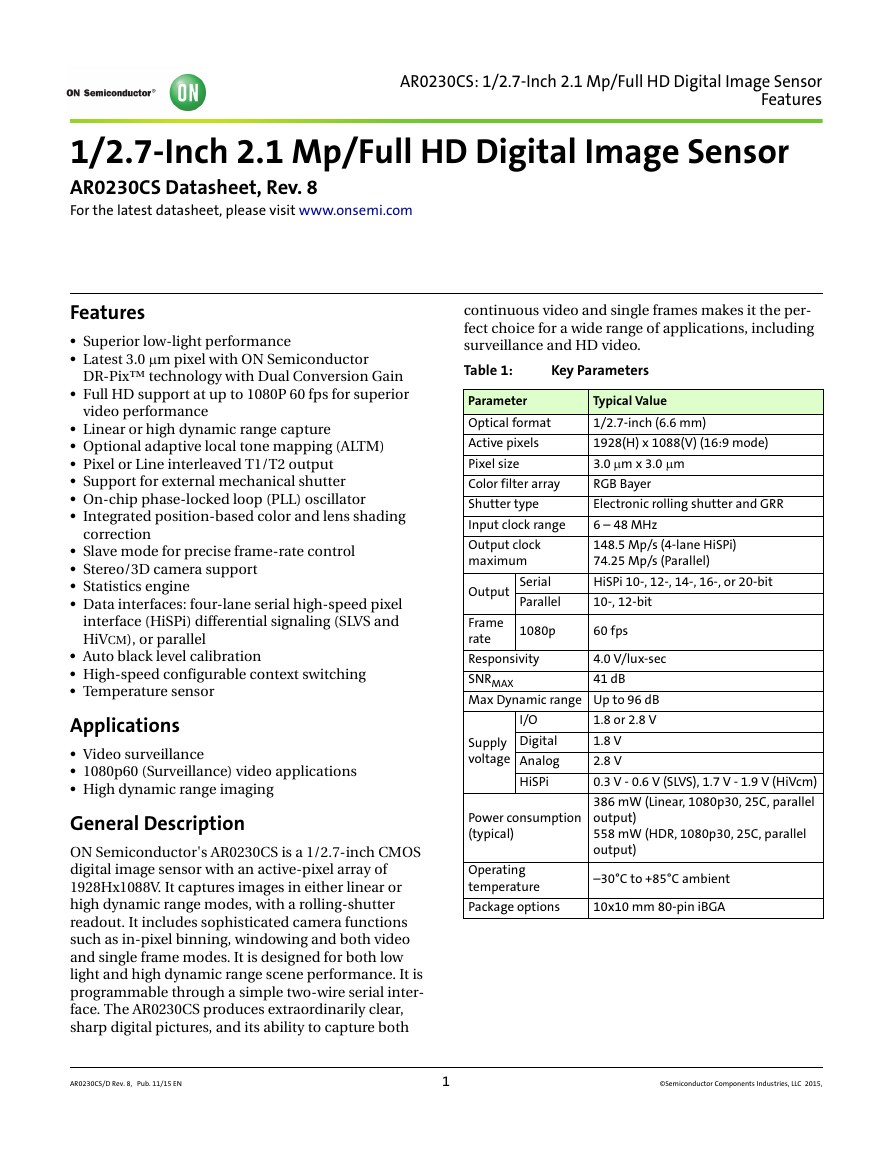

Table 1:

Key Parameters

Parameter

Optical format

Active pixels

Pixel size

Color filter array

Shutter type

Input clock range

Output clock

maximum

Output

Serial

Parallel

Typical Value

1/2.7-inch (6.6 mm)

1928(H) x 1088(V) (16:9 mode)

3.0 m x 3.0m

RGB Bayer

Electronic rolling shutter and GRR

6 – 48 MHz

148.5 Mp/s (4-lane HiSPi)

74.25 Mp/s (Parallel)

HiSPi 10-, 12-, 14-, 16-, or 20-bit

10-, 12-bit

1080p

60 fps

4.0 V/lux-sec

41 dB

Frame

rate

Responsivity

SNRMAX

Max Dynamic range Up to 96 dB

1.8 or 2.8 V

1.8 V

2.8 V

0.3 V - 0.6 V (SLVS), 1.7 V - 1.9 V (HiVcm)

386 mW (Linear, 1080p30, 25C, parallel

output)

558 mW (HDR, 1080p30, 25C, parallel

output)

Power consumption

(typical)

I/O

Digital

Analog

HiSPi

Supply

voltage

Operating

temperature

Package options

–30°C to +85°C ambient

10x10 mm 80-pin iBGA

AR0230CS/D Rev. 8, Pub. 11/15 EN

1

©Semiconductor Components Industries, LLC 2015,

�

AR0230CS: 1/2.7-Inch 2.1 Mp/Full HD Digital Image Sensor

Ordering Information

Ordering Information

Table 2:

Available Part Numbers

Part Number

AR0230CSSC00SUEA0-DRBR

AR0230CSSC00SUEAD3-GEVK

AR0230CSSC00SUEAH3-GEVB

AR0230CSSC12SUEA0-DR

AR0230CSSC12SUEAD3-GEVK

AR0230CSSC12SUEAH3-GEVB

Product Description

2 Mp 1/3" CIS RGB, 0deg CRA, iBGA Package

RGB, 0deg CRA, Demo Kit

RGB, 0deg CRA, Headboard

2 Mp 1/3" CIS RGB, 12deg CRA, iBGA Package

RGB, 12deg CRA, Demo Kit

RGB, 12deg CRA, Headboard

Orderable Product Attribute Description

Drypack, Anti-Reflective Glass

Demo Kit

Headboard

Drypack

Demo Kit

Headboard

See the ON Semiconductor Device Nomenclature document (TND310/D) for a full

description of the naming convention used for image sensors. For reference documenta-

tion, including information on evaluation kits, please visit our web site at

www.onsemi.com.

AR0230CS/D Rev. 8, Pub. 11/15 EN

2

©Semiconductor Components Industries, LLC, 2015.

�

AR0230CS: 1/2.7-Inch 2.1 Mp/Full HD Digital Image Sensor

Table of Contents

Table of Contents

Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Functional Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Pixel Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Features Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Electrical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Power-On Reset and Standby Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Package Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

AR0230CS/D Rev. 8, Pub. 11/15 EN

3

©Semiconductor Components Industries, LLC, 2015.

�

AR0230CS: 1/2.7-Inch 2.1 Mp/Full HD Digital Image Sensor

List of Figures

List of Figures

Figure 1:

Figure 2:

Figure 3:

Figure 4:

Figure 5:

Figure 6:

Figure 7:

Figure 8:

Figure 9:

Figure 10:

Figure 11:

Figure 12:

Figure 13:

Block Diagram of AR0230CS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Typical Configuration: Serial Four-Lane HiSPi Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Typical Configuration: Parallel Pixel Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

80-Ball IBGA Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Pixel Array Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Pixel Color Pattern Detail (Top Right Corner) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Imaging a Scene . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Quantum Efficiency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Two-Wire Serial Bus Timing Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

I/O Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Power Up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Power Down. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

80iBGA 10 x 10 Package Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

AR0230CS/D Rev. 8, Pub. 11/15 EN

4

©Semiconductor Components Industries, LLC, 2015.

�

AR0230CS: 1/2.7-Inch 2.1 Mp/Full HD Digital Image Sensor

List of Tables

List of Tables

Table 1:

Table 2:

Table 3:

Table 4:

Table 5:

Table 6:

Table 7:

Table 8:

Table 9:

Table 10:

Table 11:

Table 12:

Table 13:

Table 14:

Table 15:

Table 16:

Table 17:

Table 18:

Table 19:

Table 20:

Table 21:

Key Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Available Part Numbers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

Pin Descriptions, 80-ball iBGA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

List of Configurable Registers for Context A and Context B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Two-Wire Serial Bus Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

I/O Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

1080p30 HDR (ALTM) 74MHz Parallel 2.8V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

1080p30 Linear 74MHz Parallel 2.8V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

1080p30 HDR (ALTM) 74MHz Parallel 1.8V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

1080p30 Linear 74 MHz Parallel 1.8V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

1080p30 HDR (ALTM) 74 MHz HiSPi SLVS (Low Power Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

1080p30 Linear 74 MHz HiSPi SLVS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

1080p30 HDR (ALTM) 74 MHz HiSPi HiVcm (Low Power Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

1080p30 Linear 74 MHz HiSPi HiVcm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Line Interleaved HiSPi SLVS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Line Interleaved HiSPi HiVcm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Channel Skew . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Power-Up Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Power-Down Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

AR0230CS/D Rev. 8, Pub. 11/15 EN

5

©Semiconductor Components Industries, LLC, 2015.

�

AR0230CS: 1/2.7-Inch 2.1 Mp/Full HD Digital Image Sensor

General Description

General Description

The ON Semiconductor AR0230CS can be operated in its default mode or programmed

for frame size, exposure, gain, and other parameters. The default mode output is a

1080p-resolution image at 60 frames per second (fps) through the HiSPi port. In linear

mode, it outputs 12-bit or 10-bit A-Law compressed raw data, using either the parallel or

serial (HiSPi) output ports. In high dynamic range mode, it outputs 12-bit compressed

data using parallel output. In HiSPi mode, 12- or 14-bit compressed, or 16-bit linearized

data may be output. The device may be operated in video (master) mode or in single

frame trigger mode.

FRAME_VALID and LINE_VALID signals are output on dedicated pins, along with a

synchronized pixel clock in parallel mode.

The AR0230CS includes additional features to allow application-specific tuning:

windowing and offset, auto black level correction, and on-board temperature sensor.

Optional register information and histogram statistic information can be embedded in

the first and last 2 lines of the image frame.

The AR0230CS is designed to operate over a wide temperature range of -30°C to +85°C

ambient.

AR0230CS/D Rev. 8, Pub. 11/15 EN

6

©Semiconductor Components Industries, LLC, 2015.

�

AR0230CS: 1/2.7-Inch 2.1 Mp/Full HD Digital Image Sensor

Functional Overview

Functional Overview

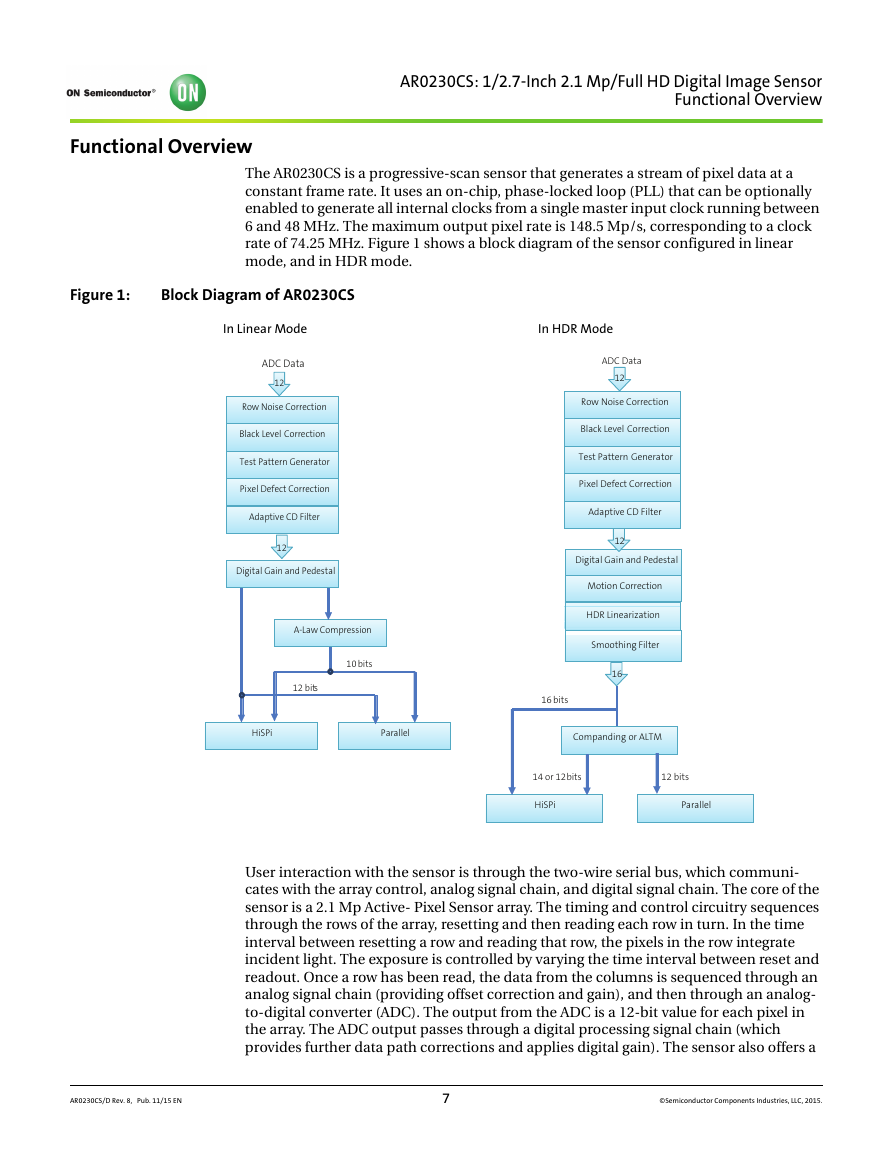

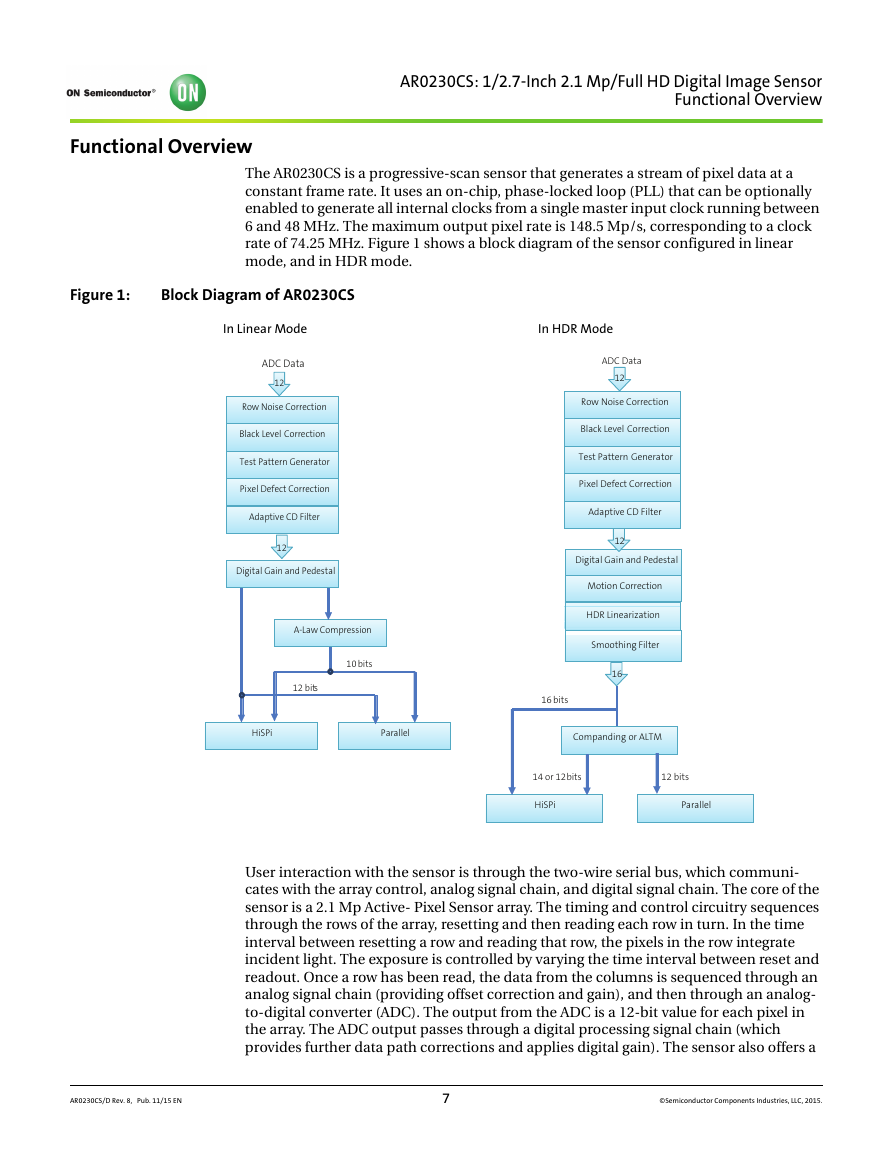

The AR0230CS is a progressive-scan sensor that generates a stream of pixel data at a

constant frame rate. It uses an on-chip, phase-locked loop (PLL) that can be optionally

enabled to generate all internal clocks from a single master input clock running between

6 and 48 MHz. The maximum output pixel rate is 148.5 Mp/s, corresponding to a clock

rate of 74.25 MHz. Figure 1 shows a block diagram of the sensor configured in linear

mode, and in HDR mode.

Figure 1:

Block Diagram of AR0230CS

In Linear Mode

In HDR Mode

ADC Data

12

Row Noise Correction

Black Level Correction

Test Pattern Generator

Pixel Defect Correction

Adaptive CD Filter

12

Digital Gain and Pedestal

A-Law Compression

10 bits

12 bits

ADC Data

12

Row Noise Correction

Black Level Correction

Test Pattern Generator

Pixel Defect Correction

Adaptive CD Filter

12

Digital Gain and Pedestal

Motion Correction

HDR Linearization

HDR Linearization

Smoothing Filter

16

HiSPi

Parallel

Companding or ALTM

16 bits

14 or 12 bits

12 bits

HiSPi

Parallel

User interaction with the sensor is through the two-wire serial bus, which communi-

cates with the array control, analog signal chain, and digital signal chain. The core of the

sensor is a 2.1 Mp Active- Pixel Sensor array. The timing and control circuitry sequences

through the rows of the array, resetting and then reading each row in turn. In the time

interval between resetting a row and reading that row, the pixels in the row integrate

incident light. The exposure is controlled by varying the time interval between reset and

readout. Once a row has been read, the data from the columns is sequenced through an

analog signal chain (providing offset correction and gain), and then through an analog-

to-digital converter (ADC). The output from the ADC is a 12-bit value for each pixel in

the array. The ADC output passes through a digital processing signal chain (which

provides further data path corrections and applies digital gain). The sensor also offers a

AR0230CS/D Rev. 8, Pub. 11/15 EN

7

©Semiconductor Components Industries, LLC, 2015.

�

AR0230CS: 1/2.7-Inch 2.1 Mp/Full HD Digital Image Sensor

Functional Overview

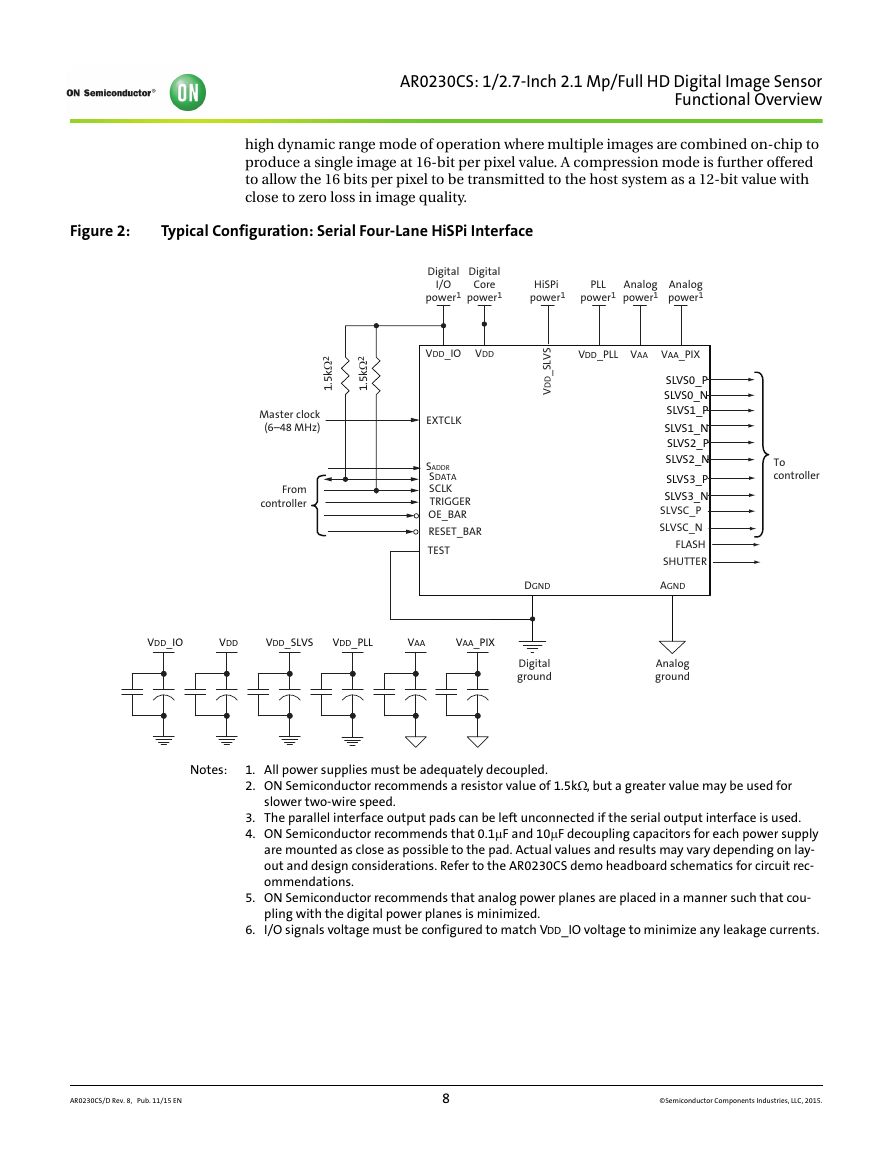

high dynamic range mode of operation where multiple images are combined on-chip to

produce a single image at 16-bit per pixel value. A compression mode is further offered

to allow the 16 bits per pixel to be transmitted to the host system as a 12-bit value with

close to zero loss in image quality.

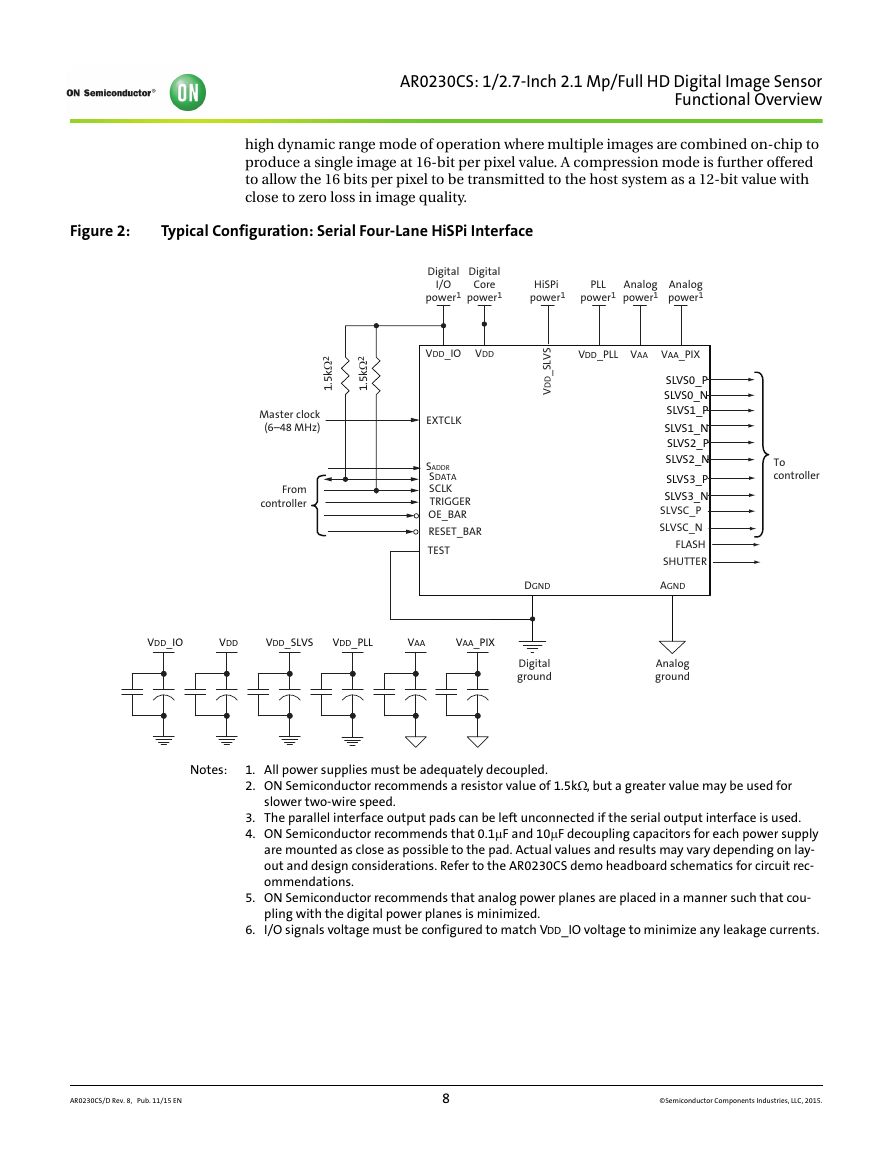

Figure 2:

Typical Configuration: Serial Four-Lane HiSPi Interface

Digital

I/O

power1

Digital

Core

power1

HiSPi

power1

PLL

power1

Analog

power1

Analog

power1

2

Ω

k

5

1

.

2

Ω

k

5

1

.

VDD_IO

VDD

S

V

L

S

_

D

D

V

Master clock

(6–48 MHz)

From

controller

EXTCLK

SADDR

SDATA

SCLK

TRIGGER

OE_BAR

RESET_BAR

TEST

VDD_PLL

VAA VAA_PIX

SLVS0_P

SLVS0_N

SLVS1_P

SLVS1_N

SLVS2_P

SLVS2_N

SLVS3_P

SLVS3_N

SLVSC_P

SLVSC_N

FLASH

SHUTTER

To

controller

VDD_IO

VDD

VDD_SLVS

VDD_PLL

VAA

VAA_PIX

DGND

AGND

Digital

ground

Analog

ground

Notes:

1. All power supplies must be adequately decoupled.

2. ON Semiconductor recommends a resistor value of 1.5k, but a greater value may be used for

slower two-wire speed.

3. The parallel interface output pads can be left unconnected if the serial output interface is used.

4. ON Semiconductor recommends that 0.1F and 10F decoupling capacitors for each power supply

are mounted as close as possible to the pad. Actual values and results may vary depending on lay-

out and design considerations. Refer to the AR0230CS demo headboard schematics for circuit rec-

ommendations.

5. ON Semiconductor recommends that analog power planes are placed in a manner such that cou-

pling with the digital power planes is minimized.

I/O signals voltage must be configured to match VDD_IO voltage to minimize any leakage currents.

6.

AR0230CS/D Rev. 8, Pub. 11/15 EN

8

©Semiconductor Components Industries, LLC, 2015.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc