Vivado Design Suite User

Guide

See all versions

of this document

High-Level Synthesis

UG902 (v2019.2) January 13, 2020

�

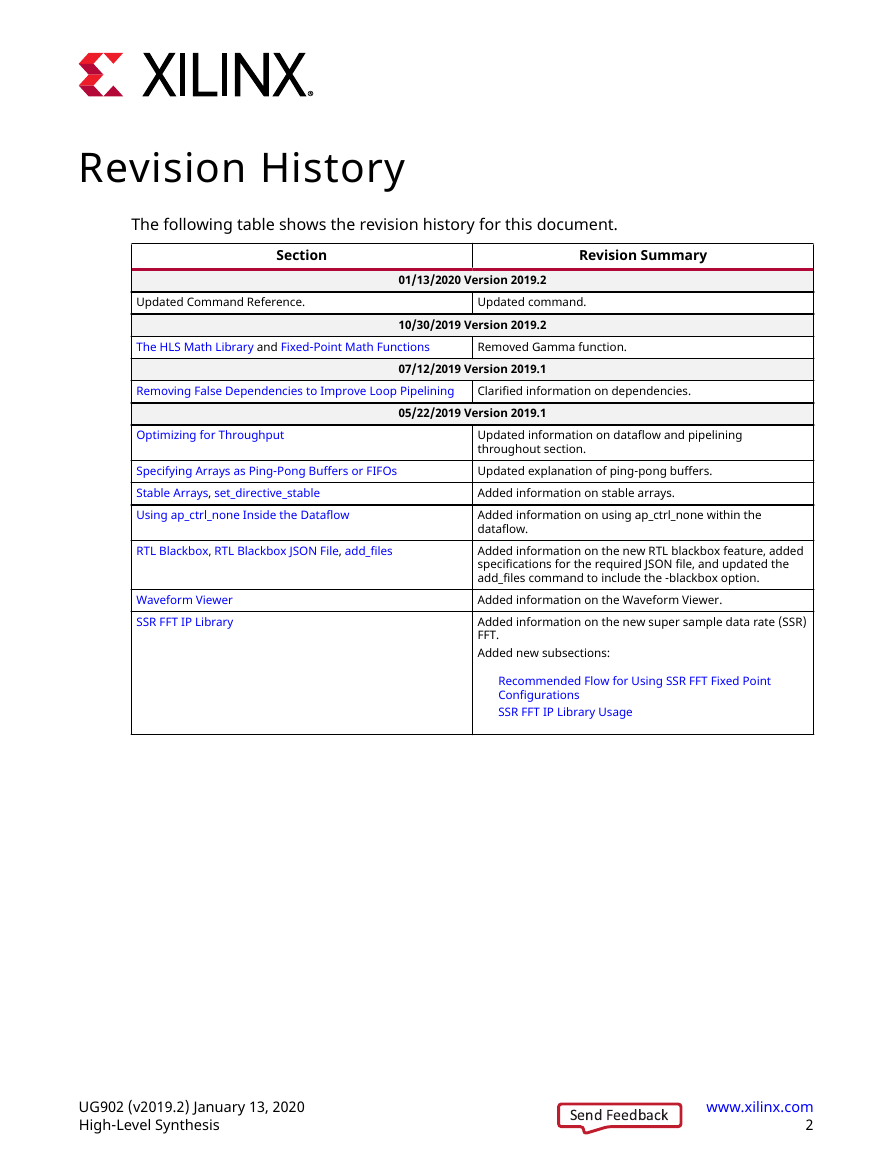

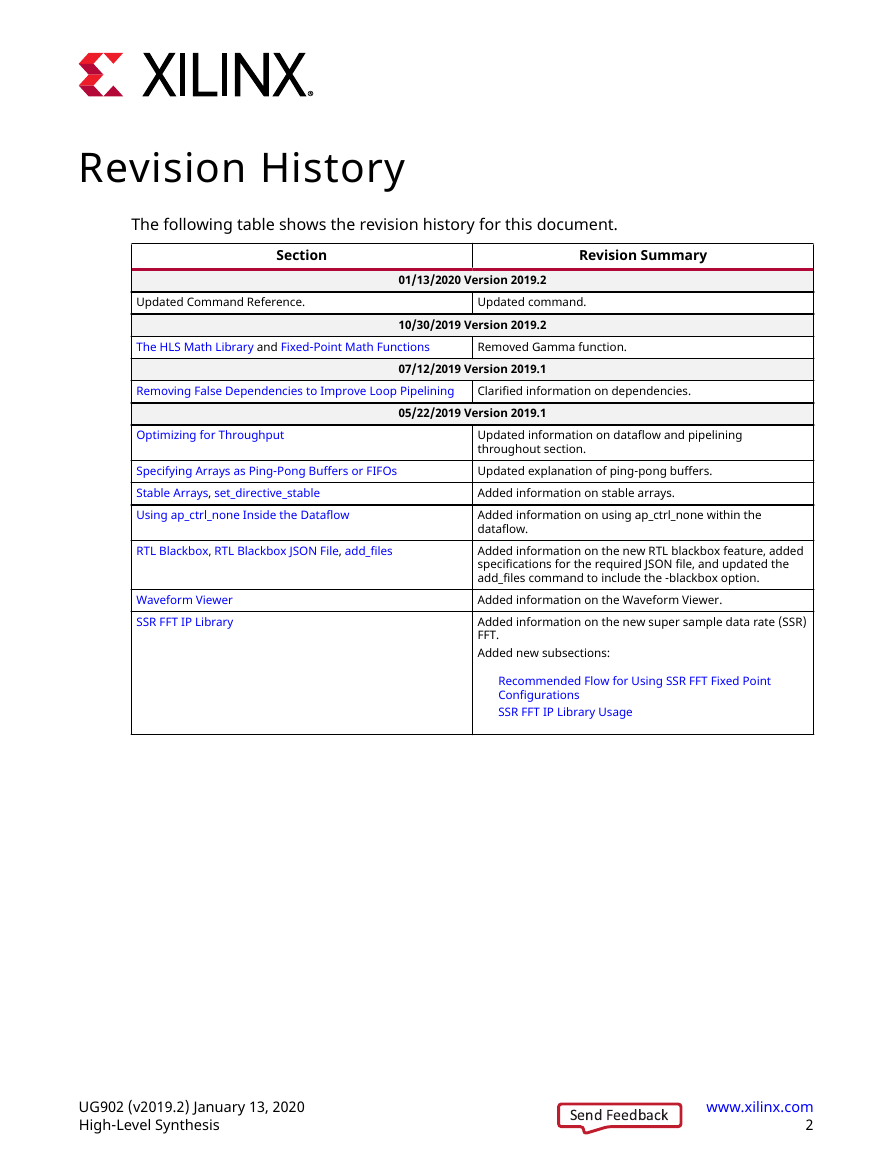

Revision History

Revision History

The following table shows the revision history for this document.

Section

Revision Summary

01/13/2020 Version 2019.2

Updated Command Reference.

Updated command.

10/30/2019 Version 2019.2

The HLS Math Library and Fixed-Point Math Functions

Removed Gamma function.

07/12/2019 Version 2019.1

Removing False Dependencies to Improve Loop Pipelining

Clarified information on dependencies.

05/22/2019 Version 2019.1

Optimizing for Throughput

Specifying Arrays as Ping-Pong Buffers or FIFOs

Stable Arrays, set_directive_stable

Using ap_ctrl_none Inside the Dataflow

RTL Blackbox, RTL Blackbox JSON File, add_files

Waveform Viewer

SSR FFT IP Library

Updated information on dataflow and pipelining

throughout section.

Updated explanation of ping-pong buffers.

Added information on stable arrays.

Added information on using ap_ctrl_none within the

dataflow.

Added information on the new RTL blackbox feature, added

specifications for the required JSON file, and updated the

add_files command to include the -blackbox option.

Added information on the Waveform Viewer.

Added information on the new super sample data rate (SSR)

FFT.

Added new subsections:

Recommended Flow for Using SSR FFT Fixed Point

Configurations

SSR FFT IP Library Usage

UG902 (v2019.2) January 13, 2020

High-Level Synthesis

www.xilinx.com

2

Send Feedback�

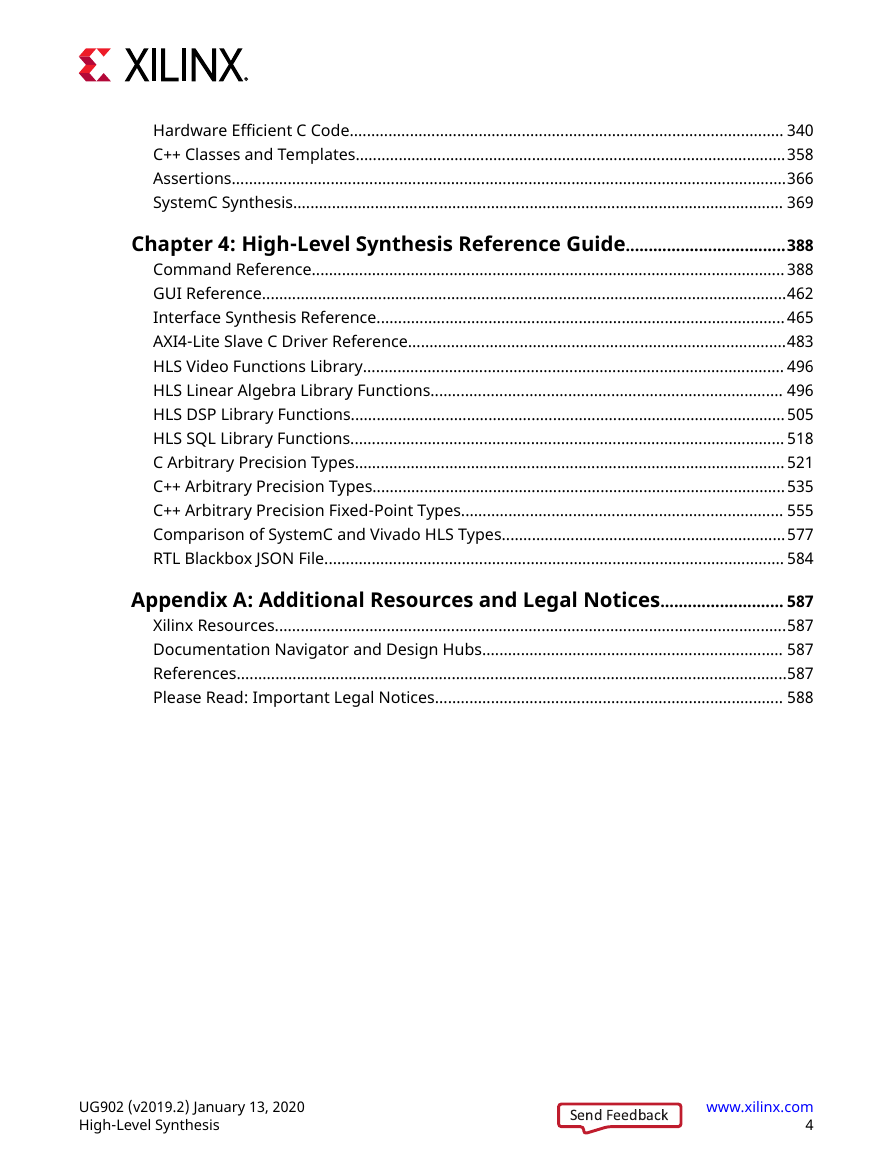

Table of Contents

Revision History...............................................................................................................2

Chapter 1: High-Level Synthesis............................................................................ 5

High-Level Synthesis Benefits....................................................................................................5

High-Level Synthesis Basics....................................................................................................... 6

Understanding Vivado HLS...................................................................................................... 12

Using Vivado HLS...................................................................................................................... 19

Data Types for Efficient Hardware.......................................................................................... 71

Managing Interfaces.................................................................................................................77

Optimizing the Design............................................................................................................118

Verifying the RTL..................................................................................................................... 177

Exporting the RTL Design.......................................................................................................191

Chapter 2: High-Level Synthesis C Libraries................................................198

Arbitrary Precision Data Types Library.................................................................................198

HLS Stream Library................................................................................................................. 213

HLS Math Library.....................................................................................................................222

HLS Video Library.................................................................................................................... 232

HLS IP Libraries........................................................................................................................232

HLS Linear Algebra Library.................................................................................................... 264

HLS DSP Library.......................................................................................................................275

HLS SQL Library....................................................................................................................... 277

Chapter 3: High-Level Synthesis Coding Styles..........................................279

Unsupported C Constructs.....................................................................................................279

C Test Bench.............................................................................................................................283

Functions..................................................................................................................................290

RTL Blackbox............................................................................................................................292

Loops........................................................................................................................................ 297

Arrays........................................................................................................................................305

Data Types................................................................................................................................314

C Builtin Functions.................................................................................................................. 339

UG902 (v2019.2) January 13, 2020

High-Level Synthesis

www.xilinx.com

3

Send Feedback�

Hardware Efficient C Code..................................................................................................... 340

C++ Classes and Templates....................................................................................................358

Assertions.................................................................................................................................366

SystemC Synthesis.................................................................................................................. 369

Chapter 4: High-Level Synthesis Reference Guide...................................388

Command Reference.............................................................................................................. 388

GUI Reference..........................................................................................................................462

Interface Synthesis Reference............................................................................................... 465

AXI4-Lite Slave C Driver Reference........................................................................................483

HLS Video Functions Library.................................................................................................. 496

HLS Linear Algebra Library Functions.................................................................................. 496

HLS DSP Library Functions.....................................................................................................505

HLS SQL Library Functions..................................................................................................... 518

C Arbitrary Precision Types.................................................................................................... 521

C++ Arbitrary Precision Types................................................................................................535

C++ Arbitrary Precision Fixed-Point Types........................................................................... 555

Comparison of SystemC and Vivado HLS Types..................................................................577

RTL Blackbox JSON File........................................................................................................... 584

Appendix A: Additional Resources and Legal Notices........................... 587

Xilinx Resources.......................................................................................................................587

Documentation Navigator and Design Hubs...................................................................... 587

References................................................................................................................................587

Please Read: Important Legal Notices................................................................................. 588

UG902 (v2019.2) January 13, 2020

High-Level Synthesis

www.xilinx.com

4

Send Feedback�

Chapter 1

High-Level Synthesis

The Xilinx® Vivado® High-Level Synthesis (HLS) tool transforms a C specification into a register

transfer level (RTL) implementation that you can synthesize into a Xilinx field programmable gate

array (FPGA). You can write C specifications in C, C++, or SystemC, and the FPGA provides a

massively parallel architecture with benefits in performance, cost, and power over traditional

processors. This chapter provides an overview of high-level synthesis.

Note: For more information on FPGA architectures and Vivado HLS basic concepts, see the Introduction to

FPGA Design Using High-Level Synthesis (UG998).

High-Level Synthesis Benefits

High-level synthesis bridges hardware and software domains, providing the following primary

benefits:

• Improved productivity for hardware designers

Hardware designers can work at a higher level of abstraction while creating high-performance

hardware.

• Improved system performance for software designers

Software developers can accelerate the computationally intensive parts of their algorithms on

a new compilation target, the FPGA.

Using a high-level synthesis design methodology allows you to:

• Develop algorithms at the C-level

Work at a level that is abstract from the implementation details, which consume development

time.

• Verify at the C-level

Validate the functional correctness of the design more quickly than with traditional hardware

description languages.

• Control the C synthesis process through optimization directives

Create specific high-performance hardware implementations.

• Create multiple implementations from the C source code using optimization directives

UG902 (v2019.2) January 13, 2020

High-Level Synthesis

www.xilinx.com

5

Send Feedback�

Chapter 1: High-Level Synthesis

Explore the design space, which increases the likelihood of finding an optimal implementation.

• Create readable and portable C source code

Retarget the C source into different devices as well as incorporate the C source into new

projects.

High-Level Synthesis Basics

High-level synthesis includes the following phases:

• Scheduling

Determines which operations occur during each clock cycle based on:

Length of the clock cycle or clock frequency

•

• Time it takes for the operation to complete, as defined by the target device

• User-specified optimization directives

If the clock period is longer or a faster FPGA is targeted, more operations are completed

within a single clock cycle, and all operations might complete in one clock cycle. Conversely, if

the clock period is shorter or a slower FPGA is targeted, high-level synthesis automatically

schedules the operations over more clock cycles, and some operations might need to be

implemented as multicycle resources.

• Binding

Determines which hardware resource implements each scheduled operation. To implement

the optimal solution, high-level synthesis uses information about the target device.

• Control logic extraction

Extracts the control logic to create a finite state machine (FSM) that sequences the operations

in the RTL design.

High-level synthesis synthesizes the C code as follows:

• Top-level function arguments synthesize into RTL I/O ports

• C functions synthesize into blocks in the RTL hierarchy

If the C code includes a hierarchy of sub-functions, the final RTL design includes a hierarchy of

modules or entities that have a one-to-one correspondence with the original C function

hierarchy. All instances of a function use the same RTL implementation or block.

• Loops in the C functions are kept rolled by default

UG902 (v2019.2) January 13, 2020

High-Level Synthesis

www.xilinx.com

6

Send Feedback�

Chapter 1: High-Level Synthesis

When loops are rolled, synthesis creates the logic for one iteration of the loop, and the RTL

design executes this logic for each iteration of the loop in sequence. Using optimization

directives, you can unroll loops, which allows all iterations to occur in parallel. Loops can also

be pipelined, either with a finite-state machine fine-grain implementation (loop pipelining) or

with a more coarse-grain handshake-based implementation (dataflow).

• Arrays in the C code synthesize into block RAM or UltraRAM in the final FPGA design

If the array is on the top-level function interface, high-level synthesis implements the array as

ports to access a block RAM outside the design.

High-level synthesis creates an optimized implementation based on default behavior, constraints,

and any optimization directives you specify. You can use optimization directives to modify and

control the default behavior of the internal logic and I/O ports. This allows you to generate

variations of the hardware implementation from the same C code.

To determine if the design meets your requirements, you can review the performance metrics in

the synthesis report generated by high-level synthesis. After analyzing the report, you can use

optimization directives to refine the implementation. The synthesis report contains information

on the following performance metrics:

• Area: Amount of hardware resources required to implement the design based on the resources

available in the FPGA, including look-up tables (LUT), registers, block RAMs, and DSP48s.

• Latency: Number of clock cycles required for the function to compute all output values.

• Initiation interval (II): Number of clock cycles before the function can accept new input data.

• Loop iteration latency: Number of clock cycles it takes to complete one iteration of the loop.

• Loop initiation interval: Number of clock cycles before the next iteration of the loop starts to

process data.

• Loop latency: Number of cycles to execute all iterations of the loop.

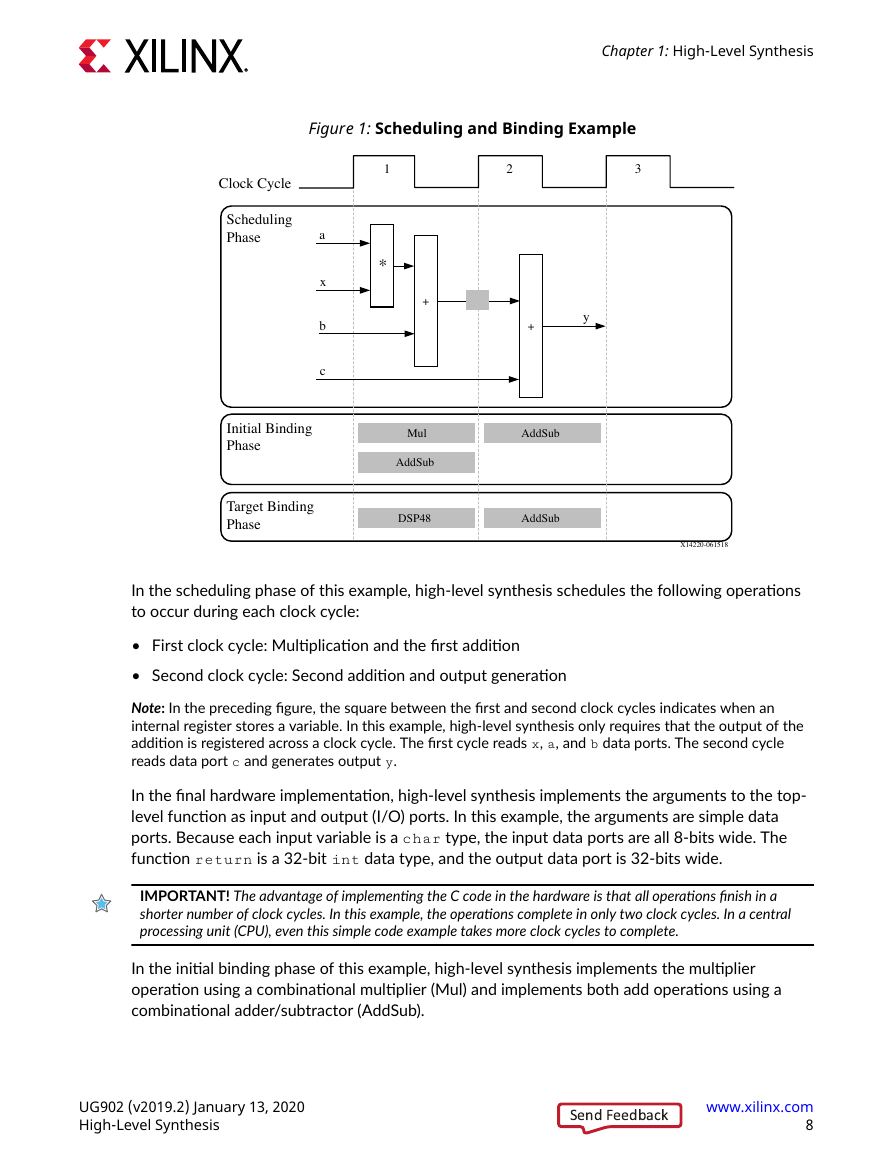

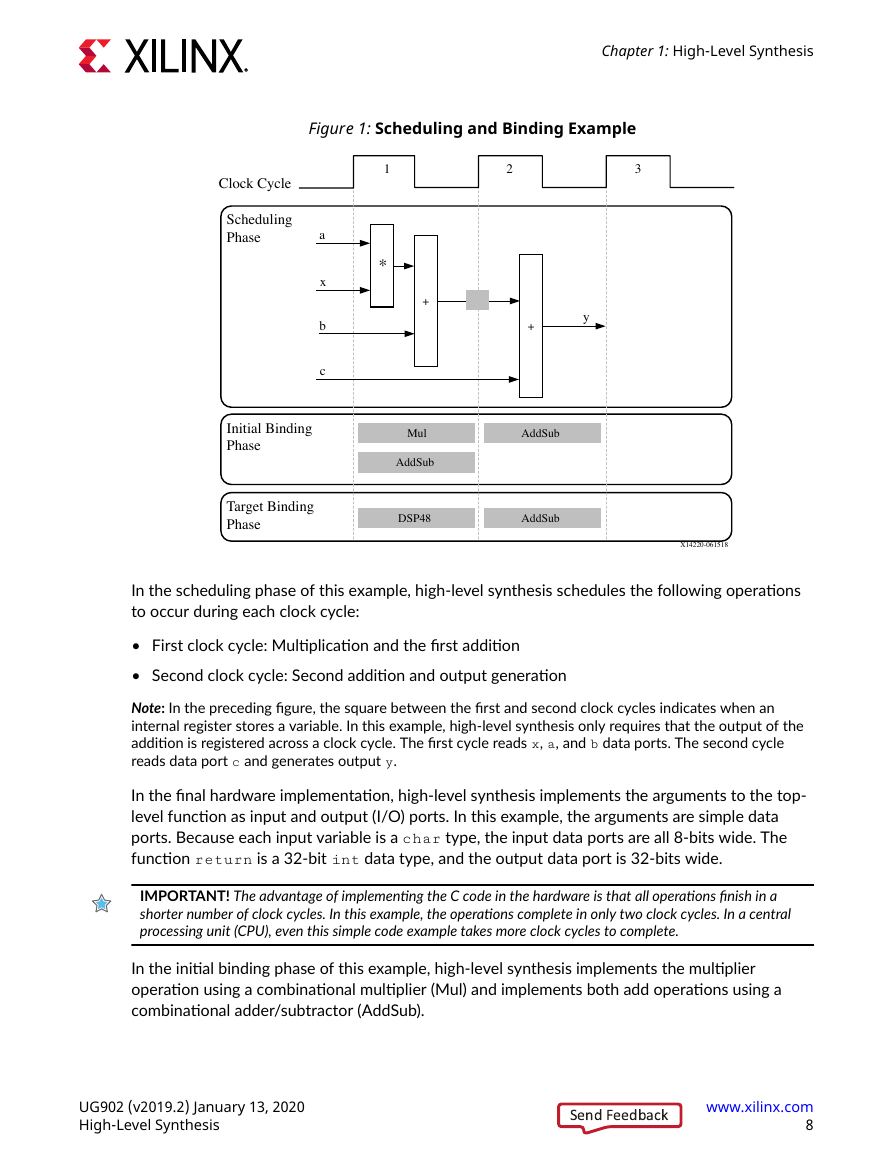

Scheduling and Binding Example

The following figure shows an example of the scheduling and binding phases for this code

example:

int foo(char x, char a, char b, char c) {

char y;

y = x*a+b+c;

return y;

}

UG902 (v2019.2) January 13, 2020

High-Level Synthesis

www.xilinx.com

7

Send Feedback�

Chapter 1: High-Level Synthesis

Figure 1: Scheduling and Binding Example

Clock Cycle

Scheduling

Phase

1

*

a

x

b

c

2

3

+

y

+

Initial Binding

Phase

Target Binding

Phase

Mul

AddSub

AddSub

DSP48

AddSub

X14220-061518

In the scheduling phase of this example, high-level synthesis schedules the following operations

to occur during each clock cycle:

• First clock cycle: Multiplication and the first addition

• Second clock cycle: Second addition and output generation

Note: In the preceding figure, the square between the first and second clock cycles indicates when an

internal register stores a variable. In this example, high-level synthesis only requires that the output of the

addition is registered across a clock cycle. The first cycle reads x, a, and b data ports. The second cycle

reads data port c and generates output y.

In the final hardware implementation, high-level synthesis implements the arguments to the top-

level function as input and output (I/O) ports. In this example, the arguments are simple data

ports. Because each input variable is a char type, the input data ports are all 8-bits wide. The

function return is a 32-bit int data type, and the output data port is 32-bits wide.

IMPORTANT! The advantage of implementing the C code in the hardware is that all operations finish in a

shorter number of clock cycles. In this example, the operations complete in only two clock cycles. In a central

processing unit (CPU), even this simple code example takes more clock cycles to complete.

In the initial binding phase of this example, high-level synthesis implements the multiplier

operation using a combinational multiplier (Mul) and implements both add operations using a

combinational adder/subtractor (AddSub).

UG902 (v2019.2) January 13, 2020

High-Level Synthesis

www.xilinx.com

8

Send Feedback�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc