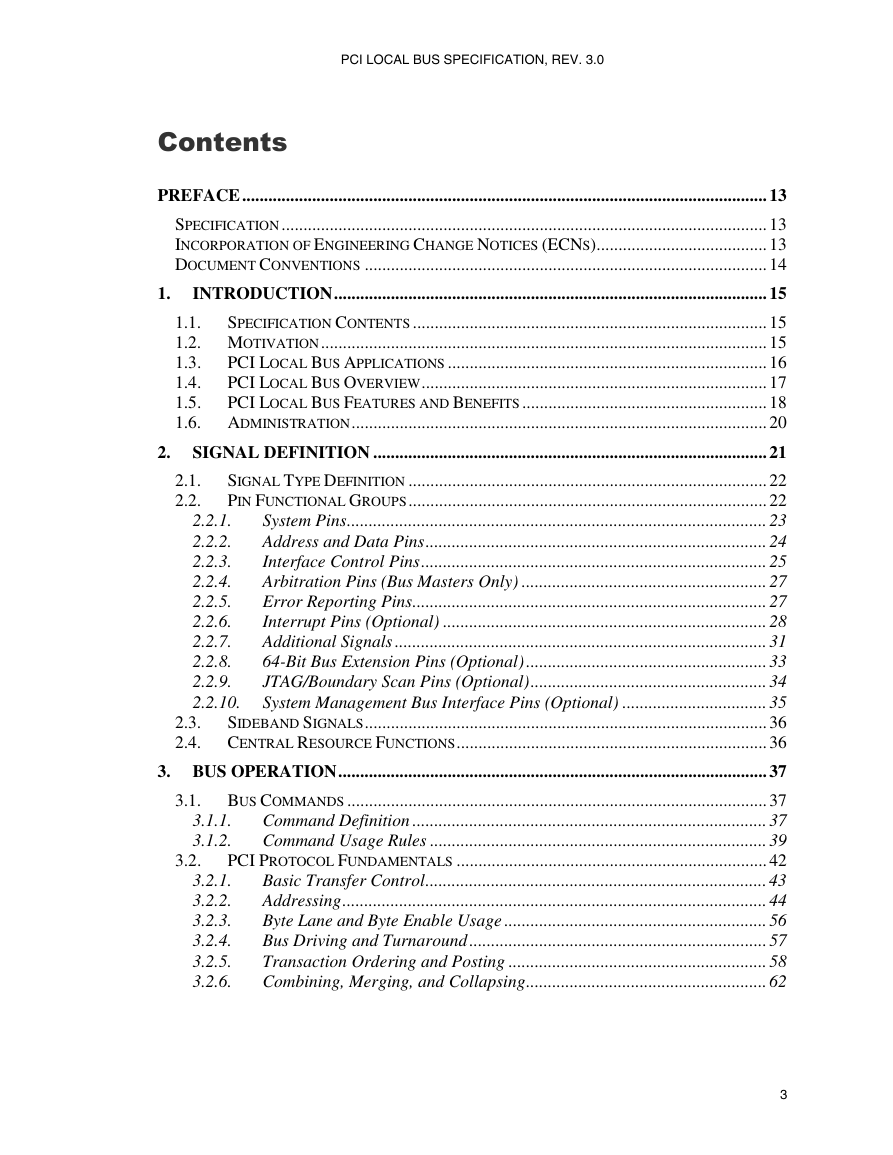

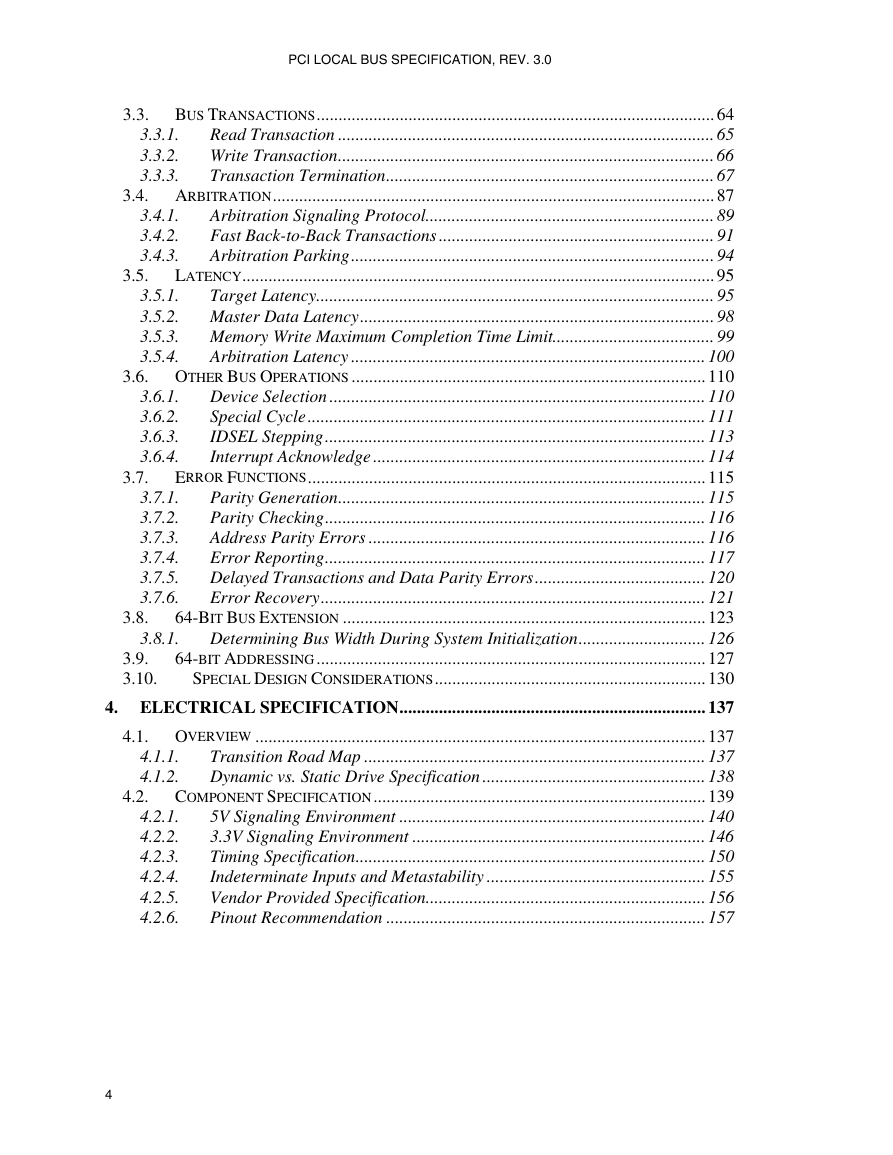

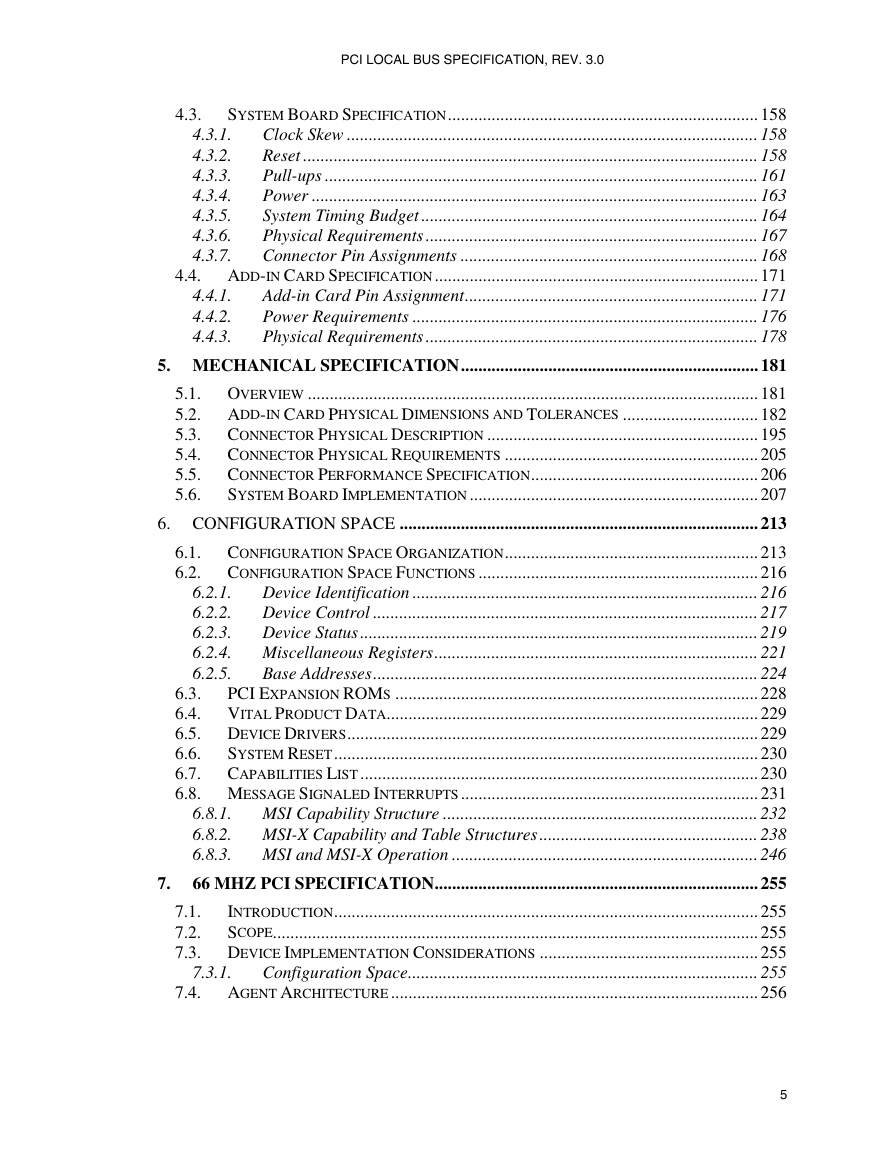

Contents

Figures

Tables

Preface

Specification

Incorporation of Engineering Change Notices (ECNs)

Document Conventions

1. Introduction

1.1. Specification Contents

1.2. Motivation

1.3. PCI Local Bus Applications

1.4. PCI Local Bus Overview

1.5. PCI Local Bus Features and Benefits

1.6. Administration

2. Signal Definition

2.1. Signal Type Definition

2.2. Pin Functional Groups

2.2.1. System Pins

2.2.2. Address and Data Pins

2.2.3. Interface Control Pins

2.2.4. Arbitration Pins (Bus Masters Only)

2.2.5. Error Reporting Pins

2.2.6. Interrupt Pins (Optional)

2.2.7. Additional Signals

2.2.8. 64-Bit Bus Extension Pins (Optional)

2.2.9. JTAG/Boundary Scan Pins (Optional)

2.2.10. System Management Bus Interface Pins (Optional)

2.3. Sideband Signals

2.4. Central Resource Functions

3. Bus Operation

3.1. Bus Commands

3.1.1. Command Definition

3.1.2. Command Usage Rules

3.2. PCI Protocol Fundamentals

3.2.1. Basic Transfer Control

3.2.2. Addressing

3.2.2.1. I/O Space Decoding

3.2.2.2. Memory Space Decoding

3.2.2.3. Configuration Space Decoding

3.2.2.3.1. Configuration Commands (Type 0 and Type 1)

3.2.2.3.2. Software Generation of Configuration Transactions

3.2.2.3.3. Software Generation of Special Cycles

3.2.2.3.4. Selection of a Device’s Configuration Space

3.2.2.3.5. System Generation of IDSEL

3.2.3. Byte Lane and Byte Enable Usage

3.2.4. Bus Driving and Turnaround

3.2.5. Transaction Ordering and Posting

3.2.5.1. Transaction Ordering and Posting for Simple

3.2.5.2. Transaction Ordering and Posting for Bridges

3.2.6. Combining, Merging, and Collapsing

3.3. Bus Transactions

3.3.1. Read Transaction

3.3.2. Write Transaction

3.3.3. Transaction Termination

3.3.3.1. Master Initiated Termination

3.3.3.2. Target Initiated Termination

3.3.3.2.1. Target Termination Signaling Rules

3.3.3.2.2. Requirements on a Master Because of Target

3.3.3.3. Delayed Transactions

3.3.3.3.1. Basic Operation of a Delayed Transaction

3.3.3.3.2. Information Required to Complete a Delayed

3.3.3.3.3. Discarding a Delayed Transaction

3.3.3.3.4. Memory Writes and Delayed Transactions

3.3.3.3.5. Supporting Multiple Delayed Transactions

3.4. Arbitration

3.4.1. Arbitration Signaling Protocol

3.4.2. Fast Back-to-Back Transactions

3.4.3. Arbitration Parking

3.5. Latency

3.5.1. Target Latency

3.5.1.1. Target Initial Latency

3.5.1.2. Target Subsequent Latency

3.5.2. Master Data Latency

3.5.3. Memory Write Maximum Completion Time Limit

3.5.4. Arbitration Latency

3.5.4.1. Bandwidth and Latency Considerations

3.5.4.2. Determining Arbitration Latency

3.5.4.3. Determining Buffer Requirements

3.6. Other Bus Operations

3.6.1. Device Selection

3.6.2. Special Cycle

3.6.3. IDSEL Stepping

3.6.4. Interrupt Acknowledge

3.7. Error Functions

3.7.1. Parity Generation

3.7.2. Parity Checking

3.7.3. Address Parity Errors

3.7.4. Error Reporting

3.7.4.1. Data Parity Error Signaling on PERR#

3.7.4.2. Other Error Signaling on SERR#

3.7.4.3. Master Data Parity Error Status Bit

3.7.4.4. Detected Parity Error Status Bit

3.7.5. Delayed Transactions and Data Parity Errors

3.7.6. Error Recovery

3.8. 64-Bit Bus Extension

3.8.1. Determining Bus Width During System Initialization

3.9. 64-bit Addressing

3.10. Special Design Considerations

4. Electrical Specification

4.1. Overview

4.1.1. Transition Road Map

4.1.2. Dynamic vs. Static Drive Specification

4.2. Component Specification

4.2.1. 5V Signaling Environment

4.2.1.1. DC Specifications

4.2.1.2. AC Specifications

4.2.1.3. Maximum AC Ratings and Device Protection

4.2.2. 3.3V Signaling Environment

4.2.2.1. DC Specifications

4.2.2.2. AC Specifications

4.2.2.3. Maximum AC Ratings and Device Protection

4.2.3. Timing Specification

4.2.3.1. Clock Specification

4.2.3.2. Timing Parameters

4.2.3.3. Measurement and Test Conditions

4.2.4. Indeterminate Inputs and Metastability

4.2.5. Vendor Provided Specification

4.2.6. Pinout Recommendation

4.3. System Board Specification

4.3.1. Clock Skew

4.3.2. Reset

4.3.3. Pull-ups

4.3.4. Power

4.3.4.1. Power Requirements

4.3.4.2. Sequencing

4.3.4.3. Decoupling

4.3.5. System Timing Budget

4.3.6. Physical Requirements

4.3.6.1. Routing and Layout Recommendations for Four-Layer

4.3.6.2. System Board Impedance

4.3.7. Connector Pin Assignments

4.4. Add-in Card Specification

4.4.1. Add-in Card Pin Assignment

4.4.2. Power Requirements

4.4.2.1. Decoupling

4.4.2.2. Power Consumption

4.4.3. Physical Requirements

4.4.3.1. Trace Length Limits

4.4.3.2. Routing Recommendations for Four-Layer Add- in

4.4.3.3. Impedance

4.4.3.4. Signal Loading

5. Mechanical Specification

5.1. Overview

5.2. Add-in Card Physical Dimensions and Tolerances

5.3. Connector Physical Description

5.4. Connector Physical Requirements

5.5. Connector Performance Specification

5.6. System Board Implementation

6. Configuration Space

6.1. Configuration Space Organization

6.2. Configuration Space Functions

6.2.1. Device Identification

6.2.2. Device Control

6.2.3. Device Status

6.2.4. Miscellaneous Registers

6.2.5. Base Addresses

6.2.5.1. Address Maps

6.2.5.2. Expansion ROM Base Address Register

6.3. PCI Expansion ROMs

6.4. Vital Product Data

6.5. Device Drivers

6.6. System Reset

6.7. Capabilities List

6.8. Message Signaled Interrupts

6.8.1. MSI Capability Structure

6.8.1.1. Capability ID for MSI

6.8.1.2. Next Pointer for MSI

6.8.1.3. Message Control for MSI

6.8.1.4. Message Address for MSI

6.8.1.5. Message Upper Address for MSI (Optional)

6.8.1.6. Message Data for MSI

6.8.1.7. Mask Bits for MSI (Optional)

6.8.1.8. Pending Bits for MSI (Optional)

6.8.2. MSI-X Capability and Table Structures

6.8.2.1. Capability ID for MSI-X

6.8.2.2. Next Pointer for MSI-X

6.8.2.3. Message Control for MSI-X

6.8.2.4. Table Offset/Table BIR for MSI-X

6.8.2.5. PBA Offset/PBA BIR for MSI-X

6.8.2.6. Message Address for MSI-X Table Entries

6.8.2.7. Message Upper Address for MSI-X Table Entries

6.8.2.8. Message Data for MSI-X Table Entries

6.8.2.9. Vector Control for MSI-X Table Entries

6.8.2.10. Pending Bits for MSI-X PBA Entries

6.8.3. MSI and MSI-X Operation

6.8.3.1. MSI Configuration

6.8.3.2. MSI-X Configuration

6.8.3.3. Enabling Operation

6.8.3.4. Sending Messages

6.8.3.5. Per-vector Masking and Function Masking

6.8.3.6. Hardware/Software Synchronization

6.8.3.7. Message Transaction Termination

6.8.3.8. Message Transaction Reception and Ordering

7. 66 MHz PCI Specification

7.1. Introduction

7.2. Scope

7.3. Device Implementation Considerations

7.3.1. Configuration Space

7.4. Agent Architecture

7.5. Protocol

7.5.1. 66MHZ_ENABLE (M66EN) Pin Definition

7.5.2. Latency

7.6. Electrical Specification

7.6.1. Overview

7.6.2. Transition Roadmap to 66 MHz PCI

7.6.3. Signaling Environment

7.6.3.1. DC Specifications

7.6.3.2. AC Specifications

7.6.3.3. Maximum AC Ratings and Device Protection

7.6.4. Timing Specification

7.6.4.1. Clock Specification

7.6.4.2. Timing Parameters

7.6.4.3. Measurement and Test Conditions

7.6.5. Vendor Provided Specification

7.6.6. Recommendations

7.6.6.1. Pinout Recommendations

7.6.6.2. Clocking Recommendations

7.7. System Board Specification

7.7.1. Clock Uncertainty

7.7.2. Reset

7.7.3. Pullups

7.7.4. Power

7.7.4.1. Power Requirements

7.7.4.2. Sequencing

7.7.4.3. Decoupling

7.7.5. System Timing Budget

7.7.6. Physical Requirements

7.7.6.1. Routing and Layout Recommendations for Four-Layer

7.7.6.2. System Board Impedance

7.7.7. Connector Pin Assignments

7.8. Add-in Card Specifications

8. System Support for SMBus

8.1. SMBus System Requirements

8.1.1. Power

8.1.2. Physical and Logical SMBus

8.1.3. Bus Connectivity

8.1.4. Master and Slave Support

8.1.5. Addressing and Configuration

8.1.6. Electrical

8.1.7. SMBus Behavior on PCI Reset

8.2. Add-in Card SMBus Requirements

8.2.1. Connection

8.2.2. Master and Slave Support

8.2.3. Addressing and Configuration

8.2.4. Power

8.2.5. Electrical

A. Special Cycle Messages

A.1. Message Encodings

A.2. Use of Specific Encodings

B. State Machines

B.1. Target LOCK Machine

B.2. Master Sequencer Machine

B.3. Master LOCK Machine

C. Operating Rules

C.1. When Signals are Stable

C.2. Master Signals

C.3. Target Signals

C.4. Data Phases

C.5. Arbitration

C.6. Latency

C.7. Device Selection

C.8. Parity

D. Class Codes

D.1. Base Class 00h

D.2. Base Class 01h

D.3. Base Class 02h

D.4. Base Class 03h

D.5. Base Class 04h

D.6. Base Class 05h

D.7. Base Class 06h

D.8. Base Class 07h

D.9. Base Class 08h

D.10. Base Class 09h

D.11. Base Class 0Ah

D.12. Base Class 0Bh

D.13. Base Class 0Ch

D.14. Base Class 0Dh

D.15. Base Class 0Eh

D.16. Base Class 0Fh

D.17. Base Class 10h

D.18. Base Class 11h

E. System Transaction Ordering

E.1. Producer - Consumer Ordering Model

E.2. Summary of PCI Ordering Requirements

E.3. Ordering of Requests

E.4. Ordering of Delayed Transactions

E.5. Delayed Transactions and LOCK#

E.6. Error Conditions

F. Exclusive Accesses

F.1. Exclusive Accesses on PCI

F.2. Starting an Exclusive Access

F.3. Continuing an Exclusive Access

F.4. Accessing a Locked Agent

F.5. Completing an Exclusive Access

F.6. Complete Bus Lock

G. I/O Space Address Decoding for Legacy Devices

H. Capability IDs

I. Vital Product Data

I.1. VPD Format

I.2. Compatibility

I.3. VPD Definitions

I.3.1. VPD Large and Small Resource Data Tags

I.3.1.1. Read-Only Fields

I.3.1.2. Read/Write Fields

I.3.2. VPD Example

Glossary

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc