月隐出品

1 前言

JESD204B 的 AXI4-Lite 时序分析

本人在写 JESD204B 的 AXI4-Lite 配置接口时,发现对端口时序的理解和常

规的理解不一样,因此写这篇文章以作记录,具体如下。

1.1 写时序异常

按常规理解的时序图(参照 SRIO)写出来的代码,ready 是因,valid 是果。

在仿真时发现在时钟复位配置好后,ready 信号并没有按想象中一样,会先拉高

来等待输入数据。ready 信号是一直为 0 的。

检查配置情况发现配置没有错误,然后对比 JESD204B ip 核的 demo 文件仿

真图,发现 ready 信号要先等 valid 信号有效后才会输出一个时钟的有效信号。

这成了 valid 是因,ready 是果。因果和常规理解的是反着的。

具体的情况见第 3 节。

1.2 读时序异常

按常规理解的时序为,ready 准备好后,输入读取的地址并且 valid 有效时,

ready 会拉低去处理内部信号,在输出对应地址数据后,再次拉高等待下一次读

取。

但是 JESD204B 的 ip 中 AXI4-Lite 配置接口的读 aready 是隔一段时间输出

一个固定的 2 个时钟高 ready。即使是在 availd 拉高后 aready 也不会根据 availd

拉低,依然是输出固定的 2 个时钟高信号。这导致我们在需要连续读取内部数据

时,不能单纯的把 aready 当成读取下一个地址准备好的依据。

具体情况见第 4 节。

2 JESD204B 的 AXI4-Lite 接口功能

AXI4-Lite 部分的接口是用于配置 JESD204 core 的寄存器,其中有一些关

键参数是必须要配置的,比如:

a) M:(converters/device):AD/DA 器件的转换通道数

b) L:(Lanes per Link):接的通道线数量,即占用 GTX 线数

c) LR:(Line Rate):单根线(通道)的速率,LR=(M*S*N’*10/8*FC)/L,FC

为采样率;

d) F:(octets per frame):每帧包含的字节数,F=(M*S*N’)/(8*L);

e) K:(frames per multiframe):一个多帧包含多少个帧,根据 AD/DA 手册填

写,一般是 32;

f) N:转换器的分辨率;

g) N’:word 的长度,4 的倍数,N’=N+CS+T,CS 是控制位,T 是尾码;

�

月隐出品

h) S:(samples):S 表示每一个转换器每一帧中的采样次数。一般情况下,

S 都是 1,。S 必须是整数。协议中允许 S 大于 1,但是 S 等于 1 的时候

开业保证帧时钟和采样时钟相等。比如 S=1,则一个 500MSPS 的转换

器,帧时钟也是 500M。

因此配置 JESD204B 的 AXI4-Lite 接口是必须的。下面谈谈我对 JESD204B 的

AXI4-Lite 接口时序的理解,仅做参考。

3 写时序

srio 中的时序为常规理解的时序图,demo 中时序情况为 JESD204B 的 ip 核

时序情况。

3.1 srio 中的写时序说明

由于 JESD204B 的 ip 核手册《pg066》上没有这一部分的时序讲解,因此我

参照 srio 的 ip 核手册《pg007》上的写时序写了第一版程序。Srio 中的写时序

如下图所示。

下面 a-c 是客户端需要处理的,d 是 ip 核内部处理的。

A) 写地址 awaddr:在写地址准备好信号 awready==1 时有效(awvalid=1),

在 awready==0 时无效;

B) 写数据 wdata:在写数据准备好信号 wready==1 时有效(wvalid=1),在

wready==0 时无效;

C) 写响应准备好信号 bready:在写地址、写数据有效时变高,在写响应有

效指示信号 bvalid==1 时,变低。

D) 写地址准备好信号 awready、写数据准备好信号 wready:在无写响应时

变高,在写地址、写数据有效时变低。

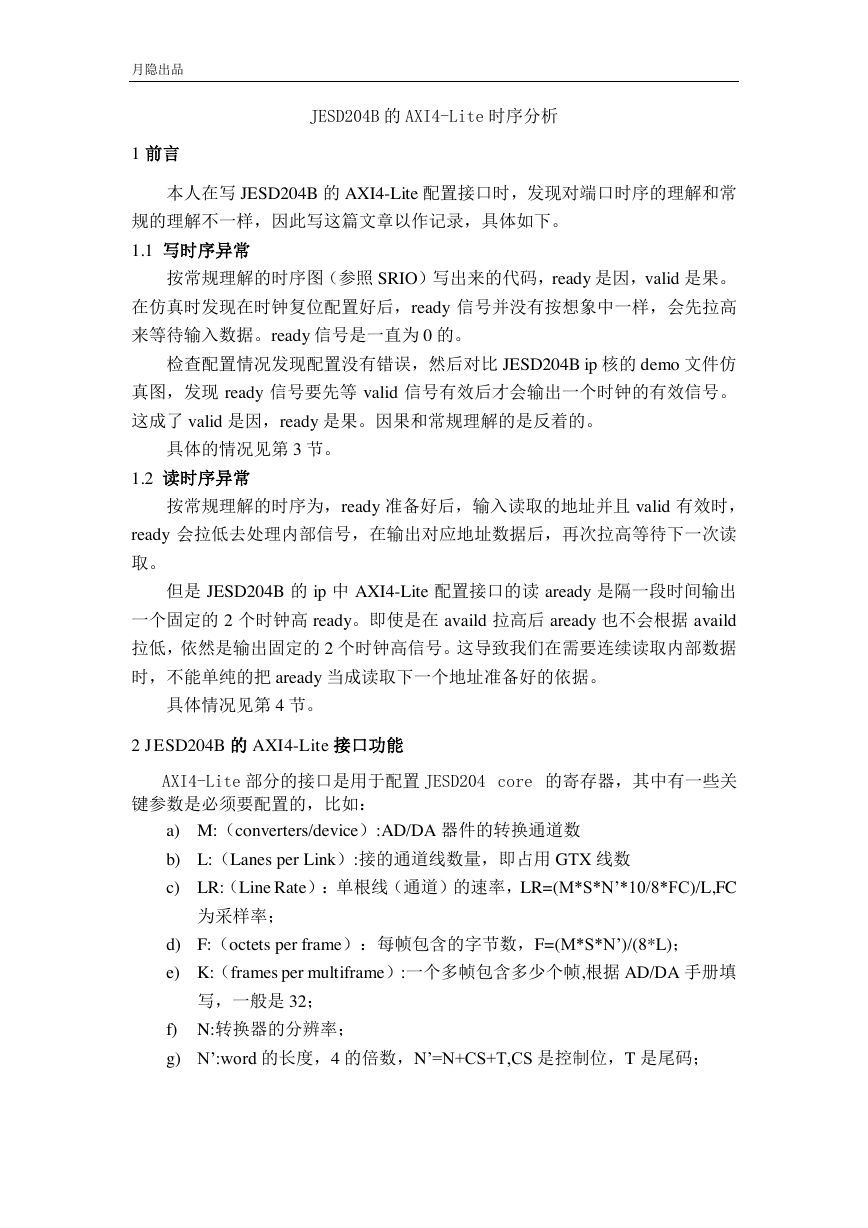

3.2 demo 中的写时序情况

demo 中的写时序情况为写数据有效为因,写数据准备好信号为果。具体如下:

�

月隐出品

a) 写数据时序:在一个时刻先写入写数据 wdata,wvalid 拉高,等待 wready

有效后再把写数据有效信号 wvalid 拉低;

b) 写地址时序:在写入数据有效的同时,写入地址 awaddr,awvalid 拉高,

等待 awready 有效后再把 awvalid 拉低。

4 读时序

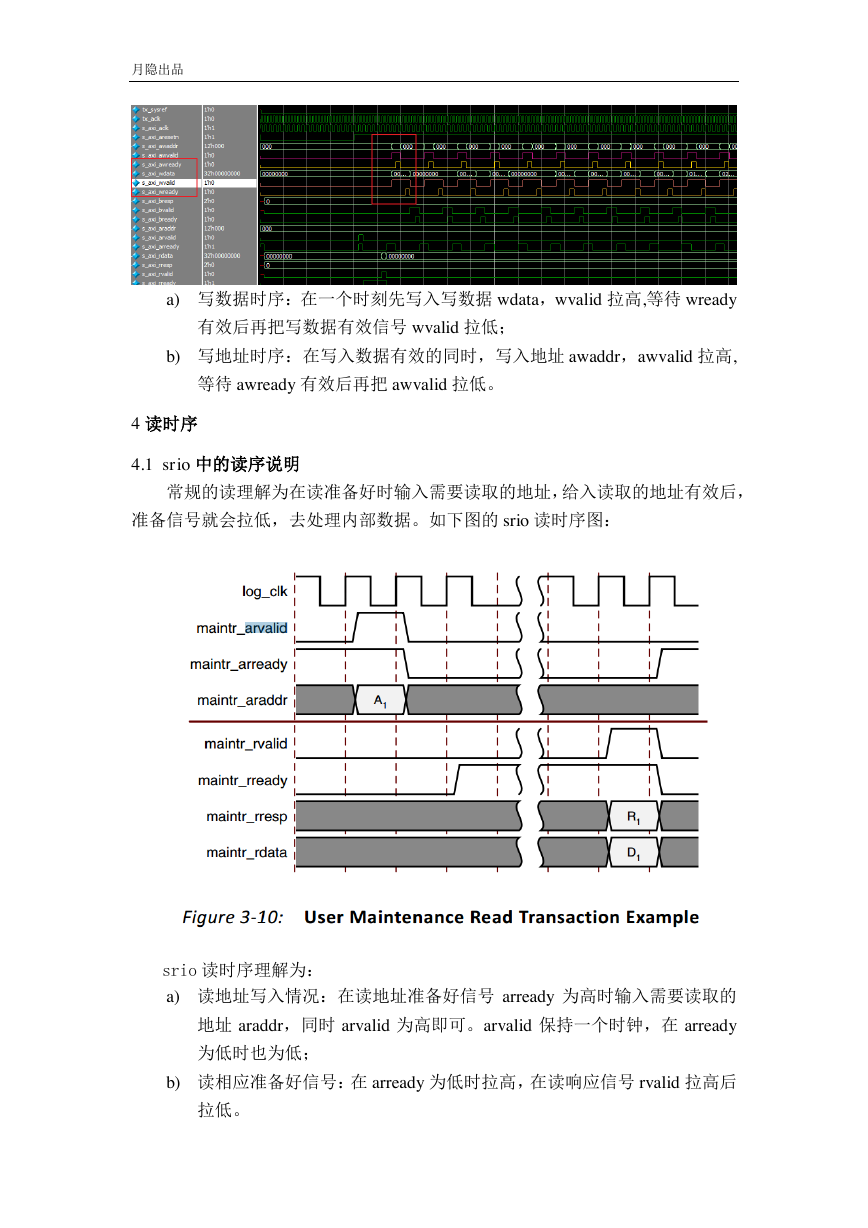

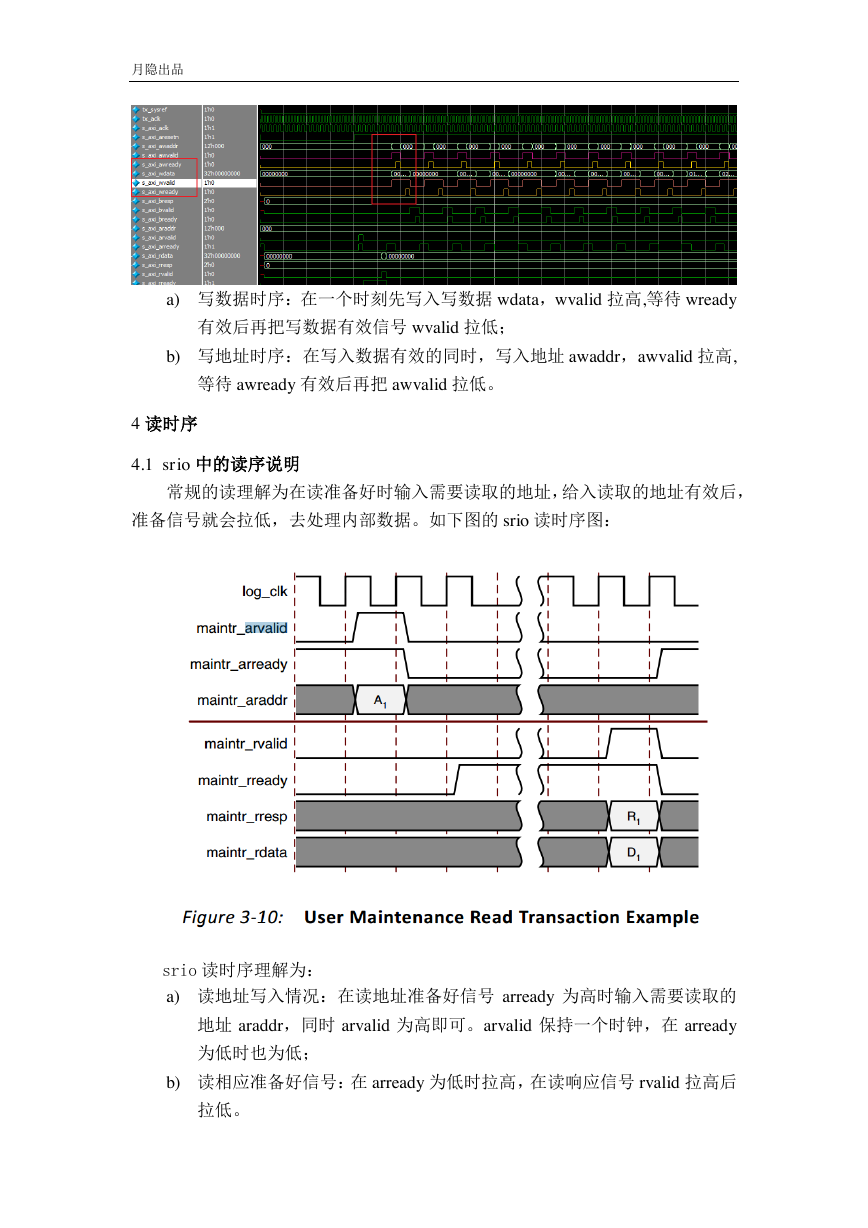

4.1 srio 中的读序说明

常规的读理解为在读准备好时输入需要读取的地址,给入读取的地址有效后,

准备信号就会拉低,去处理内部数据。如下图的 srio 读时序图:

srio 读时序理解为:

a) 读地址写入情况:在读地址准备好信号 arready 为高时输入需要读取的

地址 araddr,同时 arvalid 为高即可。arvalid 保持一个时钟,在 arready

为低时也为低;

b) 读相应准备好信号:在 arready 为低时拉高,在读响应信号 rvalid 拉高后

拉低。

�

月隐出品

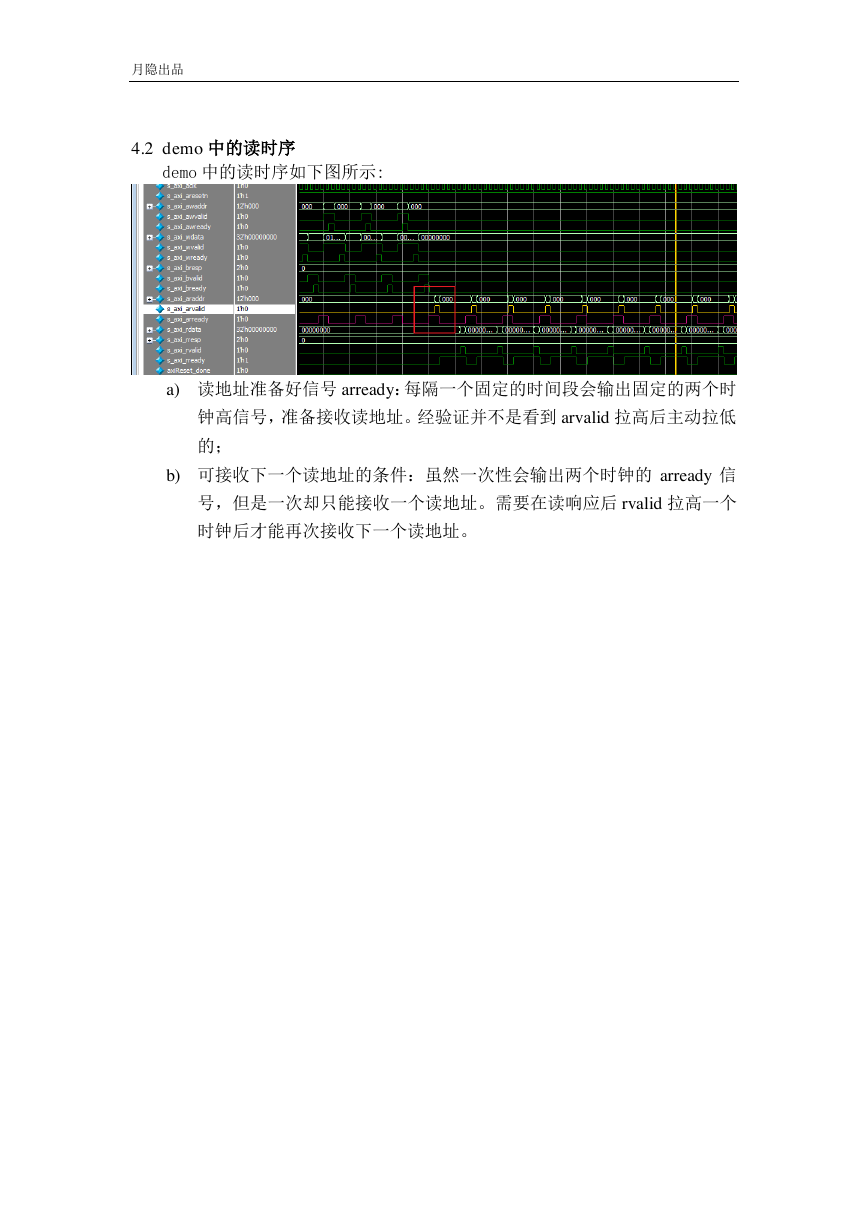

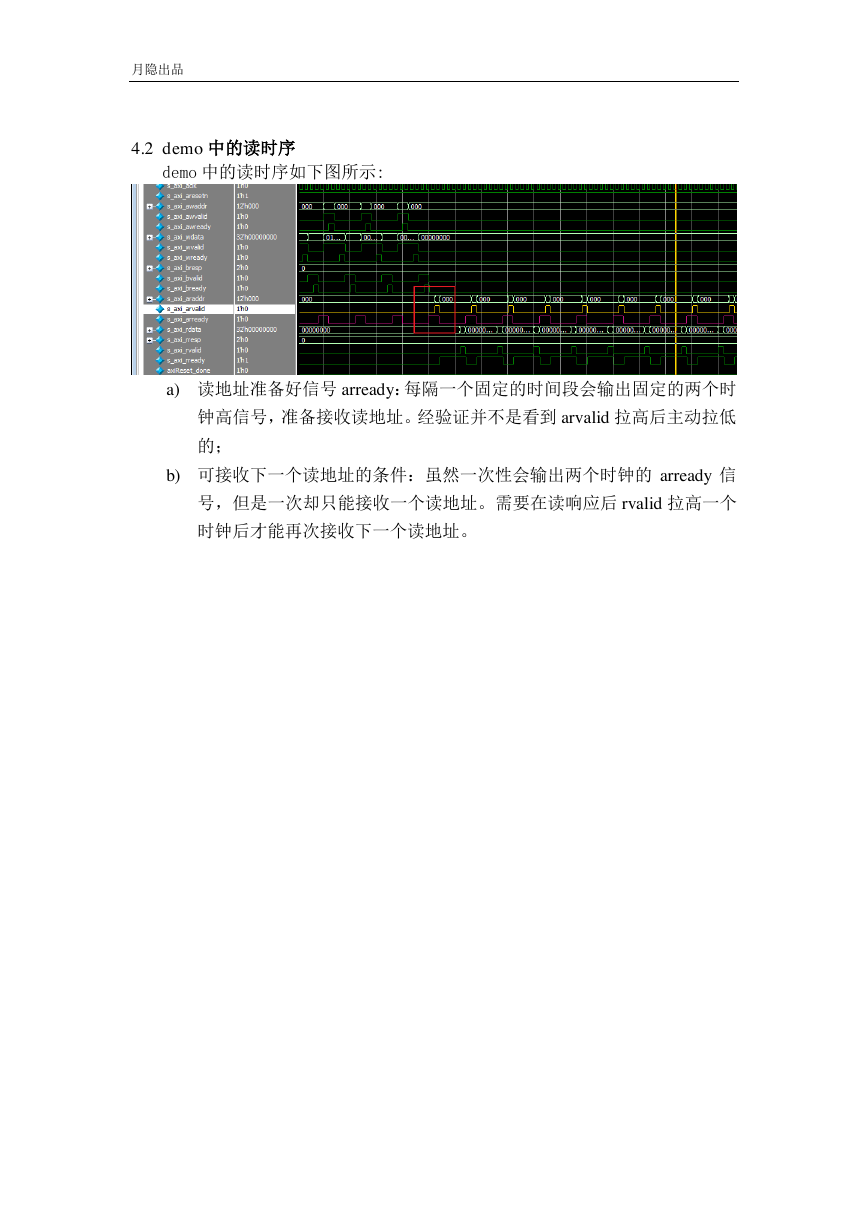

4.2 demo 中的读时序

demo 中的读时序如下图所示:

a) 读地址准备好信号 arready:每隔一个固定的时间段会输出固定的两个时

钟高信号,准备接收读地址。经验证并不是看到 arvalid 拉高后主动拉低

的;

b) 可接收下一个读地址的条件:虽然一次性会输出两个时钟的 arready 信

号,但是一次却只能接收一个读地址。需要在读响应后 rvalid 拉高一个

时钟后才能再次接收下一个读地址。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc