PHASELOCK TECHNIQUES

�

PHASELOCK TECHNIQUES

Third Edition

FLOYD M. GARDNER

Consulting Engineer

Palo Alto, California

A JOHN WILEY & SONS, INC., PUBLICATION

�

Copyright 2005 by John Wiley & Sons, Inc. All rights reserved.

Published by John Wiley & Sons, Inc., Hoboken, New Jersey.

Published simultaneously in Canada.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in

any form or by any means, electronic, mechanical, photocopying, recording, scanning, or

otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright

Act, without either the prior written permission of the Publisher, or authorization through

payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222

Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4470, or on the web at

www.copyright.com. Requests to the Publisher for permission should be addressed to the

Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030,

(201) 748-6011, fax (201) 748-6008, or online at http://www.wiley.com/go/permission.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their

best efforts in preparing this book, they make no representations or warranties with respect to

the accuracy or completeness of the contents of this book and specifically disclaim any

implied warranties of merchantability or fitness for a particular purpose. No warranty may be

created or extended by sales representatives or written sales materials. The advice and

strategies contained herein may not be suitable for your situation. You should consult with a

professional where appropriate. Neither the publisher nor author shall be liable for any loss

of profit or any other commercial damages, including but not limited to special, incidental,

consequential, or other damages.

For general information on our other products and services or for technical support, please

contact our Customer Care Department within the United States at (800) 762-2974, outside

the United States at (317) 572-3993 or fax (317) 572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears

in print may not be available in electronic formats. For more information about Wiley

products, visit our web site at www.wiley.com.

Library of Congress Cataloging-in-Publication Data:

Gardner, Floyd Martin, 1929–

Phaselock techniques / Floyd M. Gardner.—3rd ed.

p. cm.

Includes bibliographical references and index.

ISBN-13 978-0-471-43063-6 (cloth)

ISBN-10 0-471-43063-3 (cloth)

1. Phase-locked loops. I. Title.

TK7872.P38G37 2005

621.3815

364—dc22

2004065041

Printed in the United States of America.

10 9 8 7 6 5 4 3 2 1

�

To Benjamin

�

CONTENTS

PREFACE

NOTATION

1 INTRODUCTION

1.1 Salient Properties of PLLs / 2

1.1.1 Bandwidth / 2

1.1.2 Linearity / 3

1.2 Organization of the Book / 3

1.3 Annotated Bibliography / 3

1.3.1 Books / 3

1.3.2 Reprint Volumes / 4

1.3.3 Journal Special Issues / 5

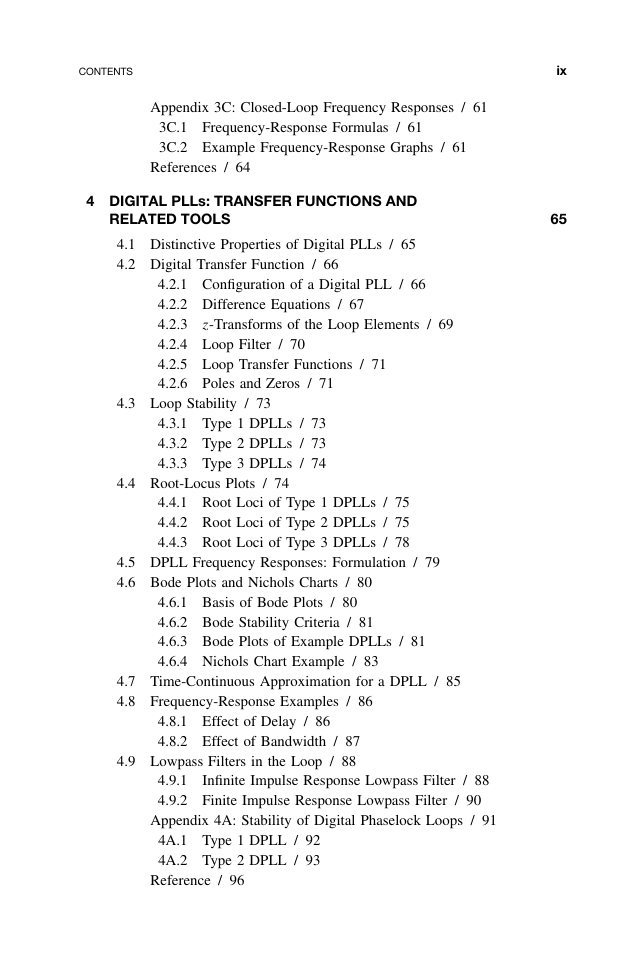

2 TRANSFER FUNCTIONS OF ANALOG PLLs

2.1 Basic Transfer Functions / 6

2.1.1 Transfer Functions of Individual Elements / 7

2.1.2 Combined Transfer Functions / 8

2.1.3 Characteristic Equation / 9

2.1.4 Nomenclature, Coefficients, and Units / 9

2.2 Second-Order PLLs / 10

2.2.1 Loop Filters / 10

2.2.2 Order and Type / 12

xvii

xix

1

6

vii

�

viii

CONTENTS

2.2.3 Loop Parameters / 12

2.2.4 Frequency Response / 15

2.3 Other Loop Types and Orders / 20

2.3.1 General Definition of Loop Gain K / 20

2.3.2 Examples of Type 1 PLLs / 22

2.3.3 Examples of Type 2 PLLs / 24

2.3.4 Higher-Type PLLs / 28

Reference / 28

3 GRAPHICAL AIDS

3.1 Root-Locus Plots / 30

29

3.1.1 Description of Root-Locus Plots / 30

3.1.2 Stability Criterion / 33

3.1.3 Root Loci of Type 1 PLLs / 33

3.1.4 Root Loci of Type 2 PLLs / 33

3.1.5 Root Loci of Type 3 PLLs / 34

3.1.6 Root Loci of Higher-Order PLLs / 35

3.1.7 Effect of Loop Delay on Root Locus / 38

3.2 Bode Plots / 38

3.2.1 Presentation Options / 38

3.2.2 Stability / 39

3.2.3 Bode Plots of Type 1 PLLs / 40

3.2.4 Bode Plots of Type 2 PLLs / 43

3.2.5 Bode Plots of Type 3 PLLs / 48

3.3 Nyquist Diagrams / 49

3.4 Nichols Charts / 49

3.4.1 Stability Criterion / 49

3.4.2 M-Contours / 50

3.4.3 Examples of Nichols Charts / 50

3.5 Closed-Loop Frequency-Response Curves / 52

Appendix 3A: Salient Features of Root Loci / 52

3A.1 Branches of Root Loci / 53

3A.2 Locus on the Real Axis / 53

3A.3 Locus Intersections with Axes / 54

Appendix 3B: Formats of the Open-Loop Transfer Function

G(s) / 56

3B.1 Proportional-Plus-Integral Section / 56

3B.2 High-Frequency Section / 60

3B.3 Calculations / 60

�

ix

65

CONTENTS

Appendix 3C: Closed-Loop Frequency Responses / 61

3C.1 Frequency-Response Formulas / 61

3C.2 Example Frequency-Response Graphs / 61

References / 64

4 DIGITAL PLLs: TRANSFER FUNCTIONS AND

RELATED TOOLS

4.1 Distinctive Properties of Digital PLLs / 65

4.2 Digital Transfer Function / 66

4.2.1 Configuration of a Digital PLL / 66

4.2.2 Difference Equations / 67

4.2.3 z-Transforms of the Loop Elements / 69

4.2.4 Loop Filter / 70

4.2.5 Loop Transfer Functions / 71

4.2.6 Poles and Zeros / 71

4.3 Loop Stability / 73

4.3.1 Type 1 DPLLs / 73

4.3.2 Type 2 DPLLs / 73

4.3.3 Type 3 DPLLs / 74

4.4 Root-Locus Plots / 74

4.4.1 Root Loci of Type 1 DPLLs / 75

4.4.2 Root Loci of Type 2 DPLLs / 75

4.4.3 Root Loci of Type 3 DPLLs / 78

4.5 DPLL Frequency Responses: Formulation / 79

4.6 Bode Plots and Nichols Charts / 80

4.6.1 Basis of Bode Plots / 80

4.6.2 Bode Stability Criteria / 81

4.6.3 Bode Plots of Example DPLLs / 81

4.6.4 Nichols Chart Example / 83

4.7 Time-Continuous Approximation for a DPLL / 85

4.8 Frequency-Response Examples / 86

4.8.1 Effect of Delay / 86

4.8.2 Effect of Bandwidth / 87

4.9 Lowpass Filters in the Loop / 88

4.9.1 Infinite Impulse Response Lowpass Filter / 88

4.9.2 Finite Impulse Response Lowpass Filter / 90

Appendix 4A: Stability of Digital Phaselock Loops / 91

4A.1 Type 1 DPLL / 92

4A.2 Type 2 DPLL / 93

Reference / 96

�

x

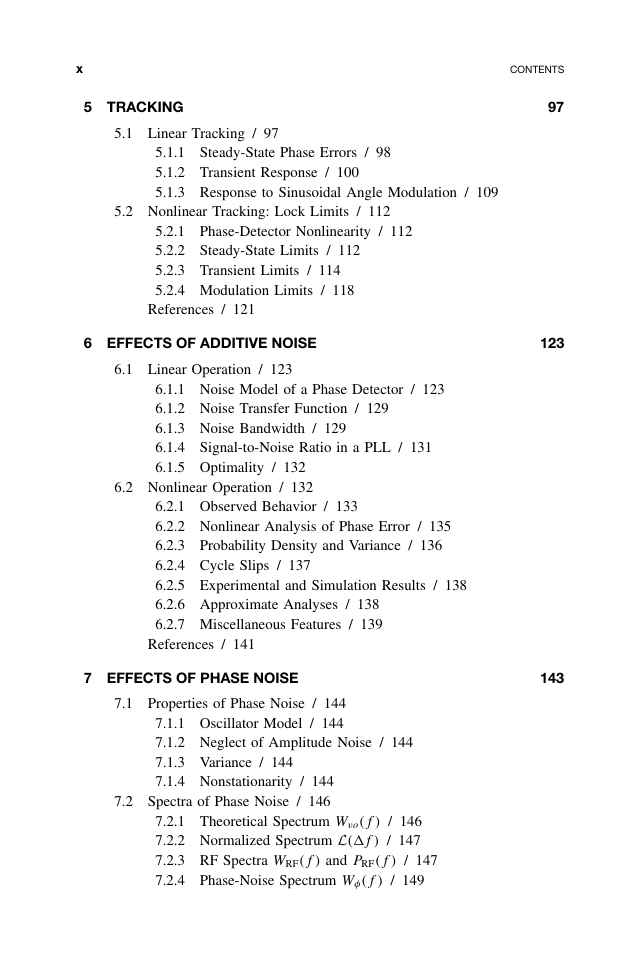

5 TRACKING

5.1 Linear Tracking / 97

CONTENTS

97

5.1.1 Steady-State Phase Errors / 98

5.1.2 Transient Response / 100

5.1.3 Response to Sinusoidal Angle Modulation / 109

5.2 Nonlinear Tracking: Lock Limits / 112

5.2.1 Phase-Detector Nonlinearity / 112

5.2.2 Steady-State Limits / 112

5.2.3 Transient Limits / 114

5.2.4 Modulation Limits / 118

References / 121

6 EFFECTS OF ADDITIVE NOISE

6.1 Linear Operation / 123

123

6.1.1 Noise Model of a Phase Detector / 123

6.1.2 Noise Transfer Function / 129

6.1.3 Noise Bandwidth / 129

6.1.4 Signal-to-Noise Ratio in a PLL / 131

6.1.5 Optimality / 132

6.2 Nonlinear Operation / 132

6.2.1 Observed Behavior / 133

6.2.2 Nonlinear Analysis of Phase Error / 135

6.2.3 Probability Density and Variance / 136

6.2.4 Cycle Slips / 137

6.2.5 Experimental and Simulation Results / 138

6.2.6 Approximate Analyses / 138

6.2.7 Miscellaneous Features / 139

References / 141

7 EFFECTS OF PHASE NOISE

143

7.1 Properties of Phase Noise / 144

7.1.1 Oscillator Model / 144

7.1.2 Neglect of Amplitude Noise / 144

7.1.3 Variance / 144

7.1.4 Nonstationarity / 144

7.2 Spectra of Phase Noise / 146

7.2.1 Theoretical Spectrum Wvo(f ) / 146

7.2.2 Normalized Spectrum L(�f ) / 147

7.2.3 RF Spectra WRF(f ) and PRF(f ) / 147

7.2.4 Phase-Noise Spectrum Wφ(f ) / 149

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc