爱手册爱翻译 中为电子科技

DDR3 布局布线

译自 飞思卡尔官方文档

Hardware Development Guide

for i.MX 6Quad, 6Dual, 6DualLite,

6Solo Families of

Applications Processors

IMX6 Serial Layout Recommendations

Document revision history

Date

Revision

Changes

2015-02-04

1.0

第一次撰稿

1 / 23

�

爱手册爱翻译 中为电子科技

目录

1. DDR 原理性连接框图 ........................................................................................................... 3

2. DDR 布局布线规则 ............................................................................................................... 4

3. DDR 布线细节 ....................................................................................................................... 5

3.1 数据线的交换 ................................................................................................................ 6

3.2 DDR3(64bits)T 型拓扑介绍 ....................................................................................... 6

3.3 DDR3(64bits)Fly-by 型拓扑介绍 ............................................................................... 6

3.4 2GB DDR 布局布线建议 ................................................................................................. 6

3.5 4GB DDR 布局布线建议 ................................................................................................. 7

4. DDR 布局布线实例 ............................................................................................................... 8

4.1 4 片 DDR T 型拓扑实例 .................................................................................................. 8

4.2 8 片 DDR Fly-by 型拓扑实例 ........................................................................................ 12

5. 高速信号布线建议 ............................................................................................................ 19

6. 地平面设计建议 ................................................................................................................ 19

7. DDR POWER 布线建议 ........................................................................................................ 21

8. 参考 .................................................................................................................................... 23

9. 声明 .................................................................................................................................... 23

2 / 23

�

爱手册爱翻译 中为电子科技

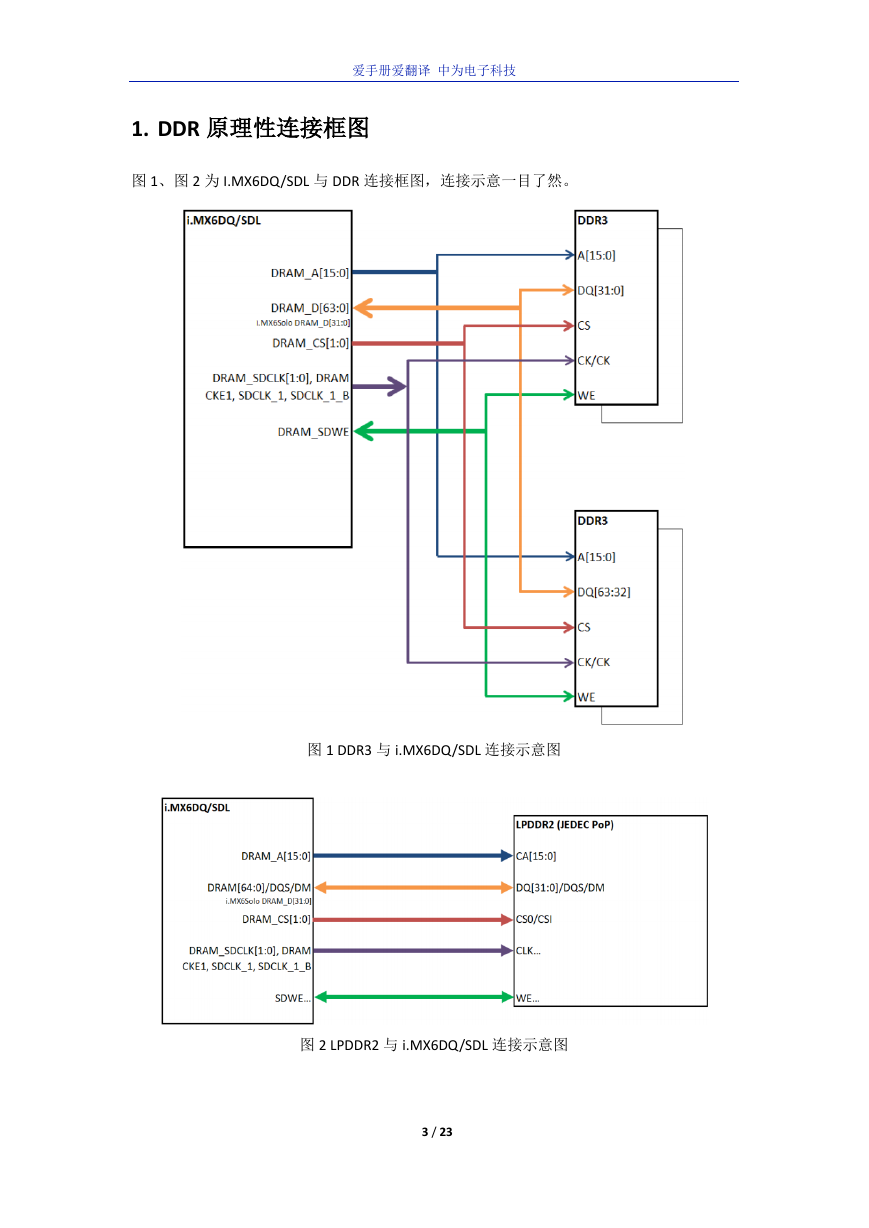

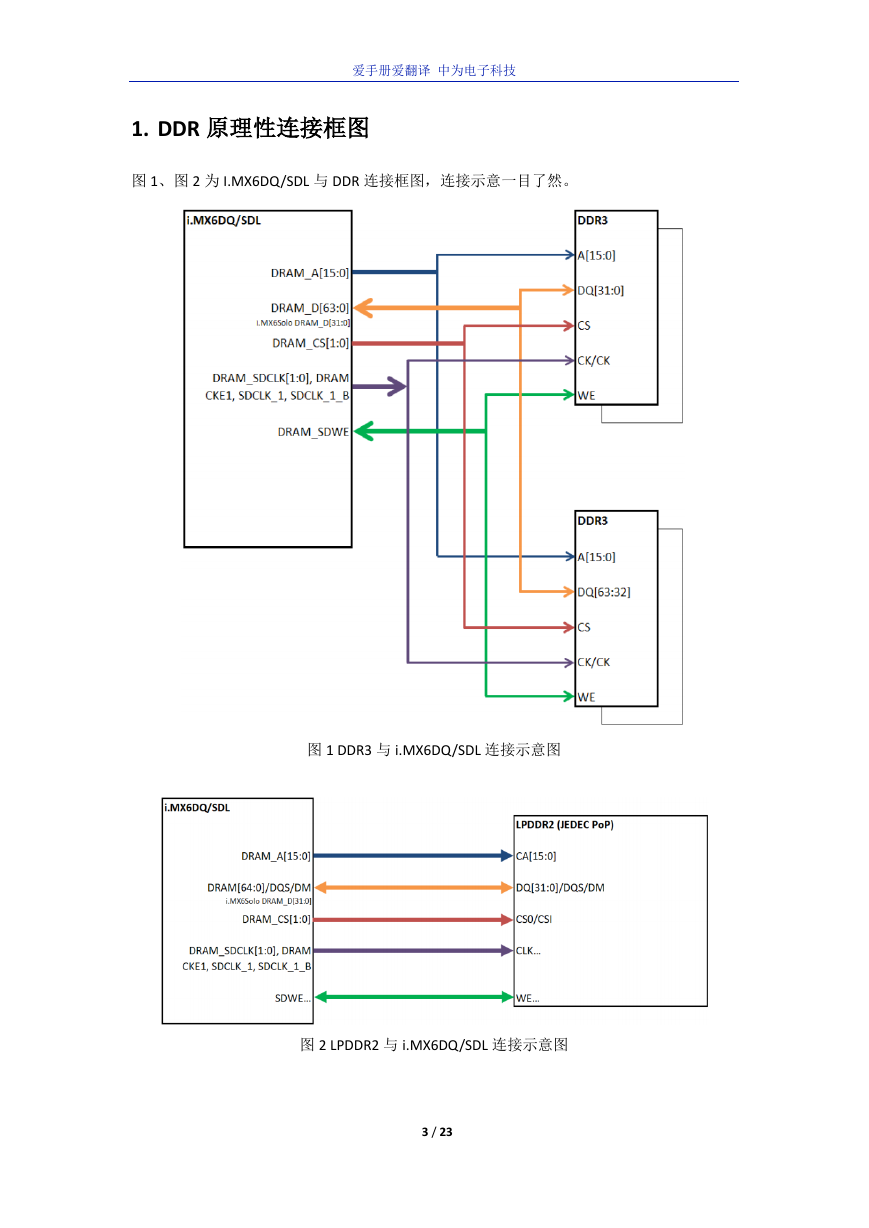

1. DDR 原理性连接框图

图 1、图 2 为 I.MX6DQ/SDL 与 DDR 连接框图,连接示意一目了然。

图 1 DDR3 与 i.MX6DQ/SDL 连接示意图

图 2 LPDDR2 与 i.MX6DQ/SDL 连接示意图

3 / 23

�

爱手册爱翻译 中为电子科技

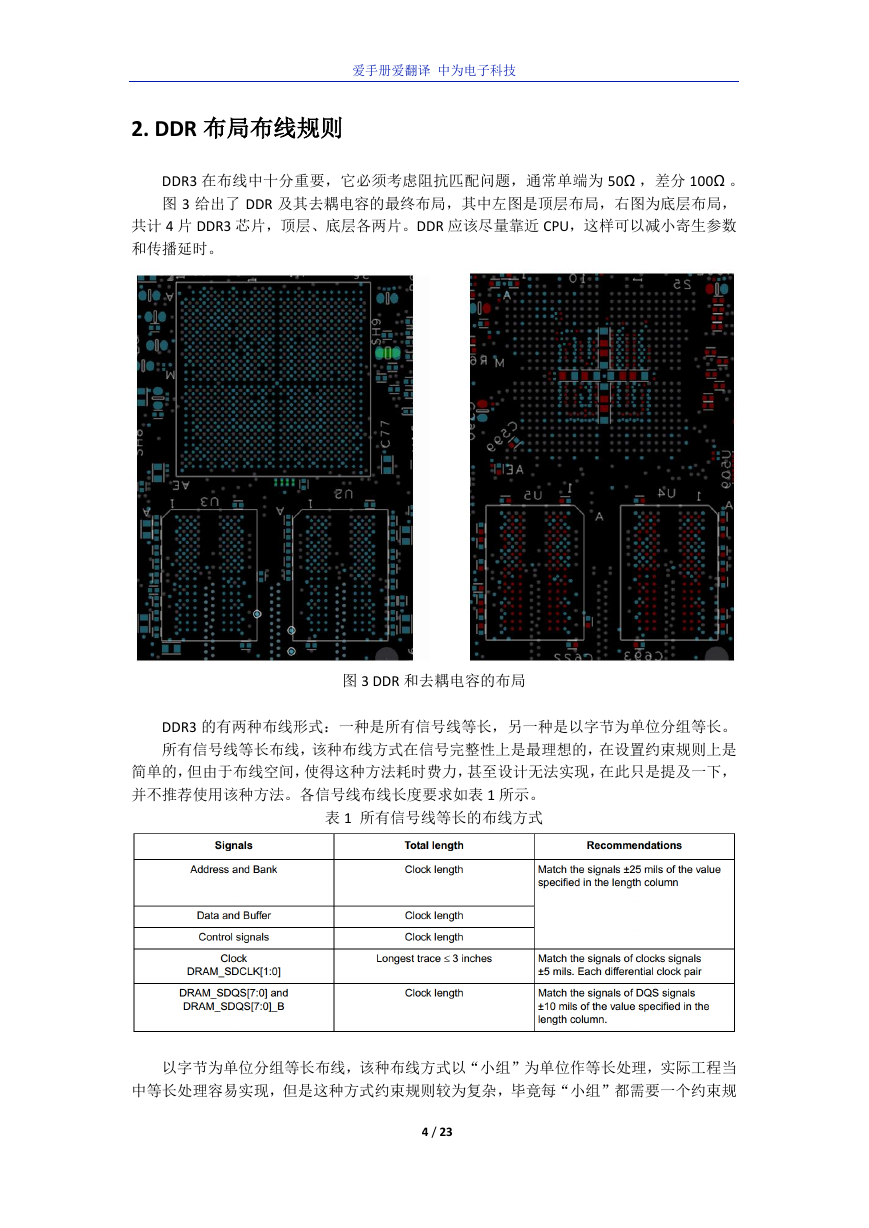

2. DDR 布局布线规则

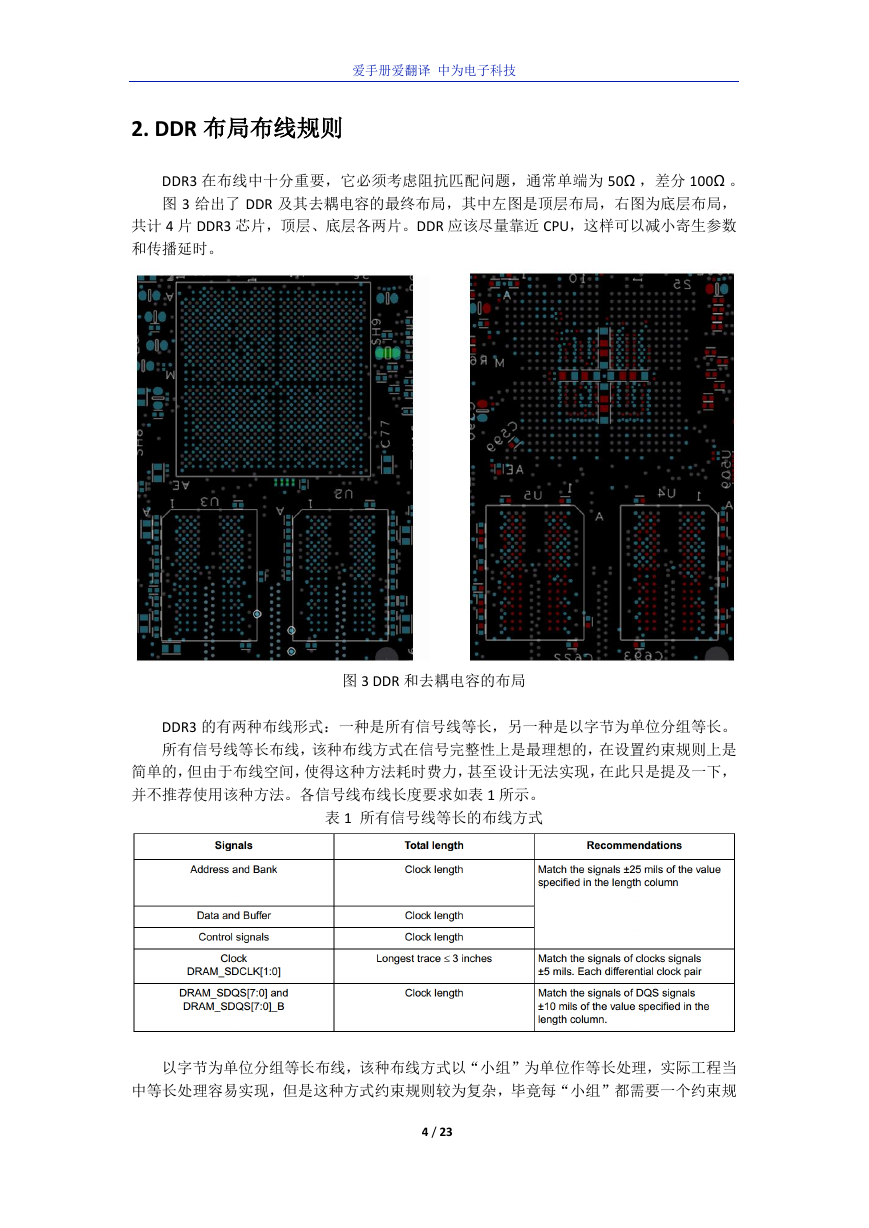

DDR3 在布线中十分重要,它必须考虑阻抗匹配问题,通常单端为 50Ω ,差分 100Ω 。

图 3 给出了 DDR 及其去耦电容的最终布局,其中左图是顶层布局,右图为底层布局,

共计 4 片 DDR3 芯片,顶层、底层各两片。DDR 应该尽量靠近 CPU,这样可以减小寄生参数

和传播延时。

图 3 DDR 和去耦电容的布局

DDR3 的有两种布线形式:一种是所有信号线等长,另一种是以字节为单位分组等长。

所有信号线等长布线,该种布线方式在信号完整性上是最理想的,在设置约束规则上是

简单的,但由于布线空间,使得这种方法耗时费力,甚至设计无法实现,在此只是提及一下,

并不推荐使用该种方法。各信号线布线长度要求如表 1 所示。

表 1 所有信号线等长的布线方式

以字节为单位分组等长布线,该种布线方式以“小组”为单位作等长处理,实际工程当

中等长处理容易实现,但是这种方式约束规则较为复杂,毕竟每“小组”都需要一个约束规

4 / 23

�

爱手册爱翻译 中为电子科技

则。表 2 给出了以字节为单位分组等长布线要求。

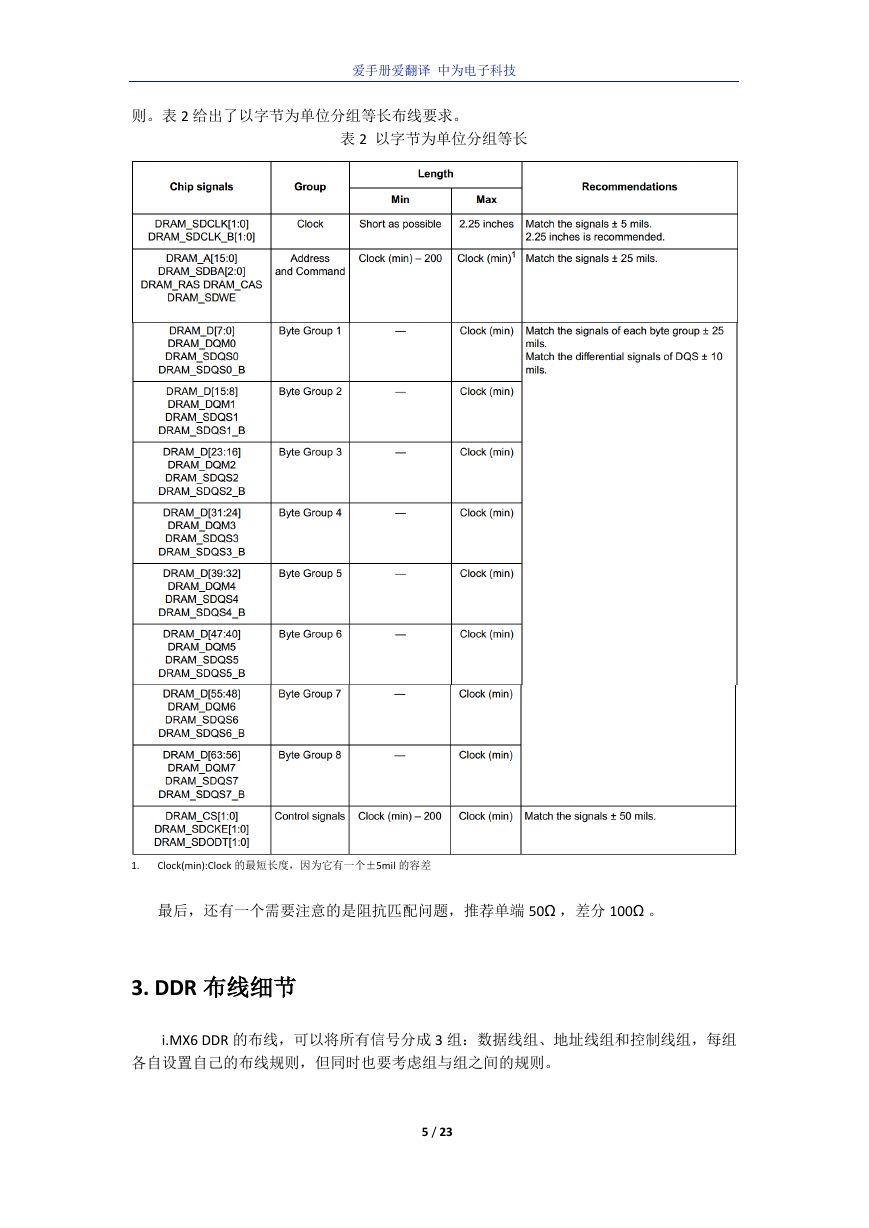

表 2 以字节为单位分组等长

1.

Clock(min):Clock 的最短长度,因为它有一个±5mil 的容差

最后,还有一个需要注意的是阻抗匹配问题,推荐单端 50Ω ,差分 100Ω 。

3. DDR 布线细节

i.MX6 DDR 的布线,可以将所有信号分成 3 组:数据线组、地址线组和控制线组,每组

各自设置自己的布线规则,但同时也要考虑组与组之间的规则。

5 / 23

�

爱手册爱翻译 中为电子科技

3.1 数据线的交换

在 DDR3 的布线中,可以根据实际情况交换数据线的线序,但必须保证是以字节为单位

(数据 0~7 间是允许交换线序,跨字节是不允许的),这样可以简化设计。

■ 布线尽量简短,减少过孔数量。

■ 布线时避免改变走线参考层面。

■ 数据线线序,推荐 D0、D8、D16、D24、D32、D40、D48、D56 不要改变,其它的

数据线可以在字节内自由调换(see the “Write Leveling” section in JESD79-3E)。

■ DQS 和 DQM 不能调换,必须在相应通道。

3.2 DDR3(64bits)T 型拓扑介绍

当设计采用 T 型拓扑结构,请确认以下信息。

■ 布线规则见上文表 2。

■ 终端电阻可以省略。

■ 布线长度的控制。

■ DDR 数量限制在 4 片以下。

3.3 DDR3(64bits)Fly-by 型拓扑介绍

当采用 Fly-by 的拓扑结构时,在设计中请注意以下事项。

■ DDR 控制器集成了地址镜像功能。

■ 终端电阻不可以省略。

3.4 2GB DDR 布局布线建议

4 片 DDR 共计 2GB 内存。

■ 保证 T 型拓扑的对称性。

■ 减少过孔,避免多次换层。

■ 禁止分割走线下的参考层。

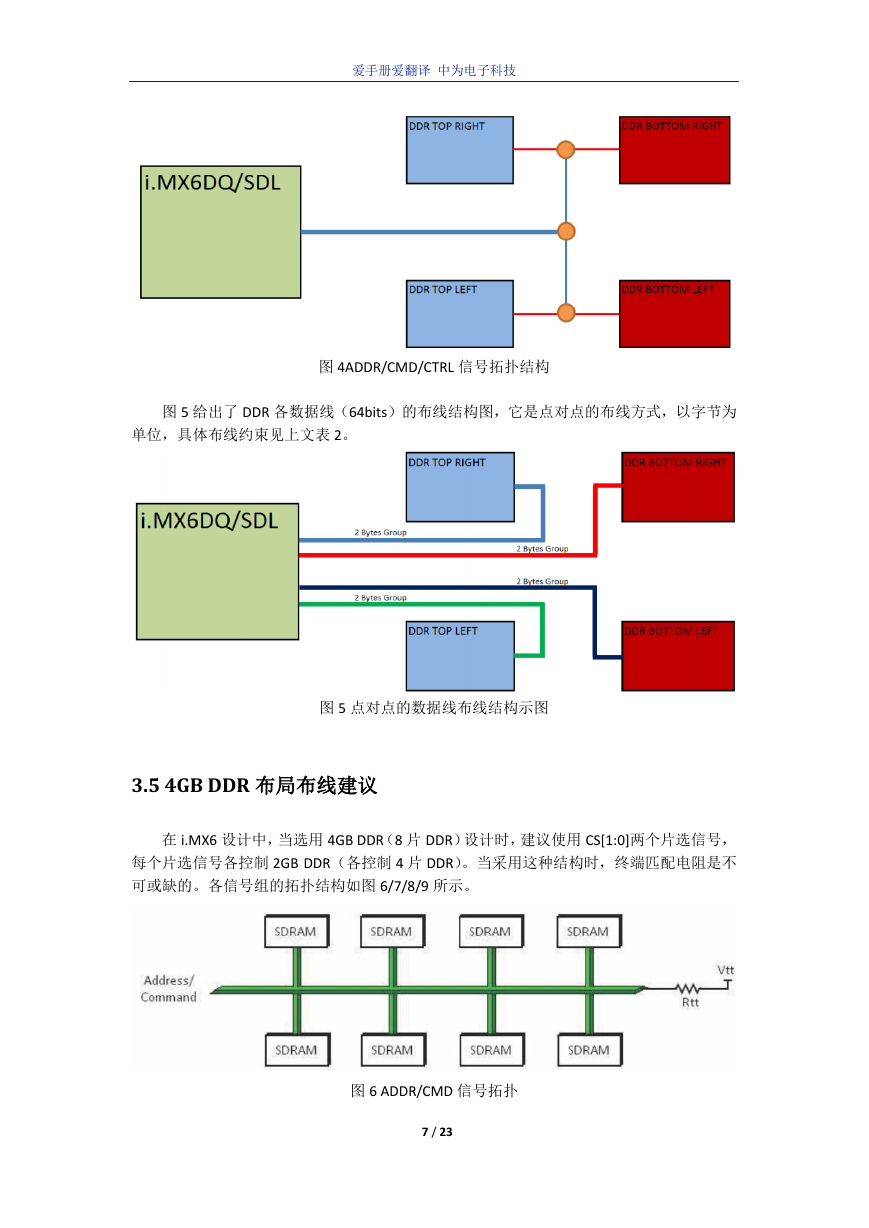

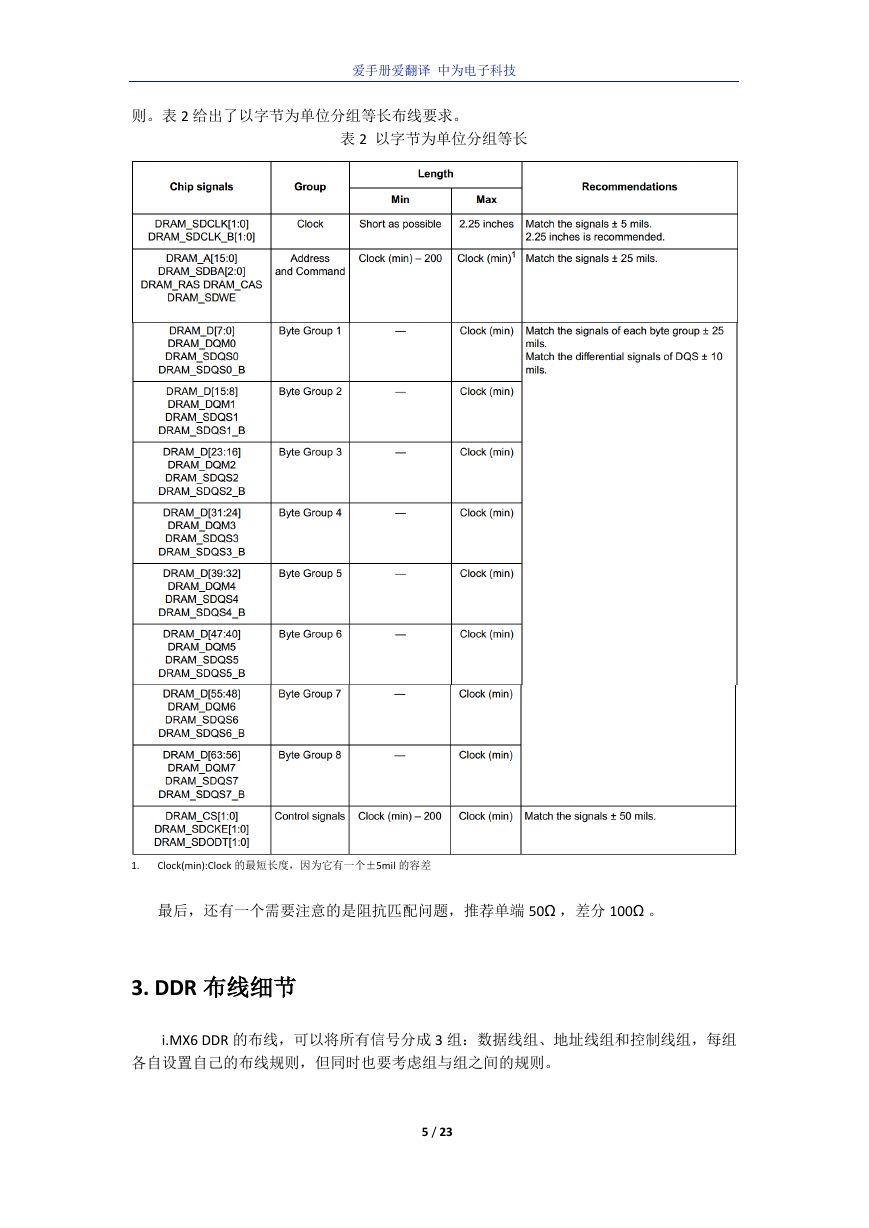

图 4 是 T 型拓扑的结构框图,在 i.MX6 设计中,ADDR/CMD/CTRL 信号会用到这种拓扑

结构。

6 / 23

�

爱手册爱翻译 中为电子科技

图 4ADDR/CMD/CTRL 信号拓扑结构

图 5 给出了 DDR 各数据线(64bits)的布线结构图,它是点对点的布线方式,以字节为

单位,具体布线约束见上文表 2。

图 5 点对点的数据线布线结构示图

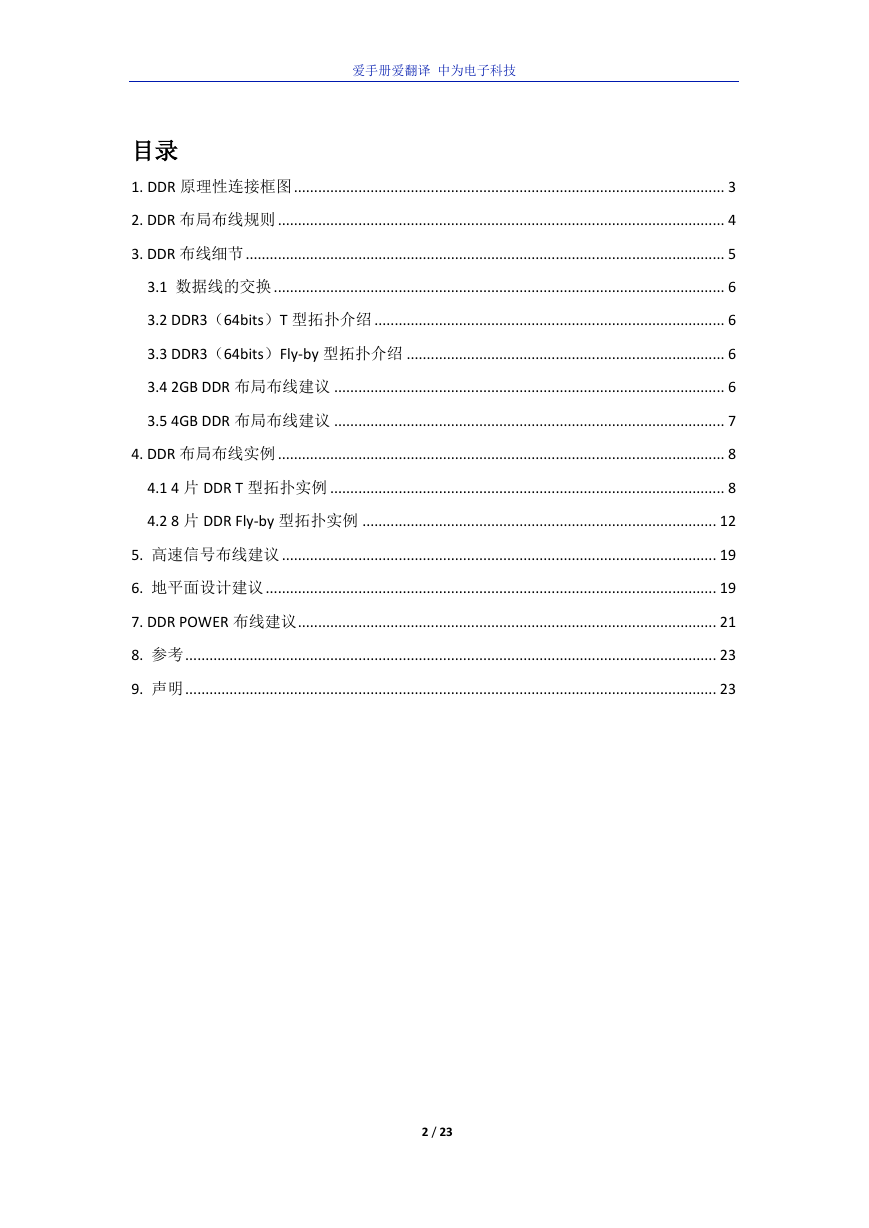

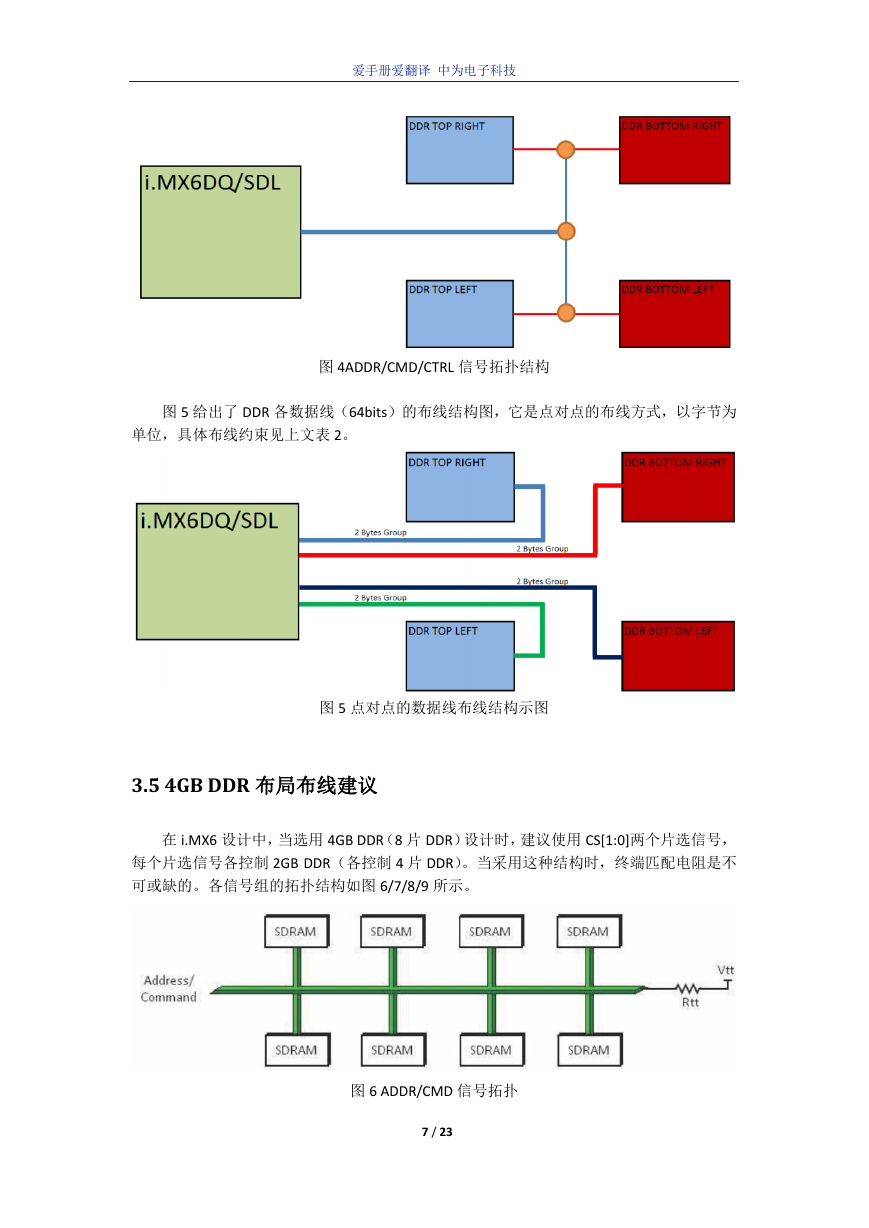

3.5 4GB DDR 布局布线建议

在 i.MX6 设计中,当选用 4GB DDR(8 片 DDR)设计时,建议使用 CS[1:0]两个片选信号,

每个片选信号各控制 2GB DDR(各控制 4 片 DDR)。当采用这种结构时,终端匹配电阻是不

可或缺的。各信号组的拓扑结构如图 6/7/8/9 所示。

图 6 ADDR/CMD 信号拓扑

7 / 23

�

爱手册爱翻译 中为电子科技

图 7 CTRL 控制信号拓扑

图 8 数据线拓扑

图 9 时钟线拓扑

4. DDR 布局布线实例

本节列出了 2 种布局布线方式,截图均出自官方 EVM 板。

4.1 4 片 DDR T 型拓扑实例

该例用了 4 片 DDR3,共计 2GB 内存,采用 T 型拓扑结构。具体说明见下文表 3 和图 10

/ 11 / 12。

8 / 23

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc