基于 FPGA 的图像采集系统设计与实现

时间:2009-03-06 09:01:14 来源:仪器仪表学报 作者:

1、引言

视频图像采集是视频信号处理系统的前端部分,正在向高速、高分辨率、高集成

化、高可靠性方向发展。图像采集系统在当今工业、军事、医学各个领域都有着极其广泛的

应用,如使用在远程监控、安防、远程抄表、可视电话、工业控制、图像模式识别、医疗器

械等各个领域都有着广泛的应用[1]。本文介绍了一种基于 FPGA 的图像采集系统,用户可

以根据需要对 FPGA 内部的逻辑模块和 I/O 模块重新配置,以实现系统的重构[1][2];而且

采用这种设计方案 ,便于及时地发现设计中的错误,能够有效地缩短研发时间,提高工作效

率。

2、系统的总体框架和工作原理

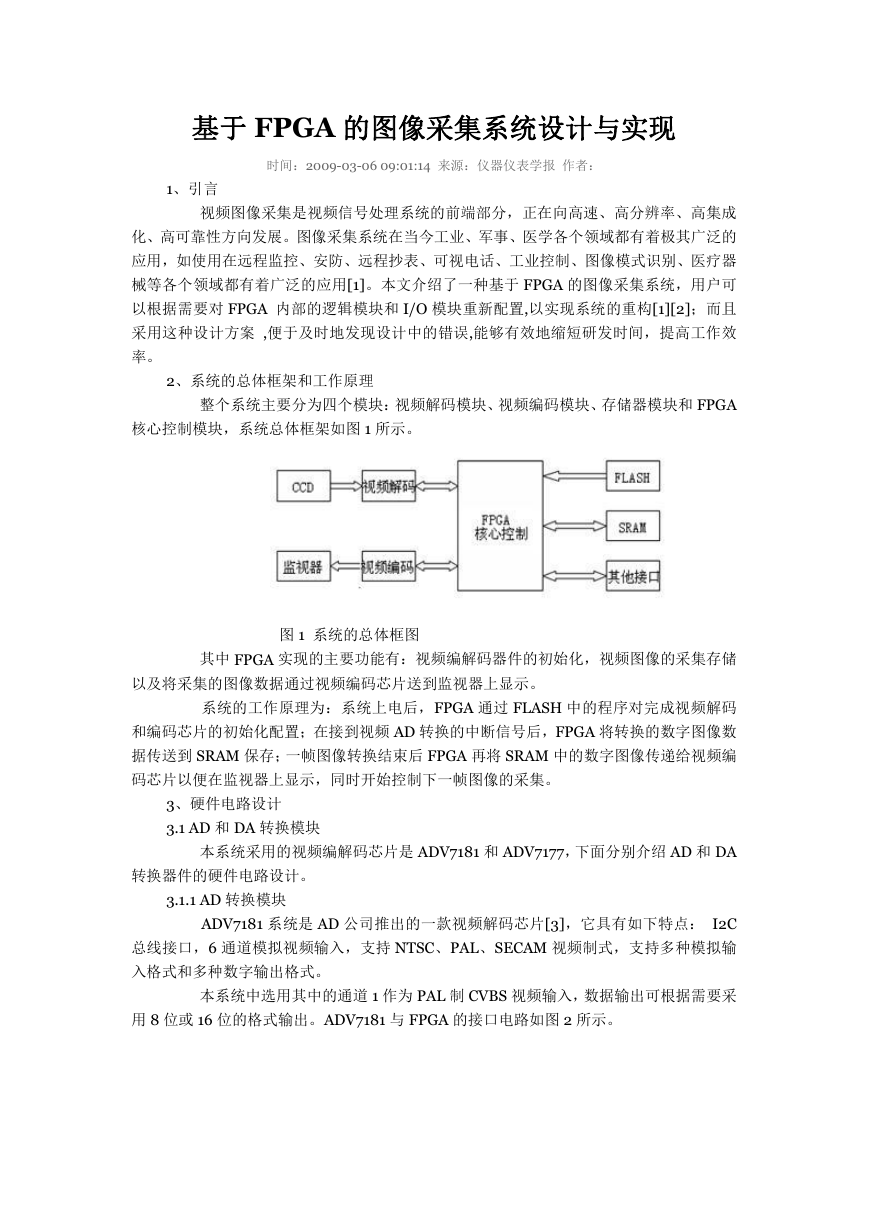

整个系统主要分为四个模块:视频解码模块、视频编码模块、存储器模块和 FPGA

核心控制模块,系统总体框架如图 1 所示。

图 1 系统的总体框图

其中 FPGA 实现的主要功能有:视频编解码器件的初始化,视频图像的采集存储

以及将采集的图像数据通过视频编码芯片送到监视器上显示。

系统的工作原理为:系统上电后,FPGA 通过 FLASH 中的程序对完成视频解码

和编码芯片的初始化配置;在接到视频 AD 转换的中断信号后,FPGA 将转换的数字图像数

据传送到 SRAM 保存;一帧图像转换结束后 FPGA 再将 SRAM 中的数字图像传递给视频编

码芯片以便在监视器上显示,同时开始控制下一帧图像的采集。

3、硬件电路设计

3.1 AD 和 DA 转换模块

本系统采用的视频编解码芯片是 ADV7181 和 ADV7177,下面分别介绍 AD 和 DA

转换器件的硬件电路设计。

3.1.1 AD 转换模块

ADV7181 系统是 AD 公司推出的一款视频解码芯片[3],它具有如下特点: I2C

总线接口,6 通道模拟视频输入,支持 NTSC、PAL、SECAM 视频制式,支持多种模拟输

入格式和多种数字输出格式。

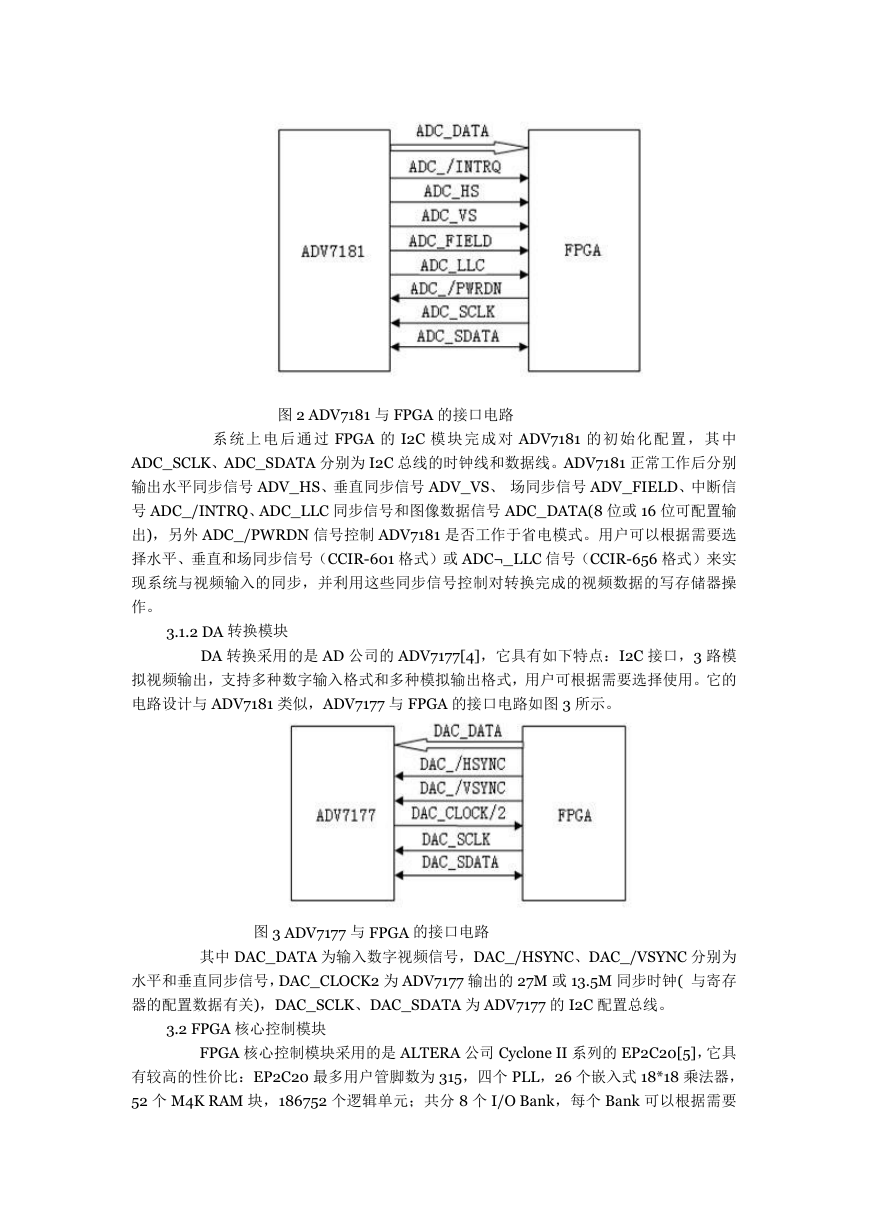

本系统中选用其中的通道 1 作为 PAL 制 CVBS 视频输入,数据输出可根据需要采

用 8 位或 16 位的格式输出。ADV7181 与 FPGA 的接口电路如图 2 所示。

�

图 2 ADV7181 与 FPGA 的接口电路

系 统 上 电 后 通 过 FPGA 的 I2C 模 块 完 成 对 ADV7181 的 初 始 化 配 置 , 其 中

ADC_SCLK、ADC_SDATA 分别为 I2C 总线的时钟线和数据线。ADV7181 正常工作后分别

输出水平同步信号 ADV_HS、垂直同步信号 ADV_VS、 场同步信号 ADV_FIELD、中断信

号 ADC_/INTRQ、ADC_LLC 同步信号和图像数据信号 ADC_DATA(8 位或 16 位可配置输

出),另外 ADC_/PWRDN 信号控制 ADV7181 是否工作于省电模式。用户可以根据需要选

择水平、垂直和场同步信号(CCIR-601 格式)或 ADC¬_LLC 信号(CCIR-656 格式)来实

现系统与视频输入的同步,并利用这些同步信号控制对转换完成的视频数据的写存储器操

作。

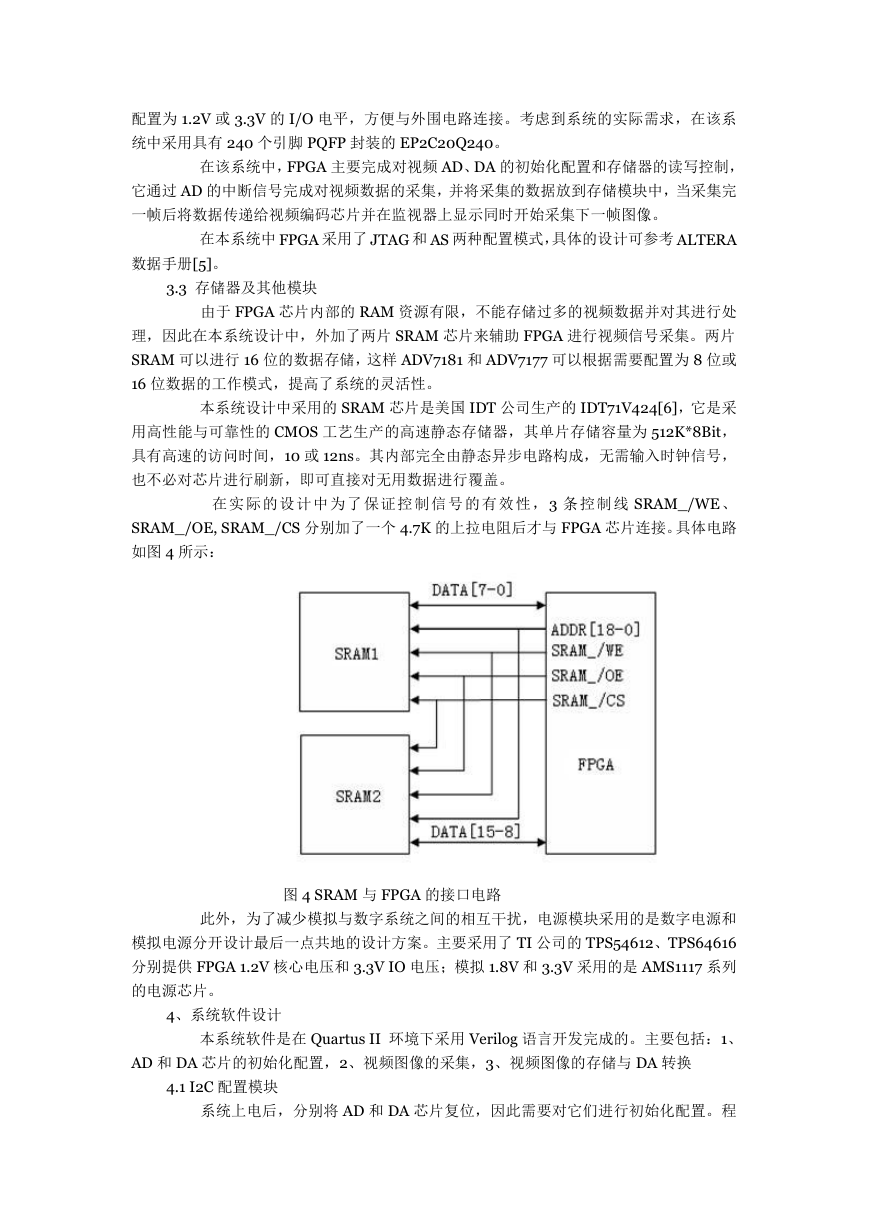

3.1.2 DA 转换模块

DA 转换采用的是 AD 公司的 ADV7177[4],它具有如下特点:I2C 接口,3 路模

拟视频输出,支持多种数字输入格式和多种模拟输出格式,用户可根据需要选择使用。它的

电路设计与 ADV7181 类似,ADV7177 与 FPGA 的接口电路如图 3 所示。

图 3 ADV7177 与 FPGA 的接口电路

其中 DAC_DATA 为输入数字视频信号,DAC_/HSYNC、DAC_/VSYNC 分别为

水平和垂直同步信号,DAC_CLOCK2 为 ADV7177 输出的 27M 或 13.5M 同步时钟( 与寄存

器的配置数据有关),DAC_SCLK、DAC_SDATA 为 ADV7177 的 I2C 配置总线。

3.2 FPGA 核心控制模块

FPGA 核心控制模块采用的是 ALTERA 公司 Cyclone II 系列的 EP2C20[5],它具

有较高的性价比:EP2C20 最多用户管脚数为 315,四个 PLL,26 个嵌入式 18*18 乘法器,

52 个 M4K RAM 块,186752 个逻辑单元;共分 8 个 I/O Bank,每个 Bank 可以根据需要

�

配置为 1.2V 或 3.3V 的 I/O 电平,方便与外围电路连接。考虑到系统的实际需求,在该系

统中采用具有 240 个引脚 PQFP 封装的 EP2C20Q240。

在该系统中,FPGA 主要完成对视频 AD、DA 的初始化配置和存储器的读写控制,

它通过 AD 的中断信号完成对视频数据的采集,并将采集的数据放到存储模块中,当采集完

一帧后将数据传递给视频编码芯片并在监视器上显示同时开始采集下一帧图像。

在本系统中 FPGA 采用了 JTAG 和 AS 两种配置模式,具体的设计可参考 ALTERA

数据手册[5]。

3.3 存储器及其他模块

由于 FPGA 芯片内部的 RAM 资源有限,不能存储过多的视频数据并对其进行处

理,因此在本系统设计中,外加了两片 SRAM 芯片来辅助 FPGA 进行视频信号采集。两片

SRAM 可以进行 16 位的数据存储,这样 ADV7181 和 ADV7177 可以根据需要配置为 8 位或

16 位数据的工作模式,提高了系统的灵活性。

本系统设计中采用的 SRAM 芯片是美国 IDT 公司生产的 IDT71V424[6],它是采

用高性能与可靠性的 CMOS 工艺生产的高速静态存储器,其单片存储容量为 512K*8Bit,

具有高速的访问时间,10 或 12ns。其内部完全由静态异步电路构成,无需输入时钟信号,

也不必对芯片进行刷新,即可直接对无用数据进行覆盖。

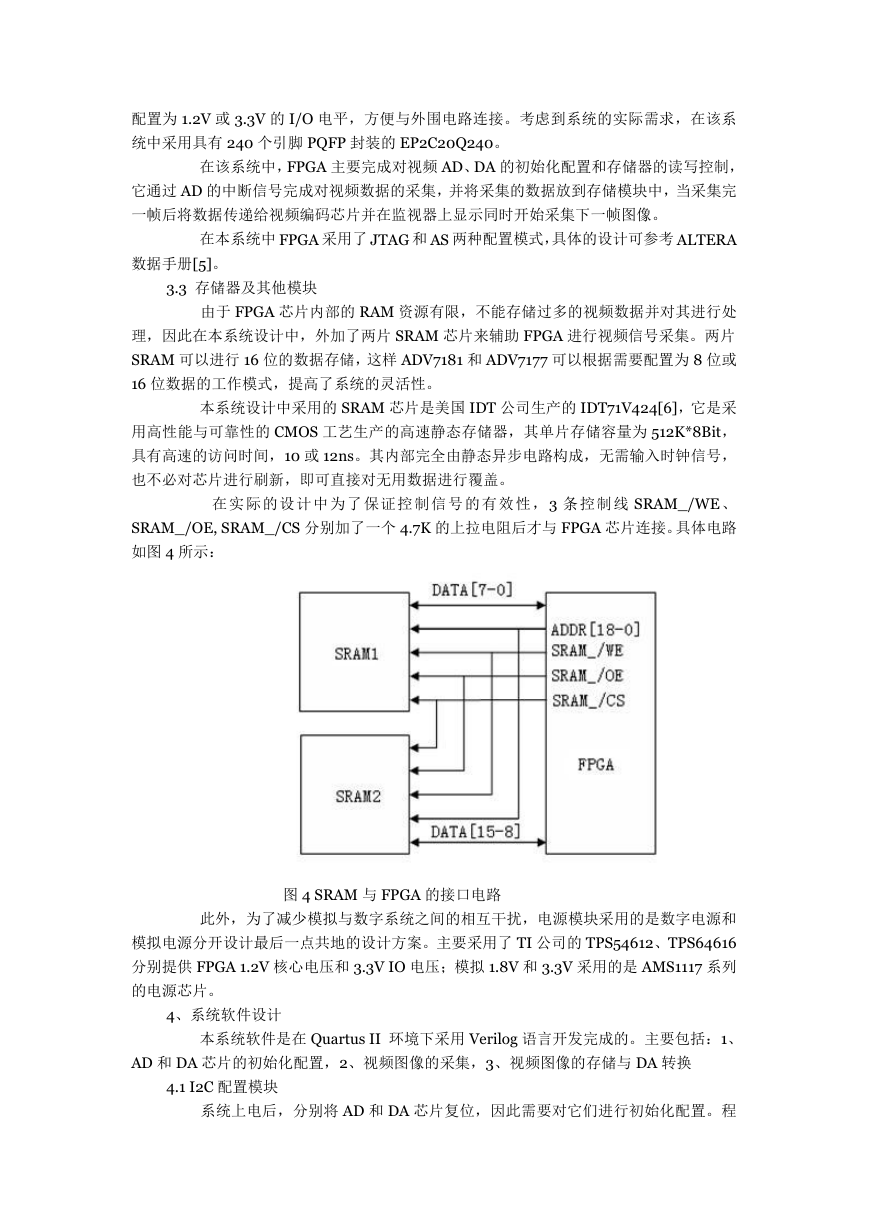

在 实 际 的 设 计 中 为 了 保 证 控 制 信 号 的 有 效 性 ,3 条 控 制 线 SRAM_/WE 、

SRAM_/OE, SRAM_/CS 分别加了一个 4.7K 的上拉电阻后才与 FPGA 芯片连接。具体电路

如图 4 所示:

图 4 SRAM 与 FPGA 的接口电路

此外,为了减少模拟与数字系统之间的相互干扰,电源模块采用的是数字电源和

模拟电源分开设计最后一点共地的设计方案。主要采用了 TI 公司的 TPS54612、TPS64616

分别提供 FPGA 1.2V 核心电压和 3.3V IO 电压;模拟 1.8V 和 3.3V 采用的是 AMS1117 系列

的电源芯片。

4、系统软件设计

本系统软件是在 Quartus II 环境下采用 Verilog 语言开发完成的。主要包括:1、

AD 和 DA 芯片的初始化配置,2、视频图像的采集,3、视频图像的存储与 DA 转换

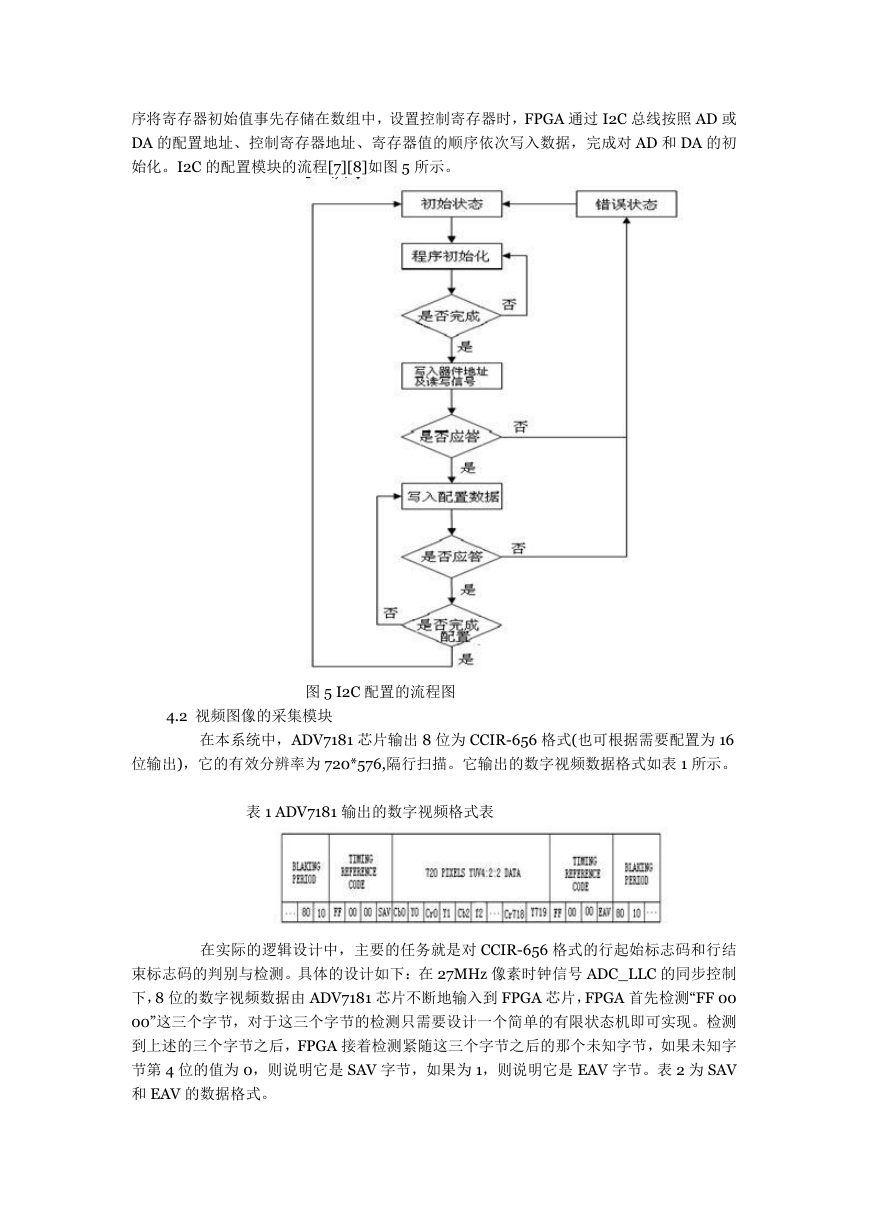

4.1 I2C 配置模块

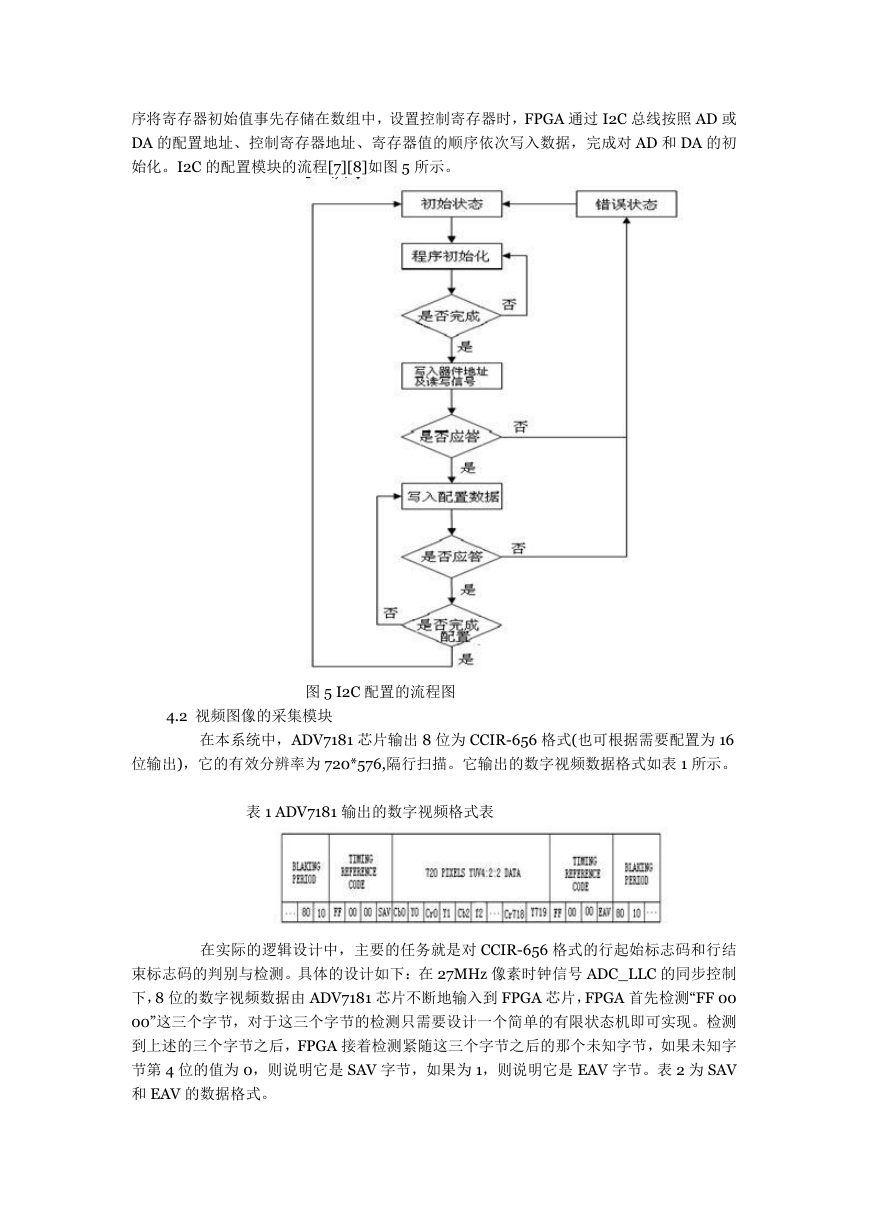

系统上电后,分别将 AD 和 DA 芯片复位,因此需要对它们进行初始化配置。程

�

序将寄存器初始值事先存储在数组中,设置控制寄存器时,FPGA 通过 I2C 总线按照 AD 或

DA 的配置地址、控制寄存器地址、寄存器值的顺序依次写入数据,完成对 AD 和 DA 的初

始化。I2C 的配置模块的流程[7][8]如图 5 所示。

图 5 I2C 配置的流程图

4.2 视频图像的采集模块

在本系统中,ADV7181 芯片输出 8 位为 CCIR-656 格式(也可根据需要配置为 16

位输出),它的有效分辨率为 720*576,隔行扫描。它输出的数字视频数据格式如表 1 所示。

表 1 ADV7181 输出的数字视频格式表

在实际的逻辑设计中,主要的任务就是对 CCIR-656 格式的行起始标志码和行结

束标志码的判别与检测。具体的设计如下:在 27MHz 像素时钟信号 ADC_LLC 的同步控制

下,8 位的数字视频数据由 ADV7181 芯片不断地输入到 FPGA 芯片,FPGA 首先检测“FF 00

00”这三个字节,对于这三个字节的检测只需要设计一个简单的有限状态机即可实现。检测

到上述的三个字节之后,FPGA 接着检测紧随这三个字节之后的那个未知字节,如果未知字

节第 4 位的值为 0,则说明它是 SAV 字节,如果为 1,则说明它是 EAV 字节。表 2 为 SAV

和 EAV 的数据格式。

�

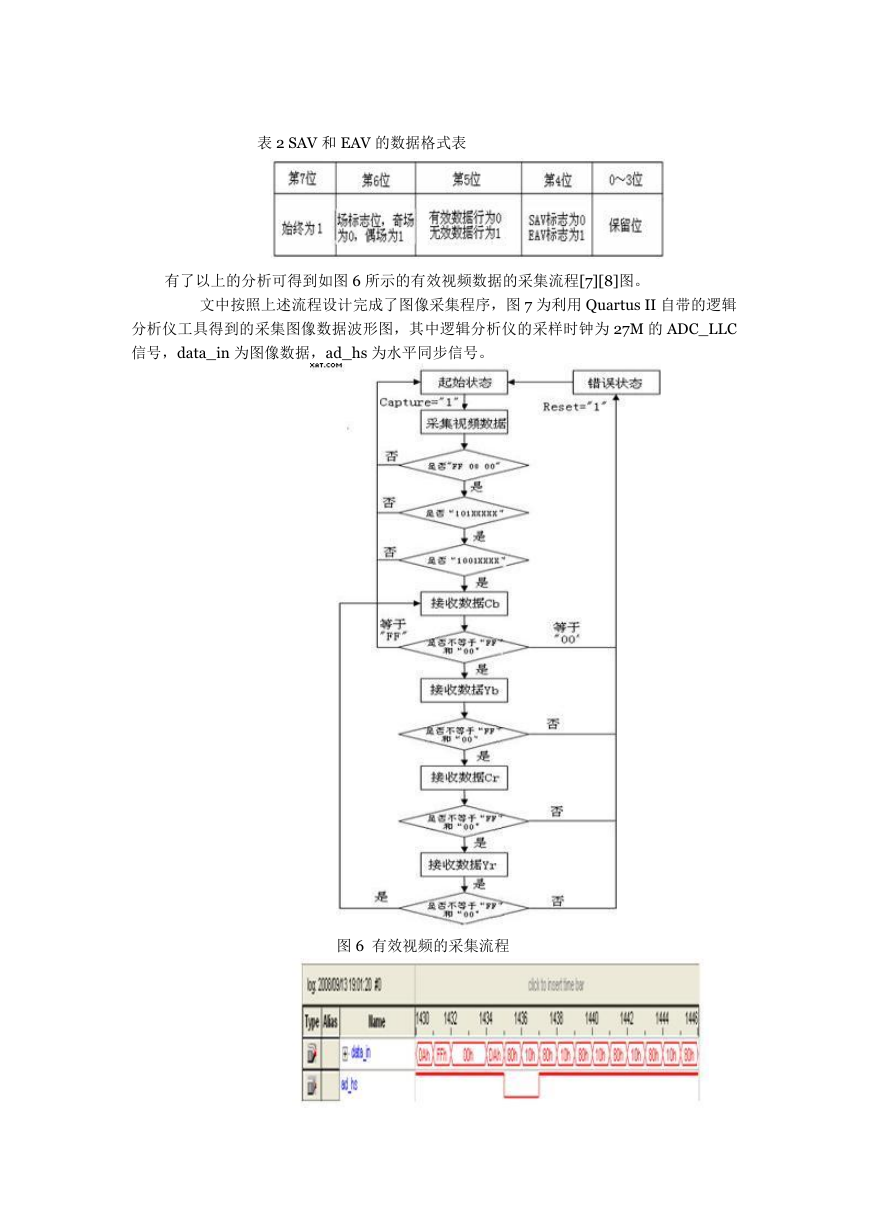

表 2 SAV 和 EAV 的数据格式表

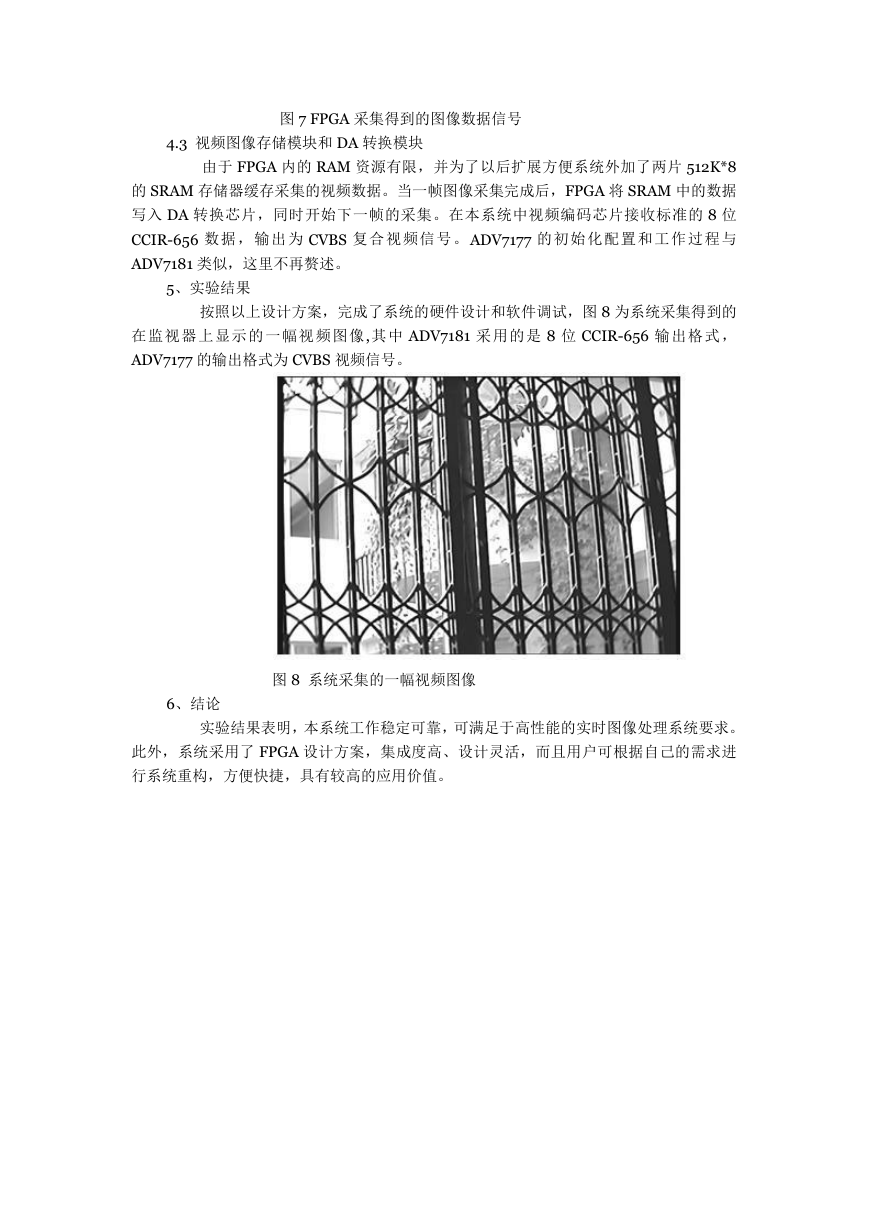

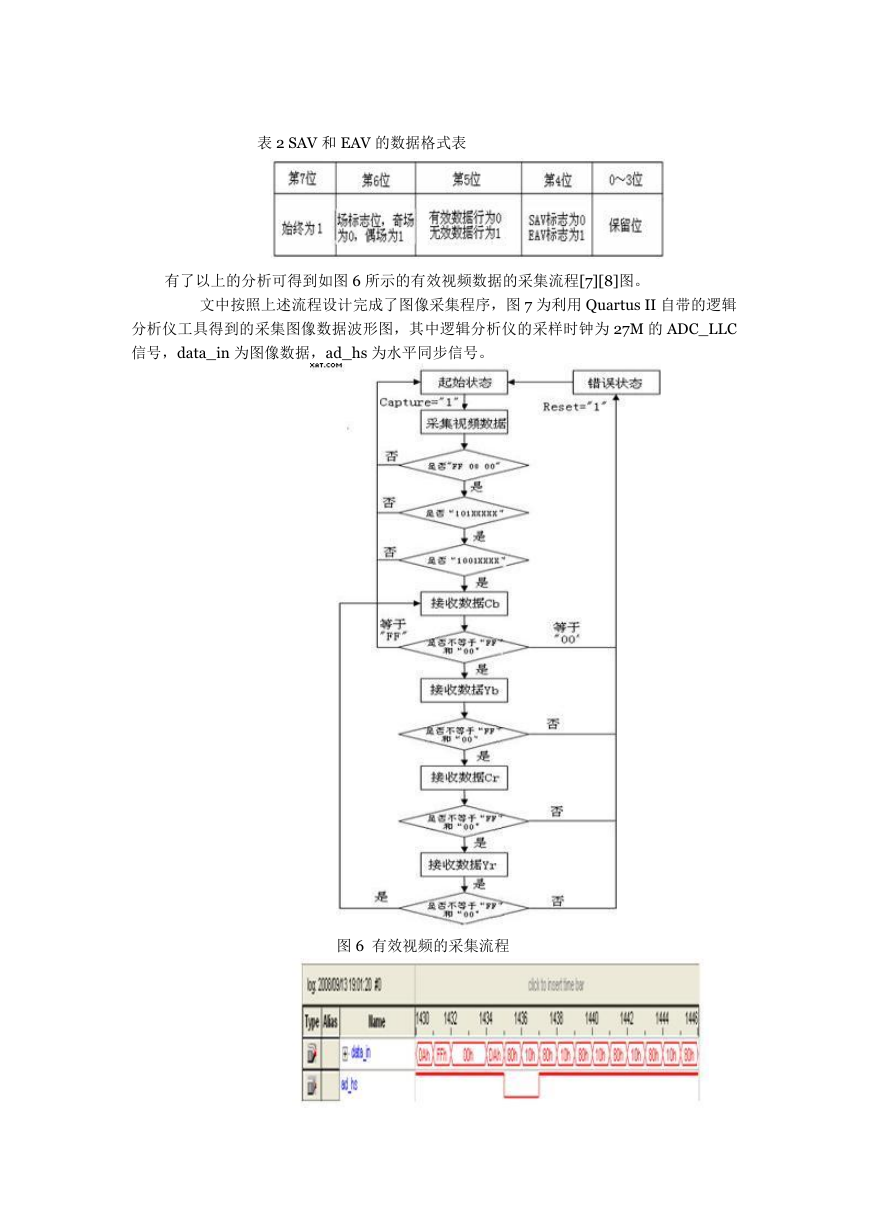

有了以上的分析可得到如图 6 所示的有效视频数据的采集流程[7][8]图。

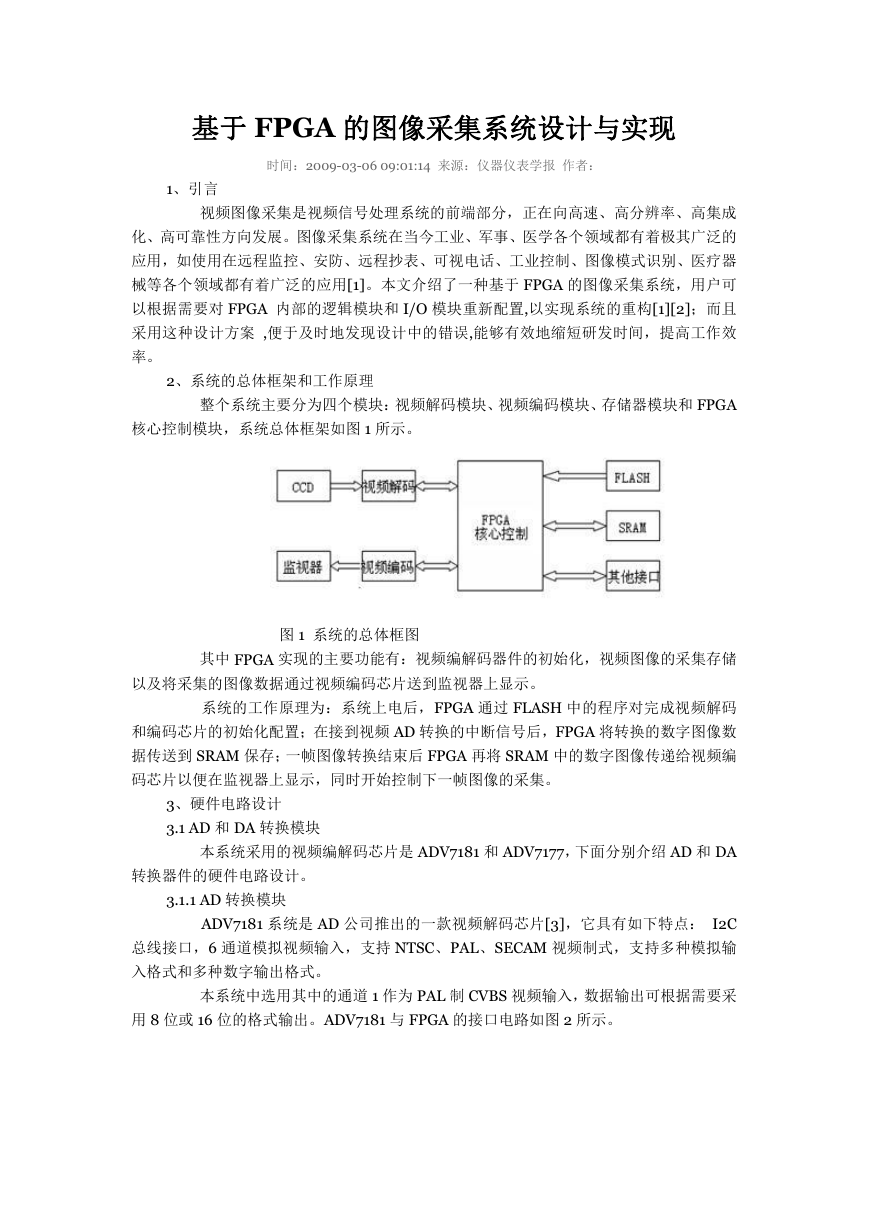

文中按照上述流程设计完成了图像采集程序,图 7 为利用 Quartus II 自带的逻辑

分析仪工具得到的采集图像数据波形图,其中逻辑分析仪的采样时钟为 27M 的 ADC_LLC

信号,data_in 为图像数据,ad_hs 为水平同步信号。

图 6 有效视频的采集流程

�

图 7 FPGA 采集得到的图像数据信号

4.3 视频图像存储模块和 DA 转换模块

由于 FPGA 内的 RAM 资源有限,并为了以后扩展方便系统外加了两片 512K*8

的 SRAM 存储器缓存采集的视频数据。当一帧图像采集完成后,FPGA 将 SRAM 中的数据

写入 DA 转换芯片,同时开始下一帧的采集。在本系统中视频编码芯片接收标准的 8 位

CCIR-656 数 据 , 输 出 为 CVBS 复 合 视 频 信 号。ADV7177 的 初 始 化 配 置和 工 作 过 程 与

ADV7181 类似,这里不再赘述。

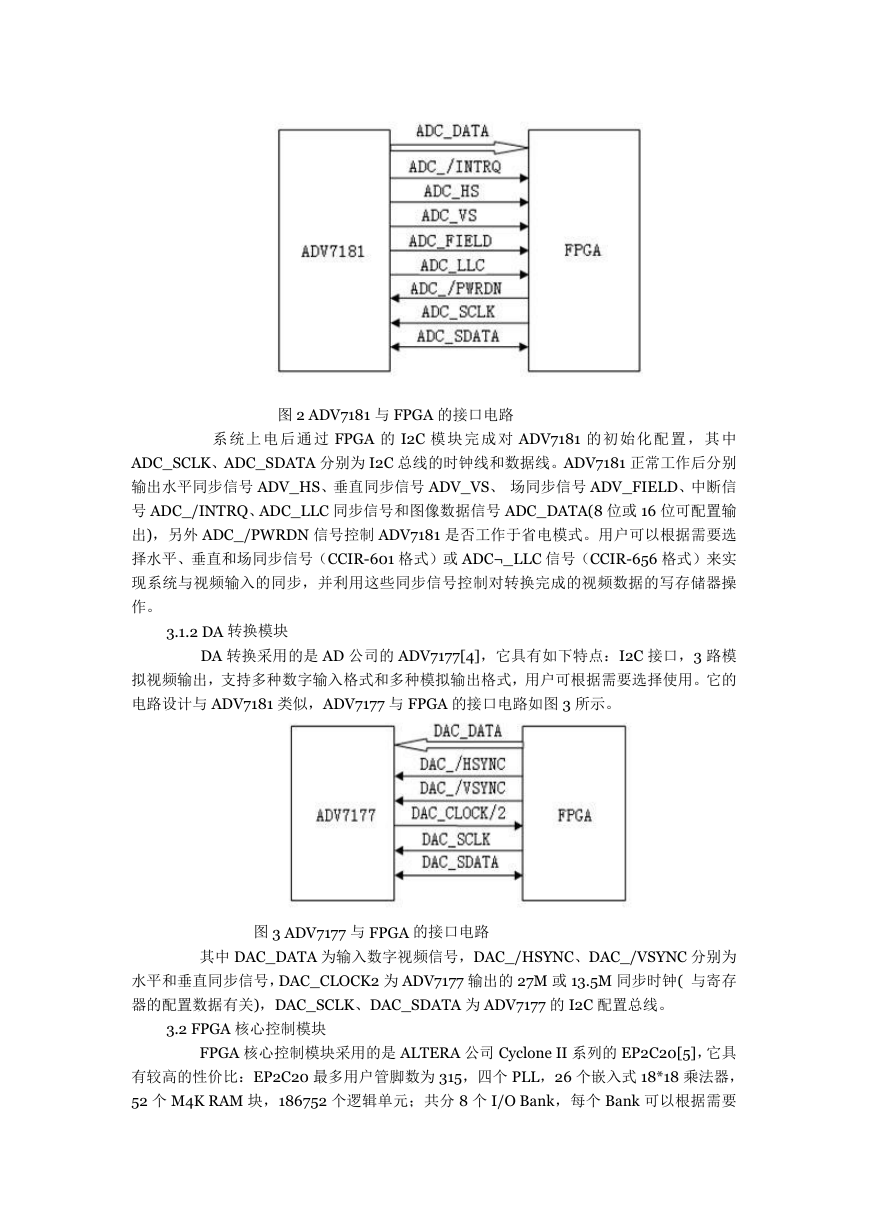

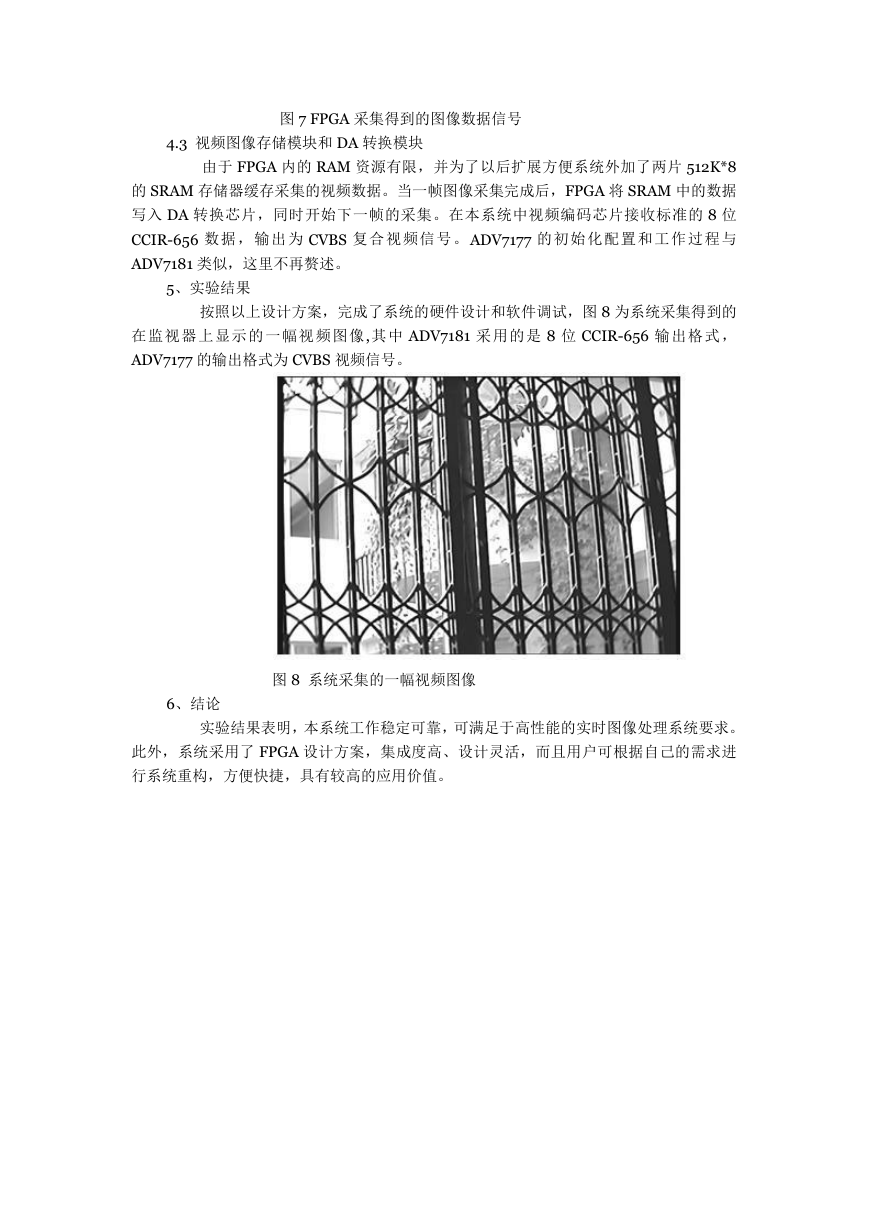

5、实验结果

按照以上设计方案,完成了系统的硬件设计和软件调试,图 8 为系统采集得到的

在 监视 器 上 显示 的 一 幅视 频 图 像,其 中 ADV7181 采 用的 是 8 位 CCIR-656 输 出格 式 ,

ADV7177 的输出格式为 CVBS 视频信号。

图 8 系统采集的一幅视频图像

6、结论

实验结果表明,本系统工作稳定可靠,可满足于高性能的实时图像处理系统要求。

此外,系统采用了 FPGA 设计方案,集成度高、设计灵活,而且用户可根据自己的需求进

行系统重构,方便快捷,具有较高的应用价值。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc