中国科技论文在线

http://www.paper.edu.cn

10G-EPON OLT 侧高速同步器的设计和实

现#

韩卫平,张民**

5

(北京邮电大学信息光子学与光通信研究院国家重点实验室,北京 100876)

摘要:高速同步器是在接收端检测同步帧的模块。根据 10G-EPON 标准 IEEE 802.3av 有关

OLT 端高速同步器的相关规定,设计高速同步器的难点在于 66 位序列汉明距的计算。本文

通过对高速同步器的关键部分汉明距计算电路的分析,提出了一种基于流水寄存求和网络法

的高速同步器设计方案并对比分析了求和网络法和 RAM-求和网络法实现高速同步器的性

能。最后用 Verilog 在 FPGA 上实现了光线路终端(OLT)端高速同步器,给出了波形仿真性

能、可工作频率和占用 FPGA 资源的统计结果。经 ModelSim 仿真验证,数据速率可达到

13.2Gbit/s,满足 10G-EPON 的系统要求。

关键词:10G-EPON;OLT;高速同步器;汉明距离;FPGA

中图分类号:TN913.7

10

15

Design and Implementation of High Speed Synchronizer at

OLT in 10G-EPON

Han Weiping, Zhang Min

20

(State Key Laboratory of IPOC, Beijing University of Posts and Telecommunications,Beijing

100876)

25

30

Abstract: High-speed Synchronizer is the module of detecting the synchronous frame at the

receiving terminal. According to the relevant contents of high-speed synchronizer at the Optical

Line Terminal (OLT) in 10G-EPON standard IEEE 802.3av,the difficulty in the design of

high-speed synchronizer depends on 66 bit-sequences Hamming distance calculation. In this paper,

via analyzing hamming distance calculation circuit, the key part of high-speed synchronizer,a

scheme of high-speed synchronizer based on sum-network method with pipelining registers is

proposed and the performance is analyzed compared with the sum-network and RAM-sum

network methods. High-speed synchronization at the OLT is implemented using Verilog on FPGA.

The simulation performance, the statistical results of the frequency and occupied FPGA resources

are given. Through simulation with ModelSim, the data rate can be achieved to 13.2Gbit/s which

can meet the 10G-EPON system requirements.

Key words: 10G-EPON; OLT; High-speed Synchronizer; Hamming Distance; FPGA

0 引言

35

随着互联网技术的蓬勃发展,用户对接入带宽的需要呈爆炸式增长,现有的 EPON 技

术无法满足更高的带宽需求,光网络的发展遇到了瓶颈。为了满足更高的带宽需求、更高的

传输速率、更高的组网能力和兼容性,下一代光接入网 10G-EPON(Ethernet Passive Optical

Network)作为主要的宽带光接入技术备受关注[1-3]。经过三年多的研究工作,2009 年 10 月

30 日,IEEE 正式批准发布了 10G-EPON 标准 IEEE 802.3av。10G-EPON 的关键技术,诸如

40

高速同步技术、高速 FEC 编解码技术、动态带宽分配机制、高速信号完整性和大容量转发

延时等问题亟待解决[2]。上行 10G 的速率,对 OLT 端的接收技术提出了更高的要求,OLT

基金项目:国家自然科学基金(No.61072008)

作者简介:韩卫平(1984-),女,硕士,大容量光通信系统与网络、宽带接入网

通信联系人:张民(1974-),男,教授,主要研究方向:大容量光通信系统与网络、宽带接入网. E-mail:

mzhang@bupt.edu.cn

- 1 -

�

中国科技论文在线

http://www.paper.edu.cn

端必须在短时间内对来自 ONU 的数据进行发现、判决、同步和接收,高速同步器的性能直

接影响整个 OLT 端对上行数据处理的能力,标准中阐述了光线路终端(OLT)用户端和光网络

单元(ONU)的数据流的同步原理,但没有具体的实现方案。

45

针对不同的系统,有不同的同步检测方案[4-7]。对于 10G-EPON 上行 10G 比特的速率,

ONU 端工作在突发模式,每一帧数据前后加上特殊的码组作为头尾标记。高速同步器的设

计难点就在于快速的进行帧同步,检测头帧和尾帧的方法即计算接收到的数据与帧头帧尾的

汉明距。因而高效的汉明距计算电路是直接影响高速同步器的关键因素,特别在数据速率很

高的情况下,汉明距的计算能力无疑就成为了高速同步系统的瓶颈。目前,计算汉明距的方

法有计数法、逻辑函数法、查找表法和求和网络法等[8]。

50

本文在对求和网络法和查找表法两种方法实现 66 位高速数据流汉明距计算电路分析的

基础上,提出了一种更好的采用流水寄存求和网络法实现高速同步器的方案,不仅实现简单,

而且工作效率高,并结合 10G-EPON 标准用 Xilinx 公司的现场可编程门阵列(FPGA)通过

Verilog HDL 进行仿真分析。

55

1 10G-EPON OLT 端数据帧同步方案

根据 IEEE 802.3av 的建议, OLT 端对接收到的高速数据流实现帧同步的主要思想是计

算收到的数据流的码字与突发定界符(BD,BURST DELIMITER)的汉明距,通过汉明距衡量

它们的相似程度,当汉明距小于一定的门限条件时,即可判断系统进入同步状态。类似地,

在系统同步后,开始计算接收到的数据流码字与帧结束定界符(EOB,End Burst Delimiter)

60

的汉明距,当汉明距小于设定的门限达到设定的次数后,可判断一帧数据结束,系统进入失

步状态,重新检测下一帧的起始定界符。

图 1 检测电路

Fig. 1 Detecting Circuit

65

图 1 是 66 位数据汉明距的检测电路原理图。设

是待检测 66 位数据,

是位宽 66 位的帧同步头,

是

与

的比较结果。计算出汉明距就

是检测出

中比特“1”的个数。

10G-EPON 物理编码子层(PCS)上行数据传输过程如图 2 所示[1],ONU 端数据经过 PCS

层的带宽调整、64B/66B 编码、扰码、前向纠错(FEC)编码和变速箱(GEAR BOX)进入到物

70

理介质连接(PMA)子层,再经过物理媒质相关(PMD)子层将数据送到光纤链路上进行传输,

当数据到达 OLT 端,数据经过 PMD 层进入到 PMA 层,来自 PMA 层的数据,通过 16 路

到 66 路的变换,将 66 位的高速数据送入高速同步器进行帧同步检测,同步后的数据经过

FEC 解码、解扰、64B/66B 解码和带宽调整进入到 10Gb 介质无关接口(XGMII)接口。ONU

端突发模式发送的帧数据格式如图 3 所示,每一帧以突发定界符(BD)开始,然后是有效的

- 2 -

S[65:0]BD[65:0]D[65:0]S[65:0]BD[65:0]D[65:0]�

中国科技论文在线

http://www.paper.edu.cn

75

FEC 码字,在若干个 FEC 码字后以结束定界符(EOB)结束数据帧。

图 2 PCS 层上行数据传输过程框图

Fig. 2 Block diagram of upstream data transmission in PCS

80

图 3 上行传输的数据帧格式

Fig. 3 Frame format of upstream data transmission

高速同步过程流程图如图 4 所示。系统上电后,在时钟 上升沿采样,检测到复位信

号 为高电平时,复位整个系统,同时输出数据为 0,同步状态指示信号 Cw_lock 输出为

0。当复位信号为低电平时,进入同步检测过程,在同步状态锁定指示信号

为 0

85

时,首先缓存三个时钟节拍的数据,然后检测数据与

的汉明距离,如图 5 所示,

先缓存 3 个周期的数据,在缓存第三个周期的数据时并对已经缓存的

数据

的数据同时进行帧同步头检测,要在一个时钟节拍内完成,

,

,

, … ,

在同一时间分别和 异或相加,然后送入汉明距计算电路,当检

90

测到任一组数据与 的汉明距离小于设定的门限值 12 时,系统进入同步锁定状态,并锁

定同步位置

。当系统进入同步状态后,系统输出同步后的数据,同时输出同步状

态 指 示 信 号

为 1 。 图 5 中 假 设 锁 定 同 步 位 置 为 第 6 位 , 则 输 出

的 数 据 , 然 后 将

的 数 据 移 位 到

的位置。在系统同步锁定成功后,开始进行

的检测。当检测到

95

数据与

的汉明距离小于 11 时,计数器

加 1,当计数器加到 3(本文中

帧结束定界符

为 3 组 66bit 数据)时,系统进入失步状态,帧结束指示信号

有效,指示为 1,同时复位

为 0,一帧数据结束。系统重新接收下一帧数据进行

同步检测。

- 3 -

clkrstBD_validBDbuffer_block[197:0]buffer_block[130:0]buffer_block[65:0]buffer_block[66:1]buffer_block[67:2]buffer_block[130:65]BDBDmove_cntCw_lockbuffer_block[137:72]buffer_block[197:138]buffer_block[131:72]EOBEOBEOB_valid_cntEOBEOB_validBD_valid�

中国科技论文在线

http://www.paper.edu.cn

100

图 4 高速同步流程 图 5 同步位置锁定过程

Fig.4 Flowchart of high-speed synchronization Fig.5 Locking process of synchronous position

2 66 位高速数据汉明距计算电路设计

高速同步器的核心模块是 66 位汉明距离的计算电路。汉明距计算的原理是统计两个码

字异或后结果中“1”的个数。在 FPGA 中,异或运算比较容易实现,如何统计 1 的个数是

105

技术难点,本文在研究前两种方案的基础上提出了第三种方案来计算 66 位二进制序列的汉

明距。

2.1 无流水寄存求和网络法

设

为要计算的 66 位数据,

为求出的 66 位汉明距。最简单的计

算 66 位汉明距的方法是在 FPGA 中直接利用加法器将 66 位直接相加, 即:

110

(2-1)

完成计算要用 65 个加法器。

求和网络法对上述算法进行优化,减小算数表达式树高度,从而减小组合逻辑长度,提

高系统工作频率。

(2-2)

115

从公式上看完成计算也要用 65 个加法器,但在 FPGA 中综合工具综合出的电路级数会

大大减少。可以减少关键路径长度,节省系统延时。下面以 4 位加法来说明算术表达式树高

度优化方法[10]。设

(2-3-a)

(2-3- b)

120

对于式(2-3-a),等价的算术表达式树如图 6(a)所示,表达式树包含 3 个加法器,树高度

为 3 个加法器;对于式(3-3-b),是优化后的表达式,等价的算术表达式树如图 6(b)所示,显

然树高度减小为两个加法器,从而减小了组合逻辑的路径长度。

125

Fig. 6 Optimization of the high degree of arithmetic expression tree

图 6 算术表达式树高度优化

- 4 -

D[65:0]SUM_D[6:0]SUM_D[6:0]=D[0]+D[1]+D[2]++D[64]+D[65]SUM_D[6:0]=(((D[0]+D[1])+(D[2]+D[3]))+((D[4]+D[5])++(D[64]+D[65])))1;xabcd2()();xabcd�

中国科技论文在线

http://www.paper.edu.cn

图 7 为采用无流水寄存求和网络法计算 66 位序列汉明距电路图,即完全采用加法器来计算,

并采用了上述的优化算法。

130

Fig.7 Sum-network method without pipelining registers

2.2 查找表-求和网络法,又可以称之为 RAM-求和网络法

图 7 无流水寄存求和网络法

BLOCK RAM 资源是 FPGA 的 IP 核。IP 核能够大幅度减少设计的工作量,避免重复设

计,缩短工程时间,提高工作质量和效率[10]。根据 Xilinx 的 FPGA 器件特点和结构,为了

充分发挥 FPGA 的功能,我们采用 BLOCK RAM 来实现汉明距的计算。Virtex-5 FPGA 的

135

BLOCK RAM 可以配置为 2 个独立的 18Kb 的 RAM 或者一个 36Kb 的 RAM,每个 36Kb 的

BLOCK RAM 又可以配置成一个 64K×1 (当与 36 Kb 的 BLOCK RAM 级联时),32K×1,

16K×2, 8K×4, 4K×9,2K×18,或者 1K×36 的存储器。每个 18 Kb 的 BLOCK RAM 又可

以配置成一个 16K×1, 8K×2 ,4K×4, 2K×9, 或者 1K×18 的存储器。在本文中我们将

FPGA 的 18Kb BLOCK RAM 配置为 4K×4 的存储器。

140

图 8 为采用 RAM-求和网络法的 66 位序列汉明距离计算电路原理图。为了充分利用

Virtex-5 FPGA 内的存储器资源,将 66 位序列等分为 6 段,每一段采用 BLOCK RAM 计算

汉明距,每个 RAM 的存储深度为

,地址线的宽度为 11,每个存储单元的数据宽

度为 4,则每个 RAM 的存储容量为

,总的存储器容量为

,求和网络中加

法器总数为 5。

145

RAM-求和网络法采用 FPGA 的 IP 核资源计算汉明距,节省了硬件的逻辑资源,提高了工作

效率。

图 8 RAM-求和网络法

Fig. 8 RAM sum-network method

- 5 -

1122048112411246�

中国科技论文在线

150

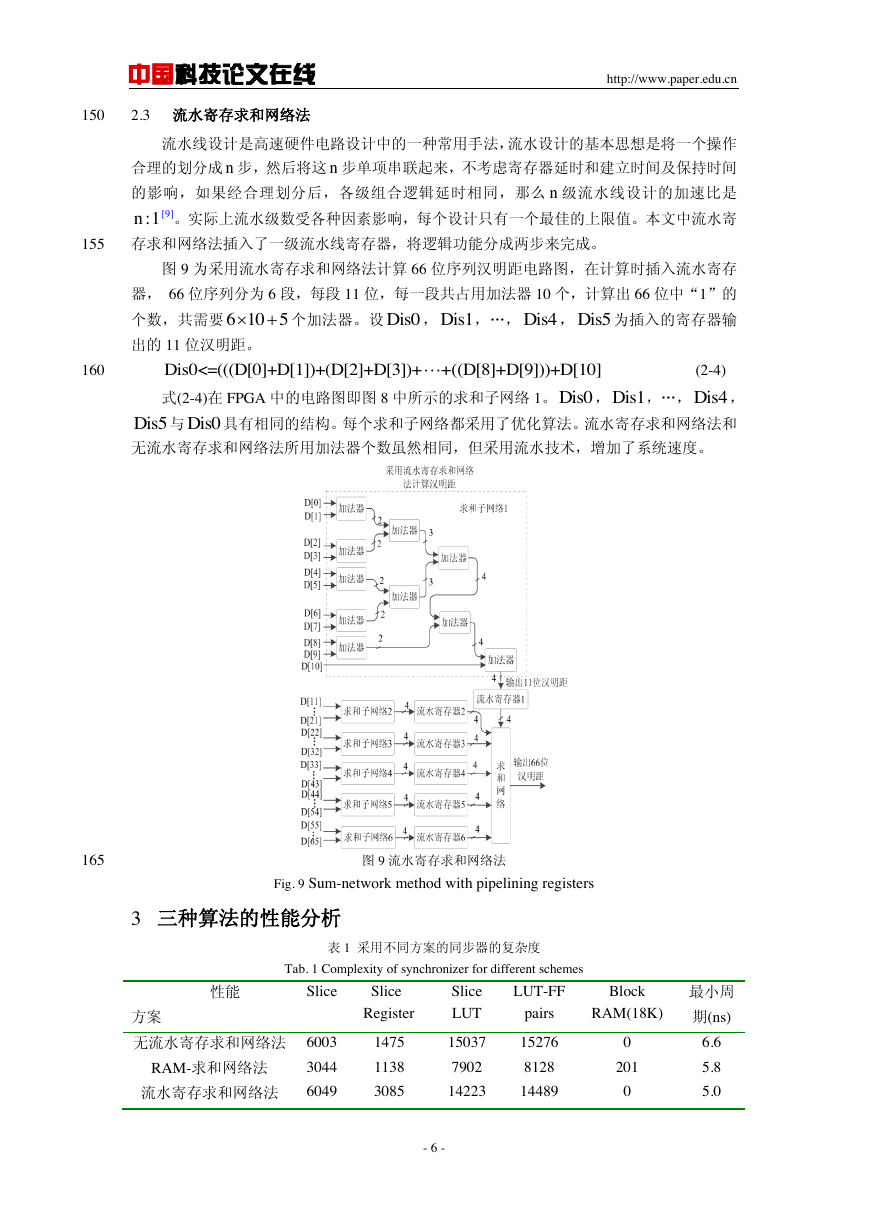

2.3 流水寄存求和网络法

http://www.paper.edu.cn

流水线设计是高速硬件电路设计中的一种常用手法,流水设计的基本思想是将一个操作

合理的划分成 步,然后将这 步单项串联起来,不考虑寄存器延时和建立时间及保持时间

的影响,如果经合理划分后,各级组合逻辑延时相同,那么 级流水线设计的加速比是

[9]。实际上流水级数受各种因素影响,每个设计只有一个最佳的上限值。本文中流水寄

155

存求和网络法插入了一级流水线寄存器,将逻辑功能分成两步来完成。

图 9 为采用流水寄存求和网络法计算 66 位序列汉明距电路图,在计算时插入流水寄存

器, 66 位序列分为 6 段,每段 11 位,每一段共占用加法器 10 个,计算出 66 位中“1”的

个数,共需要

个加法器。设

,

,„,

,

为插入的寄存器输

出的 11 位汉明距。

160

(2-4)

式(2-4)在 FPGA 中的电路图即图 8 中所示的求和子网络 1。

,

,„,

,

与

具有相同的结构。每个求和子网络都采用了优化算法。流水寄存求和网络法和

无流水寄存求和网络法所用加法器个数虽然相同,但采用流水技术,增加了系统速度。

165

图 9 流水寄存求和网络法

Fig. 9 Sum-network method with pipelining registers

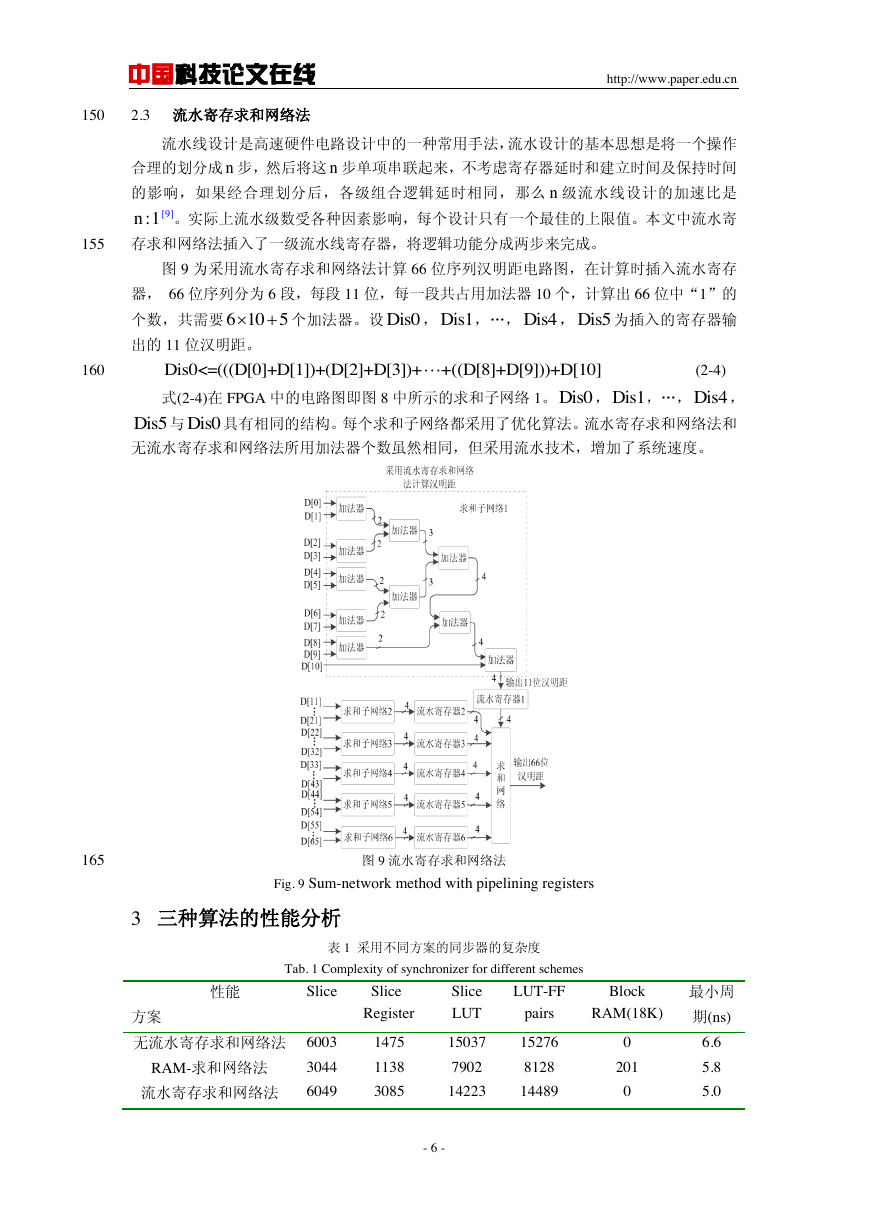

3 三种算法的性能分析

表 1 采用不同方案的同步器的复杂度

Tab. 1 Complexity of synchronizer for different schemes

性能

Slice

Slice

方案

无流水寄存求和网络法

6003

RAM-求和网络法

流水寄存求和网络法

3044

6049

Register

1475

1138

3085

Slice

LUT

LUT-FF

Block

pairs

RAM(18K)

15037

15276

7902

8128

14223

14489

0

201

0

最小周

期(ns)

6.6

5.8

5.0

- 6 -

nnn:1n6105Dis0Dis1Dis4Dis5Dis0<=(((D[0]+D[1])+(D[2]+D[3])++((D[8]+D[9]))+D[10]Dis0Dis1Dis4Dis5Dis0�

中国科技论文在线

http://www.paper.edu.cn

170

本文采用 Verilog HDL 语言编程实现高速同步器的设计,FPGA 开发板是 Virtex-5

ML523,采用 Xilinx 公司的 xc5vfx100t-3ff1136 芯片,开发环境采用 ISE12.4,仿真工具采

用 ModelSim SE 6.5C。采用三种不同方案完成同步器设计的性能如表 1 所示。

从表 1 可以看出,无流水寄存求和网络法系统占用 Slice 资源为 6003,最高工作频率可

以到 151.5MHz;RAM-求和网络法节省了一半的 slice 资源,这是以占用 BLOCK RAM 资源

175

为代价,时钟工作频率可以达到 172.4M,处理数据速率可以达到 10Gbit/s 以上;流水寄存

求和网络法可以达到更高的速率,提高了系统性能,但是需要消耗更多的寄存器资源,并且

增加系统延时,本文中汉明距离的计算只加了一级流水寄存器,延迟周期比不加流水寄存多

1,如果采用多级流水线技术,系统性能还可以提高。RAM-求和网络法和流水寄存求和网

络法都可以满足 10Gbit/s 速率的要求。在系统资源严格要求的情况下,可以采用 RAM-求和

180

网络法,节省系统逻辑资源,但是 OLT 端对高速数据的快速处理是主要技术要求,本文中

的方法更适合于高速系统。

综合时序结果和资源占用情况分别如图 10 和图 11 所示。

185

Fig. 10 Synthesized timing results of three schemes

图 10 三种方案综合时序结果

图 11 三种方案资源分配情况

Fig. 11 Device utilization of three schemes

假设数据速率为 10.3125Gbit/s,时钟周期为 6.4ns,对高速同步器进行仿真,得到图 12

190

和图 13。图 12 为设计综合出的高速同步模块图,图 13 为功能仿真和时序仿真结果,从仿

真结果可以看出,由于 FPGA 输入输出管脚延迟的原因,时序仿真比功能仿真延迟一个周期

输出。

- 7 -

�

中国科技论文在线

http://www.paper.edu.cn

195

图 12 综合出的 RTL 原理图

Fig. 12 Synthesized RTL Schematic

图 13 时序仿真结果

Fig. 13 Timing simulation waveforms

4 结论

200

本文采用 Xilinx 公司的 FPGA 实现了 10G-EPON OLT 端高速同步器设计,提出的基于

流水寄存求和网络法计算汉明距的高速同步方案比已有的方案实现简单,而且工作速率提高

到 13.2Gbit/s。通过对 10Gbit/s 系统的仿真和分析,结果表明采用流水寄存求和网络法,可

处理的数据速率高于另外两种方案。

[参考文献] (References)

205

210

215

220

Inácio,et al.,10G EPON Standardization

[1] IEEE Std 802.3av™-2009, Carrier Sense Multiple Access With Collision Detection (CSMA/CD) Access

Method and Physical Layer Specification, Amendment 1: Physical Layer Specifications and Management

Parameters for 10 Gb/s Passive Optical Networks[S]. 2009.

[2] Marek Hajduczenia,Pedro R. M.

Project.OFC/NFOEC, 2008, Paper NMD4.

[3] Keiji Tanaka, Akira Agata, and Yukio Horiuchi , IEEE 802.3av 10G-EPON Standardization and Its Research

and Development Status[J].IEEE, Journal of Lightwave Technology, vol.28,No.4 2010:651-661.

[4] Hao Yang, Xiaolang Yan, Fast FEC Synchronization For 10G Ethernet Receiver[J].Journal of Lightwave

TechnologyY, Vol. 28, NO. 4, 2010.

[5] H. Hu, J.L. Areal, H.C.H. Mulvad,Synchronization, retiming and OTDM of an asynchronous 10 Gigabit

Ethernet NRZ packet using a time lens for Terabit Ethernet. ECOC Technical Digest 2011 OSA.

[6] 刘昭,金德鹏,曾烈光.10G 以太网帧同步系统的研究[J].高技术通讯,2004,14(5):4-9.

[7] 刘昭,金德鹏,曾烈光.基于连续性判别的并行帧同步系统[J],电子学报,2005,33(7):1177-1182.

[8] 薛铭.基于 FPGA 的汉明距离计算电路的设计[J].长春工程学院学报(自然科学版),2007,8(4):47-49.

[9] 王杰,王城,谢龙汉.Xilinx FPGA/CPLD 设计手册[M].北京:人民邮电出版社,2011.

[10] 刘福奇,刘波.Verilog HDL 应用程序设计实例精讲[M].北京:电子工业出版社,2009.

in

IEEE 802.3av

- 8 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc