Ù

军 事 通 信 技 术

Ù

V o l. 25 N o. 2

Jun. 2004

Ξ

2

2

2

2

第 25 卷 第 2 期

2004 年 6 月

Jou rnal of M ilitary Comm un ication s T echno logy

SP I 总线接口的 F PGA 设计与实现

杨承富1, 徐志军2

(1. 解放军理工大学通信工程学院研究生 2 队, 江苏 南京 210007;

2. 解放军理工大学通信工程学院电子信息工程系)

摘 要: 文中介绍了采用 A lterea 公司 FL EX10K 型的 FPGA 器件实现串行外设接口 (SP I) 的原理与过程,

给出了逻辑框图以及部分 V erilog 代码。 用此种方法实现的接口与专用接口芯片相比, 具有使用灵活, 系统配置方

便的优点。

关键词: 串行外设接口; 现场可编程门阵列; V erilog 硬件描述语言

中图分类号: T P336 文献标识码: A

文章编号: 0032

1289 (2004) 02

0072

05

D e s ign a nd Im p lem e n t S P I B us In te rfa ce w ith FPGA

YA N G Cheng

f u 1, X U Z h i

jun 2

(1. Po stgraduate T eam 2 ICE, PLAU ST , N an jing 210007, Ch ina;

2. D epartm en t of Eelctron ic Info rm ation Engneering ICE, PLAU ST )

A bs tra c t: T he theo ry and the w ay of

in terface w ith FPGA are

in troduced, and the b lock diagram and som e V erilog code are p resen ted. T he ch ip im p lem en ted in

th is w ay has m o re agility and is m o re conven ien t to configu re than o thers.

im p lem en ting a SP I

Ke y w o rds: SP I in terface; FPGA ; V erilog HDL

串行外设接口 SP I(Serial Perip heral In terface) 是M o to ro la 公司推出的一种同步串行接口。M o to ro la 公

司生产的绝大多数单片机都配有 SP I 硬件接口, 如 68 系列单片机。但也有许多单片机没有 SP I 接口, 在需要

应用 SP I 进行通信的场合, 就需要对其进行 SP I 接口扩展。SP I 接口的扩展有硬件和软件两种方法, 软件模

拟 SP I 接口方法虽然简单方便, 但是速度受到限制, 若用来进行通信, 则速度不会很高。 因此我们可以用

FPGA 来实现 SP I 接口, FPGA 的速度很高, 可以实现高速串行通信。 根据 SP I 总线的电气特性, 我们采用

AL T ERA 公司的 FL EX 10K 系列 FPGA 器件设计并实现了 SP I 总线的通信接口, 该总线接口具有高速、易

调试、配置灵活等等优点, 大大地减少了系统的开发周期。

1 SP I 简介

SP I 接口是工业标准的同步串行接口, 是一种全双工、三线通信的系统。 它允许处理器与各种外围设备

以串行方式 (8 位数据同时、同步地被发送和接收) 进行通信。 在 SP I 接口中, 数据的传输需要 1 个时钟信号

和两条数据线。

SP I 总线由四根线组成: 串行时钟线 (SCK ) , 主机输出

从机输入线 (M O S I) , 主机输入

从机输出线

(M ISO ) , 还有一根是从机选择线 (SS) , 它们在与总线相连的各个设备之间传送信息。

06

收稿日期: 2003

作者简介: 杨承富 (1980-

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

05; 修回日期: 2003

) , 男, 硕士生.

06

20

�

第 2 期 杨承富等: SP I 总线接口的 FPGA 设计与实现

37

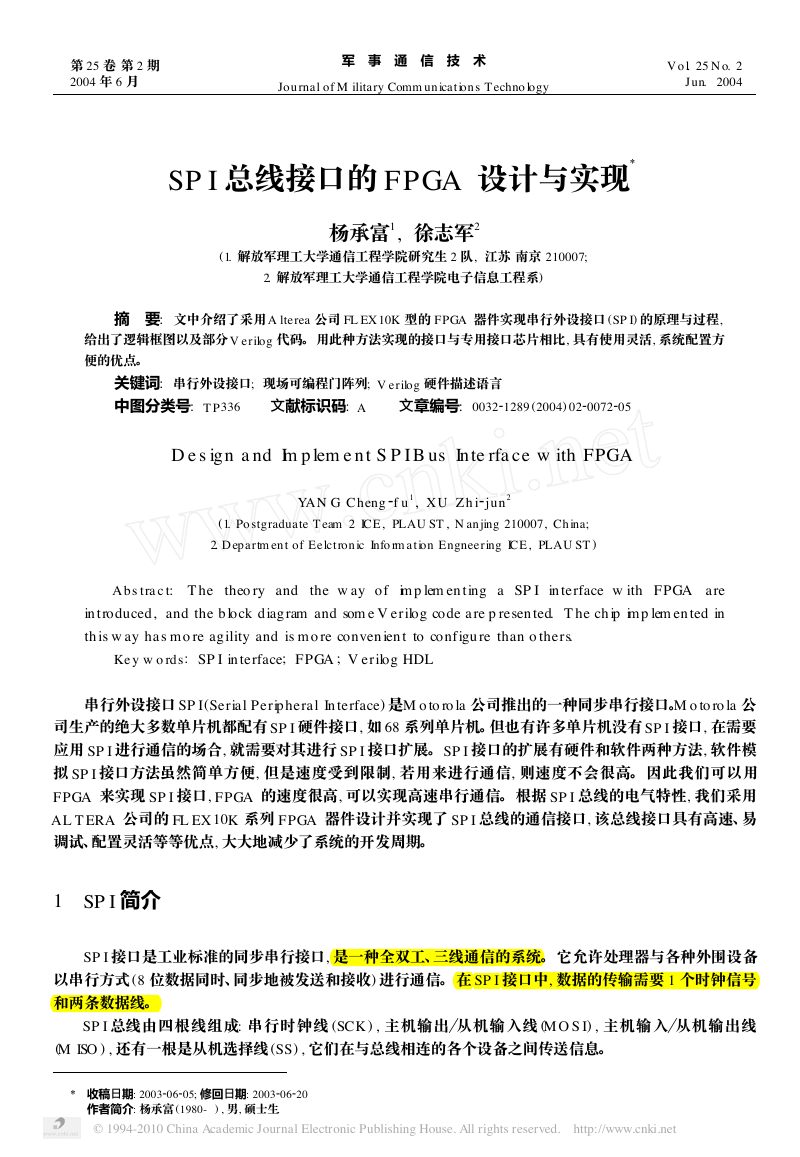

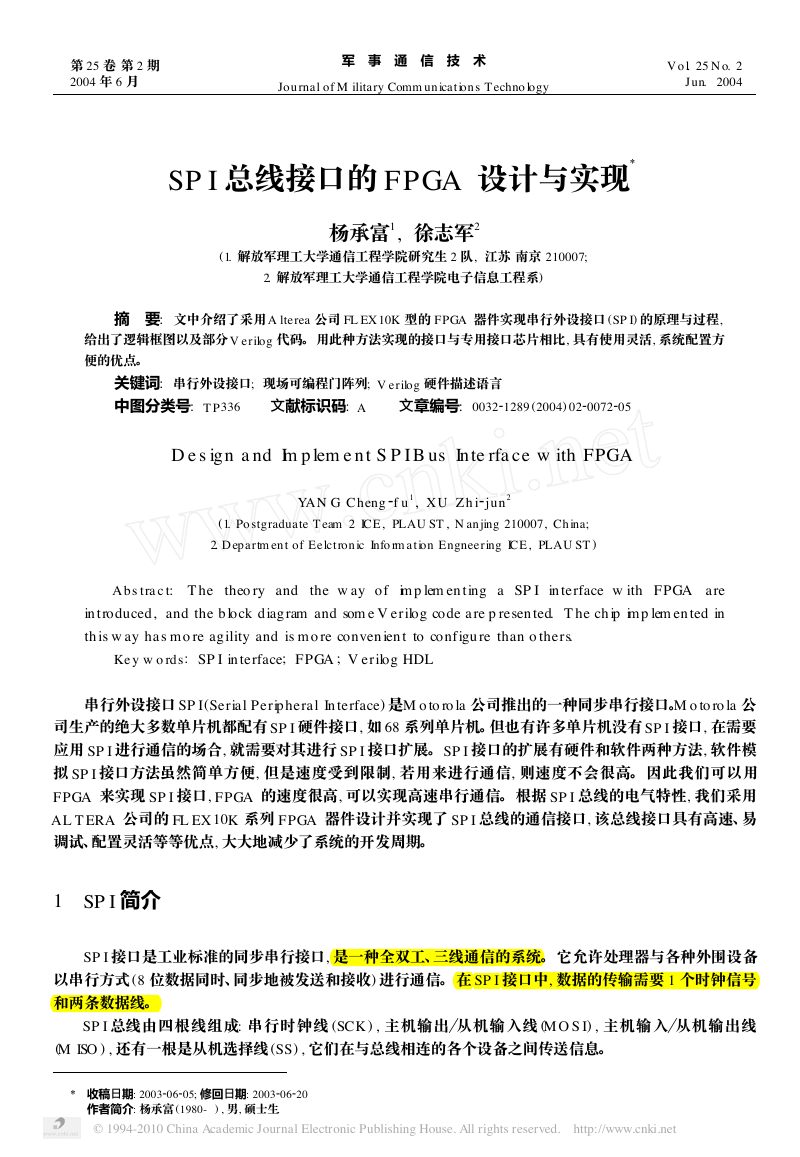

SP I 总线中所有的数据传输由串行时钟 SCK

来进行同步, 每个时钟脉冲传送 1 比特数据。SCK

由 主机产生, 是从机的一个输入。 时钟的相位

(CPHA ) 与极性 (CPOL ) 可以用来控制数据的传

输。CPOL =“0”表示 SCK 的静止状态为低电平,

CPOL =“1”则表示 SCK 静止状态为高电平。时钟

相位 (CPHA ) 可以用来选择两种不同的数据传输

模式。如果 CPHA =“0”, 数据在信号 SS 声明后的

第一个 SCK 边沿有效; 而当 CPHA =“1”时, 数据

在信号 SS 声明后的第二个 SCK 边沿才有效。

因此, 主机与从机中 SP I 设备的时钟相位和极

性必须要一致才能进行通信。图 1 和图 2 分别

为不同相位与极性的时钟控制下的数据传输模

式。

图 1 CPHA = 0 时的传输模式

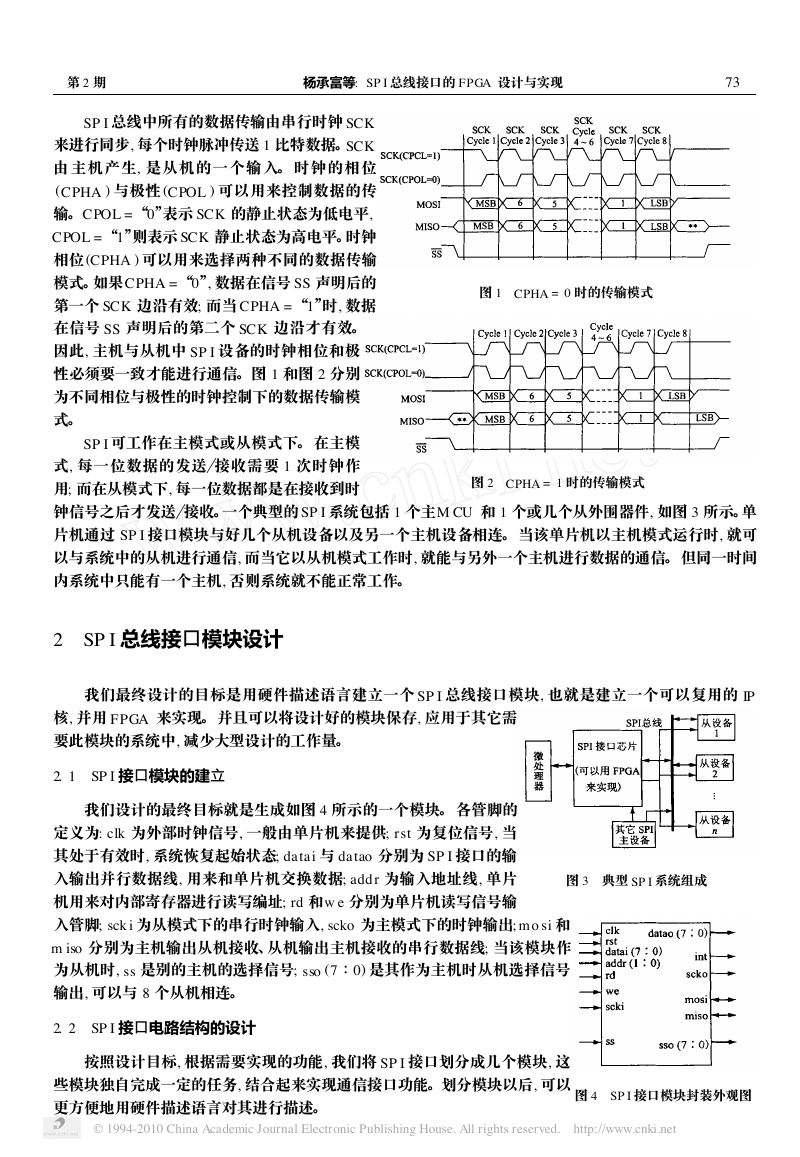

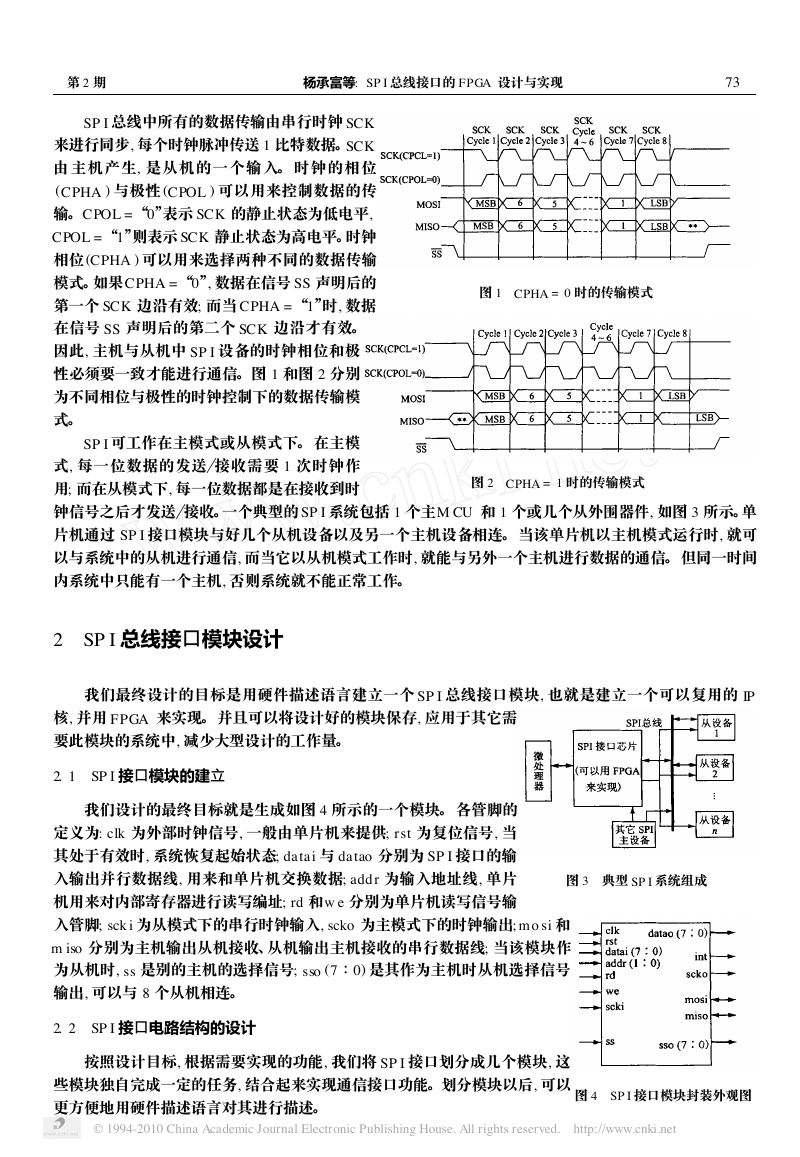

SP I 可工作在主模式或从模式下。 在主模

式, 每一位数据的发送

接收需要 1 次时钟作

用; 而在从模式下, 每一位数据都是在接收到时

钟信号之后才发送

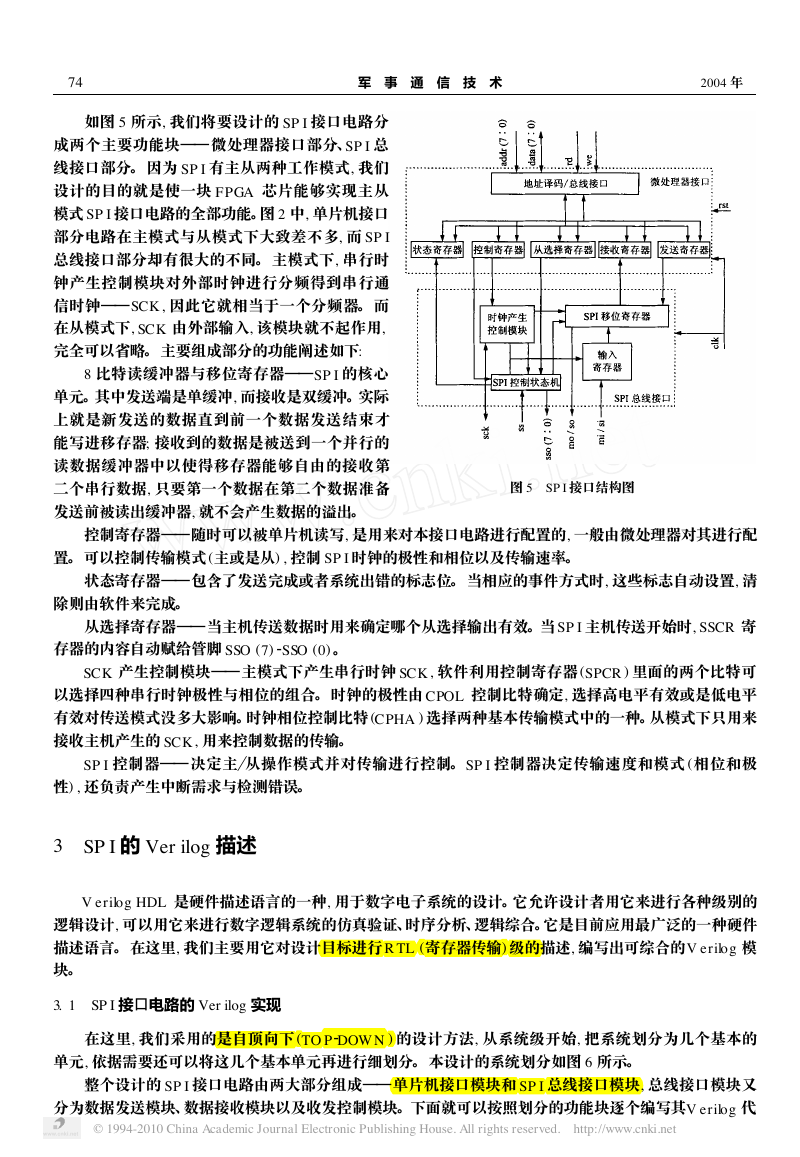

接收。一个典型的 SP I 系统包括 1 个主M CU 和 1 个或几个从外围器件, 如图 3 所示。单

片机通过 SP I 接口模块与好几个从机设备以及另一个主机设备相连。 当该单片机以主机模式运行时, 就可

以与系统中的从机进行通信, 而当它以从机模式工作时, 就能与另外一个主机进行数据的通信。 但同一时间

内系统中只能有一个主机, 否则系统就不能正常工作。

图 2 CPHA = 1 时的传输模式

2 SP I 总线接口模块设计

我们最终设计的目标是用硬件描述语言建立一个 SP I 总线接口模块, 也就是建立一个可以复用的 IP

核, 并用 FPGA 来实现。 并且可以将设计好的模块保存, 应用于其它需

要此模块的系统中, 减少大型设计的工作量。

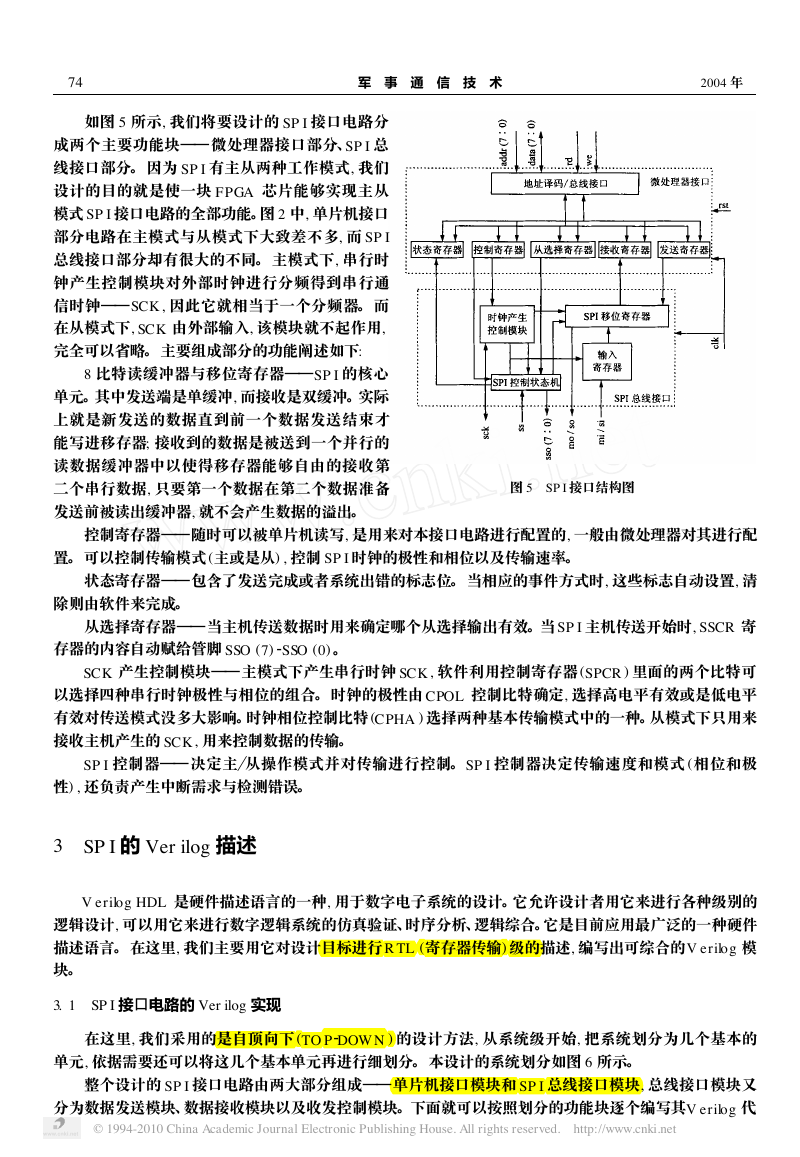

2. 1 SP I 接口模块的建立

我们设计的最终目标就是生成如图 4 所示的一个模块。 各管脚的

定义为: clk 为外部时钟信号, 一般由单片机来提供; rst 为复位信号, 当

其处于有效时, 系统恢复起始状态; datai 与 datao 分别为 SP I 接口的输

入输出并行数据线, 用来和单片机交换数据; addr 为输入地址线, 单片

机用来对内部寄存器进行读写编址; rd 和w e 分别为单片机读写信号输

入管脚; sck i 为从模式下的串行时钟输入, scko 为主模式下的时钟输出; m o si 和

m iso 分别为主机输出从机接收、从机输出主机接收的串行数据线; 当该模块作

为从机时, ss 是别的主机的选择信号; sso (7∶0) 是其作为主机时从机选择信号

输出, 可以与 8 个从机相连。

图 3 典型 SP I 系统组成

2. 2 SP I 接口电路结构的设计

按照设计目标, 根据需要实现的功能, 我们将 SP I 接口划分成几个模块, 这

些模块独自完成一定的任务, 结合起来实现通信接口功能。划分模块以后, 可以

更方便地用硬件描述语言对其进行描述。

图 4 SP I 接口模块封装外观图

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

2

47

军 事 通 信 技 术 2004 年

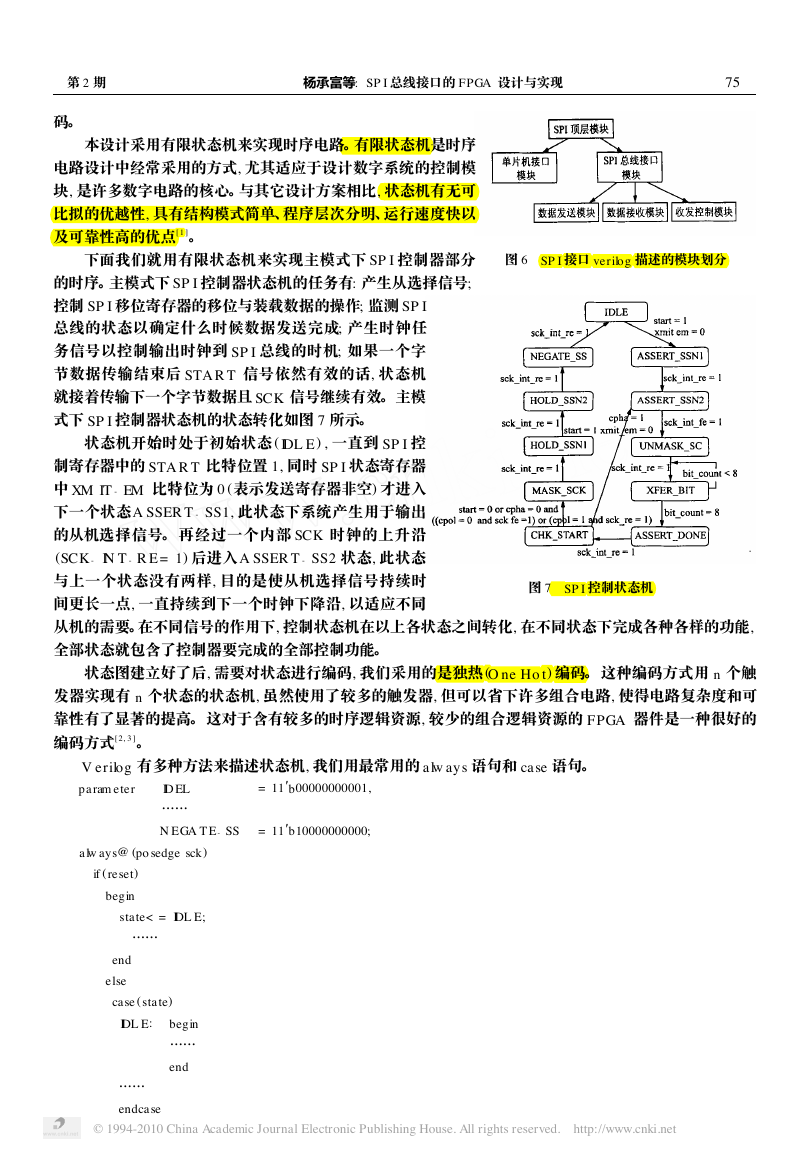

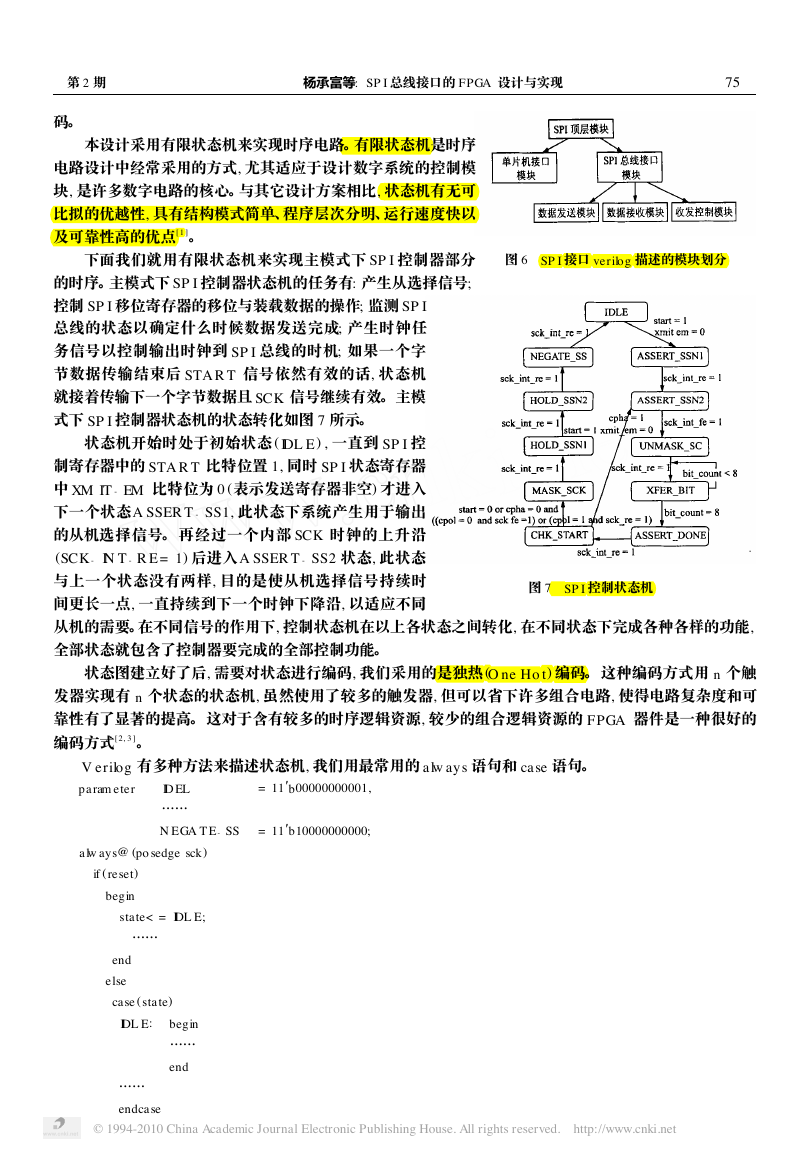

如图 5 所示, 我们将要设计的 SP I 接口电路分

成两个主要功能块—— 微处理器接口部分、SP I 总

线接口部分。 因为 SP I 有主从两种工作模式, 我们

设计的目的就是使一块 FPGA 芯片能够实现主从

模式 SP I 接口电路的全部功能。图 2 中, 单片机接口

部分电路在主模式与从模式下大致差不多, 而 SP I

总线接口部分却有很大的不同。 主模式下, 串行时

钟产生控制模块对外部时钟进行分频得到串行通

信时钟——SCK, 因此它就相当于一个分频器。 而

在从模式下, SCK 由外部输入, 该模块就不起作用,

完全可以省略。 主要组成部分的功能阐述如下:

8 比特读缓冲器与移位寄存器——SP I 的核心

单元。其中发送端是单缓冲, 而接收是双缓冲。实际

上就是新发送的数据直到前一个数据发送结束才

能写进移存器; 接收到的数据是被送到一个并行的

读数据缓冲器中以使得移存器能够自由的接收第

二个串行数据, 只要第一个数据在第二个数据准备

发送前被读出缓冲器, 就不会产生数据的溢出。

图 5 SP I 接口结构图

控制寄存器——随时可以被单片机读写, 是用来对本接口电路进行配置的, 一般由微处理器对其进行配

置。 可以控制传输模式 (主或是从) , 控制 SP I 时钟的极性和相位以及传输速率。

状态寄存器——包含了发送完成或者系统出错的标志位。 当相应的事件方式时, 这些标志自动设置, 清

除则由软件来完成。

从选择寄存器——当主机传送数据时用来确定哪个从选择输出有效。当 SP I 主机传送开始时, SSCR 寄

存器的内容自动赋给管脚 SSO (7)

SSO (0)。

SCK 产生控制模块——主模式下产生串行时钟 SCK, 软件利用控制寄存器 (SPCR ) 里面的两个比特可

以选择四种串行时钟极性与相位的组合。 时钟的极性由 CPOL 控制比特确定, 选择高电平有效或是低电平

有效对传送模式没多大影响。时钟相位控制比特 (CPHA ) 选择两种基本传输模式中的一种。从模式下只用来

接收主机产生的 SCK, 用来控制数据的传输。

SP I 控制器—— 决定主

从操作模式并对传输进行控制。SP I 控制器决定传输速度和模式 (相位和极

性) , 还负责产生中断需求与检测错误。

3 SP I 的 Ver ilog 描述

V erilog HDL 是硬件描述语言的一种, 用于数字电子系统的设计。它允许设计者用它来进行各种级别的

逻辑设计, 可以用它来进行数字逻辑系统的仿真验证、时序分析、逻辑综合。它是目前应用最广泛的一种硬件

描述语言。 在这里, 我们主要用它对设计目标进行 R TL (寄存器传输) 级的描述, 编写出可综合的V erilog 模

块。

3. 1 SP I 接口电路的 Ver ilog 实现

在这里, 我们采用的是自顶向下 (TO P

DOW N ) 的设计方法, 从系统级开始, 把系统划分为几个基本的

单元, 依据需要还可以将这几个基本单元再进行细划分。 本设计的系统划分如图 6 所示。

整个设计的 SP I 接口电路由两大部分组成——单片机接口模块和 SP I 总线接口模块, 总线接口模块又

分为数据发送模块、数据接收模块以及收发控制模块。下面就可以按照划分的功能块逐个编写其V erilog 代

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

第 2 期 杨承富等: SP I 总线接口的 FPGA 设计与实现

57

码。

本设计采用有限状态机来实现时序电路。有限状态机是时序

电路设计中经常采用的方式, 尤其适应于设计数字系统的控制模

块, 是许多数字电路的核心。与其它设计方案相比, 状态机有无可

比拟的优越性, 具有结构模式简单、程序层次分明、运行速度快以

及可靠性高的优点[ 1 ]。

下面我们就用有限状态机来实现主模式下 SP I 控制器部分

的时序。主模式下 SP I 控制器状态机的任务有: 产生从选择信号;

控制 SP I 移位寄存器的移位与装载数据的操作; 监测 SP I

总线的状态以确定什么时候数据发送完成; 产生时钟任

务信号以控制输出时钟到 SP I 总线的时机; 如果一个字

节数据传输结束后 STA R T 信号依然有效的话, 状态机

就接着传输下一个字节数据且 SCK 信号继续有效。主模

式下 SP I 控制器状态机的状态转化如图 7 所示。

图 6 SP I 接口 verilog 描述的模块划分

状态机开始时处于初始状态 ( IDL E) , 一直到 SP I 控

制寄存器中的 STA R T 比特位置 1, 同时 SP I 状态寄存器

中 XM IT - EM 比特位为 0 (表示发送寄存器非空) 才进入

下一个状态A SSER T - SS1, 此状态下系统产生用于输出

的从机选择信号。 再经过一个内部 SCK 时钟的上升沿

(SCK - IN T - R E = 1) 后进入 A SSER T - SS2 状态, 此状态

与上一个状态没有两样, 目的是使从机选择信号持续时

间更长一点, 一直持续到下一个时钟下降沿, 以适应不同

从机的需要。在不同信号的作用下, 控制状态机在以上各状态之间转化, 在不同状态下完成各种各样的功能,

全部状态就包含了控制器要完成的全部控制功能。

图 7 SP I 控制状态机

状态图建立好了后, 需要对状态进行编码, 我们采用的是独热 (O ne Ho t) 编码。 这种编码方式用 n 个触

发器实现有 n 个状态的状态机, 虽然使用了较多的触发器, 但可以省下许多组合电路, 使得电路复杂度和可

靠性有了显著的提高。 这对于含有较多的时序逻辑资源, 较少的组合逻辑资源的 FPGA 器件是一种很好的

编码方式[ 2, 3 ]。

V erilog 有多种方法来描述状态机, 我们用最常用的 alw ays 语句和 case 语句。

param eter ID EL = 11′b00000000001,

……

N EGA T E - SS

= 11′b10000000000;

alw ays@ (po sedge sck)

if (reset)

begin

state< = IDL E;

……

end

else

case (state)

IDL E: begin

……

end

……

endcase

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

Ù

67

军 事 通 信 技 术 2004 年

3. 2 仿真与验证

将要设计的 SP I 接口电路用V erilog 语言描述好了以后, 用 synp lify 对其进行综合, 再用A ltera 公司的

软件对生成的网表文件进行编译仿真, 部分管脚的仿真结果见图 8。 可以看出, 功能仿真的结果

m axp lu s-

完全正确。

综合、仿真完成后, 我们用

具体的器件对设计进行了验

证。我们选用的是A ltera 公司

的 FPGA 器件。A ltera 公司的

FPGA 器件内部连线采用连续

式互连结构, 即采用同样长度

的一些金属线实现逻辑单元之

间的连接, 这种结构的优点是

其延时可预测。从互连结构看,

这 样 的 器 件 属 于 CPLD , 但

A ltera 公 司 的 FL EX、A PEX

系列器件同时具有 FPGA 的

典型特点, 如精细分割的结构

和大量的寄存器等, 因此把它

们归结为 FPGA。可以说 A ltera 公司的 FPGA 器件集 FPGA 和 CPLD 两种结构之优点, 可以满足各个方面

的应用需求[ 3 ]。 本设计采用 FL EX10K 系列中的 PF 10K20TC144

3 来实现了 SP I 的总线通信接口, 该芯片

共有 1152 个逻辑单元, 本设计使用了 860 个, 占全部资源的 74%。 布局布线后, 经测试, FPGA 的速度最高

可以达到 144 M H z, 符合设计要求, 达到了预期的目的。

图 8 仿真波形

4 结束语

随着技术的不断进步, CPLD

FPGA 的速度越来越快, 包含的门数成倍增加, 价格也越来越合理。因此,

我们可以利用其应用方便、开发装置简单的优点, 用它们来实现符合不同需要的多种电路, 缩短科研开发的

周期。

参考文献:

[ 1 ] 徐志军, 徐光辉. CPLD

[ 2 ] 夏宇闻. 复杂数字逻辑系统的 V erilog HDL 设计技术和方法[M ]. 北京: 高等教育出版社, 2001.

[ 3 ] 王金明, 杨吉斌. 数字系统设计与 V erilog HDL [M ]. 北京: 电子工业出版社, 2002.

FPGA 的开发与应用[M ]. 北京: 电子工业出版社, 2002.

陈太一顾问逝世

著名通信信息工程技术专家、教育家、中国工程院院士, 我刊顾问陈太一同志因病医治无效, 于 2004 年

5 月 6 日在北京逝世, 享年 83 岁。

陈太一顾问生前为我国、我军的通信事业做出了杰出贡献, 对我刊自创刊以来就不间断地关注、关心、指

(本刊讯)

导, 并亲自撰稿, 担任我刊顾问以来做了大量的重要工作。 我刊将永远的怀念他、纪念他。

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc