封面

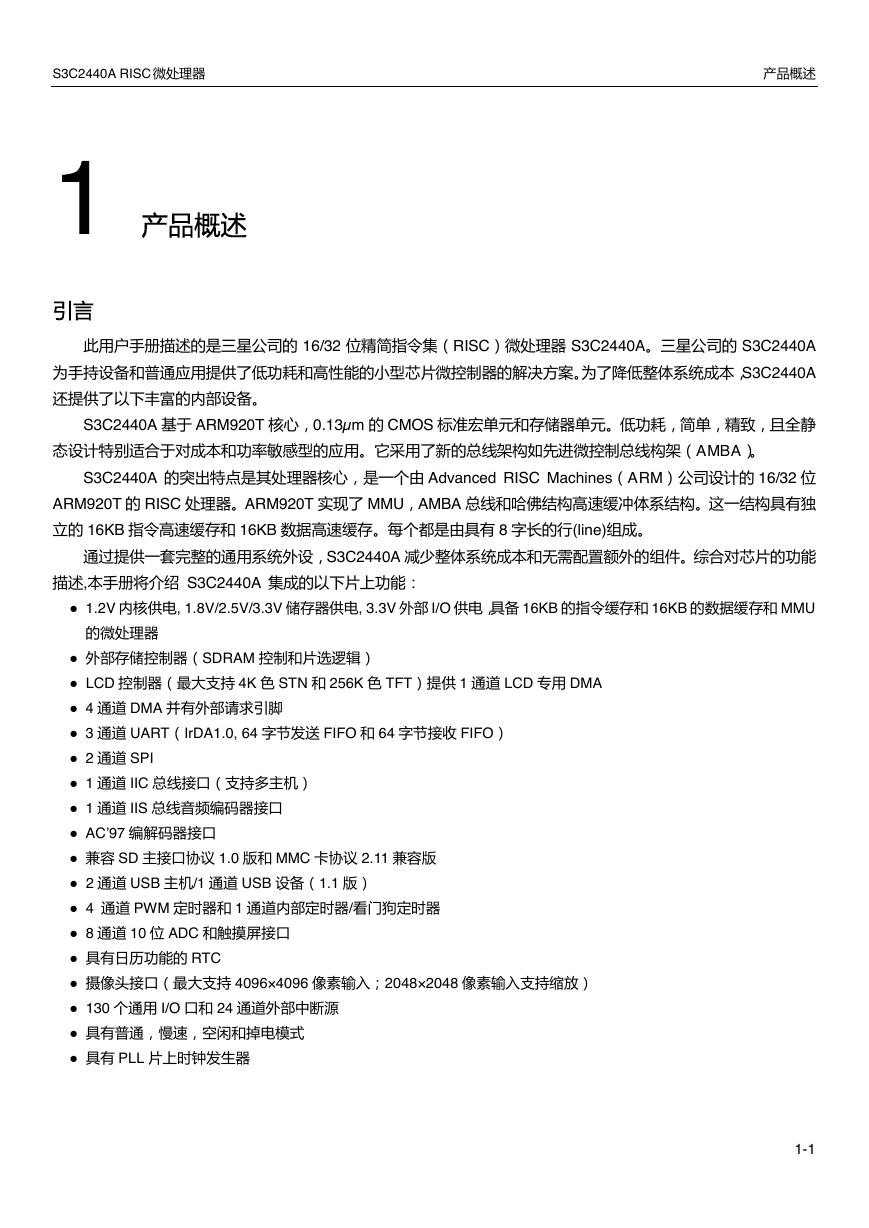

1 产品概述

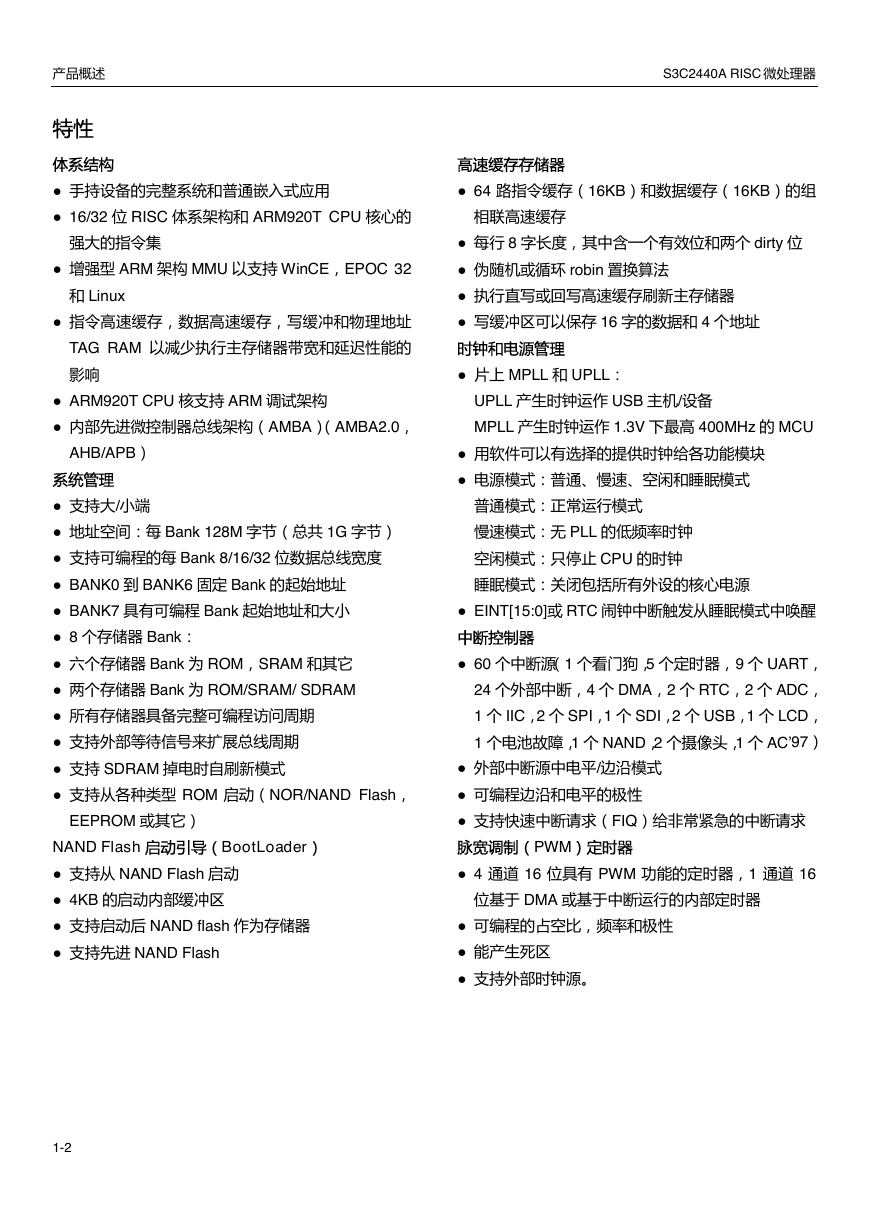

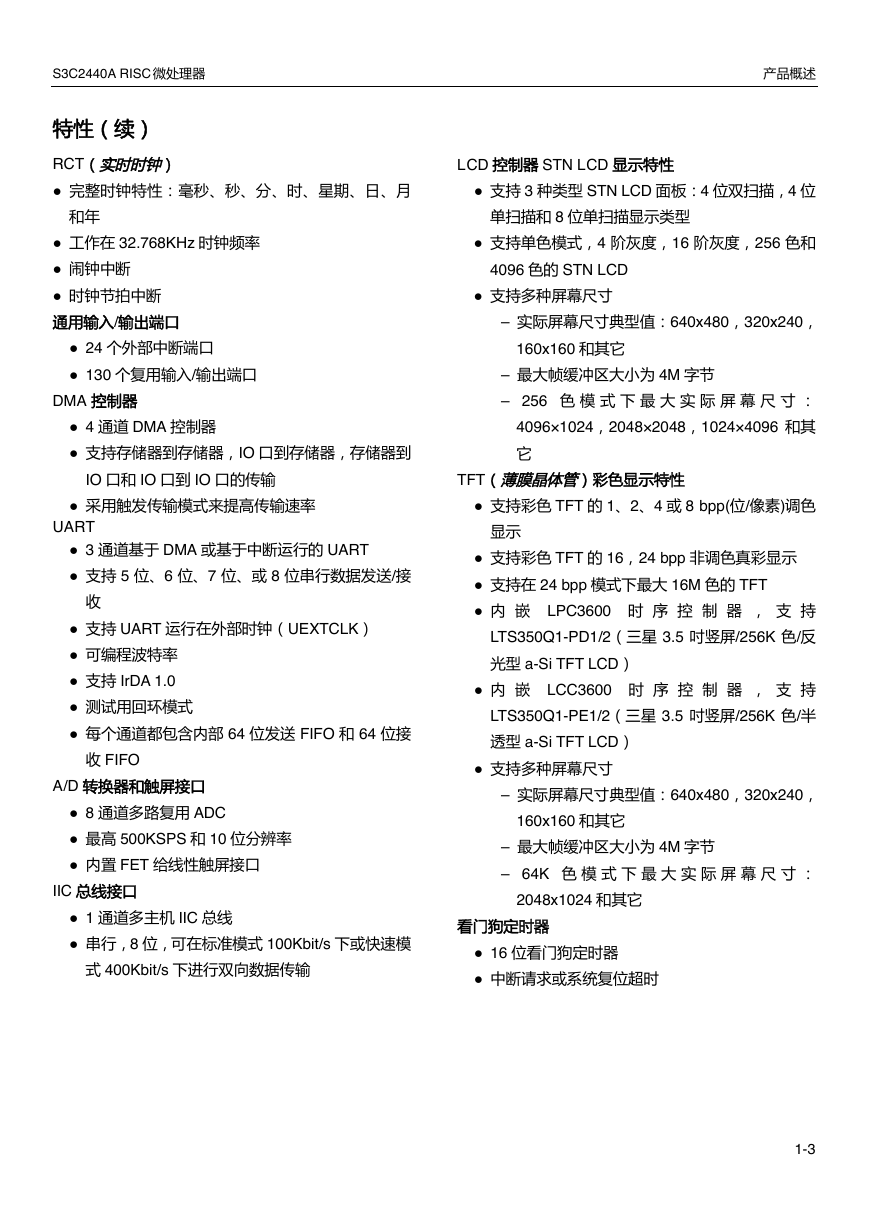

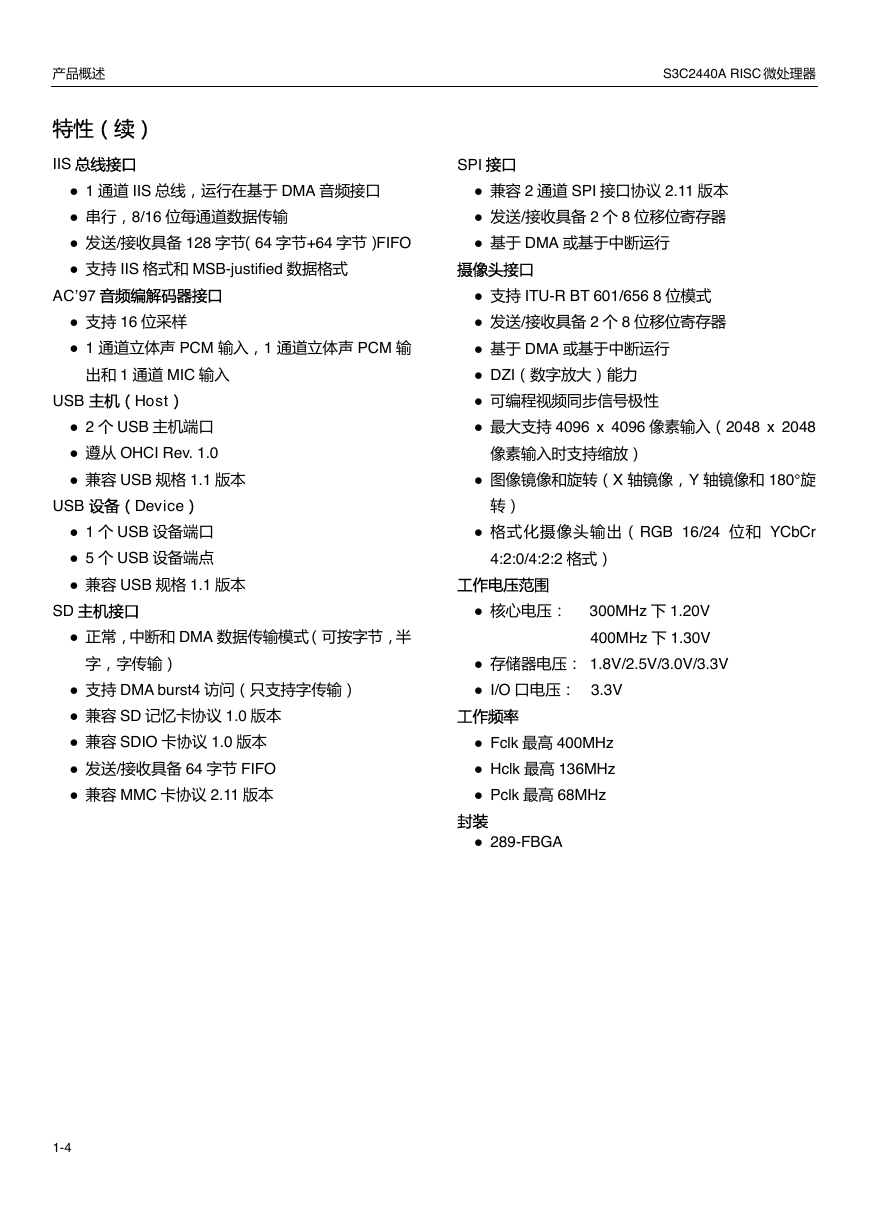

特性

方框图

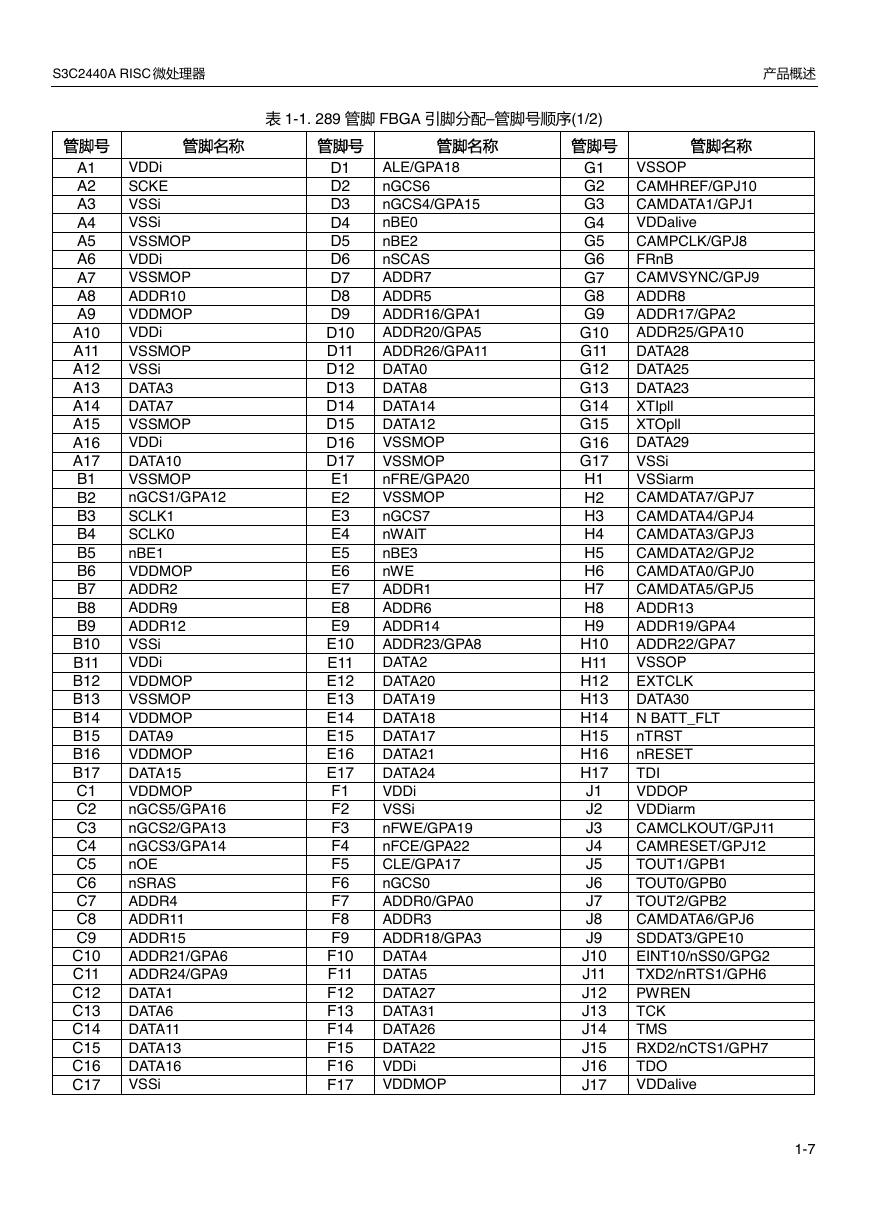

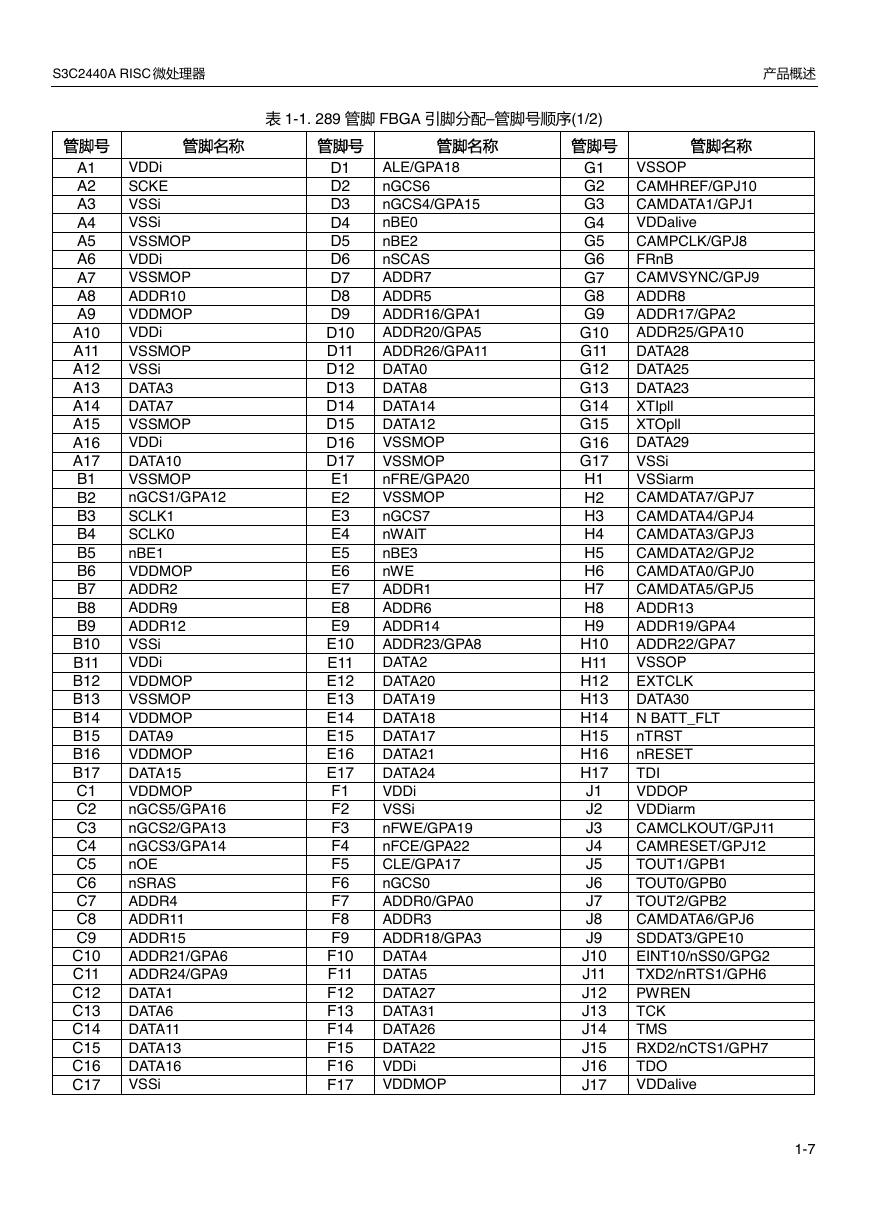

引脚分配

信号端描述

S3C2440A特殊寄存器

2 程序员模型

处理器运行状态

进入 ARM 状态

存储格式

运行模式

内部寄存器

程序状态寄存器

异常

快中断 FIQ

中断 IRQ

异常向量

复位

3 ARM 指令集

格式概述

指令概述

条件字段

数据处理指令

PSR传送指令(MRS,MSR)

乘法和乘加指令(MUL,MLA)

长乘法和长乘加指令(MULL,MLAL)

单数据传送(LDR,STR)

半字和有符号数据传送(LDRH/STRH/LDRSB/STRSH)

块数据传送(LDM,STM)

单数据交换(SWP)

软件中断(SWI)

协处理器数据操作(CDP)

协处理器数据传送(LDC,STC)

协处理器寄存器传送(MRC,MCR)

未定义指令

指令集例子

4 THUMB 指令集

Thumb指令集格式

操作码概述

ARM 代码

5 存储器控制器

概述

复位后S3C2440A 的存储器映射

功能描述

SDRAM BANK地址引脚连接例子

nWAIT引脚操作

nXBREQ/nXBACK引脚操作

ROM 存储器接口例子

SRAM 存储器接口例子

可编程访问周期

BANK控制寄存器(BANKCONn:nGCS0至 nGCS5)

BANK控制寄存器(BANKCONn:nGCS6至 nGCS7)

刷新控制寄存器

Bank 大小寄存器

SDRAM模式 寄存器组寄存器(MRSR)

6 NAND FLASH 控制器

概述

特性

方框图

引导加载(BootLoader)功能

引脚配置

NAND Flash存储器时序

软件模式

数据寄存器配置

EEC(错误纠正码)

NAND Flash存储器映射

NAND Flash存储器配置

NAND Flash配置寄存器

控制寄存器

命令寄存器

地址寄存器

数据寄存器

主数据区域寄存器

备份区域 ECC寄存器

NFCON状态寄存器

ECC0/1状态寄存器

主数据区域 ECC0/1 状态寄存器

备份区域 ECC状态寄存器

块地址寄存器

7 时钟和电源管理

概述

功能描述

时钟源选择

锁相环(PLL)

PLL(锁相环)方框图

时钟控制逻辑

上电复位(XTIpll)

普通模式下改变PLL设置

USB时钟控制

FCLK,HCLK和 PCLK

电源管理

PLL开启/关闭

时钟发生器和电源管理特殊寄存器

锁定时间计数寄存器(LOCKTIME)

PLL控制寄存器(MPLLCON和 UPLLCON)

MPLL控制寄存器

UPLL控制寄存器

PLL值选择向导(MPLLCON)

时钟控制寄存器(CLKCON)

时钟慢速控制(CLKSLOW)寄存器

时钟分频控制(CLKDIVN)寄存器

摄像头时钟分频(CAMDIVN)寄存器

8 直接存储器存取 DMA

概述

DMA请求源

DMA操作

外部 DMA请求/应答(DREQ/DACK)协议

例子

DMA特殊寄存器

DMA初始源(DISRC)寄存器

DMA初始源控制(DISRCC)寄存器

DMA初始目标(DIDST)寄存器

DMA初始目标控制(DIDSTC)寄存器

DMA控制(DCON)寄存器

DMA控制(DCON)寄存器(续)

DMA状态(DSTAT)寄存器

DMA当前源(DCSRC)寄存器

DMA当前目标(DCDST)寄存器

DMA触发屏蔽(DMASKTRIG)寄存器

9 输入/输出端口

概述

端口控制描述

端口配置寄存器(GPACON至 GPJCON)

端口数据寄存器(GPADAT至 GPJDAT)

端口上拉寄存器(GPBUP 至 GPJUP)

杂项控制寄存器

外部中断控制寄存器

I/O口控制寄存器

端口 A控制寄存器(GPACON,GPADAT)

端口 B控制寄存器(GPBCON,GPBDAT,GPBUP)

端口 C控制寄存器(GPCCON,GPCDAT,GPCUP)

端口 D控制寄存器(GPDCON,GPDDAT,GPDUP)

端口 E控制寄存器(GPECON,GPEDAT,GPEUP)

端口 F控制寄存器(GPFCON,GPFDAT,GPFUP)

端口 G控制寄存器(GPGCON,GPGDAT,GPGUP)

端口 H控制寄存器(GPHCON,GPHDAT,GPHUP)

端口 J控制寄存器(GPJCON,GPJDAT,GPJUP)

杂项控制寄存器(MISCCR)

DCLK控制寄存器(DCLKCON)

EXTINTn(外部中断控制寄存器 n)

EINTFLTn(外部中断滤波寄存器 n)

EINTMASK(外部中断屏蔽寄存器)

EINTPEND(外部中断挂起寄存器)

GSTATUSn(通用状态寄存器)

DSCn(驱动强度控制寄存器)

MSLCON(存储器睡眠控制寄存器)

10 PWM 定时器

概述

特性

PWM 定时器操作

基本时序操作

自动重载和双缓冲

使用手动更新位和变相位初始化定时器

定时器操作

脉宽调制(PWM)

输出电平控制

死区发生器

DMA请求模式

PWM 定时器控制寄存器

定时器配制寄存器 0(TCFG0)

定时器配制寄存器 1(TCFG1)

定时器控制寄存器 1(TCON)

定时器 0计数缓冲寄存器和比较缓冲寄存器(TCNTB0/TCMPB0)

定时器 0计数监视寄存器(TCNTO0)

定时器 1计数缓冲寄存器和比较缓冲寄存器(TCNTB1/TCMPB1)

定时器 1计数监视寄存器(TCNTO1)

定时器 2计数缓冲寄存器和比较缓冲寄存器(TCNTB2/TCMPB2)

定时器 2计数监视寄存器(TCNTO2)

定时器 3计数缓冲寄存器和比较缓冲寄存器(TCNTB3/TCMPB3)

定时器 3计数监视寄存器(TCNTO3)

定时器 4计数缓冲寄存器(TCNTB4)

定时器 4计数监视寄存器(TCNTO4)

11 UART

概述

方框图

UART操作

数据发送

数据接收

自动流控制(AFC)

非自动流控制的例子(软件控制nRTS和 nCTS)

中断/DMA请求产生

UART错误状态FIFO

波特率发生

环回模式

红外(IR)模式

UART特殊寄存器

UART线路控制寄存器

UART控制寄存器

UART FIFO 控制寄存器

UART MODEM控制寄存器

UART TX/RX 状态寄存器

UART错误状态寄存器

UART FIFO 状态寄存器

UART MODEM状态寄存器

UART发送缓冲寄存器(保持寄存器和 FIFO寄存器)

UART接收缓冲寄存器(保持寄存器和 FIFO寄存器)

UART波特率分频寄存器

12 USB 主机控制器

概述

USB主机控制器的OHCI 寄存器

13 USB 设备控制器

概述

USB设备控制器特殊寄存器

功能地址寄存器(FUNC_ADDR_REG)

电源管理寄存器(PWR_REG)

中断寄存器(EP_INT_REG/USB_INT_REG)

中断使能寄存器(EP_INT_EN_REG/USB_INT_EN_REG)

帧号寄存器(FPAME_NUM1_REG/FRAME_NUM2_REG)

标记寄存器(INDEX_REG)

最大数据包寄存器(MAXP_REG)

端点 0控制状态寄存器(EP0_CSR)

端点输入控制状态寄存器(IN_CSR1_REG/IN_CSR2_REG)

端点输出控制状态寄存器(OUT_CSR1_REG/OUT_CSR2_REG)

端点输出写计数寄存器(OUT_FIFO_CNT1_REG/OUT_FIFO_CNT2_REG)

端点 FIFO寄存器(EPN_FIFO_REG)

DMA 接口控制寄存器(EPN_DMA_CON)

DMA单元计数器寄存器(EPN_DMA_UNIT)

DMA FIFO 计数器寄存器(EPN_DMA_FIFO)

DMA总计传输计数器寄存器(EPn_DMA_TTC_L,M,H)

14 中断控制器

概述

中断控制器操作

中断源

中断次级源

中断优先级

中断优先级发生模块

中断控制器特殊寄存器

源挂起(SRCPND)寄存器

中断模式(INTMOD)寄存器

中断屏蔽(INTMSK)寄存器

优先级寄存器(PRIORITY)

中断挂起(INTPND)寄存器

中断偏移(INTOFFSET)寄存器

次级源挂起(SUBSRCPND)寄存器

中断次级屏蔽(INTSUBMSK)寄存器

15 LCD 控制器

概述

外接信号

方框图

STN LCD控制器操作

时序发生器(TIMEGEN)

视频操作

存储器数据格式(STN,BSWP = 0)

TFT LCD控制器操作

三星 TFT LCD面板(3.5吋竖屏/256K色/反光型 a-Si/半透型 a-Si TFT LCD)

虚拟显示(TFT/STN)

LCD电源使能(STN/TFT)

LCD控制器特殊寄存器

LCD控制 1寄存器

LCD控制 2寄存器

LCD控制 3寄存器

LCD控制 4寄存器

LCD控制 5寄存器

帧缓冲器开始地址 1寄存器

帧缓冲器开始地址2寄存器

帧缓冲器开始地址3寄存器

红色查找表寄存器

绿色查找表寄存器

蓝色查找表寄存器

抖动模式寄存器

临时调色板寄存器

LCD中断挂起寄存器

LCD源挂起寄存器

LCD中断屏蔽寄存器

TCON控制寄存器

寄存器设置向导(STN)

例

灰度选择向导

LCD刷新总线带宽计算向导

寄存器设置向导(TFT LCD)

16 模/数转换器及触摸屏接口

概述

ADC和触摸屏接口操作

A/D 转换时间

触摸屏接口模式

编程笔记

ADC和触摸屏接口特殊寄存器

ADC控制寄存器(ADCCON)

ADC触摸屏控制寄存器(ADCTSC)

ADC启动延时寄存器(ADCDLY)

ADC转换数据寄存器(ADCDAT0)

ADC转换数据寄存器(ADCDAT1)

ADC触摸屏起落中断检测寄存器(ADCUPDN)

17 实时时钟

概述

闰年发生器

读/写寄存器

实时时钟特殊功能寄存器

实时时钟控制(RTCCON)寄存器

节拍时间计数(TICNT)寄存器

RTC闹钟控制(RTCALM)寄存器

闹钟秒数据(ALMSEC)寄存器

闹钟分数据(ALMMIN)寄存器

闹钟时数据(ALMHOUR)寄存器

闹钟日数据(ALMDATE)寄存器

闹钟月数据(ALMMON)寄存器

闹钟年数据(ALMYEAR)寄存器

BCD秒(BCDSEC)寄存器

BCD分(BCDMIN)寄存器

BCD时(BCDHOUR)寄存器

BCD日(BCDDATE)寄存器

BCD星期(BCDDAY)寄存器

BCD月(BCDMON)寄存器

BCD年(BCDYEAR)寄存器

18 看门狗定时器

概述

看门狗定时器特殊寄存器

看门狗定时器控制(WTCON)寄存器

看门狗定时器数据(WTDAT)寄存器

看门狗定时器计数(WTCNT)寄存器

19 MMC/SD/SDIO控制器

特性

方框图

SD操作

SDIO操作

SDI特殊寄存器

SDI 控制寄存器(SDICON)

SDI 波特率预分频寄存器(SDIPRE)

SDI 命令参数寄存器(SDICmdArg)

SDI 命令控制寄存器(SDICmdCon)

SDI 命令状态寄存器(SDICmdSta)

SDI 响应寄存器 0(SDIRSP0)

SDI 响应寄存器 1(SDIRSP1)

SDI 响应寄存器 2(SDIRSP2)

SDI 响应寄存器 3(SDIRSP3)

SDI 数据/忙定时器寄存器(SDIDTimer)

SDI 块大小寄存器(SDIBSize)

SDI 数据控制寄存器(SDIDatCon)

SDI 数据持续(Remain)计数器寄存器(ADIDatCnt)

SDI 数据状态寄存器(ADIDatSta)

SDI FIFO状态寄存器(SDIFSTA)

SDI 中断屏蔽寄存器(SDIIntMsk)

SDI 数据寄存器(SDIDAT)

20 IIC总线接口

概述

IIC总线接口

起始和停止条件

数据传输格式

发送 ACK信号

发送 ACK信号

读写操作

总线仲裁步骤

中止条件

每种模式中操作流程图

IIC总线接口特殊寄存器

多主机 IIC总线控制(IICCON)寄存器

多主机 IIC总线控制/状态(IICSTAT)寄存器

多主机 IIC总线地址(IICADD)寄存器

多主机 IIC总线发送/接收数据移位(IICDS)寄存器

多主机 IIC总线线控制(IICLC)寄存器

21 IIS总线接口

概述

功能描述

只发送或只接收模式

音频串行接口格式

IIS总线接口特殊寄存器

IIS控制(IISCON)寄存器

IIS模式(IISMOD)寄存器

IIS预分频(IISPSR)寄存器

IIS FIFO控制(IISFCON)寄存器

IIS FIFO(IISFIFO)寄存器

22 SPI

概述

方框图

SPI操作

SPI特殊寄存器

SPI控制寄存器

SPI状态寄存器

SPI引脚控制寄存器

SPI波特率预分频寄存器

SPI发送数据寄存器

SPI接收数据寄存器

23 摄像头接口

概述

方框图

时序图

摄像头接口操作

存储器储存方式

摄像头接口特殊寄存器

源帧寄存器

窗口选择寄存器

全局控制寄存器

Yx开始地址寄存器

CBx 开始地址寄存器

CRx 开始地址寄存器

编码目标格式寄存器

编码 DMA控制寄存器

编码缩放器和预览缩放器的寄存器设置指南

编码预缩放控制寄存器

编码主缩放控制寄存器

编码 DMA目标区域寄存器

编码状态寄存器

RGB 开始地址寄存器

预览目标格式寄存器

预览 DMA控制寄存器

预览预缩放控制寄存器

预览主缩放控制寄存器

预览 DMA目标区域寄存器

预览状态寄存器

图像捕获使能寄存器

24 AC’97 控制器

概述

AC’97控制器操作

内部数据路径

AC’97操作流程图

AC-LINK数字接口协议

AC-LINK输出帧(SDATA_OUT)

AC-LINK输入帧(SDATA_IN)

AC’97掉电

掉电 AC-link

唤醒 AC-link——由 AC’97控制器触发唤醒

冷 AC’97复位

热 AC’97复位

AC’97控制器特殊寄存器

AC’97 全局控制寄存器(AC_GLBCTRL)

AC’97 全局状态寄存器(AC_GLBSTAT)

AC’97 编解码器命令寄存器(AC_CODEC_CMD)

AC’97 编解码器状态寄存器(AC_CODEC_CMD)

AC’97 PCM输入/输出通道 FIFO地址寄存器(AC_PCMADDR)

AC’97 MIC输入通道 FIFO 地址寄存器(AC_MICADDR)

AC’97 PCM输入/输出通道 FIFO数据寄存器(AC_PCMDATA)

AC’97 MIC输入通道 FIFO 数据寄存器(AC_MICDATA)

25 总线优先级

概述

26 机械数据

封装尺寸

27 电气数据

绝对最大额定值

推荐工作条件

直流电气特性

交流电气特性

XTIpll时钟时序图

EXTCLK 时钟输入时序图

当使用无PLL的EXTCLK 时的EXTCLK/HCLK

当使用了EXTCLK 的 HCLK/CLKOUT/SCLK

手动复位输入时序图

上电振荡设置时序图

睡眠模式恢复振荡设置时序图

ROM/SRAM突发读时序图(Ⅰ)

ROM/SRAM突发读时序图(Ⅱ)

ROM/SRAM周期中外部总线请求

ROM/SRAM读时序图(Ⅰ)

ROM/SRAM读时序图(Ⅱ)

ROM/SRAM写时序图(Ⅰ)

ROM/SRAM写时序图(Ⅱ)

外部 nWAIT 读时序图

外部 nWAIT 写时序图

掩模ROM单次读时序图

掩模ROM连续读时序图

SDRAM单次突发读时序图

SDRAM中外部总线请求时序图

SDRAM MRS时序图

SDRAM单次读时序图(Ⅰ)

SDRAM单次读时序图(Ⅱ)

SDRAM自动刷新时序图

SDRAM页Hit-Miss读时序图

SDRAM自刷新时序图

SDRAM单次写时序图

SDRAM页Hit-Miss写时序图

外部DMA 时序图

TFT LCD 控制器时序图

IIS 接口时序图

IIC 接口时序图

SD/MMC接口时序图

SPI接口时序图

NAND Flash地址/命令时序图

时钟时序常数

ROM/SRAM总线时序常数

存储器接口时序常数

外部总线请求时序常数

. DMA控制器模块信号时序常数

TFT LCD 控制器模块信号时序常数

IIS 控制器模块信号时序常数

IIC 总线控制器模块信号时序常数

SD/MMC接口发送/接收时序常数

SPI接口发送/接收时序常数

USB全速输出缓冲电气规范

USB低速输出缓冲电气规范

NAND Flash接口时序常数

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc