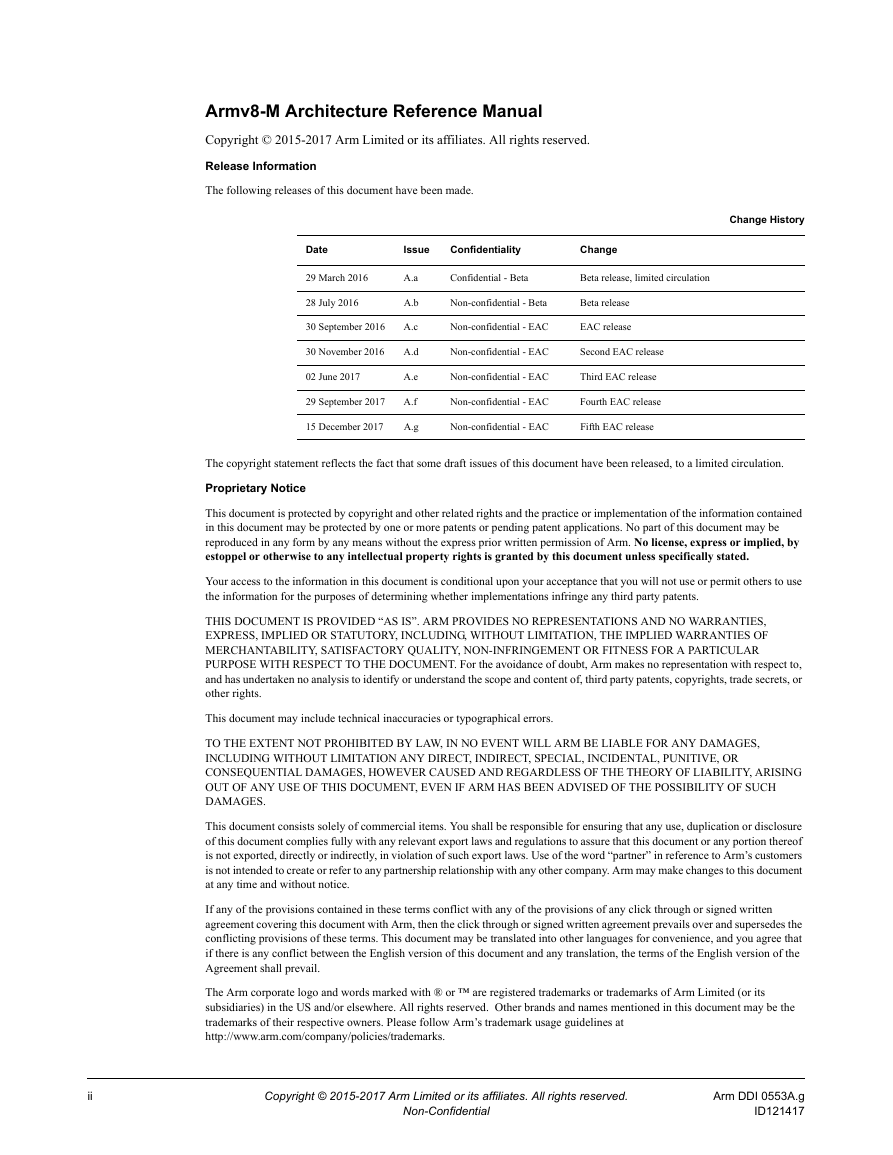

Armv8-M Architecture Reference Manual

Contents

Preface

About this book

Using this book

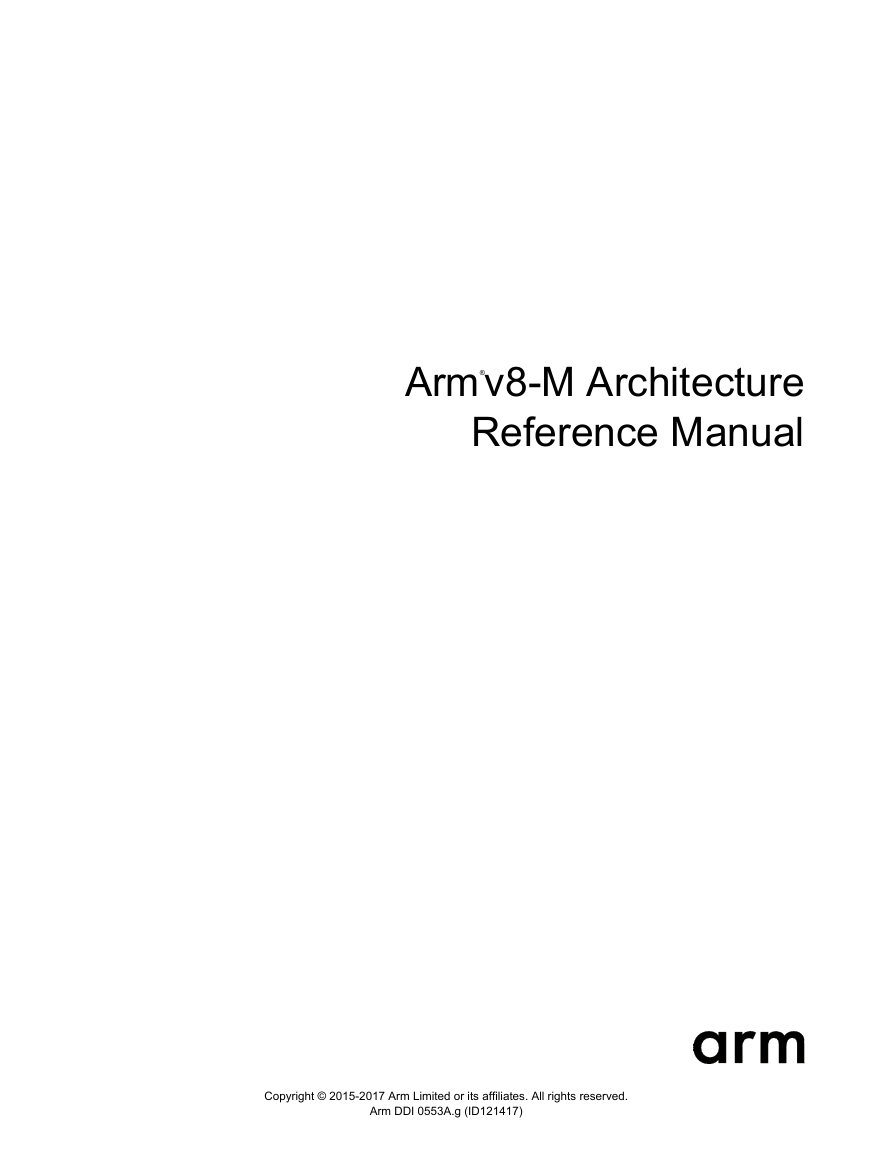

Part A, Armv8-M Architecture Introduction and Overview

Part B, Armv8-M Architecture Rules

Part C, Armv8-M Instructions

Part D, Armv8-M Registers

Part E, Armv8-M Pseudocode

Part F, Packet Protocols

Conventions

Typographic conventions

Signals

Numbers

Pseudocode descriptions

Assembler syntax descriptions

Additional reading

Arm publications

Other publications

Feedback

Feedback on this book

Part A: Armv8-M Architecture Introduction and Overview

A1: Introduction

A1.1 Document layout and terminology

A1.1.1 Structure of the document

A1.1.2 Scope of the document

A1.1.3 Intended audience

A1.1.4 Terminology, phrases

A1.1.5 Terminology, Armv8-M specific terms

A1.2 About the Armv8 architecture, and architecture profiles

A1.3 The Armv8-M architecture profile

A1.3.1 Security Extension

A1.3.2 MPU model

A1.3.3 Nested Vector Interrupt Controller

A1.3.4 Stack pointers

A1.3.5 The Armv8-M instruction set

A1.3.6 Debug

A1.4 Armv8-M variants

Part B: Armv8-M Architecture Rules

B1: Resets

B1.1 Resets, Cold reset, and Warm reset

B2: Power Management

B2.1 Power management

B2.1.1 The Wait for Event (WFE) instruction

B2.1.2 The Event register

B2.1.3 The Wait for Interrupt (WFI) instruction

B2.1.4 Sleep on exit

B3: Programmers’ Model

B3.1 PE modes, Thread mode and Handler mode

B3.2 Privileged and unprivileged execution

B3.3 Registers

B3.4 Special-purpose CONTROL register

B3.5 XPSR, APSR, IPSR, and EPSR

B3.5.1 Interrupt Program Status Register (IPSR)

B3.5.2 Execution Program Status Register (EPSR)

B3.6 Security states, Secure state, and Non-secure state

B3.7 Security states, register banking between them

B3.8 Stack pointer

B3.9 Exception numbers and exception priority numbers

B3.10 Exception enable, pending, and active bits

B3.11 Security states, exception banking

B3.12 Faults

B3.13 Priority model

B3.14 Secure address protection

B3.15 Security state transitions

B3.16 Function calls from Secure state to Non-secure state

B3.17 Function returns from Non-secure state

B3.18 Exception handling

B3.19 Exception entry, context stacking

B3.20 Exception entry, register clearing after context stacking

B3.21 Stack limit checks

B3.22 Exception return

B3.23 Integrity signature

B3.24 Exceptions during exception entry

B3.25 Exceptions during exception return

B3.26 Tail-chaining

B3.27 Exceptions, instruction resume, or instruction restart

B3.28 Vector tables

B3.29 Hardware-controlled priority escalation to HardFault

B3.30 Special-purpose mask registers, PRIMASK, BASEPRI, FAULTMASK, for configurable priority boosting

B3.31 Lockup

B3.31.1 Instruction-related lockup behavior

B3.31.2 Exception-related lockup behavior

B3.32 Context Synchronization Event

B3.33 Coprocessor support

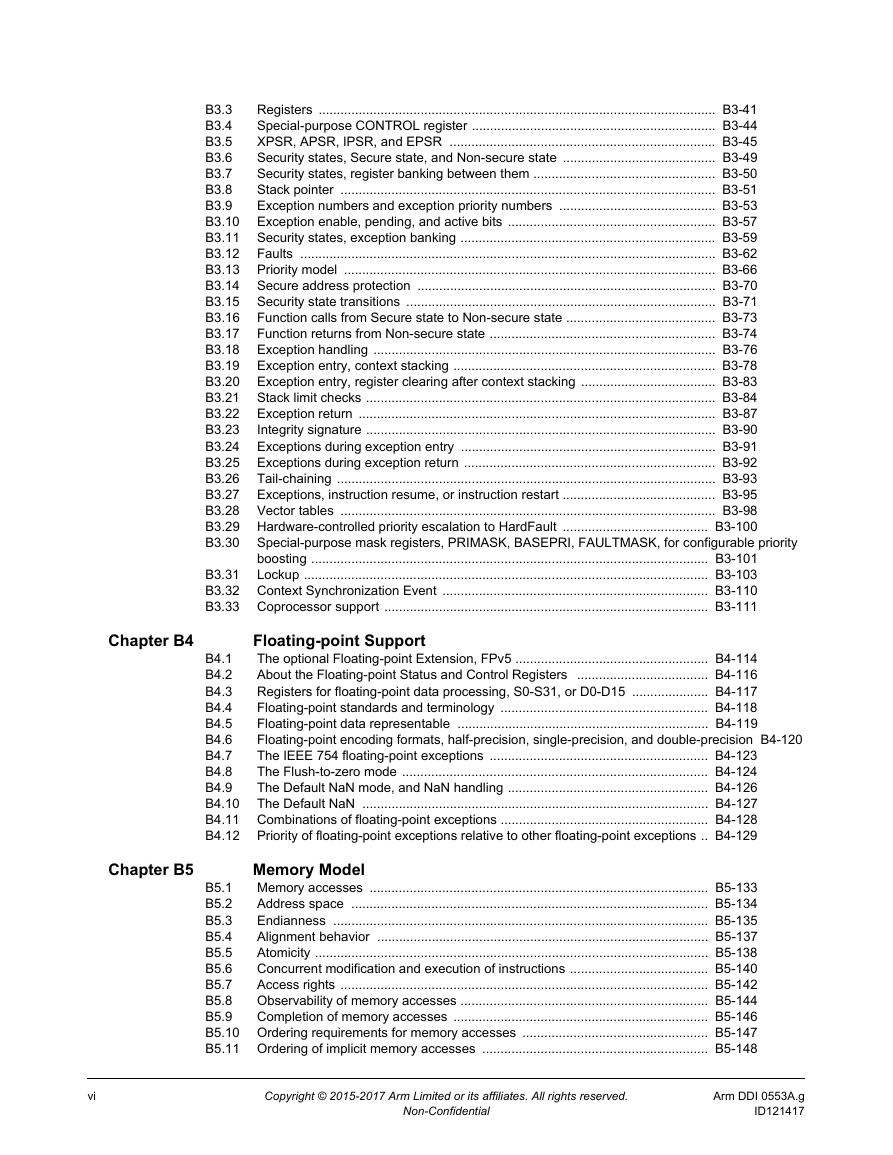

B4: Floating-point Support

B4.1 The optional Floating-point Extension, FPv5

B4.2 About the Floating-point Status and Control Registers

B4.3 Registers for floating-point data processing, S0-S31, or D0-D15

B4.4 Floating-point standards and terminology

B4.5 Floating-point data representable

B4.6 Floating-point encoding formats, half-precision, single-precision, and double-precision

B4.7 The IEEE 754 floating-point exceptions

B4.8 The Flush-to-zero mode

B4.9 The Default NaN mode, and NaN handling

B4.10 The Default NaN

B4.11 Combinations of floating-point exceptions

B4.12 Priority of floating-point exceptions relative to other floating-point exceptions

B5: Memory Model

B5.1 Memory accesses

B5.2 Address space

B5.3 Endianness

B5.4 Alignment behavior

B5.5 Atomicity

B5.5.1 Single-copy atomicity

B5.5.2 Multi-copy atomicity

B5.6 Concurrent modification and execution of instructions

B5.7 Access rights

B5.8 Observability of memory accesses

B5.9 Completion of memory accesses

B5.10 Ordering requirements for memory accesses

B5.11 Ordering of implicit memory accesses

B5.12 Ordering of explicit memory accesses

B5.13 Memory barriers

B5.13.1 Instruction Synchronization Barrier

B5.13.2 Data Memory Barrier

B5.13.3 Data Synchronization Barrier

B5.13.4 Synchronization requirements for System Control Space

B5.14 Normal memory

B5.15 Cacheability attributes

B5.16 Device memory

B5.17 Device memory attributes

B5.17.1 Gathering and non-Gathering Device memory attributes

B5.17.2 Reordering and non-Reordering Device memory attributes

B5.17.3 Early Write Acknowledgement and no Early Write Acknowledgement Device memory attributes

B5.18 Shareability domains

B5.19 Shareability attributes

B5.20 Memory access restrictions

B5.21 Mismatched memory attributes

B5.22 Load-Exclusive and Store-Exclusive accesses to Normal memory

B5.23 Load-Acquire and Store-Release accesses to memory

B5.24 Caches

B5.25 Cache identification

B5.26 Cache visibility

B5.27 Cache coherency

B5.28 Cache enabling and disabling

B5.29 Cache behavior at reset

B5.30 Behavior of Preload Data (PLD) and Preload Instruction (PLI) instructions with caches

B5.31 Branch predictors

B5.32 Cache maintenance operations

B5.33 Ordering of cache maintenance operations

B5.34 Branch predictor maintenance operations

B6: The System Address Map

B6.1 System address map

B6.2 The System region of the system address map

B6.3 The System Control Space (SCS)

B7: Synchronization and Semaphores

B7.1 Exclusive access instructions

B7.2 The local monitors

B7.3 The global monitor

B7.3.1 Load-Exclusive and Store-Exclusive

B7.3.2 Load-Exclusive and Store-Exclusive in Shareable memory

B7.4 Exclusive access instructions and the monitors

B7.5 Load-Exclusive and Store-Exclusive instruction constraints

B8: The Armv8-M Protected Memory System Architecture

B8.1 Memory Protection Unit

B8.2 Security attribution

B8.3 Security attribution unit (SAU)

B8.4 IMPLEMENTATION DEFINED Attribution Unit (IDAU)

B9: The System Timer, SysTick

B9.1 The system timer, SysTick

B10: Nested Vectored Interrupt Controller

B10.1 NVIC definition

B10.2 NVIC operation

B11: Debug

B11.1 Debug feature overview

B11.1.1 Debug mechanisms

B11.1.2 Debug resources

B11.1.3 Trace

B11.2 Accessing debug features

B11.2.1 ROM table

B11.2.2 Debug System registers

B11.2.3 CoreSight and identification registers

B11.3 Debug authentication interface

B11.3.1 Halting debug authentication

B11.3.2 DebugMonitor exception authentication

B11.3.3 Non-invasive debug authentication

B11.3.4 DAP access permissions

B11.4 Debug event behavior

B11.4.1 About debug events

B11.4.2 Debug stepping

B11.4.3 Vector catch

B11.4.4 Breakpoint instructions

B11.4.5 External debug request

B11.5 Debug state

B11.6 Exiting Debug state

B11.7 Multiprocessor support

B11.7.1 Cross-halt event

B11.7.2 External restart request

B12: Debug and Trace Components

B12.1 Instrumentation Trace Macrocell

B12.1.1 About the ITM

B12.1.2 ITM operation

B12.1.3 Timestamp support

B12.1.4 Synchronization support

B12.1.5 Continuation bits

B12.2 Data Watchpoint and Trace unit

B12.2.1 About the DWT

B12.2.2 DWT unit operation

B12.2.3 Constraints on programming DWT comparators

B12.2.4 CMPMATCH trigger events

B12.2.5 Matching in detail

B12.2.6 DWT match restrictions and relaxations

B12.2.7 DWT trace restrictions and relaxations

B12.2.8 CYCCNT cycle counter and related timers

B12.2.9 Profiling counter support

B12.2.10 Program Counter sampling support

B12.3 Embedded Trace Macrocell

B12.4 Trace Port Interface Unit

B12.5 Flash Patch and Breakpoint unit

B12.5.1 About the FPB unit

B12.5.2 FPB unit operation

Part C: Armv8-M Instruction Set

C1: Instruction Set Overview

C1.1 Instruction set

C1.2 Format of instruction descriptions

C1.2.1 The title

C1.2.2 A short description

C1.2.3 The instruction encoding or encodings

C1.2.4 Any alias conditions, if applicable

C1.2.5 A list of the assembler symbols for the instruction

C1.2.6 Pseudocode describing how the instruction operates

C1.2.7 Exceptions

C1.2.8 Notes

C1.3 Pseudocode for instruction descriptions

C1.3.1 Instruction encoding diagrams and instruction pseudocode

C1.3.2 Pseudocode descriptions of operations on general-purpose registers and the PC

C1.3.3 Limitations of the instruction pseudocode

C1.4 Unified Assembler Language

C1.4.1 Conditional instructions

C1.4.2 Use of labels in UAL instruction syntax

C1.4.3 Using syntax information

C1.5 Standard assembler syntax fields

C1.6 Conditional execution

C1.6.1 Pseudocode details of conditional execution

C1.6.2 Conditional execution of undefined instructions

C1.6.3 Interaction of undefined instruction behavior with unpredictable or constrained unpredictable instruction behavior

C1.6.4 ITSTATE

C1.6.5 Branching into and out of an IT block

C1.7 Instruction set encoding information

C1.7.1 UNDEFINED and UNPREDICTABLE instruction set space

C1.7.2 Use of 0b1111 as a register specifier

C1.7.3 Use of 0b1101 as a register specifier

C1.7.4 Branching

C1.8 Modified immediate constants

C1.8.1 Operation of modified immediate constants

C1.9 NOP-compatible hint instructions

C1.10 Instruction set, interworking support

C1.11 Instruction set, interstating support

C1.12 SBZ or SBO fields in instructions

C2: Instruction Specification

C2.1 Top level T32 instruction set encoding

C2.2 16-bit T32 instruction encoding

C2.2.1 Shift (immediate), add, subtract, move, and compare

Add, subtract (three low registers)

Add, subtract (two low registers and immediate)

Add, subtract, compare, move (one low register and immediate)

C2.2.2 Data-processing (two low registers)

C2.2.3 Special data instructions and branch and exchange

Branch and exchange

Add, subtract, compare, move (two high registers)

C2.2.4 Load/store (register offset)

C2.2.5 Load/store word/byte (immediate offset)

C2.2.6 Load/store halfword (immediate offset)

C2.2.7 Load/store (SP-relative)

C2.2.8 Add PC/SP (immediate)

C2.2.9 Miscellaneous 16-bit instructions

Adjust SP (immediate)

Extend

Reverse bytes

Hints

Push and Pop

C2.2.10 Load/store multiple

C2.2.11 Conditional branch, and Supervisor Call

Exception generation

C2.3 32-bit T32 instruction encoding

C2.3.1 Load/store (multiple, dual, exclusive, acquire-release), table branch

Load/store multiple

Load/store exclusive, load-acquire/store-release, table branch

Load/store dual (post-indexed)

Load/store dual (literal and immediate)

Load/store dual (pre-indexed), secure gateway

C2.3.2 Data-processing (shifted register)

C2.3.3 Data-processing (modified immediate)

C2.3.4 Data-processing (plain binary immediate)

Data-processing (simple immediate)

Move Wide (16-bit immediate)

Saturate, Bitfield

C2.3.5 Branches and miscellaneous control

Hints

Miscellaneous system

Exception generation

C2.3.6 Load/store single

Load/store, unsigned (register offset)

Load/store, unsigned (immediate, post-indexed)

Load/store, unsigned (negative immediate)

Load/store, unsigned (unprivileged)

Load/store, unsigned (immediate, pre-indexed)

Load/store, unsigned (positive immediate)

Load, unsigned (literal)

Load/store, signed (register offset)

Load/store, signed (immediate, post-indexed)

Load/store, signed (negative immediate)

Load/store, signed (unprivileged)

Load/store, signed (immediate, pre-indexed)

Load/store, signed (positive immediate)

Load, signed (literal)

C2.3.7 Data-processing (register)

Register extends

Parallel add-subtract

Data-processing (two source registers)

C2.3.8 Multiply, multiply accumulate, and absolute difference

Multiply and absolute difference

C2.3.9 Long multiply and divide

C2.3.10 Coprocessor and floating-point instructions

Floating-point load/store and 64-bit register moves

Floating-point data-processing

Floating-point 32-bit register moves

Coprocessor

C2.4 Alphabetical list of instructions

C2.4.1 ADC (immediate)

T1

Assembler symbols

Operation

C2.4.2 ADC (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.3 ADD (SP plus immediate)

T1

T2

T3

T4

Assembler symbols

Operation for all encodings

C2.4.4 ADD (SP plus register)

T1

T2

T3

Assembler symbols

Operation for all encodings

C2.4.5 ADD (immediate)

T1

T2

T3

T4

Assembler symbols

Operation for all encodings

C2.4.6 ADD (immediate, to PC)

T1

T3

Assembler symbols

Operation for all encodings

C2.4.7 ADD (register)

T1

T2

T3

Assembler symbols

Operation for all encodings

C2.4.8 ADR

T1

T2

T3

Alias conditions

Assembler symbols

Operation for all encodings

C2.4.9 AND (immediate)

T1

Assembler symbols

Operation

C2.4.10 AND (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.11 ASR (immediate)

T2

T3

Assembler symbols

Operation for all encodings

C2.4.12 ASR (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.13 ASRS (immediate)

T2

T3

Assembler symbols

Operation for all encodings

C2.4.14 ASRS (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.15 B

T1

T2

T3

T4

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.16 BFC

T1

Assembler symbols

Operation

C2.4.17 BFI

T1

Assembler symbols

Operation

C2.4.18 BIC (immediate)

T1

Assembler symbols

Operation

C2.4.19 BIC (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.20 BKPT

T1

Assembler symbols

Operation

C2.4.21 BL

T1

Assembler symbols

Operation

C2.4.22 BLX, BLXNS

T1

Assembler symbols

Operation

CONSTRAINED UNPREDICTABLE behavior

C2.4.23 BX, BXNS

T1

Assembler symbols

Operation

C2.4.24 CBNZ, CBZ

T1

Assembler symbols

Operation

C2.4.25 CDP, CDP2

T1

T2

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.26 CLREX

T1

Assembler symbols

Operation

C2.4.27 CLZ

T1

Assembler symbols

Operation

C2.4.28 CMN (immediate)

T1

Assembler symbols

Operation

C2.4.29 CMN (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.30 CMP (immediate)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.31 CMP (register)

T1

T2

T3

Assembler symbols

Operation for all encodings

C2.4.32 CPS

T1

Assembler symbols

Operation

C2.4.33 DBG

T1

Assembler symbols

Operation

C2.4.34 DMB

T1

Assembler symbols

Operation

C2.4.35 DSB

T1

Assembler symbols

Operation

C2.4.36 EOR (immediate)

T1

Assembler symbols

Operation

C2.4.37 EOR (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.38 FLDMDBX, FLDMIAX

T1

Notes for all encodings

Assembler symbols

Operation

C2.4.39 FSTMDBX, FSTMIAX

T1

Notes for all encodings

Assembler symbols

Operation

C2.4.40 ISB

T1

Assembler symbols

Operation

C2.4.41 IT

T1

Notes for all encodings

Assembler symbols

Operation

C2.4.42 LDA

T1

Assembler symbols

Operation

C2.4.43 LDAB

T1

Assembler symbols

Operation

C2.4.44 LDAEX

T1

Assembler symbols

Operation

C2.4.45 LDAEXB

T1

Assembler symbols

Operation

C2.4.46 LDAEXH

T1

Assembler symbols

Operation

C2.4.47 LDAH

T1

Assembler symbols

Operation

C2.4.48 LDC, LDC2 (immediate)

T1

T2

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.49 LDC, LDC2 (literal)

T1

T2

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.50 LDM, LDMIA, LDMFD

T1

T2

T3

Assembler symbols

Operation for all encodings

C2.4.51 LDMDB, LDMEA

T1

Assembler symbols

Operation

C2.4.52 LDR (immediate)

T1

T2

T3

T4

Alias conditions

Assembler symbols

Operation for all encodings

constrained unpredictable behavior

C2.4.53 LDR (literal)

T1

T2

Assembler symbols

Operation for all encodings

constrained unpredictable behavior

C2.4.54 LDR (register)

T1

T2

Assembler symbols

Operation for all encodings

constrained unpredictable behavior

C2.4.55 LDRB (immediate)

T1

T2

T3

Assembler symbols

Operation for all encodings

C2.4.56 LDRB (literal)

T1

Assembler symbols

Operation

C2.4.57 LDRB (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.58 LDRBT

T1

Assembler symbols

Operation

C2.4.59 LDRD (immediate)

T1

Notes for all encodings

Assembler symbols

Operation

C2.4.60 LDRD (literal)

T1

Notes for all encodings

Assembler symbols

Operation

constrained unpredictable behavior

C2.4.61 LDREX

T1

Assembler symbols

Operation

C2.4.62 LDREXB

T1

Assembler symbols

Operation

C2.4.63 LDREXH

T1

Assembler symbols

Operation

C2.4.64 LDRH (immediate)

T1

T2

T3

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.65 LDRH (literal)

T1

Assembler symbols

Operation

C2.4.66 LDRH (register)

T1

T2

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.67 LDRHT

T1

Assembler symbols

Operation

C2.4.68 LDRSB (immediate)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.69 LDRSB (literal)

T1

Assembler symbols

Operation

C2.4.70 LDRSB (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.71 LDRSBT

T1

Assembler symbols

Operation

C2.4.72 LDRSH (immediate)

T1

T2

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.73 LDRSH (literal)

T1

Notes for all encodings

Assembler symbols

Operation

C2.4.74 LDRSH (register)

T1

T2

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.75 LDRSHT

T1

Assembler symbols

Operation

C2.4.76 LDRT

T1

Assembler symbols

Operation

C2.4.77 LSL (immediate)

T2

T3

Assembler symbols

Operation for all encodings

C2.4.78 LSL (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.79 LSLS (immediate)

T2

T3

Assembler symbols

Operation for all encodings

C2.4.80 LSLS (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.81 LSR (immediate)

T2

T3

Assembler symbols

Operation for all encodings

C2.4.82 LSR (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.83 LSRS (immediate)

T2

T3

Assembler symbols

Operation for all encodings

C2.4.84 LSRS (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.85 MCR, MCR2

T1

T2

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.86 MCRR, MCRR2

T1

T2

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.87 MLA

T1

Assembler symbols

Operation

C2.4.88 MLS

T1

Assembler symbols

Operation

C2.4.89 MOV (immediate)

T1

T2

T3

Assembler symbols

Operation for all encodings

C2.4.90 MOV (register)

T1

T2

T3

Notes for all encodings

Alias conditions

Assembler symbols

Operation for all encodings

C2.4.91 MOV, MOVS (register-shifted register)

T1

T2

Notes for all encodings

Alias conditions

Assembler symbols

Operation for all encodings

C2.4.92 MOVT

T1

Assembler symbols

Operation

C2.4.93 MRC, MRC2

T1

T2

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.94 MRRC, MRRC2

T1

T2

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.95 MRS

T1

Assembler symbols

Operation

constrained unpredictable behavior

C2.4.96 MSR (register)

T1

Assembler symbols

Operation

constrained unpredictable behavior

C2.4.97 MUL

T1

T2

Assembler symbols

Operation for all encodings

C2.4.98 MVN (immediate)

T1

Assembler symbols

Operation

C2.4.99 MVN (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.100 NOP

T1

T2

Assembler symbols

Operation for all encodings

C2.4.101 ORN (immediate)

T1

Assembler symbols

Operation

C2.4.102 ORN (register)

T1

Assembler symbols

Operation

C2.4.103 ORR (immediate)

T1

Assembler symbols

Operation

C2.4.104 ORR (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.105 PKHBT, PKHTB

T1

Assembler symbols

Operation

C2.4.106 PLD (literal)

T1

Assembler symbols

Operation

C2.4.107 PLD (register)

Register-offset

Assembler symbols

Operation

C2.4.108 PLD, PLDW (immediate)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.109 PLI (immediate, literal)

T1

T2

T3

Assembler symbols

Operation for all encodings

C2.4.110 PLI (register)

T1

Assembler symbols

Operation

C2.4.111 POP (multiple registers)

T2

T3

Assembler symbols

Operation for all encodings

C2.4.112 POP (single register)

T4

Assembler symbols

Operation

C2.4.113 PUSH (multiple registers)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.114 PUSH (single register)

T4

Assembler symbols

Operation

C2.4.115 QADD

T1

Assembler symbols

Operation

C2.4.116 QADD16

T1

Assembler symbols

Operation

C2.4.117 QADD8

T1

Assembler symbols

Operation

C2.4.118 QASX

T1

Assembler symbols

Operation

C2.4.119 QDADD

T1

Assembler symbols

Operation

C2.4.120 QDSUB

T1

Assembler symbols

Operation

C2.4.121 QSAX

T1

Assembler symbols

Operation

C2.4.122 QSUB

T1

Assembler symbols

Operation

C2.4.123 QSUB16

T1

Assembler symbols

Operation

C2.4.124 QSUB8

T1

Assembler symbols

Operation

C2.4.125 RBIT

T1

Assembler symbols

Operation

C2.4.126 REV

T1

T2

Assembler symbols

Operation for all encodings

C2.4.127 REV16

T1

T2

Assembler symbols

Operation for all encodings

C2.4.128 REVSH

T1

T2

Assembler symbols

Operation for all encodings

C2.4.129 ROR (immediate)

T3

Assembler symbols

Operation

C2.4.130 ROR (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.131 RORS (immediate)

T3

Assembler symbols

Operation

C2.4.132 RORS (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.133 RRX

T3

Assembler symbols

Operation

C2.4.134 RRXS

T3

Assembler symbols

Operation

C2.4.135 RSB (immediate)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.136 RSB (register)

T1

Assembler symbols

Operation

C2.4.137 SADD16

T1

Assembler symbols

Operation

C2.4.138 SADD8

T1

Assembler symbols

Operation

C2.4.139 SASX

T1

Assembler symbols

Operation

C2.4.140 SBC (immediate)

T1

Assembler symbols

Operation

C2.4.141 SBC (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.142 SBFX

T1

Assembler symbols

Operation

C2.4.143 SDIV

T1

Assembler symbols

Operation

C2.4.144 SEL

T1

Assembler symbols

Operation

C2.4.145 SEV

T1

T2

Assembler symbols

Operation for all encodings

C2.4.146 SG

T1

Assembler symbols

Operation

C2.4.147 SHADD16

T1

Assembler symbols

Operation

C2.4.148 SHADD8

T1

Assembler symbols

Operation

C2.4.149 SHASX

T1

Assembler symbols

Operation

C2.4.150 SHSAX

T1

Assembler symbols

Operation

C2.4.151 SHSUB16

T1

Assembler symbols

Operation

C2.4.152 SHSUB8

T1

Assembler symbols

Operation

C2.4.153 SMLABB, SMLABT, SMLATB, SMLATT

T1

Assembler symbols

Operation

C2.4.154 SMLAD, SMLADX

T1

Assembler symbols

Operation

C2.4.155 SMLAL

T1

Assembler symbols

Operation

C2.4.156 SMLALBB, SMLALBT, SMLALTB, SMLALTT

T1

Assembler symbols

Operation

C2.4.157 SMLALD, SMLALDX

T1

Assembler symbols

Operation

C2.4.158 SMLAWB, SMLAWT

T1

Assembler symbols

Operation

C2.4.159 SMLSD, SMLSDX

T1

Assembler symbols

Operation

C2.4.160 SMLSLD, SMLSLDX

T1

Assembler symbols

Operation

C2.4.161 SMMLA, SMMLAR

T1

Assembler symbols

Operation

C2.4.162 SMMLS, SMMLSR

T1

Assembler symbols

Operation

C2.4.163 SMMUL, SMMULR

T1

Assembler symbols

Operation

C2.4.164 SMUAD, SMUADX

T1

Assembler symbols

Operation

C2.4.165 SMULBB, SMULBT, SMULTB, SMULTT

T1

Assembler symbols

Operation

C2.4.166 SMULL

T1

Assembler symbols

Operation

C2.4.167 SMULWB, SMULWT

T1

Assembler symbols

Operation

C2.4.168 SMUSD, SMUSDX

T1

Assembler symbols

Operation

C2.4.169 SSAT

T1

Assembler symbols

Operation

C2.4.170 SSAT16

T1

Assembler symbols

Operation

C2.4.171 SSAX

T1

Assembler symbols

Operation

C2.4.172 SSUB16

T1

Assembler symbols

Operation

C2.4.173 SSUB8

T1

Assembler symbols

Operation

C2.4.174 STC, STC2

T1

T2

Notes for all encodings

Assembler symbols

Operation for all encodings

C2.4.175 STL

T1

Assembler symbols

Operation

C2.4.176 STLB

T1

Assembler symbols

Operation

C2.4.177 STLEX

T1

Assembler symbols

Operation

C2.4.178 STLEXB

T1

Assembler symbols

Operation

C2.4.179 STLEXH

T1

Assembler symbols

Operation

C2.4.180 STLH

T1

Assembler symbols

Operation

C2.4.181 STM, STMIA, STMEA

T1

T2

Assembler symbols

Operation for all encodings

C2.4.182 STMDB, STMFD

T1

T2

Assembler symbols

Operation for all encodings

C2.4.183 STR (immediate)

T1

T2

T3

T4

Alias conditions

Assembler symbols

Operation for all encodings

C2.4.184 STR (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.185 STRB (immediate)

T1

T2

T3

Assembler symbols

Operation for all encodings

C2.4.186 STRB (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.187 STRBT

T1

Assembler symbols

Operation

C2.4.188 STRD (immediate)

T1

Notes for all encodings

Assembler symbols

Operation

C2.4.189 STREX

T1

Assembler symbols

Operation

C2.4.190 STREXB

T1

Assembler symbols

Operation

C2.4.191 STREXH

T1

Assembler symbols

Operation

C2.4.192 STRH (immediate)

T1

T2

T3

Assembler symbols

Operation for all encodings

C2.4.193 STRH (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.194 STRHT

T1

Assembler symbols

Operation

C2.4.195 STRT

T1

Assembler symbols

Operation

C2.4.196 SUB (SP minus immediate)

T1

T2

T3

Assembler symbols

Operation for all encodings

C2.4.197 SUB (SP minus register)

T1

Assembler symbols

Operation

C2.4.198 SUB (immediate)

T1

T2

T3

T4

Assembler symbols

Operation for all encodings

C2.4.199 SUB (immediate, from PC)

T2

Assembler symbols

Operation

C2.4.200 SUB (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.201 SVC

T1

Assembler symbols

Operation

C2.4.202 SXTAB

T1

Assembler symbols

Operation

C2.4.203 SXTAB16

T1

Assembler symbols

Operation

C2.4.204 SXTAH

T1

Assembler symbols

Operation

C2.4.205 SXTB

T1

T2

Assembler symbols

Operation for all encodings

C2.4.206 SXTB16

T1

Assembler symbols

Operation

C2.4.207 SXTH

T1

T2

Assembler symbols

Operation for all encodings

C2.4.208 TBB, TBH

T1

Assembler symbols

Operation

C2.4.209 TEQ (immediate)

T1

Assembler symbols

Operation

C2.4.210 TEQ (register)

T1

Assembler symbols

Operation

C2.4.211 TST (immediate)

T1

Assembler symbols

Operation

C2.4.212 TST (register)

T1

T2

Assembler symbols

Operation for all encodings

C2.4.213 TT, TTT, TTA, TTAT

T1

Assembler symbols

Operation

C2.4.214 UADD16

T1

Assembler symbols

Operation

C2.4.215 UADD8

T1

Assembler symbols

Operation

C2.4.216 UASX

T1

Assembler symbols

Operation

C2.4.217 UBFX

T1

Assembler symbols

Operation

C2.4.218 UDF

T1

T2

Assembler symbols

Operation for all encodings

C2.4.219 UDIV

T1

Assembler symbols

Operation

C2.4.220 UHADD16

T1

Assembler symbols

Operation

C2.4.221 UHADD8

T1

Assembler symbols

Operation

C2.4.222 UHASX

T1

Assembler symbols

Operation

C2.4.223 UHSAX

T1

Assembler symbols

Operation

C2.4.224 UHSUB16

T1

Assembler symbols

Operation

C2.4.225 UHSUB8

T1

Assembler symbols

Operation

C2.4.226 UMAAL

T1

Assembler symbols

Operation

C2.4.227 UMLAL

T1

Assembler symbols

Operation

C2.4.228 UMULL

T1

Assembler symbols

Operation

C2.4.229 UQADD16

T1

Assembler symbols

Operation

C2.4.230 UQADD8

T1

Assembler symbols

Operation

C2.4.231 UQASX

T1

Assembler symbols

Operation

C2.4.232 UQSAX

T1

Assembler symbols

Operation

C2.4.233 UQSUB16

T1

Assembler symbols

Operation

C2.4.234 UQSUB8

T1

Assembler symbols

Operation

C2.4.235 USAD8

T1

Assembler symbols

Operation

C2.4.236 USADA8

T1

Assembler symbols

Operation

C2.4.237 USAT

T1

Assembler symbols

Operation

C2.4.238 USAT16

T1

Assembler symbols

Operation

C2.4.239 USAX

T1

Assembler symbols

Operation

C2.4.240 USUB16

T1

Assembler symbols

Operation

C2.4.241 USUB8

T1

Assembler symbols

Operation

C2.4.242 UXTAB

T1

Assembler symbols

Operation

C2.4.243 UXTAB16

T1

Assembler symbols

Operation

C2.4.244 UXTAH

T1

Assembler symbols

Operation

C2.4.245 UXTB

T1

T2

Assembler symbols

Operation for all encodings

C2.4.246 UXTB16

T1

Assembler symbols

Operation

C2.4.247 UXTH

T1

T2

Assembler symbols

Operation for all encodings

C2.4.248 VABS

T2

Assembler symbols

Operation

C2.4.249 VADD

T2

Assembler symbols

Operation

C2.4.250 VCMP

T1

T2

Assembler symbols

Operation for all encodings

C2.4.251 VCMPE

T1

T2

Assembler symbols

Operation for all encodings

C2.4.252 VCVT (between double-precision and single-precision)

T1

Assembler symbols

Operation

C2.4.253 VCVT (between floating-point and fixed-point)

T1

Assembler symbols

Operation

C2.4.254 VCVT (floating-point to integer)

T1

Notes for all encodings

Assembler symbols

Operation

C2.4.255 VCVT (integer to floating-point)

T1

Notes for all encodings

Assembler symbols

Operation

C2.4.256 VCVTA

T1

Assembler symbols

Operation

C2.4.257 VCVTB

T1

Assembler symbols

Operation

C2.4.258 VCVTM

T1

Assembler symbols

Operation

C2.4.259 VCVTN

T1

Assembler symbols

Operation

C2.4.260 VCVTP

T1

Assembler symbols

Operation

C2.4.261 VCVTR

T1

Notes for all encodings

Assembler symbols

Operation

C2.4.262 VCVTT

T1

Assembler symbols

Operation

C2.4.263 VDIV

T1

Assembler symbols

Operation

C2.4.264 VFMA

T2

Assembler symbols

Operation

C2.4.265 VFMS

T2

Assembler symbols

Operation

C2.4.266 VFNMA

T1

Assembler symbols

Operation

C2.4.267 VFNMS

T1

Assembler symbols

Operation

C2.4.268 VLDM

T1

T2

Notes for all encodings

Alias conditions

Assembler symbols

Operation for all encodings

C2.4.269 VLDR

T1

T2

Assembler symbols

Operation for all encodings

C2.4.270 VLLDM

T1

Assembler symbols

Operation

C2.4.271 VLSTM

T1

Assembler symbols

Operation

C2.4.272 VMAXNM

T2

Assembler symbols

Operation

C2.4.273 VMINNM

T2

Assembler symbols

Operation

C2.4.274 VMLA

T2

Assembler symbols

Operation

C2.4.275 VMLS

T2

Assembler symbols

Operation

C2.4.276 VMOV (between general-purpose register and single-precision register)

T1

Assembler symbols

Operation

C2.4.277 VMOV (between two general-purpose registers and a doubleword register)

T1

Assembler symbols

Operation

C2.4.278 VMOV (between two general-purpose registers and two single-precision registers)

T1

Assembler symbols

Operation

C2.4.279 VMOV (half of doubleword register to single general-purpose register)

T1

Assembler symbols

Operation

C2.4.280 VMOV (immediate)

T2

Assembler symbols

Operation

C2.4.281 VMOV (register)

T2

Assembler symbols

Operation

C2.4.282 VMOV (single general-purpose register to half of doubleword register)

T1

Assembler symbols

Operation

C2.4.283 VMRS

T1

Assembler symbols

Operation

C2.4.284 VMSR

T1

Assembler symbols

Operation

C2.4.285 VMUL

T2

Assembler symbols

Operation

C2.4.286 VNEG

T2

Assembler symbols

Operation

C2.4.287 VNMLA

T1

Assembler symbols

Operation

C2.4.288 VNMLS

T1

Assembler symbols

Operation

C2.4.289 VNMUL

T1

Assembler symbols

Operation

C2.4.290 VPOP

T1

T2

Assembler symbols

Operation for all encodings

C2.4.291 VPUSH

T1

T2

Assembler symbols

Operation for all encodings

C2.4.292 VRINTA

T1

Assembler symbols

Operation

C2.4.293 VRINTM

T1

Assembler symbols

Operation

C2.4.294 VRINTN

T1

Assembler symbols

Operation

C2.4.295 VRINTP

T1

Assembler symbols

Operation

C2.4.296 VRINTR

T1

Assembler symbols

Operation

C2.4.297 VRINTX

T1

Assembler symbols

Operation

C2.4.298 VRINTZ

T1

Assembler symbols

Operation

C2.4.299 VSEL

T1

Assembler symbols

Operation

C2.4.300 VSQRT

T1

Assembler symbols

Operation

C2.4.301 VSTM

T1

T2

Notes for all encodings

Alias conditions

Assembler symbols

Operation for all encodings

C2.4.302 VSTR

T1

T2

Assembler symbols

Operation for all encodings

C2.4.303 VSUB

T2

Assembler symbols

Operation

C2.4.304 WFE

T1

T2

Assembler symbols

Operation for all encodings

C2.4.305 WFI

T1

T2

Assembler symbols

Operation for all encodings

C2.4.306 YIELD

T1

T2

Assembler symbols

Operation for all encodings

Part D: Armv8-M Registers

D1: Register Specification

D1.1 Register index

D1.1.1 Special and general-purpose registers

D1.1.2 Payloads

D1.1.3 Instrumentation Macrocell

D1.1.4 Data Watchpoint and Trace

D1.1.5 Flash Patch and Breakpoint

D1.1.6 Implementation Control Block

D1.1.7 SysTick Timer

D1.1.8 Nested Vectored Interrupt Controller

D1.1.9 System Control Block

D1.1.10 Memory Protection Unit

D1.1.11 Security Attribution Unit

D1.1.12 Debug Control Block

D1.1.13 Software Interrupt Generation

D1.1.14 Floating-Point Extension

D1.1.15 Cache Maintenance Operations

D1.1.16 Debug Identification Block

D1.1.17 Implementation Control Block (NS alias)

D1.1.18 SysTick Timer (NS alias)

D1.1.19 Nested Vectored Interrupt Controller (NS alias)

D1.1.20 System Control Block (NS alias)

D1.1.21 Memory Protection Unit (NS alias)

D1.1.22 Debug Control Block (NS alias)

D1.1.23 Software Interrupt Generation (NS alias)

D1.1.24 Floating-Point Extension (NS alias)

D1.1.25 Cache Maintenance Operations (NS alias)

D1.1.26 Debug Identification Block (NS alias)

D1.1.27 Trace Port Interface Unit

D1.2 Alphabetical list of registers

D1.2.1 ACTLR, Auxiliary Control Register

Field descriptions

D1.2.2 AFSR, Auxiliary Fault Status Register

Field descriptions

D1.2.3 AIRCR, Application Interrupt and Reset Control Register

Field descriptions

D1.2.4 APSR, Application Program Status Register

Field descriptions

D1.2.5 BASEPRI, Base Priority Mask Register

Field descriptions

D1.2.6 BFAR, BusFault Address Register

Preface

Field descriptions

D1.2.7 BFSR, BusFault Status Register

Preface

Field descriptions

D1.2.8 BPIALL, Branch Predictor Invalidate All

Field descriptions

D1.2.9 CCR, Configuration and Control Register

Field descriptions

D1.2.10 CCSIDR, Current Cache Size ID register

Preface

Field descriptions

D1.2.11 CFSR, Configurable Fault Status Register

Field descriptions

D1.2.12 CLIDR, Cache Level ID Register

Field descriptions

D1.2.13 CONTROL, Control Register

Field descriptions

D1.2.14 CPACR, Coprocessor Access Control Register

Field descriptions

D1.2.15 CPPWR, Coprocessor Power Control Register

Field descriptions

D1.2.16 CPUID, CPUID Base Register

Field descriptions

D1.2.17 CSSELR, Cache Size Selection Register

Field descriptions

D1.2.18 CTR, Cache Type Register

Field descriptions

D1.2.19 DAUTHCTRL, Debug Authentication Control Register

Field descriptions

D1.2.20 DAUTHSTATUS, Debug Authentication Status Register

Field descriptions

D1.2.21 DCCIMVAC, Data Cache line Clean and Invalidate by Address to PoC

Field descriptions

D1.2.22 DCCISW, Data Cache line Clean and Invalidate by Set/Way

Field descriptions

D1.2.23 DCCMVAC, Data Cache line Clean by Address to PoC

Field descriptions

D1.2.24 DCCMVAU, Data Cache line Clean by address to PoU

Field descriptions

D1.2.25 DCCSW, Data Cache Clean line by Set/Way

Field descriptions

D1.2.26 DCIDR0, SCS Component Identification Register 0

Field descriptions

D1.2.27 DCIDR1, SCS Component Identification Register 1

Field descriptions

D1.2.28 DCIDR2, SCS Component Identification Register 2

Field descriptions

D1.2.29 DCIDR3, SCS Component Identification Register 3

Field descriptions

D1.2.30 DCIMVAC, Data Cache line Invalidate by Address to PoC

Field descriptions

D1.2.31 DCISW, Data Cache line Invalidate by Set/Way

Field descriptions

D1.2.32 DCRDR, Debug Core Register Data Register

Field descriptions

D1.2.33 DCRSR, Debug Core Register Select Register

Field descriptions

D1.2.34 DDEVARCH, SCS Device Architecture Register

Field descriptions

D1.2.35 DDEVTYPE, SCS Device Type Register

Field descriptions

D1.2.36 DEMCR, Debug Exception and Monitor Control Register

Field descriptions

D1.2.37 DFSR, Debug Fault Status Register

Field descriptions

D1.2.38 DHCSR, Debug Halting Control and Status Register

Field descriptions

D1.2.39 DLAR, SCS Software Lock Access Register

Field descriptions

D1.2.40 DLSR, SCS Software Lock Status Register

Field descriptions

D1.2.41 DPIDR0, SCS Peripheral Identification Register 0

Field descriptions

D1.2.42 DPIDR1, SCS Peripheral Identification Register 1

Field descriptions

D1.2.43 DPIDR2, SCS Peripheral Identification Register 2

Field descriptions

D1.2.44 DPIDR3, SCS Peripheral Identification Register 3

Field descriptions

D1.2.45 DPIDR4, SCS Peripheral Identification Register 4

Field descriptions

D1.2.46 DPIDR5, SCS Peripheral Identification Register 5

Field descriptions

D1.2.47 DPIDR6, SCS Peripheral Identification Register 6

Field descriptions

D1.2.48 DPIDR7, SCS Peripheral Identification Register 7

Field descriptions

D1.2.49 DSCSR, Debug Security Control and Status Register

Field descriptions

D1.2.50 DWT_CIDR0, DWT Component Identification Register 0

Field descriptions

D1.2.51 DWT_CIDR1, DWT Component Identification Register 1

Field descriptions

D1.2.52 DWT_CIDR2, DWT Component Identification Register 2

Field descriptions

D1.2.53 DWT_CIDR3, DWT Component Identification Register 3

Field descriptions

D1.2.54 DWT_COMPn, DWT Comparator Register, n = 0 - 14

Field descriptions

D1.2.55 DWT_CPICNT, DWT CPI Count Register

Field descriptions

D1.2.56 DWT_CTRL, DWT Control Register

Field descriptions

D1.2.57 DWT_CYCCNT, DWT Cycle Count Register

Field descriptions

D1.2.58 DWT_DEVARCH, DWT Device Architecture Register

Field descriptions

D1.2.59 DWT_DEVTYPE, DWT Device Type Register

Field descriptions

D1.2.60 DWT_EXCCNT, DWT Exception Overhead Count Register

Field descriptions

D1.2.61 DWT_FOLDCNT, DWT Folded Instruction Count Register

Field descriptions

D1.2.62 DWT_FUNCTIONn, DWT Comparator Function Register, n = 0 - 14

Field descriptions

D1.2.63 DWT_LAR, DWT Software Lock Access Register

Field descriptions

D1.2.64 DWT_LSR, DWT Software Lock Status Register

Field descriptions

D1.2.65 DWT_LSUCNT, DWT LSU Count Register

Field descriptions

D1.2.66 DWT_PCSR, DWT Program Counter Sample Register

Field descriptions

D1.2.67 DWT_PIDR0, DWT Peripheral Identification Register 0

Field descriptions

D1.2.68 DWT_PIDR1, DWT Peripheral Identification Register 1

Field descriptions

D1.2.69 DWT_PIDR2, DWT Peripheral Identification Register 2

Field descriptions

D1.2.70 DWT_PIDR3, DWT Peripheral Identification Register 3

Field descriptions

D1.2.71 DWT_PIDR4, DWT Peripheral Identification Register 4

Field descriptions

D1.2.72 DWT_PIDR5, DWT Peripheral Identification Register 5

Field descriptions

D1.2.73 DWT_PIDR6, DWT Peripheral Identification Register 6

Field descriptions

D1.2.74 DWT_PIDR7, DWT Peripheral Identification Register 7

Field descriptions

D1.2.75 DWT_SLEEPCNT, DWT Sleep Count Register

Field descriptions

D1.2.76 EPSR, Execution Program Status Register

Field descriptions

D1.2.77 EXC_RETURN, Exception Return Payload

Field descriptions

D1.2.78 FAULTMASK, Fault Mask Register

Field descriptions

D1.2.79 FNC_RETURN, Function Return Payload

Field descriptions

D1.2.80 FPCAR, Floating-Point Context Address Register

Field descriptions

D1.2.81 FPCCR, Floating-Point Context Control Register

Field descriptions

D1.2.82 FPDSCR, Floating-Point Default Status Control Register

Field descriptions

D1.2.83 FPSCR, Floating-point Status and Control Register

Preface

Field descriptions

D1.2.84 FP_CIDR0, FP Component Identification Register 0

Field descriptions

D1.2.85 FP_CIDR1, FP Component Identification Register 1

Field descriptions

D1.2.86 FP_CIDR2, FP Component Identification Register 2

Field descriptions

D1.2.87 FP_CIDR3, FP Component Identification Register 3

Field descriptions

D1.2.88 FP_COMPn, Flash Patch Comparator Register, n = 0 - 125

Field descriptions

D1.2.89 FP_CTRL, Flash Patch Control Register

Field descriptions

D1.2.90 FP_DEVARCH, FPB Device Architecture Register

Field descriptions

D1.2.91 FP_DEVTYPE, FPB Device Type Register

Field descriptions

D1.2.92 FP_LAR, FPB Software Lock Access Register

Field descriptions

D1.2.93 FP_LSR, FPB Software Lock Status Register

Field descriptions

D1.2.94 FP_PIDR0, FP Peripheral Identification Register 0

Field descriptions

D1.2.95 FP_PIDR1, FP Peripheral Identification Register 1

Field descriptions

D1.2.96 FP_PIDR2, FP Peripheral Identification Register 2

Field descriptions

D1.2.97 FP_PIDR3, FP Peripheral Identification Register 3

Field descriptions

D1.2.98 FP_PIDR4, FP Peripheral Identification Register 4

Field descriptions

D1.2.99 FP_PIDR5, FP Peripheral Identification Register 5

Field descriptions

D1.2.100 FP_PIDR6, FP Peripheral Identification Register 6

Field descriptions

D1.2.101 FP_PIDR7, FP Peripheral Identification Register 7

Field descriptions

D1.2.102 FP_REMAP, Flash Patch Remap Register

Field descriptions

D1.2.103 HFSR, HardFault Status Register

Field descriptions

D1.2.104 ICIALLU, Instruction Cache Invalidate All to PoU

Field descriptions

D1.2.105 ICIMVAU, Instruction Cache line Invalidate by Address to PoU

Field descriptions

D1.2.106 ICSR, Interrupt Control and State Register

Field descriptions

D1.2.107 ICTR, Interrupt Controller Type Register

Field descriptions

D1.2.108 ID_AFR0, Auxiliary Feature Register 0

Field descriptions

D1.2.109 ID_DFR0, Debug Feature Register 0

Preface

Field descriptions

D1.2.110 ID_ISAR0, Instruction Set Attribute Register 0

Preface

Field descriptions

D1.2.111 ID_ISAR1, Instruction Set Attribute Register 1

Preface

Field descriptions

D1.2.112 ID_ISAR2, Instruction Set Attribute Register 2

Preface

Field descriptions

D1.2.113 ID_ISAR3, Instruction Set Attribute Register 3

Preface

Field descriptions

D1.2.114 ID_ISAR4, Instruction Set Attribute Register 4

Preface

Field descriptions

D1.2.115 ID_ISAR5, Instruction Set Attribute Register 5

Field descriptions

D1.2.116 ID_MMFR0, Memory Model Feature Register 0

Field descriptions

D1.2.117 ID_MMFR1, Memory Model Feature Register 1

Field descriptions

D1.2.118 ID_MMFR2, Memory Model Feature Register 2

Field descriptions

D1.2.119 ID_MMFR3, Memory Model Feature Register 3

Field descriptions

D1.2.120 ID_PFR0, Processor Feature Register 0

Field descriptions

D1.2.121 ID_PFR1, Processor Feature Register 1

Field descriptions

D1.2.122 IPSR, Interrupt Program Status Register

Field descriptions

D1.2.123 ITM_CIDR0, ITM Component Identification Register 0

Field descriptions

D1.2.124 ITM_CIDR1, ITM Component Identification Register 1

Field descriptions

D1.2.125 ITM_CIDR2, ITM Component Identification Register 2

Field descriptions

D1.2.126 ITM_CIDR3, ITM Component Identification Register 3

Field descriptions

D1.2.127 ITM_DEVARCH, ITM Device Architecture Register

Field descriptions

D1.2.128 ITM_DEVTYPE, ITM Device Type Register

Field descriptions

D1.2.129 ITM_LAR, ITM Software Lock Access Register

Field descriptions

D1.2.130 ITM_LSR, ITM Software Lock Status Register

Field descriptions

D1.2.131 ITM_PIDR0, ITM Peripheral Identification Register 0

Field descriptions

D1.2.132 ITM_PIDR1, ITM Peripheral Identification Register 1

Field descriptions

D1.2.133 ITM_PIDR2, ITM Peripheral Identification Register 2

Field descriptions

D1.2.134 ITM_PIDR3, ITM Peripheral Identification Register 3

Field descriptions

D1.2.135 ITM_PIDR4, ITM Peripheral Identification Register 4

Field descriptions

D1.2.136 ITM_PIDR5, ITM Peripheral Identification Register 5

Field descriptions

D1.2.137 ITM_PIDR6, ITM Peripheral Identification Register 6

Field descriptions

D1.2.138 ITM_PIDR7, ITM Peripheral Identification Register 7

Field descriptions

D1.2.139 ITM_STIMn, ITM Stimulus Port Register, n = 0 - 255

Field descriptions

D1.2.140 ITM_TCR, ITM Trace Control Register

Field descriptions

D1.2.141 ITM_TERn, ITM Trace Enable Register, n = 0 - 7

Field descriptions

D1.2.142 ITM_TPR, ITM Trace Privilege Register

Field descriptions

D1.2.143 LR, Link Register

Field descriptions

D1.2.144 MAIR_ATTR, Memory Attribute Indirection Register Attributes

Field descriptions

D1.2.145 MMFAR, MemManage Fault Address Register

Field descriptions

D1.2.146 MMFSR, MemManage Fault Status Register

Field descriptions

D1.2.147 MPU_CTRL, MPU Control Register

Field descriptions

D1.2.148 MPU_MAIR0, MPU Memory Attribute Indirection Register 0

Preface

Field descriptions

D1.2.149 MPU_MAIR1, MPU Memory Attribute Indirection Register 1

Preface

Field descriptions

D1.2.150 MPU_RBAR, MPU Region Base Address Register

Preface

Field descriptions

D1.2.151 MPU_RBAR_An, MPU Region Base Address Register Alias, n = 1 - 3

Preface

Field descriptions

D1.2.152 MPU_RLAR, MPU Region Limit Address Register

Preface

Field descriptions

D1.2.153 MPU_RLAR_An, MPU Region Limit Address Register Alias, n = 1 - 3

Preface

Field descriptions

D1.2.154 MPU_RNR, MPU Region Number Register

Field descriptions

D1.2.155 MPU_TYPE, MPU Type Register

Field descriptions

D1.2.156 MSPLIM, Main Stack Pointer Limit Register

Field descriptions

D1.2.157 MVFR0, Media and VFP Feature Register 0

Preface

Field descriptions

D1.2.158 MVFR1, Media and VFP Feature Register 1

Preface

Field descriptions

D1.2.159 MVFR2, Media and VFP Feature Register 2

Preface

Field descriptions

D1.2.160 NSACR, Non-secure Access Control Register

Field descriptions

D1.2.161 NVIC_IABRn, Interrupt Active Bit Register, n = 0 - 15

Field descriptions

D1.2.162 NVIC_ICERn, Interrupt Clear Enable Register, n = 0 - 15

Field descriptions

D1.2.163 NVIC_ICPRn, Interrupt Clear Pending Register, n = 0 - 15

Field descriptions

D1.2.164 NVIC_IPRn, Interrupt Priority Register, n = 0 - 123

Field descriptions

D1.2.165 NVIC_ISERn, Interrupt Set Enable Register, n = 0 - 15

Field descriptions

D1.2.166 NVIC_ISPRn, Interrupt Set Pending Register, n = 0 - 15

Field descriptions

D1.2.167 NVIC_ITNSn, Interrupt Target Non-secure Register, n = 0 - 15

Field descriptions

D1.2.168 PC, Program Counter

Field descriptions

D1.2.169 PRIMASK, Exception Mask Register

Field descriptions

D1.2.170 PSPLIM, Process Stack Pointer Limit Register

Field descriptions

D1.2.171 Rn, General-Purpose Register, n = 0 - 12

Field descriptions

D1.2.172 RETPSR, Combined Exception Return Program Status Registers

Field descriptions

D1.2.173 SAU_CTRL, SAU Control Register

Preface

Field descriptions

D1.2.174 SAU_RBAR, SAU Region Base Address Register

Field descriptions

D1.2.175 SAU_RLAR, SAU Region Limit Address Register

Field descriptions

D1.2.176 SAU_RNR, SAU Region Number Register

Field descriptions

D1.2.177 SAU_TYPE, SAU Type Register

Field descriptions

D1.2.178 SCR, System Control Register

Field descriptions

D1.2.179 SFAR, Secure Fault Address Register

Field descriptions

D1.2.180 SFSR, Secure Fault Status Register

Field descriptions

D1.2.181 SHCSR, System Handler Control and State Register

Preface

Field descriptions

D1.2.182 SHPR1, System Handler Priority Register 1

Field descriptions

D1.2.183 SHPR2, System Handler Priority Register 2

Field descriptions

D1.2.184 SHPR3, System Handler Priority Register 3

Field descriptions

D1.2.185 SP, Current Stack Pointer Register

Field descriptions

D1.2.186 SP_NS, Stack Pointer (Non-secure)

Field descriptions

D1.2.187 STIR, Software Triggered Interrupt Register

Field descriptions

D1.2.188 SYST_CALIB, SysTick Calibration Value Register

Preface

Field descriptions

D1.2.189 SYST_CSR, SysTick Control and Status Register

Preface

Field descriptions

D1.2.190 SYST_CVR, SysTick Current Value Register

Preface

Field descriptions

D1.2.191 SYST_RVR, SysTick Reload Value Register

Preface

Field descriptions

D1.2.192 TPIU_ACPR, TPIU Asynchronous Clock Prescaler Register

Field descriptions

D1.2.193 TPIU_CIDR0, TPIU Component Identification Register 0

Field descriptions

D1.2.194 TPIU_CIDR1, TPIU Component Identification Register 1

Field descriptions

D1.2.195 TPIU_CIDR2, TPIU Component Identification Register 2

Field descriptions

D1.2.196 TPIU_CIDR3, TPIU Component Identification Register 3

Field descriptions

D1.2.197 TPIU_CSPSR, TPIU Current Parallel Port Sizes Register

Field descriptions

D1.2.198 TPIU_DEVTYPE, TPIU Device Type Register

Field descriptions

D1.2.199 TPIU_FFCR, TPIU Formatter and Flush Control Register

Field descriptions

D1.2.200 TPIU_FFSR, TPIU Formatter and Flush Status Register

Field descriptions

D1.2.201 TPIU_LAR, TPIU Software Lock Access Register

Field descriptions

D1.2.202 TPIU_LSR, TPIU Software Lock Status Register

Field descriptions

D1.2.203 TPIU_PIDR0, TPIU Peripheral Identification Register 0

Field descriptions

D1.2.204 TPIU_PIDR1, TPIU Peripheral Identification Register 1

Field descriptions

D1.2.205 TPIU_PIDR2, TPIU Peripheral Identification Register 2

Field descriptions

D1.2.206 TPIU_PIDR3, TPIU Peripheral Identification Register 3

Field descriptions

D1.2.207 TPIU_PIDR4, TPIU Peripheral Identification Register 4

Field descriptions

D1.2.208 TPIU_PIDR5, TPIU Peripheral Identification Register 5

Field descriptions

D1.2.209 TPIU_PIDR6, TPIU Peripheral Identification Register 6

Field descriptions

D1.2.210 TPIU_PIDR7, TPIU Peripheral Identification Register 7

Field descriptions

D1.2.211 TPIU_PSCR, TPIU Periodic Synchronization Control Register

Field descriptions

D1.2.212 TPIU_SPPR, TPIU Selected Pin Protocol Register

Field descriptions

D1.2.213 TPIU_SSPSR, TPIU Supported Parallel Port Sizes Register

Field descriptions

D1.2.214 TPIU_TYPE, TPIU Device Identifier Register

Field descriptions

D1.2.215 TT_RESP, Test Target Response Payload

Field descriptions

D1.2.216 UFSR, UsageFault Status Register

Field descriptions

D1.2.217 VTOR, Vector Table Offset Register

Field descriptions

D1.2.218 XPSR, Combined Program Status Registers

Field descriptions

Part E: Armv8-M Pseudocode

E1: Arm Pseudocode Definition

E1.1 About the Arm pseudocode

E1.1.1 General limitations of Arm pseudocode

E1.2 Data types

E1.2.1 General data type rules

E1.2.2 Bitstrings

E1.2.3 Integers

E1.2.4 Reals

E1.2.5 Booleans

E1.2.6 Enumerations

E1.2.7 Structures

E1.2.8 Tuples

E1.2.9 Arrays

E1.3 Operators

E1.3.1 Relational operators

E1.3.2 Boolean operators

E1.3.3 Bitstring operators

E1.3.4 Arithmetic operators

E1.3.5 The assignment operator

E1.3.6 Precedence rules

E1.3.7 Conditional expressions

E1.3.8 Operator polymorphism

E1.4 Statements and control structures

E1.4.1 Statements and Indentation

E1.4.2 Function and procedure calls

E1.4.3 Conditional control structures

E1.4.4 Loop control structures

E1.4.5 Special statements

E1.4.6 Comments

E1.5 Built-in functions

E1.5.1 Bitstring manipulation functions

E1.5.2 Arithmetic functions

E1.6 Arm pseudocode definition index

E1.7 Additional functions

E1.7.1 IsSee()

E1.7.2 IsUndefined()

E2: Pseudocode Specification

E2.1 Alphabetical Pseudocode List

E2.1.1 ALUWritePC

E2.1.2 ASR

E2.1.3 ASR_C

E2.1.4 AccType

E2.1.5 AccessAttributes

E2.1.6 ActivateException

E2.1.7 AddWithCarry

E2.1.8 AddressDescriptor

E2.1.9 BKPTInstrDebugEvent

E2.1.10 BLXWritePC

E2.1.11 BXWritePC

E2.1.12 BigEndian

E2.1.13 BigEndianReverse

E2.1.14 BranchTo

E2.1.15 BranchToAndCommit

E2.1.16 BranchToNS

E2.1.17 BranchWritePC

E2.1.18 CallSupervisor

E2.1.19 CanHaltOnEvent

E2.1.20 CanPendMonitorOnEvent

E2.1.21 CheckCPEnabled

E2.1.22 CheckDecodeFaults

E2.1.23 CheckPermission

E2.1.24 ClearEventRegister

E2.1.25 ClearExclusiveByAddress

E2.1.26 ClearExclusiveLocal

E2.1.27 ComparePriorities

E2.1.28 ConditionHolds

E2.1.29 ConditionPassed

E2.1.30 ConstrainUnpredictableBool

E2.1.31 ConsumeExcStackFrame

E2.1.32 Coproc_Accepted

E2.1.33 Coproc_DoneLoading

E2.1.34 Coproc_DoneStoring

E2.1.35 Coproc_GetOneWord

E2.1.36 Coproc_GetTwoWords

E2.1.37 Coproc_GetWordToStore

E2.1.38 Coproc_InternalOperation

E2.1.39 Coproc_SendLoadedWord

E2.1.40 Coproc_SendOneWord

E2.1.41 Coproc_SendTwoWords

E2.1.42 CreateException

E2.1.43 CurrentCond

E2.1.44 CurrentMode

E2.1.45 CurrentModeIsPrivileged

E2.1.46 D

E2.1.47 DWT_AddressCompare

E2.1.48 DWT_CycCountMatch

E2.1.49 DWT_DataAddressMatch

E2.1.50 DWT_DataMatch

E2.1.51 DWT_DataValueMatch

E2.1.52 DWT_InstructionAddressMatch

E2.1.53 DWT_InstructionMatch

E2.1.54 DWT_ValidMatch

E2.1.55 DataMemoryBarrier

E2.1.56 DataSynchronizationBarrier

E2.1.57 Deactivate

E2.1.58 Debug_authentication

E2.1.59 DecodeExecute

E2.1.60 DecodeImmShift

E2.1.61 DecodeRegShift

E2.1.62 DefaultExcInfo

E2.1.63 DefaultMemoryAttributes

E2.1.64 DefaultPermissions

E2.1.65 DerivedLateArrival

E2.1.66 DeviceType

E2.1.67 EndOfInstruction

E2.1.68 EventRegistered

E2.1.69 ExcInfo

E2.1.70 ExceptionActiveBitCount

E2.1.71 ExceptionDetails

E2.1.72 ExceptionEnabled

E2.1.73 ExceptionEntry

E2.1.74 ExceptionPriority

E2.1.75 ExceptionReturn

E2.1.76 ExceptionTaken

E2.1.77 ExceptionTargetsSecure

E2.1.78 ExclusiveMonitorsPass

E2.1.79 ExecuteCPCheck

E2.1.80 ExecuteFPCheck

E2.1.81 ExecutionPriority

E2.1.82 ExternalInvasiveDebugEnabled

E2.1.83 ExternalNoninvasiveDebugEnabled

E2.1.84 ExternalSecureInvasiveDebugEnabled

E2.1.85 ExternalSecureNoninvasiveDebugEnabled

E2.1.86 ExternalSecureSelfHostedDebugEnabled

E2.1.87 FPAbs

E2.1.88 FPAdd

E2.1.89 FPB_BreakpointMatch

E2.1.90 FPB_CheckBreakPoint

E2.1.91 FPB_CheckMatchAddress

E2.1.92 FPCompare

E2.1.93 FPDefaultNaN

E2.1.94 FPDiv

E2.1.95 FPDoubleToHalf

E2.1.96 FPDoubleToSingle

E2.1.97 FPExc

E2.1.98 FPHalfToDouble

E2.1.99 FPHalfToSingle

E2.1.100 FPInfinity

E2.1.101 FPMax

E2.1.102 FPMaxNormal

E2.1.103 FPMaxNum

E2.1.104 FPMin

E2.1.105 FPMinNum

E2.1.106 FPMul

E2.1.107 FPMulAdd

E2.1.108 FPNeg

E2.1.109 FPProcessException

E2.1.110 FPProcessNaN

E2.1.111 FPProcessNaNs

E2.1.112 FPProcessNaNs3

E2.1.113 FPRound

E2.1.114 FPRoundInt

E2.1.115 FPSingleToDouble

E2.1.116 FPSingleToHalf

E2.1.117 FPSqrt

E2.1.118 FPSub

E2.1.119 FPToFixed

E2.1.120 FPToFixedDirected

E2.1.121 FPType

E2.1.122 FPUnpack

E2.1.123 FPZero

E2.1.124 FaultNumbers

E2.1.125 FetchInstr

E2.1.126 FindPriv

E2.1.127 FixedToFP

E2.1.128 FunctionReturn

E2.1.129 GenerateCoprocessorException

E2.1.130 GenerateDebugEventResponse

E2.1.131 GenerateIntegerZeroDivide

E2.1.132 HaltingDebugAllowed

E2.1.133 HandleException

E2.1.134 HaveDSPExt

E2.1.135 HaveDWT

E2.1.136 HaveDebugMonitor

E2.1.137 HaveFPB

E2.1.138 HaveFPExt

E2.1.139 HaveHaltingDebug

E2.1.140 HaveITM

E2.1.141 HaveMainExt

E2.1.142 HaveSPFPOnly

E2.1.143 HaveSecurityExt

E2.1.144 HaveSysTick

E2.1.145 HighestPri

E2.1.146 Hint_Debug

E2.1.147 Hint_PreloadData

E2.1.148 Hint_PreloadDataForWrite

E2.1.149 Hint_PreloadInstr

E2.1.150 Hint_Yield

E2.1.151 IDAUCheck

E2.1.152 ITAdvance

E2.1.153 ITSTATE

E2.1.154 ITSTATEType

E2.1.155 InITBlock

E2.1.156 InstructionAdvance

E2.1.157 InstructionSynchronizationBarrier

E2.1.158 Int

E2.1.159 IntegerZeroDivideTrappingEnabled

E2.1.160 IsAccessible

E2.1.161 IsActiveForState

E2.1.162 IsAligned

E2.1.163 IsCPEnabled

E2.1.164 IsCPInstruction

E2.1.165 IsDWTConfigUnpredictable

E2.1.166 IsDWTEnabled

E2.1.167 IsExceptionTargetConfigurable

E2.1.168 IsExclusiveGlobal

E2.1.169 IsExclusiveLocal

E2.1.170 IsIrqValid

E2.1.171 IsReqExcPriNeg

E2.1.172 IsSecure

E2.1.173 LR

E2.1.174 LSL

E2.1.175 LSL_C

E2.1.176 LSR

E2.1.177 LSR_C

E2.1.178 LastInITBlock

E2.1.179 LoadWritePC

E2.1.180 Lockup

E2.1.181 LookUpRName

E2.1.182 LookUpSP

E2.1.183 LookUpSPLim

E2.1.184 LookUpSP_with_security_mode

E2.1.185 MAIRDecode

E2.1.186 MPUCheck

E2.1.187 MarkExclusiveGlobal

E2.1.188 MarkExclusiveLocal

E2.1.189 MaxExceptionNum

E2.1.190 MemA

E2.1.191 MemA_with_priv

E2.1.192 MemA_with_priv_security

E2.1.193 MemI

E2.1.194 MemO

E2.1.195 MemType

E2.1.196 MemU

E2.1.197 MemU_unpriv

E2.1.198 MemU_with_priv

E2.1.199 MemoryAttributes

E2.1.200 MergeExcInfo

E2.1.201 NextInstrAddr

E2.1.202 NextInstrITState

E2.1.203 NoninvasiveDebugAllowed

E2.1.204 PC

E2.1.205 PEMode

E2.1.206 PendReturnOperation

E2.1.207 PendingExceptionDetails

E2.1.208 Permissions

E2.1.209 PopStack

E2.1.210 PreserveFPState

E2.1.211 ProcessorID

E2.1.212 PushCalleeStack

E2.1.213 PushStack

E2.1.214 R

E2.1.215 RName

E2.1.216 ROR

E2.1.217 ROR_C

E2.1.218 RRX

E2.1.219 RRX_C

E2.1.220 RSPCheck

E2.1.221 RaiseAsyncBusFault

E2.1.222 RawExecutionPriority

E2.1.223 ResetSCSRegs

E2.1.224 RestrictedNSPri

E2.1.225 ReturnState

E2.1.226 S

E2.1.227 SAttributes

E2.1.228 SCS_UpdateStatusRegs

E2.1.229 SP

E2.1.230 SP_Main

E2.1.231 SP_Main_NonSecure

E2.1.232 SP_Main_Secure

E2.1.233 SP_Process

E2.1.234 SP_Process_NonSecure

E2.1.235 SP_Process_Secure

E2.1.236 SRType

E2.1.237 Sat

E2.1.238 SatQ

E2.1.239 SecureDebugMonitorAllowed

E2.1.240 SecureHaltingDebugAllowed

E2.1.241 SecureNoninvasiveDebugAllowed

E2.1.242 SecurityCheck

E2.1.243 SecurityState

E2.1.244 SendEvent

E2.1.245 SerializeVFP

E2.1.246 SetActive

E2.1.247 SetDWTDebugEvent

E2.1.248 SetEventRegister

E2.1.249 SetExclusiveMonitors

E2.1.250 SetITSTATEAndCommit

E2.1.251 SetMonStep

E2.1.252 SetPending

E2.1.253 SetThisInstrDetails

E2.1.254 Shift

E2.1.255 Shift_C

E2.1.256 SignedSat

E2.1.257 SignedSatQ

E2.1.258 SleepOnExit

E2.1.259 Stack

E2.1.260 StandardFPSCRValue

E2.1.261 SteppingDebug

E2.1.262 T32ExpandImm

E2.1.263 T32ExpandImm_C

E2.1.264 TTResp

E2.1.265 TailChain

E2.1.266 TakePreserveFPException

E2.1.267 TakeReset

E2.1.268 ThisInstr

E2.1.269 ThisInstrAddr

E2.1.270 ThisInstrITState

E2.1.271 ThisInstrLength

E2.1.272 TopLevel

E2.1.273 UnsignedSat

E2.1.274 UnsignedSatQ

E2.1.275 UpdateFPCCR

E2.1.276 UpdateSecureDebugEnable

E2.1.277 VFPExcBarrier

E2.1.278 VFPExpandImm

E2.1.279 VFPNegMul

E2.1.280 VFPSmallRegisterBank

E2.1.281 ValidateAddress

E2.1.282 ValidateExceptionReturn

E2.1.283 Vector

E2.1.284 WaitForEvent

E2.1.285 WaitForInterrupt

E2.1.286 _D

E2.1.287 _ITStateChanged

E2.1.288 _Mem

E2.1.289 _NextInstrAddr

E2.1.290 _NextInstrITState

E2.1.291 _PCChanged

E2.1.292 _PendingReturnOperation

E2.1.293 _R

E2.1.294 _SP

E2.1.295 common

Part F: Debug Packet Protocols

F1: ITM and DWT Packet Protocol Specification

F1.1 About the ITM and DWT packets

F1.1.1 Uses of ITM and DWT packets

F1.1.2 ITM and DWT protocol packet headers

F1.1.3 Packet transmission by the trace sink

F1.2 Alphabetical list of DWT and ITM packets

F1.2.1 Data Trace Data Address packet

F1.2.2 Data Trace Data Value packet

F1.2.3 Data Trace Match packet

F1.2.4 Data Trace PC Value packet

F1.2.5 Event Counter packet

F1.2.6 Exception Trace packet

F1.2.7 Extension packet

F1.2.8 Global Timestamp 1 packet

F1.2.9 Global Timestamp 2 packet

F1.2.10 Instrumentation packet

F1.2.11 Local Timestamp 1 packet

F1.2.12 Local Timestamp 2 packet

F1.2.13 Overflow packet

F1.2.14 Periodic PC Sample packet

F1.2.15 Synchronization packet

Glossary

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc