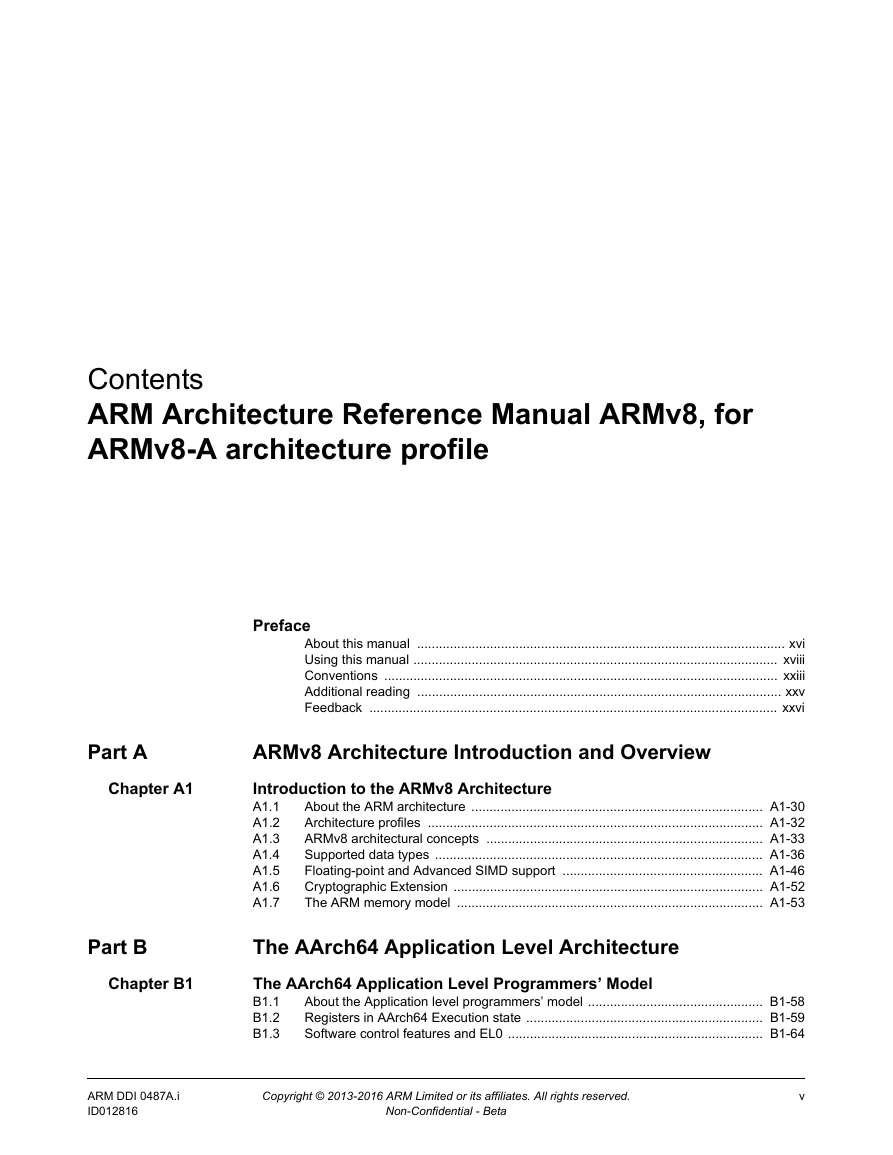

ARM Architecture Reference Manual ARMv8, for ARMv8-A architecture profile

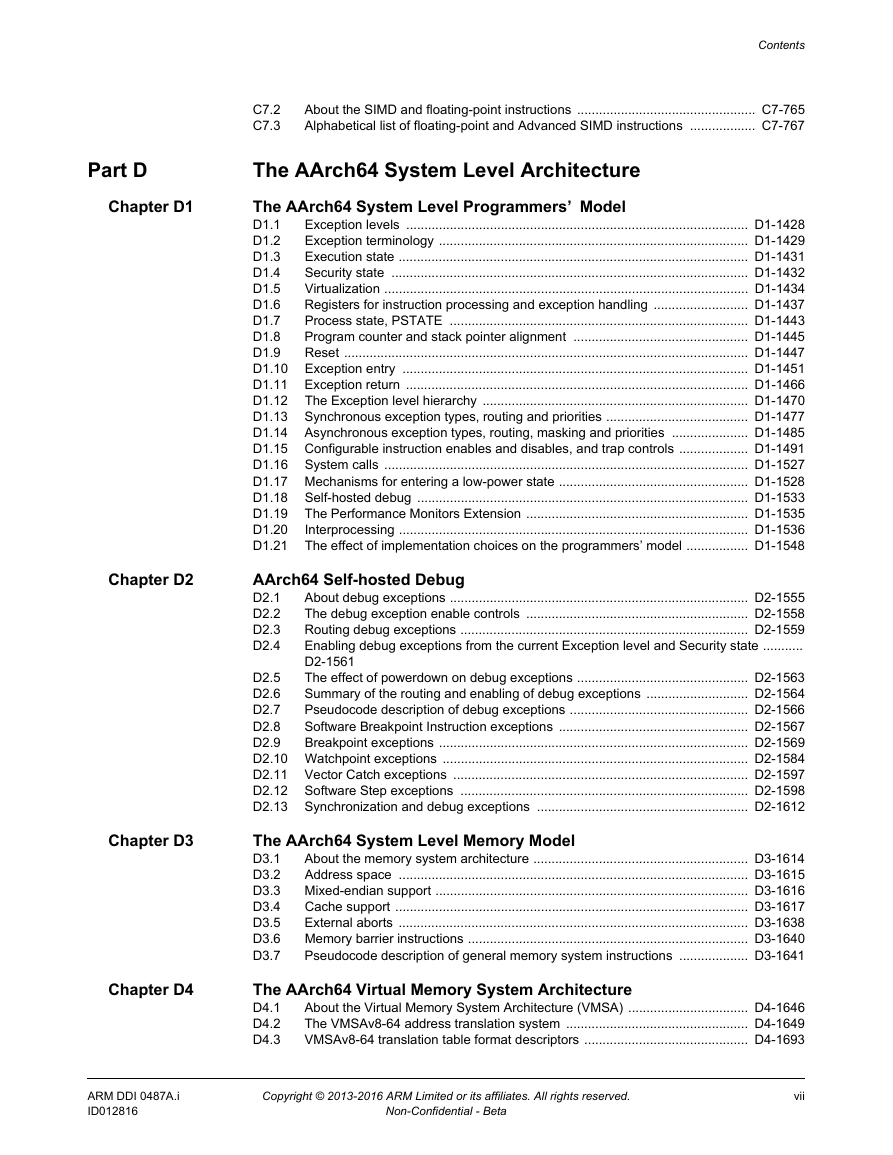

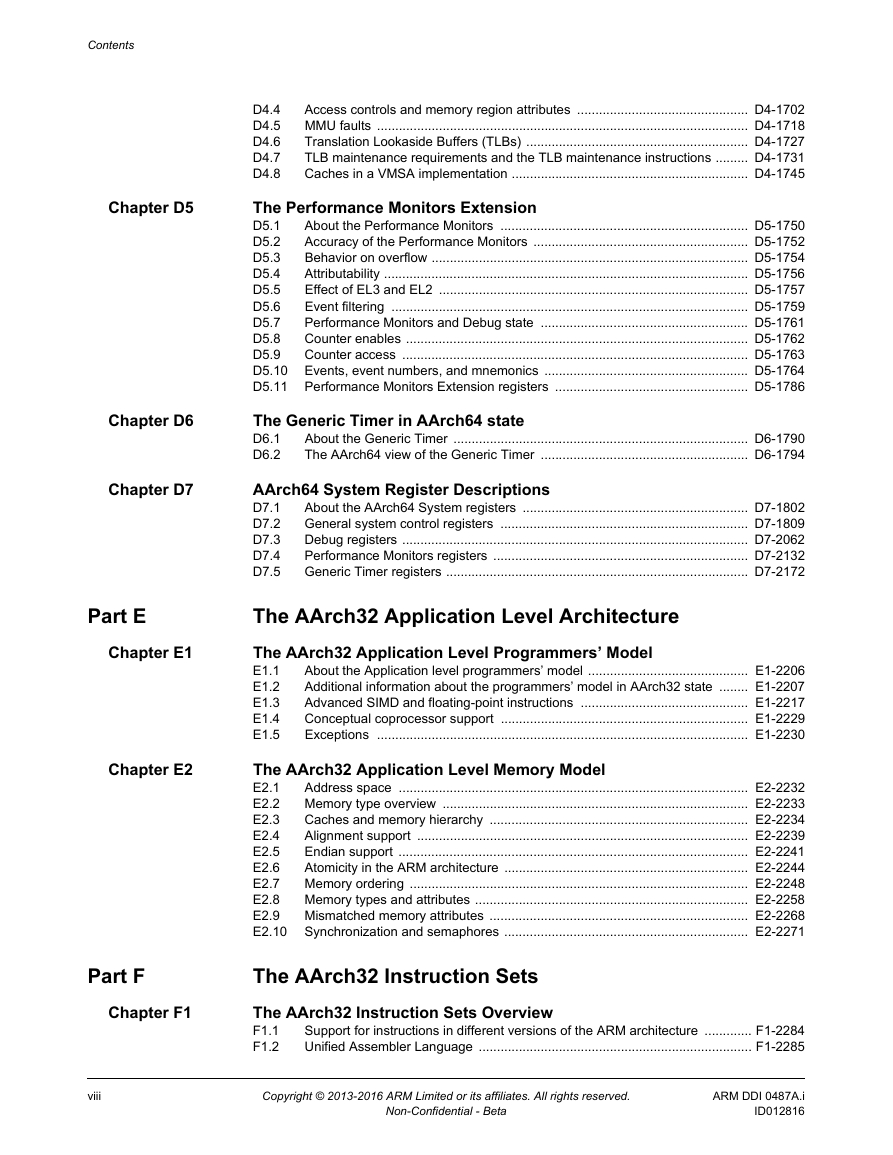

Contents

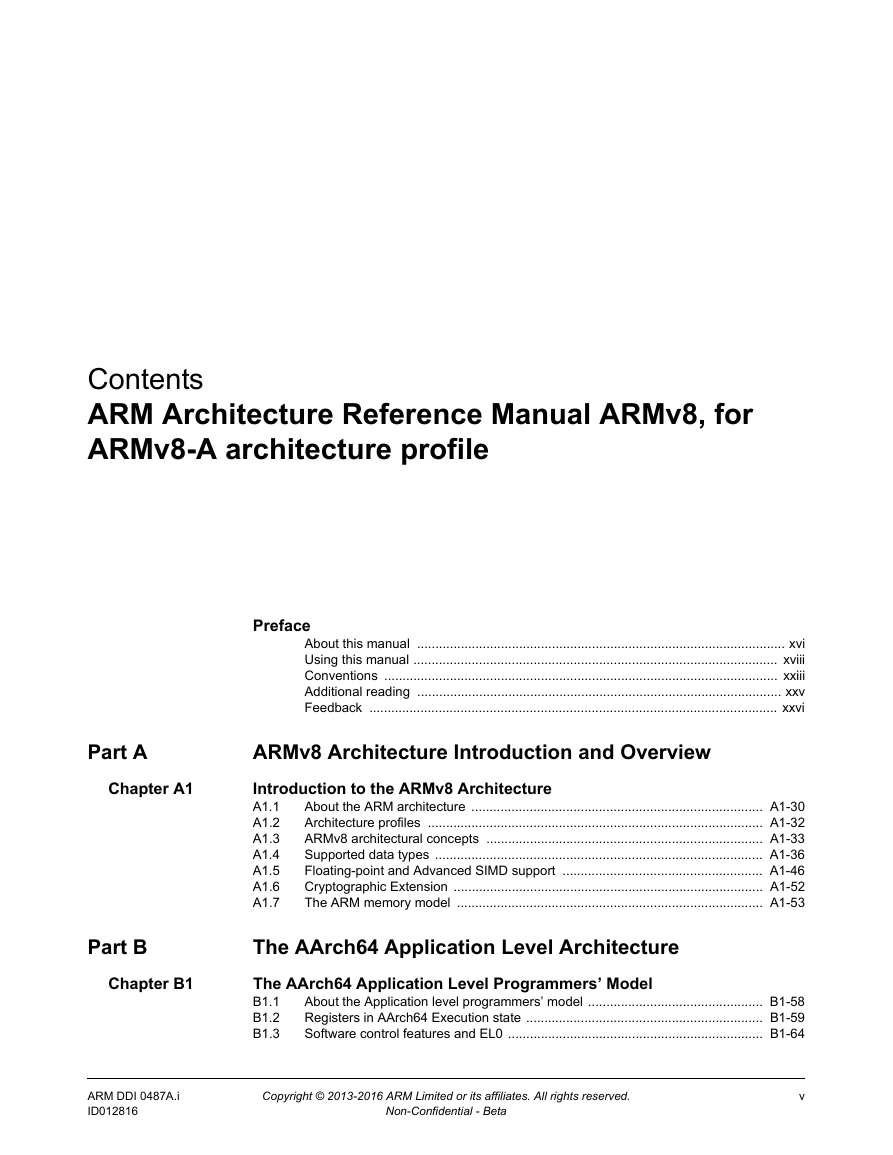

Preface

About this manual

Using this manual

Part A, Introduction and Architecture Overview

Part B, The AArch64 Application Level Architecture

Part C, The A64 Instruction Set

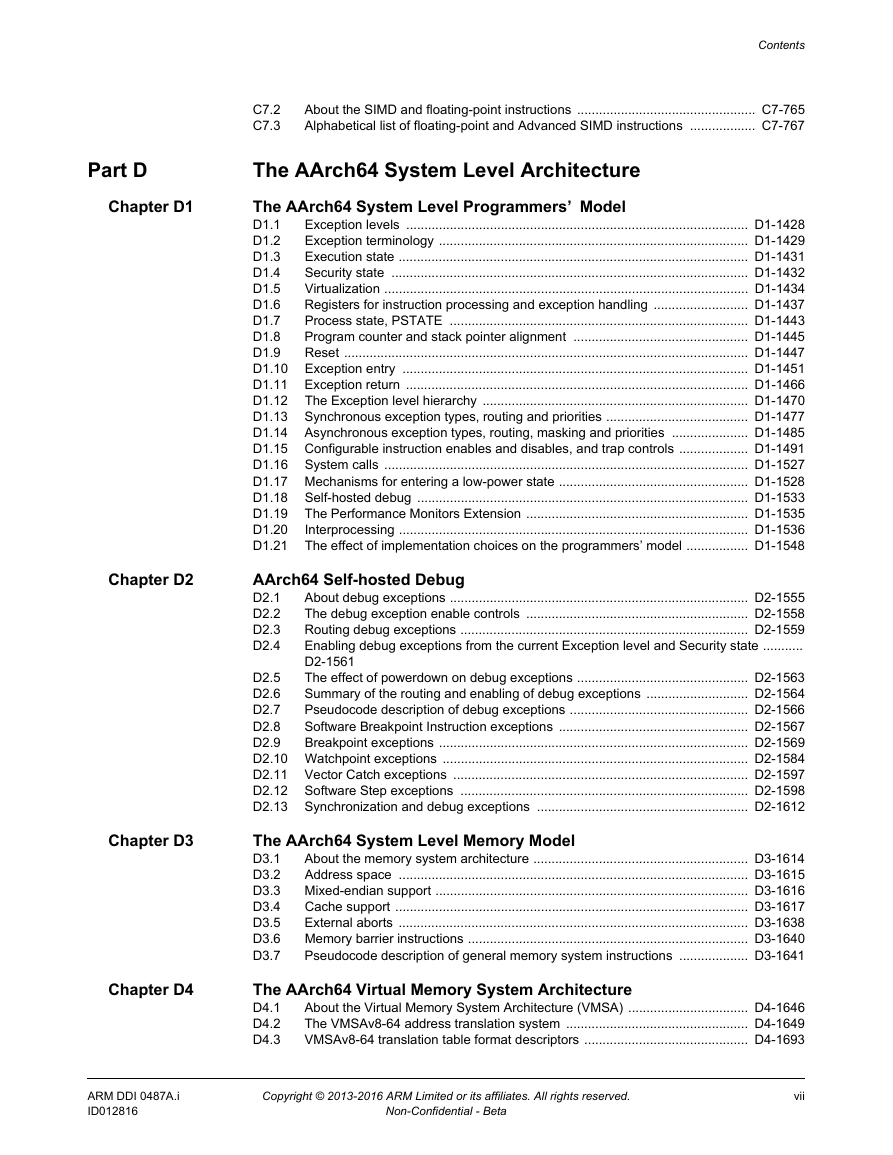

Part D, The AArch64 System Level Architecture

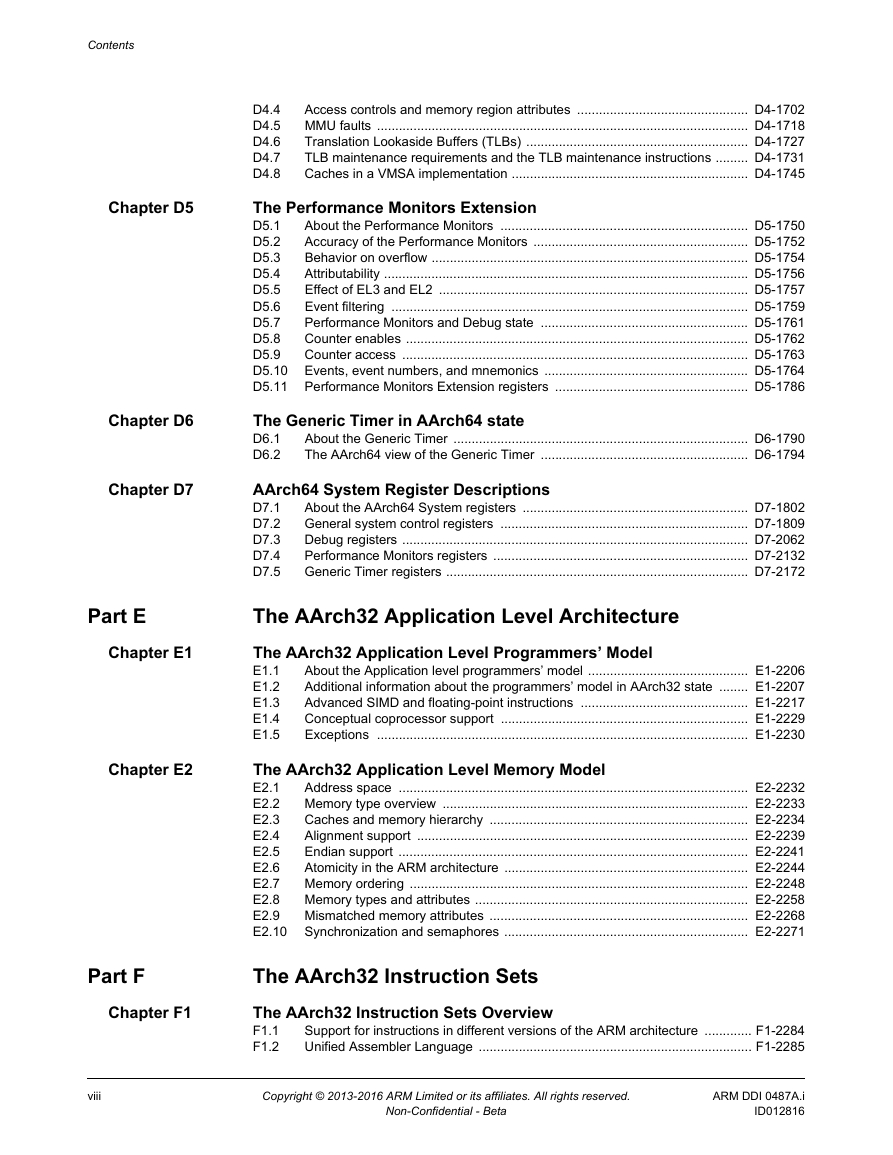

Part E, The AArch32 Application Level Architecture

Part F, The AArch32 Instruction Sets

Part G, The AArch32 System Level Architecture

Part H, External Debug

Part I, Memory-mapped Components of the ARMv8 Architecture

Part J, Architectural Pseudocode

Part K, Appendixes

Conventions

Typographic conventions

Signals

Numbers

Pseudocode descriptions

Assembler syntax descriptions

Additional reading

ARM publications

Other publications

Feedback

Feedback on this manual

Part A: ARMv8 Architecture Introduction and Overview

A1: Introduction to the ARMv8 Architecture

A1.1 About the ARM architecture

A1.2 Architecture profiles

A1.2.1 Debug architecture version

A1.3 ARMv8 architectural concepts

A1.3.1 Execution state

A1.3.2 The ARM instruction sets

A1.3.3 System registers

The ARM Generic Interrupt Controller System registers

A1.3.4 ARMv8 Debug

A1.4 Supported data types

A1.4.1 Vector formats

Vector formats in AArch64 state

Vector formats in AArch32 state

A1.4.2 Half-precision floating-point formats

A1.4.3 Single-precision floating-point format

A1.4.4 Double-precision floating-point format

A1.4.5 Fixed-point format

A1.4.6 Conversion between floating-point and fixed-point values

A1.4.7 Polynomial arithmetic over {0, 1}

Pseudocode description of polynomial multiplication

A1.5 Floating-point and Advanced SIMD support

A1.5.1 Instruction support

A1.5.2 Floating-point standards, and terminology

A1.5.3 ARM standard floating-point input and output values

A1.5.4 Flush-to-zero

A1.5.5 NaN handling and the Default NaN

A1.6 Cryptographic Extension

A1.7 The ARM memory model

Part B: The AArch64 Application Level Architecture

B1: The AArch64 Application Level Programmers’ Model

B1.1 About the Application level programmers’ model

B1.2 Registers in AArch64 Execution state

B1.2.1 Registers in AArch64 state

Pseudocode description of registers in AArch64 state

B1.2.2 Process state, PSTATE

Accessing PSTATE fields at EL0

B1.2.3 System registers

Performance Monitors support

B1.3 Software control features and EL0

B1.3.1 Exception handling

B1.3.2 Wait for Interrupt and Wait for Event

B1.3.3 The YIELD instruction

B1.3.4 Application level cache management

B1.3.5 Debug events

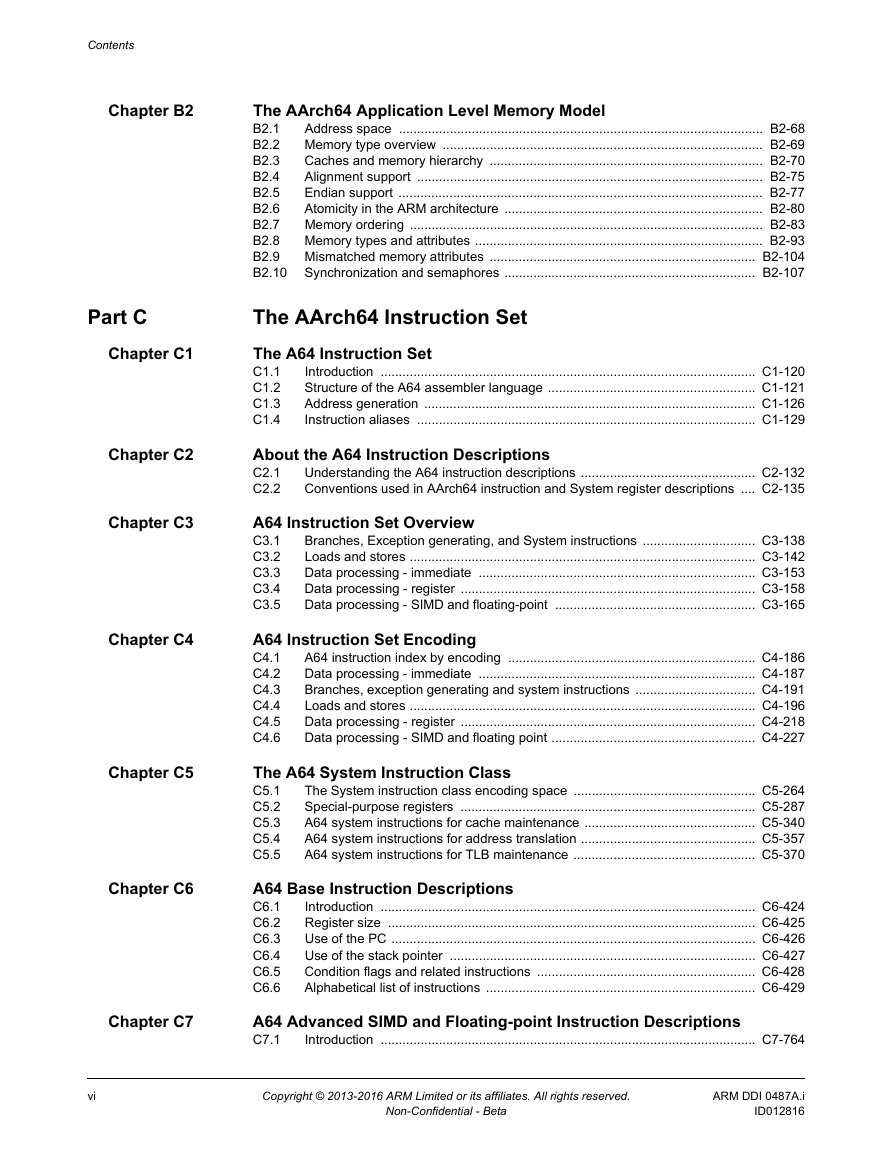

B2: The AArch64 Application Level Memory Model

B2.1 Address space

B2.2 Memory type overview

B2.3 Caches and memory hierarchy

B2.3.1 Introduction to caches

B2.3.2 Memory hierarchy

The cacheability and shareability memory attributes

B2.3.3 Application level cache instructions

B2.3.4 Implication of caches for the application programmer

Data coherency issues

Synchronization and coherency issues between data and instruction accesses

B2.3.5 Preloading caches

B2.4 Alignment support

B2.4.1 Instruction alignment

B2.4.2 Alignment of data accesses

B2.4.3 Unaligned data access restrictions

B2.5 Endian support

B2.5.1 General description of endianness in the ARM architecture

B2.5.2 Instruction endianness

B2.5.3 Data endianness

Instructions to reverse bytes in a general-purpose register or a SIMD and floating-point register

Endianness in SIMD operations

B2.6 Atomicity in the ARM architecture

B2.6.1 Requirements for single-copy atomicity

B2.6.2 Properties of single-copy atomic accesses

B2.6.3 Multi-copy atomicity

B2.6.4 Requirements for multi-copy atomicity

B2.6.5 Concurrent modification and execution of instructions

B2.7 Memory ordering

B2.7.1 Observability and completion

Completion of side-effects of accesses to Device memory

B2.7.2 Ordering requirements

Address dependencies and order

B2.7.3 Memory barriers

Instruction Synchronization Barrier (ISB)

Data Memory Barrier (DMB)

Data Synchronization Barrier (DSB)

Shareability and access limitations on the data barrier operations

Load-Acquire, Store-Release

B2.7.4 Summary of the memory ordering rules

Terms used in the summary of the memory ordering rules

B2.8 Memory types and attributes

B2.8.1 Normal memory

Shareable Normal memory

Non-shareable Normal memory

Write-Through Cacheable, Write-Back Cacheable and Non-cacheable Normal memory

Multi-register loads and stores that access Normal memory

B2.8.2 Device memory

Gathering

Reordering

Early Write Acknowledgement

Multi-register loads and stores that access Device memory

B2.8.3 Memory access restrictions

B2.9 Mismatched memory attributes

B2.10 Synchronization and semaphores

B2.10.1 Exclusive access instructions and Non-shareable memory locations

Changes to the local monitor state resulting from speculative execution

B2.10.2 Exclusive access instructions and Shareable memory locations

Operation of the global monitor

B2.10.3 Marking and the size of the marked memory block

B2.10.4 Context switch support

B2.10.5 Load-Exclusive and Store-Exclusive instruction usage restrictions

CONSTRAINED UNPREDICTABLE behavior when Load-Exclusive/Store-Exclusive access a different number of registers

B2.10.6 Use of WFE and SEV instructions by spin-locks

Part C: The AArch64 Instruction Set

C1: The A64 Instruction Set

C1.1 Introduction

C1.2 Structure of the A64 assembler language

C1.2.1 Common syntax terms

C1.2.2 Instruction Mnemonics

C1.2.3 Condition Code

C1.2.4 Register names

General-purpose register file and the stack pointer

SIMD and floating-point register file

SIMD and floating-point scalar register names

SIMD vector register names

SIMD vector element names

C1.3 Address generation

C1.3.1 Register indexed addressing

C1.3.2 PC-relative addressing

C1.3.3 Load/Store addressing modes

Address calculation

C1.4 Instruction aliases

C2: About the A64 Instruction Descriptions

C2.1 Understanding the A64 instruction descriptions

C2.1.1 The title

C2.1.2 An introduction to the instruction

C2.1.3 The instruction encoding or encodings

C2.1.4 Any alias conditions, if applicable

C2.1.5 A list of the assembler symbols for the instruction

C2.1.6 Pseudocode describing how the instruction operates

C2.1.7 Notes, if applicable

C2.2 Conventions used in AArch64 instruction and System register descriptions

C2.2.1 Fixed values in AArch64 instruction and System register descriptions

C3: A64 Instruction Set Overview

C3.1 Branches, Exception generating, and System instructions

C3.1.1 Conditional branch

C3.1.2 Unconditional branch (immediate)

C3.1.3 Unconditional branch (register)

C3.1.4 Exception generation and return

Exception generating

Exception return

Debug state

C3.1.5 System register instructions

C3.1.6 System instructions

C3.1.7 Hint instructions

C3.1.8 Barriers and CLREX instructions

C3.2 Loads and stores

C3.2.1 Load/Store register

C3.2.2 Load/Store register (unscaled offset)

C3.2.3 Load/Store Pair

C3.2.4 Load/Store Non-temporal Pair

C3.2.5 Load/Store Unprivileged

C3.2.6 Load-Exclusive/Store-Exclusive

C3.2.7 Load-Acquire/Store-Release

C3.2.8 Load/Store scalar SIMD and floating-point

Load/Store scalar SIMD and floating-point register

Load/Store scalar SIMD and floating-point register (unscaled offset)

Load/Store SIMD and Floating-point register pair

Load/Store SIMD and Floating-point Non-temporal pair

C3.2.9 Load/Store Vector

Load/Store structures

Load single structure and replicate

C3.2.10 Prefetch memory

C3.3 Data processing - immediate

C3.3.1 Arithmetic (immediate)

C3.3.2 Logical (immediate)

C3.3.3 Move (wide immediate)

C3.3.4 Move (immediate)

C3.3.5 PC-relative address calculation

C3.3.6 Bitfield move

C3.3.7 Bitfield insert and extract

C3.3.8 Extract register

C3.3.9 Shift (immediate)

C3.3.10 Sign-extend and Zero-extend

C3.4 Data processing - register

C3.4.1 Arithmetic (shifted register)

C3.4.2 Arithmetic (extended register)

C3.4.3 Arithmetic with carry

C3.4.4 Logical (shifted register)

C3.4.5 Move (register)

C3.4.6 Shift (register)

C3.4.7 Multiply and divide

Multiply

Divide

C3.4.8 CRC32

C3.4.9 Bit operation

C3.4.10 Conditional select

C3.4.11 Conditional comparison

C3.5 Data processing - SIMD and floating-point

C3.5.1 Common features of SIMD instructions

C3.5.2 Floating-point move (register)

C3.5.3 Floating-point move (immediate)

C3.5.4 Floating-point conversion

Convert floating-point precision

Convert between floating-point and integer or fixed-point

C3.5.5 Floating-point round to integral

C3.5.6 Floating-point multiply-add

C3.5.7 Floating-point arithmetic (one source)

C3.5.8 Floating-point arithmetic (two sources)

C3.5.9 Floating-point minimum and maximum

C3.5.10 Floating-point comparison

C3.5.11 Floating-point conditional select

C3.5.12 SIMD move

C3.5.13 SIMD arithmetic

C3.5.14 SIMD compare

C3.5.15 SIMD widening and narrowing arithmetic

C3.5.16 SIMD unary arithmetic

C3.5.17 SIMD by element arithmetic

C3.5.18 SIMD permute

C3.5.19 SIMD immediate

C3.5.20 SIMD shift (immediate)

C3.5.21 SIMD floating-point and integer conversion

C3.5.22 SIMD reduce (across vector lanes)

C3.5.23 SIMD pairwise arithmetic

C3.5.24 SIMD table lookup

C3.5.25 The Cryptographic Extensions

C4: A64 Instruction Set Encoding

C4.1 A64 instruction index by encoding

C4.2 Data processing - immediate

C4.2.1 Add/subtract (immediate)

C4.2.2 Bitfield

C4.2.3 Extract

C4.2.4 Logical (immediate)

C4.2.5 Move wide (immediate)

C4.2.6 PC-rel. addressing

C4.3 Branches, exception generating and system instructions

C4.3.1 Compare & branch (immediate)

C4.3.2 Conditional branch (immediate)

C4.3.3 Exception generation

C4.3.4 System

C4.3.5 Test & branch (immediate)

C4.3.6 Unconditional branch (immediate)

C4.3.7 Unconditional branch (register)

C4.4 Loads and stores

C4.4.1 Advanced SIMD load/store multiple structures

C4.4.2 Advanced SIMD load/store multiple structures (post-indexed)

C4.4.3 Advanced SIMD load/store single structure

C4.4.4 Advanced SIMD load/store single structure (post-indexed)

C4.4.5 Load register (literal)

C4.4.6 Load/store exclusive

C4.4.7 Load/store no-allocate pair (offset)

C4.4.8 Load/store register (immediate post-indexed)

C4.4.9 Load/store register (immediate pre-indexed)

C4.4.10 Load/store register (register offset)

C4.4.11 Load/store register (unprivileged)

C4.4.12 Load/store register (unscaled immediate)

C4.4.13 Load/store register (unsigned immediate)

C4.4.14 Load/store register pair (offset)

C4.4.15 Load/store register pair (post-indexed)

C4.4.16 Load/store register pair (pre-indexed)

C4.5 Data processing - register

C4.5.1 Add/subtract (extended register)

C4.5.2 Add/subtract (shifted register)

C4.5.3 Add/subtract (with carry)

C4.5.4 Conditional compare (immediate)

C4.5.5 Conditional compare (register)

C4.5.6 Conditional select

C4.5.7 Data-processing (1 source)

C4.5.8 Data-processing (2 source)

C4.5.9 Data-processing (3 source)

C4.5.10 Logical (shifted register)

C4.6 Data processing - SIMD and floating point

C4.6.1 Advanced SIMD across lanes

C4.6.2 Advanced SIMD copy

C4.6.3 Advanced SIMD extract

C4.6.4 Advanced SIMD modified immediate

C4.6.5 Advanced SIMD permute

C4.6.6 Advanced SIMD scalar copy

C4.6.7 Advanced SIMD scalar pairwise

C4.6.8 Advanced SIMD scalar shift by immediate

C4.6.9 Advanced SIMD scalar three different

C4.6.10 Advanced SIMD scalar three same

C4.6.11 Advanced SIMD scalar two-register miscellaneous

C4.6.12 Advanced SIMD scalar x indexed element

C4.6.13 Advanced SIMD shift by immediate

C4.6.14 Advanced SIMD table lookup

C4.6.15 Advanced SIMD three different

C4.6.16 Advanced SIMD three same

C4.6.17 Advanced SIMD two-register miscellaneous

C4.6.18 Advanced SIMD vector x indexed element

C4.6.19 Cryptographic AES

C4.6.20 Cryptographic three-register SHA

C4.6.21 Cryptographic two-register SHA

C4.6.22 Floating-point compare

C4.6.23 Floating-point conditional compare

C4.6.24 Floating-point conditional select

C4.6.25 Floating-point data-processing (1 source)

C4.6.26 Floating-point data-processing (2 source)

C4.6.27 Floating-point data-processing (3 source)

C4.6.28 Floating-point immediate

C4.6.29 Conversion between floating-point and fixed-point

C4.6.30 Conversion between floating-point and integer

C5: The A64 System Instruction Class

C5.1 The System instruction class encoding space

C5.1.1 Principles of the System instruction class encoding

System register width

C5.1.2 System instruction class encoding overview

UNDEFINED behaviors

C5.1.3 op0==0b00, architectural hints, barriers and CLREX, and PSTATE access

Architectural hint instructions

Barriers and CLREX

Instructions for accessing the PSTATE fields

C5.1.4 op0==0b01, cache maintenance, TLB maintenance, and address translation instructions

Cache maintenance instructions, and data cache zero

Address translation instructions

TLB maintenance instructions

Reserved encoding space for IMPLEMENTATION DEFINED instructions

C5.1.5 op0==0b10, Moves to and from debug and trace System registers

Instructions for accessing debug System registers

C5.1.6 op0==0b11, Moves to and from non-debug System registers and Special-purpose registers

Instructions for accessing non-debug System registers

Instructions for accessing Special-purpose registers

Reserved encodings for IMPLEMENTATION DEFINED registers

C5.2 Special-purpose registers

C5.2.1 CurrentEL, Current Exception Level

Field descriptions

Accessing the CurrentEL:

C5.2.2 DAIF, Interrupt Mask Bits

Field descriptions

Accessing the DAIF:

C5.2.3 DLR_EL0, Debug Link Register

Field descriptions

Accessing the DLR_EL0:

C5.2.4 DSPSR_EL0, Debug Saved Program Status Register

Field descriptions

Accessing the DSPSR_EL0:

C5.2.5 ELR_EL1, Exception Link Register (EL1)

Field descriptions

Accessing the ELR_EL1:

C5.2.6 ELR_EL2, Exception Link Register (EL2)

Field descriptions

Accessing the ELR_EL2:

C5.2.7 ELR_EL3, Exception Link Register (EL3)

Field descriptions

Accessing the ELR_EL3:

C5.2.8 FPCR, Floating-point Control Register

Field descriptions

Accessing the FPCR:

C5.2.9 FPSR, Floating-point Status Register

Field descriptions

Accessing the FPSR:

C5.2.10 NZCV, Condition Flags

Field descriptions

Accessing the NZCV:

C5.2.11 SP_EL0, Stack Pointer (EL0)

Field descriptions

Accessing the SP_EL0:

C5.2.12 SP_EL1, Stack Pointer (EL1)

Field descriptions

Accessing the SP_EL1:

C5.2.13 SP_EL2, Stack Pointer (EL2)

Field descriptions

Accessing the SP_EL2:

C5.2.14 SP_EL3, Stack Pointer (EL3)

Field descriptions

C5.2.15 SPSel, Stack Pointer Select

Field descriptions

Accessing the SPSel:

C5.2.16 SPSR_abt, Saved Program Status Register (Abort mode)

Field descriptions

Accessing the SPSR_abt:

C5.2.17 SPSR_EL1, Saved Program Status Register (EL1)

Field descriptions

Accessing the SPSR_EL1:

C5.2.18 SPSR_EL2, Saved Program Status Register (EL2)

Field descriptions

Accessing the SPSR_EL2:

C5.2.19 SPSR_EL3, Saved Program Status Register (EL3)

Field descriptions

Accessing the SPSR_EL3:

C5.2.20 SPSR_fiq, Saved Program Status Register (FIQ mode)

Field descriptions

Accessing the SPSR_fiq:

C5.2.21 SPSR_irq, Saved Program Status Register (IRQ mode)

Field descriptions

Accessing the SPSR_irq:

C5.2.22 SPSR_und, Saved Program Status Register (Undefined mode)

Field descriptions

Accessing the SPSR_und:

C5.3 A64 system instructions for cache maintenance

C5.3.1 DC CISW, Data or unified Cache line Clean and Invalidate by Set/Way

Field descriptions

Performing the DC CISW operation:

C5.3.2 DC CIVAC, Data or unified Cache line Clean and Invalidate by VA to PoC

Field descriptions

Performing the DC CIVAC operation:

C5.3.3 DC CSW, Data or unified Cache line Clean by Set/Way

Field descriptions

Performing the DC CSW operation:

C5.3.4 DC CVAC, Data or unified Cache line Clean by VA to PoC

Field descriptions

Performing the DC CVAC operation:

C5.3.5 DC CVAU, Data or unified Cache line Clean by VA to PoU

Field descriptions

Performing the DC CVAU operation:

C5.3.6 DC ISW, Data or unified Cache line Invalidate by Set/Way

Field descriptions

Performing the DC ISW operation:

C5.3.7 DC IVAC, Data or unified Cache line Invalidate by VA to PoC

Field descriptions

Performing the DC IVAC operation:

C5.3.8 DC ZVA, Data Cache Zero by VA

Field descriptions

Performing the DC ZVA operation:

C5.3.9 IC IALLU, Instruction Cache Invalidate All to PoU

Field descriptions

Performing the IC IALLU operation:

C5.3.10 IC IALLUIS, Instruction Cache Invalidate All to PoU, Inner Shareable

Field descriptions

Performing the IC IALLUIS operation:

C5.3.11 IC IVAU, Instruction Cache line Invalidate by VA to PoU

Field descriptions

Performing the IC IVAU operation:

C5.4 A64 system instructions for address translation

C5.4.1 AT S12E0R, Address Translate Stages 1 and 2 EL0 Read

Field descriptions

Performing the AT S12E0R operation:

C5.4.2 AT S12E0W, Address Translate Stages 1 and 2 EL0 Write

Field descriptions

Performing the AT S12E0W operation:

C5.4.3 AT S12E1R, Address Translate Stages 1 and 2 EL1 Read

Field descriptions

Performing the AT S12E1R operation:

C5.4.4 AT S12E1W, Address Translate Stages 1 and 2 EL1 Write

Field descriptions

Performing the AT S12E1W operation:

C5.4.5 AT S1E0R, Address Translate Stage 1 EL0 Read

Field descriptions

Performing the AT S1E0R operation:

C5.4.6 AT S1E0W, Address Translate Stage 1 EL0 Write

Field descriptions

Performing the AT S1E0W operation:

C5.4.7 AT S1E1R, Address Translate Stage 1 EL1 Read

Field descriptions

Performing the AT S1E1R operation:

C5.4.8 AT S1E1W, Address Translate Stage 1 EL1 Write

Field descriptions

Performing the AT S1E1W operation:

C5.4.9 AT S1E2R, Address Translate Stage 1 EL2 Read

Field descriptions

Performing the AT S1E2R operation:

C5.4.10 AT S1E2W, Address Translate Stage 1 EL2 Write

Field descriptions

Performing the AT S1E2W operation:

C5.4.11 AT S1E3R, Address Translate Stage 1 EL3 Read

Field descriptions

Performing the AT S1E3R operation:

C5.4.12 AT S1E3W, Address Translate Stage 1 EL3 Write

Field descriptions

Performing the AT S1E3W operation:

C5.5 A64 system instructions for TLB maintenance

C5.5.1 TLBI ALLE1, TLB Invalidate All, EL1

Field descriptions

Performing the TLBI ALLE1 operation:

C5.5.2 TLBI ALLE1IS, TLB Invalidate All, EL1, Inner Shareable

Field descriptions

Performing the TLBI ALLE1IS operation:

C5.5.3 TLBI ALLE2, TLB Invalidate All, EL2

Field descriptions

Performing the TLBI ALLE2 operation:

C5.5.4 TLBI ALLE2IS, TLB Invalidate All, EL2, Inner Shareable

Field descriptions

Performing the TLBI ALLE2IS operation:

C5.5.5 TLBI ALLE3, TLB Invalidate All, EL3

Field descriptions

Performing the TLBI ALLE3 operation:

C5.5.6 TLBI ALLE3IS, TLB Invalidate All, EL3, Inner Shareable

Field descriptions

Performing the TLBI ALLE3IS operation:

C5.5.7 TLBI ASIDE1, TLB Invalidate by ASID, EL1

Field descriptions

Performing the TLBI ASIDE1 operation:

C5.5.8 TLBI ASIDE1IS, TLB Invalidate by ASID, EL1, Inner Shareable

Field descriptions

Performing the TLBI ASIDE1IS operation:

C5.5.9 TLBI IPAS2E1, TLB Invalidate by Intermediate Physical Address, Stage 2, EL1

Field descriptions

Performing the TLBI IPAS2E1 operation:

C5.5.10 TLBI IPAS2E1IS, TLB Invalidate by Intermediate Physical Address, Stage 2, EL1, Inner Shareable

Field descriptions

Performing the TLBI IPAS2E1IS operation:

C5.5.11 TLBI IPAS2LE1, TLB Invalidate by Intermediate Physical Address, Stage 2, Last level, EL1

Field descriptions

Performing the TLBI IPAS2LE1 operation:

C5.5.12 TLBI IPAS2LE1IS, TLB Invalidate by Intermediate Physical Address, Stage 2, Last level, EL1, Inner Shareable

Field descriptions

Performing the TLBI IPAS2LE1IS operation:

C5.5.13 TLBI VAAE1, TLB Invalidate by VA, All ASID, EL1

Field descriptions

Performing the TLBI VAAE1 operation:

C5.5.14 TLBI VAAE1IS, TLB Invalidate by VA, All ASID, EL1, Inner Shareable

Field descriptions

Performing the TLBI VAAE1IS operation:

C5.5.15 TLBI VAALE1, TLB Invalidate by VA, All ASID, Last level, EL1

Field descriptions

Performing the TLBI VAALE1 operation:

C5.5.16 TLBI VAALE1IS, TLB Invalidate by VA, All ASID, EL1, Inner Shareable

Field descriptions

Performing the TLBI VAALE1IS operation:

C5.5.17 TLBI VAE1, TLB Invalidate by VA, EL1

Field descriptions

Performing the TLBI VAE1 operation:

C5.5.18 TLBI VAE1IS, TLB Invalidate by VA, EL1, Inner Shareable

Field descriptions

Performing the TLBI VAE1IS operation:

C5.5.19 TLBI VAE2, TLB Invalidate by VA, EL2

Field descriptions

Performing the TLBI VAE2 operation:

C5.5.20 TLBI VAE2IS, TLB Invalidate by VA, EL2, Inner Shareable

Field descriptions

Performing the TLBI VAE2IS operation:

C5.5.21 TLBI VAE3, TLB Invalidate by VA, EL3

Field descriptions

Performing the TLBI VAE3 operation:

C5.5.22 TLBI VAE3IS, TLB Invalidate by VA, EL3, Inner Shareable

Field descriptions

Performing the TLBI VAE3IS operation:

C5.5.23 TLBI VALE1, TLB Invalidate by VA, Last level, EL1

Field descriptions

Performing the TLBI VALE1 operation:

C5.5.24 TLBI VALE1IS, TLB Invalidate by VA, Last level, EL1, Inner Shareable

Field descriptions

Performing the TLBI VALE1IS operation:

C5.5.25 TLBI VALE2, TLB Invalidate by VA, Last level, EL2

Field descriptions

Performing the TLBI VALE2 operation:

C5.5.26 TLBI VALE2IS, TLB Invalidate by VA, Last level, EL2, Inner Shareable

Field descriptions

Performing the TLBI VALE2IS operation:

C5.5.27 TLBI VALE3, TLB Invalidate by VA, Last level, EL3

Field descriptions

Performing the TLBI VALE3 operation:

C5.5.28 TLBI VALE3IS, TLB Invalidate by VA, Last level, EL3, Inner Shareable

Field descriptions

Performing the TLBI VALE3IS operation:

C5.5.29 TLBI VMALLE1, TLB Invalidate by VMID, All at stage 1, EL1

Field descriptions

Performing the TLBI VMALLE1 operation:

C5.5.30 TLBI VMALLE1IS, TLB Invalidate by VMID, All at stage 1, EL1, Inner Shareable

Field descriptions

Performing the TLBI VMALLE1IS operation:

C5.5.31 TLBI VMALLS12E1, TLB Invalidate by VMID, All at Stage 1 and 2, EL1

Field descriptions

Performing the TLBI VMALLS12E1 operation:

C5.5.32 TLBI VMALLS12E1IS, TLB Invalidate by VMID, All at Stage 1 and 2, EL1, Inner Shareable

Field descriptions

Performing the TLBI VMALLS12E1IS operation:

C6: A64 Base Instruction Descriptions

C6.1 Introduction

C6.2 Register size

C6.3 Use of the PC

C6.4 Use of the stack pointer

C6.5 Condition flags and related instructions

C6.6 Alphabetical list of instructions

C6.6.1 ADC

Assembler symbols

Operation

C6.6.2 ADCS

Assembler symbols

Operation

C6.6.3 ADD (extended register)

Assembler symbols

Operation

C6.6.4 ADD (immediate)

Alias conditions

Assembler symbols

Operation

C6.6.5 ADD (shifted register)

Assembler symbols

Operation

C6.6.6 ADDS (extended register)

Alias conditions

Assembler symbols

Operation

C6.6.7 ADDS (immediate)

Alias conditions

Assembler symbols

Operation

C6.6.8 ADDS (shifted register)

Alias conditions

Assembler symbols

Operation

C6.6.9 ADR

Assembler symbols

Operation

C6.6.10 ADRP

Assembler symbols

Operation

C6.6.11 AND (immediate)

Assembler symbols

Operation

C6.6.12 AND (shifted register)

Assembler symbols

Operation

C6.6.13 ANDS (immediate)

Alias conditions

Assembler symbols

Operation

C6.6.14 ANDS (shifted register)

Alias conditions

Assembler symbols

Operation

C6.6.15 ASR (register)

Assembler symbols

Operation

C6.6.16 ASR (immediate)

Assembler symbols

Operation

C6.6.17 ASRV

Assembler symbols

Operation

C6.6.18 AT

Assembler symbols

Operation

C6.6.19 B.cond

Assembler symbols

Operation

C6.6.20 B

Assembler symbols

Operation

C6.6.21 BFI

Assembler symbols

Operation

C6.6.22 BFM

Alias conditions

Assembler symbols

Operation

C6.6.23 BFXIL

Assembler symbols

Operation

C6.6.24 BIC (shifted register)

Assembler symbols

Operation

C6.6.25 BICS (shifted register)

Assembler symbols

Operation

C6.6.26 BL

Assembler symbols

Operation

C6.6.27 BLR

Assembler symbols

Operation

C6.6.28 BR

Assembler symbols

Operation

C6.6.29 BRK

Assembler symbols

Operation

C6.6.30 CBNZ

Assembler symbols

Operation

C6.6.31 CBZ

Assembler symbols

Operation

C6.6.32 CCMN (immediate)

Assembler symbols

Operation

C6.6.33 CCMN (register)

Assembler symbols

Operation

C6.6.34 CCMP (immediate)

Assembler symbols

Operation

C6.6.35 CCMP (register)

Assembler symbols

Operation

C6.6.36 CINC

Assembler symbols

Operation

C6.6.37 CINV

Assembler symbols

Operation

C6.6.38 CLREX

Assembler symbols

Operation

C6.6.39 CLS

Assembler symbols

Operation

C6.6.40 CLZ

Assembler symbols

Operation

C6.6.41 CMN (extended register)

Assembler symbols

Operation

C6.6.42 CMN (immediate)

Assembler symbols

Operation

C6.6.43 CMN (shifted register)

Assembler symbols

Operation

C6.6.44 CMP (extended register)

Assembler symbols

Operation

C6.6.45 CMP (immediate)

Assembler symbols

Operation

C6.6.46 CMP (shifted register)

Assembler symbols

Operation

C6.6.47 CNEG

Assembler symbols

Operation

C6.6.48 CRC32B, CRC32H, CRC32W, CRC32X

Assembler symbols

Operation

C6.6.49 CRC32CB, CRC32CH, CRC32CW, CRC32CX

Assembler symbols

Operation

C6.6.50 CSEL

Assembler symbols

Operation

C6.6.51 CSET

Assembler symbols

Operation

C6.6.52 CSETM

Assembler symbols

Operation

C6.6.53 CSINC

Alias conditions

Assembler symbols

Operation

C6.6.54 CSINV

Alias conditions

Assembler symbols

Operation

C6.6.55 CSNEG

Alias conditions

Assembler symbols

Operation

C6.6.56 DC

Assembler symbols

Operation

C6.6.57 DCPS1

Assembler symbols

Operation

C6.6.58 DCPS2

Assembler symbols

Operation

C6.6.59 DCPS3

Assembler symbols

Operation

C6.6.60 DMB

Assembler symbols

Operation

C6.6.61 DRPS

Operation

C6.6.62 DSB

Assembler symbols

Operation

C6.6.63 EON (shifted register)

Assembler symbols

Operation

C6.6.64 EOR (immediate)

Assembler symbols

Operation

C6.6.65 EOR (shifted register)

Assembler symbols

Operation

C6.6.66 ERET

Operation

C6.6.67 EXTR

Alias conditions

Assembler symbols

Operation

C6.6.68 HINT

Assembler symbols

C6.6.69 HLT

Assembler symbols

Operation

C6.6.70 HVC

Assembler symbols

Operation

C6.6.71 IC

Assembler symbols

Operation

C6.6.72 ISB

Assembler symbols

Operation

C6.6.73 LDAR

Assembler symbols

Operation

C6.6.74 LDARB

Assembler symbols

Operation

C6.6.75 LDARH

Assembler symbols

Operation

C6.6.76 LDAXP

Notes for all encodings

Assembler symbols

Operation

C6.6.77 LDAXR

Assembler symbols

Operation

C6.6.78 LDAXRB

Assembler symbols

Operation

C6.6.79 LDAXRH

Assembler symbols

Operation

C6.6.80 LDNP

Assembler symbols

Shared decode for all encodings

Operation

C6.6.81 LDP

Post-index

Pre-index

Signed offset

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.82 LDPSW

Post-index

Pre-index

Signed offset

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.83 LDR (immediate)

Post-index

Pre-index

Unsigned offset

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.84 LDR (literal)

Assembler symbols

Operation

C6.6.85 LDR (register)

Assembler symbols

Shared decode for all encodings

Operation

C6.6.86 LDRB (immediate)

Post-index

Pre-index

Unsigned offset

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.87 LDRB (register)

Assembler symbols

Shared decode for all encodings

Operation

C6.6.88 LDRH (immediate)

Post-index

Pre-index

Unsigned offset

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.89 LDRH (register)

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation

C6.6.90 LDRSB (immediate)

Post-index

Pre-index

Unsigned offset

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.91 LDRSB (register)

Assembler symbols

Shared decode for all encodings

Operation

C6.6.92 LDRSH (immediate)

Post-index

Pre-index

Unsigned offset

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.93 LDRSH (register)

Assembler symbols

Shared decode for all encodings

Operation

C6.6.94 LDRSW (immediate)

Post-index

Pre-index

Unsigned offset

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.95 LDRSW (literal)

Assembler symbols

Operation

C6.6.96 LDRSW (register)

Assembler symbols

Shared decode for all encodings

Operation

C6.6.97 LDTR

Assembler symbols

Shared decode for all encodings

Operation

C6.6.98 LDTRB

Assembler symbols

Shared decode for all encodings

Operation

C6.6.99 LDTRH

Assembler symbols

Shared decode for all encodings

Operation

C6.6.100 LDTRSB

Assembler symbols

Shared decode for all encodings

Operation

C6.6.101 LDTRSH

Assembler symbols

Shared decode for all encodings

Operation

C6.6.102 LDTRSW

Assembler symbols

Shared decode for all encodings

Operation

C6.6.103 LDUR

Assembler symbols

Shared decode for all encodings

Operation

C6.6.104 LDURB

Assembler symbols

Shared decode for all encodings

Operation

C6.6.105 LDURH

Assembler symbols

Shared decode for all encodings

Operation

C6.6.106 LDURSB

Assembler symbols

Shared decode for all encodings

Operation

C6.6.107 LDURSH

Assembler symbols

Shared decode for all encodings

Operation

C6.6.108 LDURSW

Assembler symbols

Shared decode for all encodings

Operation

C6.6.109 LDXP

Notes for all encodings

Assembler symbols

Operation

C6.6.110 LDXR

Assembler symbols

Operation

C6.6.111 LDXRB

Assembler symbols

Operation

C6.6.112 LDXRH

Assembler symbols

Operation

C6.6.113 LSL (register)

Assembler symbols

Operation

C6.6.114 LSL (immediate)

Assembler symbols

Operation

C6.6.115 LSLV

Assembler symbols

Operation

C6.6.116 LSR (register)

Assembler symbols

Operation

C6.6.117 LSR (immediate)

Assembler symbols

Operation

C6.6.118 LSRV

Assembler symbols

Operation

C6.6.119 MADD

Alias conditions

Assembler symbols

Operation

C6.6.120 MNEG

Assembler symbols

Operation

C6.6.121 MOV (to/from SP)

Assembler symbols

Operation

C6.6.122 MOV (inverted wide immediate)

Assembler symbols

Operation

C6.6.123 MOV (wide immediate)

Assembler symbols

Operation

C6.6.124 MOV (bitmask immediate)

Assembler symbols

Operation

C6.6.125 MOV (register)

Assembler symbols

Operation

C6.6.126 MOVK

Assembler symbols

Operation

C6.6.127 MOVN

Alias conditions

Assembler symbols

Operation

C6.6.128 MOVZ

Alias conditions

Assembler symbols

Operation

C6.6.129 MRS

Assembler symbols

Operation

C6.6.130 MSR (immediate)

Assembler symbols

Operation

C6.6.131 MSR (register)

Assembler symbols

Operation

C6.6.132 MSUB

Alias conditions

Assembler symbols

Operation

C6.6.133 MUL

Assembler symbols

Operation

C6.6.134 MVN

Assembler symbols

Operation

C6.6.135 NEG (shifted register)

Assembler symbols

Operation

C6.6.136 NEGS

Assembler symbols

Operation

C6.6.137 NGC

Assembler symbols

Operation

C6.6.138 NGCS

Assembler symbols

Operation

C6.6.139 NOP

Operation

C6.6.140 ORN (shifted register)

Alias conditions

Assembler symbols

Operation

C6.6.141 ORR (immediate)

Alias conditions

Assembler symbols

Operation

C6.6.142 ORR (shifted register)

Alias conditions

Assembler symbols

Operation

C6.6.143 PRFM (immediate)

Assembler symbols

Shared decode for all encodings

Operation

C6.6.144 PRFM (literal)

Assembler symbols

Operation

C6.6.145 PRFM (register)

Assembler symbols

Shared decode for all encodings

Operation

C6.6.146 PRFM (unscaled offset)

Assembler symbols

Shared decode for all encodings

Operation

C6.6.147 RBIT

Assembler symbols

Operation

C6.6.148 RET

Assembler symbols

Operation

C6.6.149 REV

Assembler symbols

Operation

C6.6.150 REV16

Assembler symbols

Operation

C6.6.151 REV32

Assembler symbols

Operation

C6.6.152 REV64

Assembler symbols

Operation

C6.6.153 ROR (immediate)

Assembler symbols

Operation

C6.6.154 ROR (register)

Assembler symbols

Operation

C6.6.155 RORV

Assembler symbols

Operation

C6.6.156 SBC

Alias conditions

Assembler symbols

Operation

C6.6.157 SBCS

Alias conditions

Assembler symbols

Operation

C6.6.158 SBFIZ

Assembler symbols

Operation

C6.6.159 SBFM

Alias conditions

Assembler symbols

Operation

C6.6.160 SBFX

Assembler symbols

Operation

C6.6.161 SDIV

Assembler symbols

Operation

C6.6.162 SEV

Operation

C6.6.163 SEVL

Operation

C6.6.164 SMADDL

Alias conditions

Assembler symbols

Operation

C6.6.165 SMC

Assembler symbols

Operation

C6.6.166 SMNEGL

Assembler symbols

Operation

C6.6.167 SMSUBL

Alias conditions

Assembler symbols

Operation

C6.6.168 SMULH

Assembler symbols

Operation

C6.6.169 SMULL

Assembler symbols

Operation

C6.6.170 STLR

Assembler symbols

Operation

C6.6.171 STLRB

Assembler symbols

Operation

C6.6.172 STLRH

Assembler symbols

Operation

C6.6.173 STLXP

Notes for all encodings

Assembler symbols

Aborts and alignment

Operation

C6.6.174 STLXR

Notes for all encodings

Assembler symbols

Aborts and alignment

Operation

C6.6.175 STLXRB

Notes for all encodings

Assembler symbols

Aborts

Operation

C6.6.176 STLXRH

Notes for all encodings

Assembler symbols

Aborts and alignment

Operation

C6.6.177 STNP

Assembler symbols

Shared decode for all encodings

Operation

C6.6.178 STP

Post-index

Pre-index

Signed offset

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.179 STR (immediate)

Post-index

Pre-index

Unsigned offset

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.180 STR (register)

Assembler symbols

Shared decode for all encodings

Operation

C6.6.181 STRB (immediate)

Post-index

Pre-index

Unsigned offset

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.182 STRB (register)

Assembler symbols

Shared decode for all encodings

Operation

C6.6.183 STRH (immediate)

Post-index

Pre-index

Unsigned offset

Notes for all encodings

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C6.6.184 STRH (register)

Assembler symbols

Shared decode for all encodings

Operation

C6.6.185 STTR

Assembler symbols

Shared decode for all encodings

Operation

C6.6.186 STTRB

Assembler symbols

Shared decode for all encodings

Operation

C6.6.187 STTRH

Assembler symbols

Shared decode for all encodings

Operation

C6.6.188 STUR

Assembler symbols

Shared decode for all encodings

Operation

C6.6.189 STURB

Assembler symbols

Shared decode for all encodings

Operation

C6.6.190 STURH

Assembler symbols

Shared decode for all encodings

Operation

C6.6.191 STXP

Notes for all encodings

Assembler symbols

Aborts and alignment

Operation

C6.6.192 STXR

Notes for all encodings

Assembler symbols

Aborts and alignment

Operation

C6.6.193 STXRB

Notes for all encodings

Assembler symbols

Aborts

Operation

C6.6.194 STXRH

Assembler symbols

Aborts and alignment

Operation

C6.6.195 SUB (extended register)

Assembler symbols

Operation

C6.6.196 SUB (immediate)

Assembler symbols

Operation

C6.6.197 SUB (shifted register)

Alias conditions

Assembler symbols

Operation

C6.6.198 SUBS (extended register)

Alias conditions

Assembler symbols

Operation

C6.6.199 SUBS (immediate)

Alias conditions

Assembler symbols

Operation

C6.6.200 SUBS (shifted register)

Alias conditions

Assembler symbols

Operation

C6.6.201 SVC

Assembler symbols

Operation

C6.6.202 SXTB

Assembler symbols

Operation

C6.6.203 SXTH

Assembler symbols

Operation

C6.6.204 SXTW

Assembler symbols

Operation

C6.6.205 SYS

Alias conditions

Assembler symbols

Operation

C6.6.206 SYSL

Assembler symbols

Operation

C6.6.207 TBNZ

Assembler symbols

Operation

C6.6.208 TBZ

Assembler symbols

Operation

C6.6.209 TLBI

Assembler symbols

Operation

C6.6.210 TST (immediate)

Assembler symbols

Operation

C6.6.211 TST (shifted register)

Assembler symbols

Operation

C6.6.212 UBFIZ

Assembler symbols

Operation

C6.6.213 UBFM

Alias conditions

Assembler symbols

Operation

C6.6.214 UBFX

Assembler symbols

Operation

C6.6.215 UDIV

Assembler symbols

Operation

C6.6.216 UMADDL

Alias conditions

Assembler symbols

Operation

C6.6.217 UMNEGL

Assembler symbols

Operation

C6.6.218 UMSUBL

Alias conditions

Assembler symbols

Operation

C6.6.219 UMULH

Assembler symbols

Operation

C6.6.220 UMULL

Assembler symbols

Operation

C6.6.221 UXTB

Assembler symbols

Operation

C6.6.222 UXTH

Assembler symbols

Operation

C6.6.223 WFE

Operation

C6.6.224 WFI

Operation

C6.6.225 YIELD

Operation

C7: A64 Advanced SIMD and Floating-point Instruction Descriptions

C7.1 Introduction

C7.2 About the SIMD and floating-point instructions

C7.2.1 Register size

C7.2.2 Data types

C7.2.3 Condition flags and related instructions

C7.2.4 General capabilities

C7.3 Alphabetical list of floating-point and Advanced SIMD instructions

C7.3.1 ABS

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.2 ADD (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.3 ADDHN, ADDHN2

Assembler symbols

Operation

C7.3.4 ADDP (scalar)

Assembler symbols

Operation

C7.3.5 ADDP (vector)

Assembler symbols

Operation

C7.3.6 ADDV

Assembler symbols

Operation

C7.3.7 AESD

Assembler symbols

Operation

C7.3.8 AESE

Assembler symbols

Operation

C7.3.9 AESIMC

Assembler symbols

Operation

C7.3.10 AESMC

Assembler symbols

Operation

C7.3.11 AND (vector)

Assembler symbols

Operation

C7.3.12 BIC (vector, immediate)

Assembler symbols

Operation

C7.3.13 BIC (vector, register)

Assembler symbols

Operation

C7.3.14 BIF

Assembler symbols

Operation

C7.3.15 BIT

Assembler symbols

Operation

C7.3.16 BSL

Assembler symbols

Operation

C7.3.17 CLS (vector)

Assembler symbols

Operation

C7.3.18 CLZ (vector)

Assembler symbols

Operation

C7.3.19 CMEQ (register)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.20 CMEQ (zero)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.21 CMGE (register)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.22 CMGE (zero)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.23 CMGT (register)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.24 CMGT (zero)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.25 CMHI (register)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.26 CMHS (register)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.27 CMLE (zero)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.28 CMLT (zero)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.29 CMTST

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.30 CNT

Assembler symbols

Operation

C7.3.31 DUP (element)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.32 DUP (general)

Assembler symbols

Operation

C7.3.33 EOR (vector)

Assembler symbols

Operation

C7.3.34 EXT

Assembler symbols

Operation

C7.3.35 FABD

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.36 FABS (vector)

Assembler symbols

Operation

C7.3.37 FABS (scalar)

Assembler symbols

Operation

C7.3.38 FACGE

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.39 FACGT

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.40 FADD (vector)

Assembler symbols

Operation

C7.3.41 FADD (scalar)

Assembler symbols

Operation

C7.3.42 FADDP (scalar)

Assembler symbols

Operation

C7.3.43 FADDP (vector)

Assembler symbols

Operation

C7.3.44 FCCMP

Assembler symbols

Operation

C7.3.45 FCCMPE

Assembler symbols

Operation

C7.3.46 FCMEQ (register)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.47 FCMEQ (zero)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.48 FCMGE (register)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.49 FCMGE (zero)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.50 FCMGT (register)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.51 FCMGT (zero)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.52 FCMLE (zero)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.53 FCMLT (zero)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.54 FCMP

Assembler symbols

Operation

C7.3.55 FCMPE

Assembler symbols

Operation

C7.3.56 FCSEL

Assembler symbols

Operation

C7.3.57 FCVT

Assembler symbols

Operation

C7.3.58 FCVTAS (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.59 FCVTAS (scalar)

Assembler symbols

Operation

C7.3.60 FCVTAU (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.61 FCVTAU (scalar)

Assembler symbols

Operation

C7.3.62 FCVTL, FCVTL2

Assembler symbols

Operation

C7.3.63 FCVTMS (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.64 FCVTMS (scalar)

Assembler symbols

Operation

C7.3.65 FCVTMU (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.66 FCVTMU (scalar)

Assembler symbols

Operation

C7.3.67 FCVTN, FCVTN2

Assembler symbols

Operation

C7.3.68 FCVTNS (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.69 FCVTNS (scalar)

Assembler symbols

Operation

C7.3.70 FCVTNU (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.71 FCVTNU (scalar)

Assembler symbols

Operation

C7.3.72 FCVTPS (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.73 FCVTPS (scalar)

Assembler symbols

Operation

C7.3.74 FCVTPU (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.75 FCVTPU (scalar)

Assembler symbols

Operation

C7.3.76 FCVTXN, FCVTXN2

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.77 FCVTZS (vector, fixed-point)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.78 FCVTZS (vector, integer)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.79 FCVTZS (scalar, fixed-point)

Assembler symbols

Operation

C7.3.80 FCVTZS (scalar, integer)

Assembler symbols

Operation

C7.3.81 FCVTZU (vector, fixed-point)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.82 FCVTZU (vector, integer)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.83 FCVTZU (scalar, fixed-point)

Assembler symbols

Operation

C7.3.84 FCVTZU (scalar, integer)

Assembler symbols

Operation

C7.3.85 FDIV (vector)

Assembler symbols

Operation

C7.3.86 FDIV (scalar)

Assembler symbols

Operation

C7.3.87 FMADD

Assembler symbols

Operation

C7.3.88 FMAX (vector)

Assembler symbols

Operation

C7.3.89 FMAX (scalar)

Assembler symbols

Operation

C7.3.90 FMAXNM (vector)

Assembler symbols

Operation

C7.3.91 FMAXNM (scalar)

Assembler symbols

Operation

C7.3.92 FMAXNMP (scalar)

Assembler symbols

Operation

C7.3.93 FMAXNMP (vector)

Assembler symbols

Operation

C7.3.94 FMAXNMV

Assembler symbols

Operation

C7.3.95 FMAXP (scalar)

Assembler symbols

Operation

C7.3.96 FMAXP (vector)

Assembler symbols

Operation

C7.3.97 FMAXV

Assembler symbols

Operation

C7.3.98 FMIN (vector)

Assembler symbols

Operation

C7.3.99 FMIN (scalar)

Assembler symbols

Operation

C7.3.100 FMINNM (vector)

Assembler symbols

Operation

C7.3.101 FMINNM (scalar)

Assembler symbols

Operation

C7.3.102 FMINNMP (scalar)

Assembler symbols

Operation

C7.3.103 FMINNMP (vector)

Assembler symbols

Operation

C7.3.104 FMINNMV

Assembler symbols

Operation

C7.3.105 FMINP (scalar)

Assembler symbols

Operation

C7.3.106 FMINP (vector)

Assembler symbols

Operation

C7.3.107 FMINV

Assembler symbols

Operation

C7.3.108 FMLA (by element)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.109 FMLA (vector)

Assembler symbols

Operation

C7.3.110 FMLS (by element)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.111 FMLS (vector)

Assembler symbols

Operation

C7.3.112 FMOV (vector, immediate)

Assembler symbols

Operation

C7.3.113 FMOV (register)

Assembler symbols

Operation

C7.3.114 FMOV (general)

Assembler symbols

Operation

C7.3.115 FMOV (scalar, immediate)

Assembler symbols

Operation

C7.3.116 FMSUB

Assembler symbols

Operation

C7.3.117 FMUL (by element)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.118 FMUL (vector)

Assembler symbols

Operation

C7.3.119 FMUL (scalar)

Assembler symbols

Operation

C7.3.120 FMULX (by element)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.121 FMULX

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.122 FNEG (vector)

Assembler symbols

Operation

C7.3.123 FNEG (scalar)

Assembler symbols

Operation

C7.3.124 FNMADD

Assembler symbols

Operation

C7.3.125 FNMSUB

Assembler symbols

Operation

C7.3.126 FNMUL

Assembler symbols

Operation

C7.3.127 FRECPE

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.128 FRECPS

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.129 FRECPX

Assembler symbols

Operation

C7.3.130 FRINTA (vector)

Assembler symbols

Operation

C7.3.131 FRINTA (scalar)

Assembler symbols

Operation

C7.3.132 FRINTI (vector)

Assembler symbols

Operation

C7.3.133 FRINTI (scalar)

Assembler symbols

Operation

C7.3.134 FRINTM (vector)

Assembler symbols

Operation

C7.3.135 FRINTM (scalar)

Assembler symbols

Operation

C7.3.136 FRINTN (vector)

Assembler symbols

Operation

C7.3.137 FRINTN (scalar)

Assembler symbols

Operation

C7.3.138 FRINTP (vector)

Assembler symbols

Operation

C7.3.139 FRINTP (scalar)

Assembler symbols

Operation

C7.3.140 FRINTX (vector)

Assembler symbols

Operation

C7.3.141 FRINTX (scalar)

Assembler symbols

Operation

C7.3.142 FRINTZ (vector)

Assembler symbols

Operation

C7.3.143 FRINTZ (scalar)

Assembler symbols

Operation

C7.3.144 FRSQRTE

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.145 FRSQRTS

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.146 FSQRT (vector)

Assembler symbols

Operation

C7.3.147 FSQRT (scalar)

Assembler symbols

Operation

C7.3.148 FSUB (vector)

Assembler symbols

Operation

C7.3.149 FSUB (scalar)

Assembler symbols

Operation

C7.3.150 INS (element)

Assembler symbols

Operation

C7.3.151 INS (general)

Assembler symbols

Operation

C7.3.152 LD1 (multiple structures)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.153 LD1 (single structure)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.154 LD1R

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.155 LD2 (multiple structures)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.156 LD2 (single structure)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.157 LD2R

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.158 LD3 (multiple structures)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.159 LD3 (single structure)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.160 LD3R

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.161 LD4 (multiple structures)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.162 LD4 (single structure)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.163 LD4R

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.164 LDNP (SIMD&FP)

Assembler symbols

Shared decode for all encodings

Operation

C7.3.165 LDP (SIMD&FP)

Post-index

Pre-index

Signed offset

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.166 LDR (immediate, SIMD&FP)

Post-index

Pre-index

Unsigned offset

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.167 LDR (literal, SIMD&FP)

Assembler symbols

Operation

C7.3.168 LDR (register, SIMD&FP)

Assembler symbols

Shared decode for all encodings

Operation

C7.3.169 LDUR (SIMD&FP)

Assembler symbols

Shared decode for all encodings

Operation

C7.3.170 MLA (by element)

Assembler symbols

Operation

C7.3.171 MLA (vector)

Assembler symbols

Operation

C7.3.172 MLS (by element)

Assembler symbols

Operation

C7.3.173 MLS (vector)

Assembler symbols

Operation

C7.3.174 MOV (scalar)

Assembler symbols

Operation

C7.3.175 MOV (element)

Assembler symbols

Operation

C7.3.176 MOV (from general)

Assembler symbols

Operation

C7.3.177 MOV (vector)

Assembler symbols

Operation

C7.3.178 MOV (to general)

Assembler symbols

Operation

C7.3.179 MOVI

Assembler symbols

Operation

C7.3.180 MUL (by element)

Assembler symbols

Operation

C7.3.181 MUL (vector)

Assembler symbols

Operation

C7.3.182 MVN

Assembler symbols

Operation

C7.3.183 MVNI

Assembler symbols

Operation

C7.3.184 NEG (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.185 NOT

Assembler symbols

Operation

C7.3.186 ORN (vector)

Assembler symbols

Operation

C7.3.187 ORR (vector, immediate)

Assembler symbols

Operation

C7.3.188 ORR (vector, register)

Alias conditions

Assembler symbols

Operation

C7.3.189 PMUL

Assembler symbols

Operation

C7.3.190 PMULL, PMULL2

Assembler symbols

Operation

C7.3.191 RADDHN, RADDHN2

Assembler symbols

Operation

C7.3.192 RBIT (vector)

Assembler symbols

Operation

C7.3.193 REV16 (vector)

Assembler symbols

Operation

C7.3.194 REV32 (vector)

Assembler symbols

Operation

C7.3.195 REV64

Assembler symbols

Operation

C7.3.196 RSHRN, RSHRN2

Assembler symbols

Operation

C7.3.197 RSUBHN, RSUBHN2

Assembler symbols

Operation

C7.3.198 SABA

Assembler symbols

Operation

C7.3.199 SABAL, SABAL2

Assembler symbols

Operation

C7.3.200 SABD

Assembler symbols

Operation

C7.3.201 SABDL, SABDL2

Assembler symbols

Operation

C7.3.202 SADALP

Assembler symbols

Operation

C7.3.203 SADDL, SADDL2

Assembler symbols

Operation

C7.3.204 SADDLP

Assembler symbols

Operation

C7.3.205 SADDLV

Assembler symbols

Operation

C7.3.206 SADDW, SADDW2

Assembler symbols

Operation

C7.3.207 SCVTF (vector, fixed-point)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.208 SCVTF (vector, integer)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.209 SCVTF (scalar, fixed-point)

Assembler symbols

Operation

C7.3.210 SCVTF (scalar, integer)

Assembler symbols

Operation

C7.3.211 SHA1C

Assembler symbols

Operation

C7.3.212 SHA1H

Assembler symbols

Operation

C7.3.213 SHA1M

Assembler symbols

Operation

C7.3.214 SHA1P

Assembler symbols

Operation

C7.3.215 SHA1SU0

Assembler symbols

Operation

C7.3.216 SHA1SU1

Assembler symbols

Operation

C7.3.217 SHA256H2

Assembler symbols

Operation

C7.3.218 SHA256H

Assembler symbols

Operation

C7.3.219 SHA256SU0

Assembler symbols

Operation

C7.3.220 SHA256SU1

Assembler symbols

Operation

C7.3.221 SHADD

Assembler symbols

Operation

C7.3.222 SHL

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.223 SHLL, SHLL2

Assembler symbols

Operation

C7.3.224 SHRN, SHRN2

Assembler symbols

Operation

C7.3.225 SHSUB

Assembler symbols

Operation

C7.3.226 SLI

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.227 SMAX

Assembler symbols

Operation

C7.3.228 SMAXP

Assembler symbols

Operation

C7.3.229 SMAXV

Assembler symbols

Operation

C7.3.230 SMIN

Assembler symbols

Operation

C7.3.231 SMINP

Assembler symbols

Operation

C7.3.232 SMINV

Assembler symbols

Operation

C7.3.233 SMLAL, SMLAL2 (by element)

Assembler symbols

Operation

C7.3.234 SMLAL, SMLAL2 (vector)

Assembler symbols

Operation

C7.3.235 SMLSL, SMLSL2 (by element)

Assembler symbols

Operation

C7.3.236 SMLSL, SMLSL2 (vector)

Assembler symbols

Operation

C7.3.237 SMOV

Assembler symbols

Operation

C7.3.238 SMULL, SMULL2 (by element)

Assembler symbols

Operation

C7.3.239 SMULL, SMULL2 (vector)

Assembler symbols

Operation

C7.3.240 SQABS

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.241 SQADD

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.242 SQDMLAL, SQDMLAL2 (by element)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.243 SQDMLAL, SQDMLAL2 (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.244 SQDMLSL, SQDMLSL2 (by element)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.245 SQDMLSL, SQDMLSL2 (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.246 SQDMULH (by element)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.247 SQDMULH (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.248 SQDMULL, SQDMULL2 (by element)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.249 SQDMULL, SQDMULL2 (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.250 SQNEG

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.251 SQRDMULH (by element)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.252 SQRDMULH (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.253 SQRSHL

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.254 SQRSHRN, SQRSHRN2

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.255 SQRSHRUN, SQRSHRUN2

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.256 SQSHL (immediate)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.257 SQSHL (register)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.258 SQSHLU

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.259 SQSHRN, SQSHRN2

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.260 SQSHRUN, SQSHRUN2

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.261 SQSUB

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.262 SQXTN, SQXTN2

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.263 SQXTUN, SQXTUN2

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.264 SRHADD

Assembler symbols

Operation

C7.3.265 SRI

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.266 SRSHL

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.267 SRSHR

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.268 SRSRA

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.269 SSHL

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.270 SSHLL, SSHLL2

Alias conditions

Assembler symbols

Operation

C7.3.271 SSHR

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.272 SSRA

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.273 SSUBL, SSUBL2

Assembler symbols

Operation

C7.3.274 SSUBW, SSUBW2

Assembler symbols

Operation

C7.3.275 ST1 (multiple structures)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.276 ST1 (single structure)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.277 ST2 (multiple structures)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.278 ST2 (single structure)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.279 ST3 (multiple structures)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.280 ST3 (single structure)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.281 ST4 (multiple structures)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.282 ST4 (single structure)

No offset

Post-index

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.283 STNP (SIMD&FP)

Assembler symbols

Shared decode for all encodings

Operation

C7.3.284 STP (SIMD&FP)

Post-index

Pre-index

Signed offset

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.285 STR (immediate, SIMD&FP)

Post-index

Pre-index

Unsigned offset

Assembler symbols

Shared decode for all encodings

Operation for all encodings

C7.3.286 STR (register, SIMD&FP)

Assembler symbols

Shared decode for all encodings

Operation

C7.3.287 STUR (SIMD&FP)

Assembler symbols

Shared decode for all encodings

Operation

C7.3.288 SUB (vector)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.289 SUBHN, SUBHN2

Assembler symbols

Operation

C7.3.290 SUQADD

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.291 SXTL, SXTL2

Assembler symbols

Operation

C7.3.292 TBL

Assembler symbols

Operation

C7.3.293 TBX

Assembler symbols

Operation

C7.3.294 TRN1

Assembler symbols

Operation

C7.3.295 TRN2

Assembler symbols

Operation

C7.3.296 UABA

Assembler symbols

Operation

C7.3.297 UABAL, UABAL2

Assembler symbols

Operation

C7.3.298 UABD

Assembler symbols

Operation

C7.3.299 UABDL, UABDL2

Assembler symbols

Operation

C7.3.300 UADALP

Assembler symbols

Operation

C7.3.301 UADDL, UADDL2

Assembler symbols

Operation

C7.3.302 UADDLP

Assembler symbols

Operation

C7.3.303 UADDLV

Assembler symbols

Operation

C7.3.304 UADDW, UADDW2

Assembler symbols

Operation

C7.3.305 UCVTF (vector, fixed-point)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.306 UCVTF (vector, integer)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.307 UCVTF (scalar, fixed-point)

Assembler symbols

Operation

C7.3.308 UCVTF (scalar, integer)

Assembler symbols

Operation

C7.3.309 UHADD

Assembler symbols

Operation

C7.3.310 UHSUB

Assembler symbols

Operation

C7.3.311 UMAX

Assembler symbols

Operation

C7.3.312 UMAXP

Assembler symbols

Operation

C7.3.313 UMAXV

Assembler symbols

Operation

C7.3.314 UMIN

Assembler symbols

Operation

C7.3.315 UMINP

Assembler symbols

Operation

C7.3.316 UMINV

Assembler symbols

Operation

C7.3.317 UMLAL, UMLAL2 (by element)

Assembler symbols

Operation

C7.3.318 UMLAL, UMLAL2 (vector)

Assembler symbols

Operation

C7.3.319 UMLSL, UMLSL2 (by element)

Assembler symbols

Operation

C7.3.320 UMLSL, UMLSL2 (vector)

Assembler symbols

Operation

C7.3.321 UMOV

Alias conditions

Assembler symbols

Operation

C7.3.322 UMULL, UMULL2 (by element)

Assembler symbols

Operation

C7.3.323 UMULL, UMULL2 (vector)

Assembler symbols

Operation

C7.3.324 UQADD

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.325 UQRSHL

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.326 UQRSHRN, UQRSHRN2

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.327 UQSHL (immediate)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.328 UQSHL (register)

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.329 UQSHRN, UQSHRN2

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.330 UQSUB

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.331 UQXTN, UQXTN2

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.332 URECPE

Assembler symbols

Operation

C7.3.333 URHADD

Assembler symbols

Operation

C7.3.334 URSHL

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.335 URSHR

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.336 URSQRTE

Assembler symbols

Operation

C7.3.337 URSRA

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.338 USHL

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.339 USHLL, USHLL2

Alias conditions

Assembler symbols

Operation

C7.3.340 USHR

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.341 USQADD

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.342 USRA

Scalar

Vector

Assembler symbols

Operation for all encodings

C7.3.343 USUBL, USUBL2

Assembler symbols

Operation

C7.3.344 USUBW, USUBW2

Assembler symbols

Operation

C7.3.345 UXTL, UXTL2

Assembler symbols

Operation

C7.3.346 UZP1

Assembler symbols

Operation

C7.3.347 UZP2

Assembler symbols

Operation

C7.3.348 XTN, XTN2

Assembler symbols

Operation

C7.3.349 ZIP1

Assembler symbols

Operation

C7.3.350 ZIP2

Assembler symbols

Operation

Part D: The AArch64 System Level Architecture

D1: The AArch64 System Level Programmers’ Model

D1.1 Exception levels

D1.1.1 Typical Exception level usage model

D1.2 Exception terminology

D1.2.1 Terminology for taking an exception

D1.2.2 Terminology for returning from an exception

D1.2.3 Exception levels

D1.2.4 Definition of a precise exception

D1.2.5 Definitions of synchronous and asynchronous exceptions

D1.3 Execution state

D1.4 Security state

D1.4.1 The ARMv8-A security model

Security model when EL3 is using AArch64

D1.5 Virtualization

D1.5.1 The effect of implementing EL2 on the Exception model

Virtual interrupts

D1.6 Registers for instruction processing and exception handling

D1.6.1 The general purpose registers, R0-R30

D1.6.2 The stack pointer registers

Stack pointer register selection

D1.6.3 The SIMD and floating-point registers, V0-V31

D1.6.4 Saved Program Status Registers (SPSRs)

SPSR format for exceptions taken to AArch64 state

Pseudocode description of SPSR operations

D1.6.5 Exception Link Registers (ELRs)

D1.7 Process state, PSTATE

D1.7.1 Accessing PSTATE fields

D1.7.2 The Saved Program Status Registers (SPSRs)

D1.8 Program counter and stack pointer alignment

D1.8.1 PC alignment checking

D1.8.2 Stack pointer alignment checking

D1.9 Reset

D1.9.1 PE state on reset to AArch64 state

D1.9.2 Code sequence to use RMR_ELx.RR to request a Warm reset

D1.9.3 Pseudocode description of reset

D1.10 Exception entry

D1.10.1 Preferred exception return address

D1.10.2 Exception vectors

D1.10.3 Pseudocode description of exception entry to AArch64 state

D1.10.4 Exception classes and the ESR_ELx syndrome registers

Use of the ESR_EL1, ESR_EL2, and ESR_EL3

Reporting the EC encoding when an exception is routed to EL2

D1.10.5 Summary of register updates on faults taken to an Exception level that is using AArch64

Validity of FAR_ELx

Validity of HPFAR_EL2

D1.11 Exception return

D1.11.1 Exception return and PC alignment

D1.11.2 Illegal return events from AArch64 state

D1.11.3 Legal returns that set PSTATE.IL to 1

D1.11.4 The Illegal Execution state exception

D1.11.5 Pseudocode description of exception return

D1.12 The Exception level hierarchy

D1.12.1 The hierarchy of configuration and routing control

Controls provided at EL3

Controls provided at EL2

Controls provided at EL1

D1.12.2 Control of SIMD, floating-point and trace functionality

D1.12.3 Control of IMPLEMENTATION DEFINED features

D1.13 Synchronous exception types, routing and priorities

D1.13.1 Routing exceptions to EL2

D1.13.2 Synchronous exception prioritization for exceptions taken to AArch64

D1.13.3 Effect of Data Aborts

D1.13.4 Floating-point exception traps

Combinations of floating-point exceptions