2012--2013 学年第 1 学期 物理与电子工程 学院

期末考试卷《EDA 技术及应用 》 (课程论文等试卷样式)

学号: 201072020162

姓名: 张旭

班级: 2010 级电子信息(1)班

成绩:

评语:

装

订

(考试题目及要求)

利用 VHDL 语言设计一个正弦波信号发生器,采用 AD0832 芯片输出波形,要求具有至

少 100Hz、1KHz、10KHz 三段频率设置功能和频率微调功能。正弦波采样点不能低于

线

10 个,测试其输出信号波形不失真的最低频率和最高频率值。

i

�

1 引言 .................................................................................................................................................1

2 正弦波信号发生器的设计原理 .................................................................................................... 1

2.1 EDA 技术介绍..................................................................................................................... 1

2.1.1 EDA 介绍 ................................................................................................................. 1

2.1.2 VHDL 的基本介绍................................................................................................... 2

2.1.3 设计工具简介 ........................................................................................................ 3

2.2 信号发生器的原理结构 .................................................................................................... 3

2.2.1 设计流程 ................................................................................................................ 3

2.3 各个控制单元的实现......................................................................................................... 5

2.3.1 频率控制单元 ......................................................................................................... 5

2.3.2 信号波形成的设计 ................................................................................................ 7

2.4. 设计正弦波发生器功能 .................................................................................................. 8

2.5 硬件功能描述..................................................................................................................... 8

2.5.1 Altera 公司 CycloneII FPGA.............................................................................8

2.5.2 数码管驱动........................................................................................................... 10

2.5.3 DAC 模块 ............................................................................................................... 11

2.6 系统连接实物图.............................................................................................................. 14

3 程序设计及仿真分析 .................................................................................................................. 16

3.1 频率控制模块设计........................................................................................................... 16

3.1.1 输入识别模块程序设计 ......................................................................................16

3.1.2 输入识别模块的仿真 ..........................................................................................17

3.1.3 分频数模块程序设计........................................................................................... 18

3.1.4 分频数产生的仿真 ............................................................................................... 19

3.1.5 分频器模块程序设计 ..........................................................................................20

3.1.6 分频器的仿真 ...................................................................................................... 21

3.2 信号控制模块设计........................................................................................................... 21

3.2.1 信号控制模块程序设计 ......................................................................................21

3.2.2 信号控制模块仿真 .............................................................................................. 22

3.3 数码管显示模块设计....................................................................................................... 23

3.3.1 位选模块程序设计 .............................................................................................. 23

3.3.2 位选模块仿真分析 .............................................................................................. 24

3.3.3 数码管扫描模块程序设计...................................................................................24

3.3.4 数码管扫描模块仿真分析 ..................................................................................25

3.3.5 段选模块程序设计 .............................................................................................. 26

3.3.6 段选模块仿真分析 .............................................................................................. 27

4 硬件测试 ...................................................................................................................................... 27

4.1 示波器的基本波形显示及其分析 ..................................................................................27

4.2 频率改变使波形改变...................................................................................................... 28

4.3 数码管显示频率实物图以及说明 ..................................................................................30

5 设计总结 ...................................................................................................................................... 32

参考文献 .......................................................................................................................................... 33

附录 ...................................................................................................................................................34

ii

�

1 引言

简易正弦波发生器是信号发生器的一种,又名信号源。在生产实践和科研领

域中有着广泛的应用。在生产生活领域有广泛的应用。信号发生器产生不同频率

不同波形的电压、电流信号并加到被测器件或设备上,用示波器等仪器观察、测

量被测仪器的输出响应,以分析确定它们的性能参数。

信号发生器可以产生多种波形信号,如正弦波,三角波,锯齿波和方波等,

是电子测量领域中最基本、应用最广泛的一类电子仪器。基于信号发生器在生活

中应用的重要 EDA 技术的发展和应用领域的扩大与深入,EDA 技术在电子信

息、通信、自动控制及计算机等领域的重要性日益突出。作为一个学电气工程及

其自动化专业的学生,我们必须对 EDA 有个全面的认识及扎实的基础。信号发

生器在我们的日常中有很重要的应用,用 VHDL 语言去实现设计将会使我们对

本学科知识可以更好地掌握。

本设计以信号发生器的功能为设计对象,采用基于 VHDL 的采用自顶向下

设计方法,运用 EDA 技术编程进行各种波形的输入设计,设计处理和器件编程。

在 VHDL 语言的编写中按照语言描述规范,实现了几种波形的软件设计和具体

逻辑元件结构的硬件映射。在本设计中信号发生器能够产生正弦波,并能实现对

各种波形频率的选择和调节。

本设计是采用 VHDL 来实现的简易正弦波发生器。它能产生正弦波。且对

波形的要求如下:

(1)各波形的频率范围为 100Hz-10KHz;

(2)各波形频率可微调;

(3)用 LED 数码管实时显示输出波形的频率值;

2 正弦波信号发生器的设计原理

2.1 EDA 技术介绍

2.1.1 EDA 介绍

EDA 是电子设计自动化(Electronic Design Automation)的缩写,是 90 年

代初从 CAD(计算机辅助设计)、CAM(计算机辅助制造)、CAT(计算机辅

1

�

助测试)和 CAE(计算机辅助工程)的概念当中发展而来的。EDA 依赖于功能强

大的计算机,针对由 HDL(Hardware Description language)语言完成的设计

文件,自动地完成逻辑编译、化简、分割、综合及优化、布局布线、仿真以及对

于特定目标芯片的适配编译和编程下载等工作。综合器在工作前,必须给定所要

实现的硬件结构参数,它的功能就是将软件描述与给定的硬件结构用一定的方式

联系起来。也就是说,综合器是软件描述与硬件实现的一座桥梁。综合过程就是

将电路的高级语言描述转换成低级的、可与目标器件相映射的网表文件。适配器

的功能是将由综合器产生的网表文件配置于指定的目标器件中,产生最终的下载

文件。适配所选定的目标器件必须属于在综合器中已指定的目标器件系列。适配

器的功能是将由综合器产生的网表文件配置于指定的目标器件中,产生最终的下

载文件。适配所选定的目标器件必须属于在综合器中已指定的目标器件系列。

描述语言 HDL 是相对于一般的计算机软件语言,如 C、PASCAL 而言的。HDL

语言使用是设计硬件电子系统的计算机语言,它能描述电子系统的逻辑功能、电

路结构和连接方式。设计者可利用 HDL 程序来描述所希望的电路系统,规定器件

结构特征和电路的行为方式,然后利用综合器和适配器将此程序变成能控制器件

内部结构,并实现相应逻辑功能的门级或更底层的结构网表文件或下载文件。目

前比较流行的 HDL 语言主要有 Verilog HDL 和 VHDL。

几乎所有适于大学生做的数字逻辑电路实验都可以在计算机上利用 EDA

(Electronic Design Automatic—电子设计自动化)软件进行设计、仿真,只有

极少量外部配件不能在计算机上进行仿真。因此,在实习前期阶段,即实验预习

阶段的主要应用工具是 EDA 软件,利用 EDA 软件可以设计、仿真实验课题,进

行虚拟实验。通过虚拟实验使实验者在进入真实实验前就能对预做的实验有相当

的了解,甚至可以预测到实验的结果。这样在实际做实验时,可以把许多设计型

实验的难度降低,同时能有更多的时间让实验者动手做实验,研究问题,提高实

验效率。当前数字电路设计已由计算机辅助设计进入到以计算机为主的设计时

代。EDA 技术在电子信息、通信、自动控制及计算机应用等领域的重要性日益突

出。随着技术市场与人才市场对 EDA 技术的需求不断提高,产品的市场效率和技

术要求也将会影响到教学与科研。

2.1.2 VHDL 的基本介绍

VHDL 是一种主要的硬件描述语言之一,硬件描述语言(HDL)是各种描

述方法 中最能体现 EDA 优越性的描述方法。所谓硬件描述语言,实际上就是

一种描述工具,其描述的对象就是待设计电路系统的逻辑功能,实现该功能的算

法,选用的电路结构以及其他各种约束条件等。1984 年 VHDL 被 IEEE 确定为

2

�

标准的硬件描述语言。VHDL 具有涵盖面广,抽象描述强,良好可读性,即使用

周期长,完成大规模设计的分解及已有设计的再利用等优点,支持硬件的设计,

验证,综合和测试。VHDL 语言的的两个最直接应用领域时可编程逻辑器件和专

用集成电路。VHDL 能在多级别上对同一逻辑功能进行描述。VHDL 的基本结构包

含一个实体和一个结构体,而完整的 VHDL 结构还包括配置,程序包与库。各种

硬件描述语言中,VHDL 的描述能力最强,因此运用 VHDL 进行复杂电路设计时,

往往采用自顶向下结构化的设计方法。从根本来说,VHDL 是并发执行的。

2.1.3 设计工具简介

Quartus II 是 Altera 公司的综合性 PLD 发软件,支持原理图、VHDL、

VerilogHDL 以及 AHDL(Altera Hardware Description Language)等多种设计输入

形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整

PLD 设计流程。 Quartus II 支持 Altera 的 IP 核,包含了 LPM/MegaFunction 宏

功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设

计速度。对第三方 EDA 工具的良好支持,也使用户可以在设计流程的各个阶段

使用熟悉的第三方 EDA 工具。

2.2 信号发生器的原理结构

2.2.1 设计流程

基于 VHDL 语言设计一个简易正弦波发生器。通过外部选择输入键的选择,

可以输出正弦波,实现频率的改变。

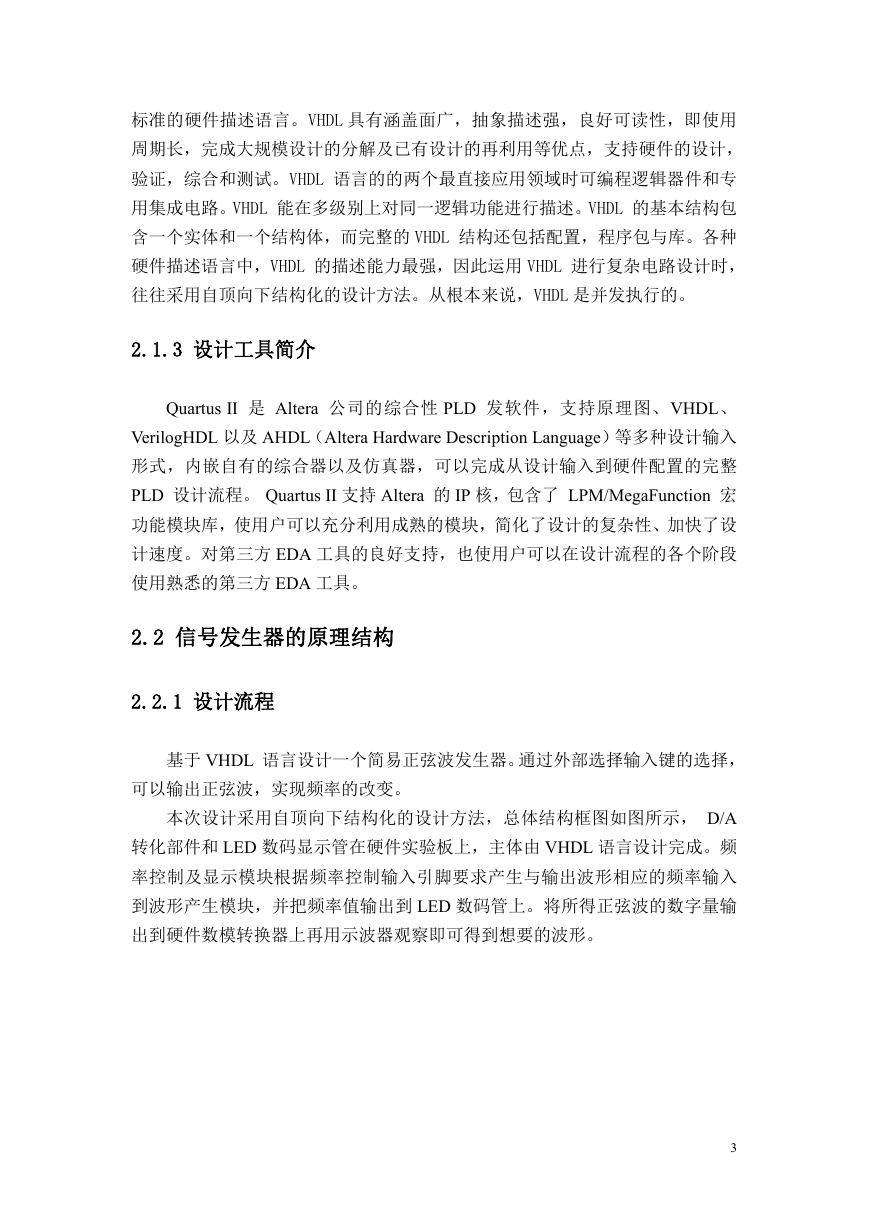

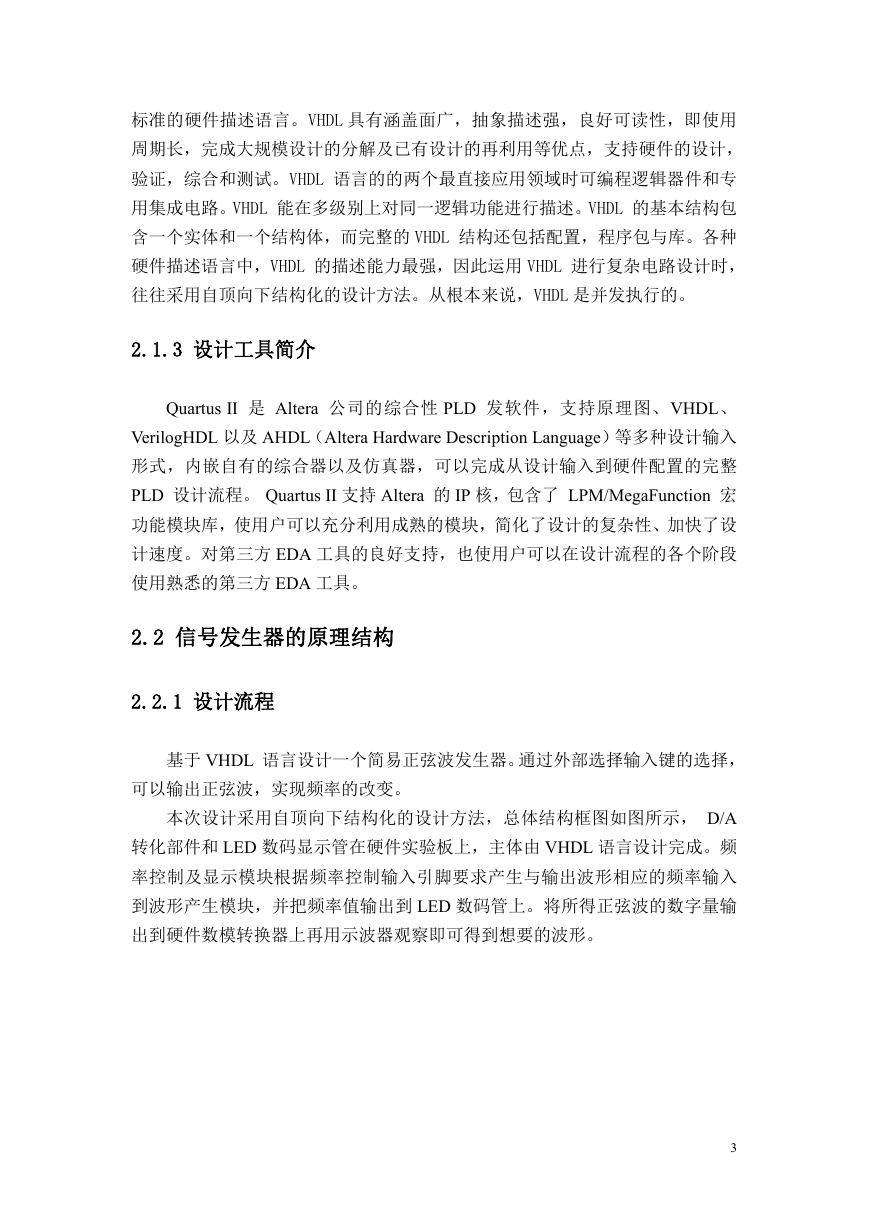

本次设计采用自顶向下结构化的设计方法,总体结构框图如图所示, D/A

转化部件和 LED 数码显示管在硬件实验板上,主体由 VHDL 语言设计完成。频

率控制及显示模块根据频率控制输入引脚要求产生与输出波形相应的频率输入

到波形产生模块,并把频率值输出到 LED 数码管上。将所得正弦波的数字量输

出到硬件数模转换器上再用示波器观察即可得到想要的波形。

3

�

输

入

频 率 控 制 及

显示

LED 显示数码管

波形形成

DA 转换

示波器

总体结构框图

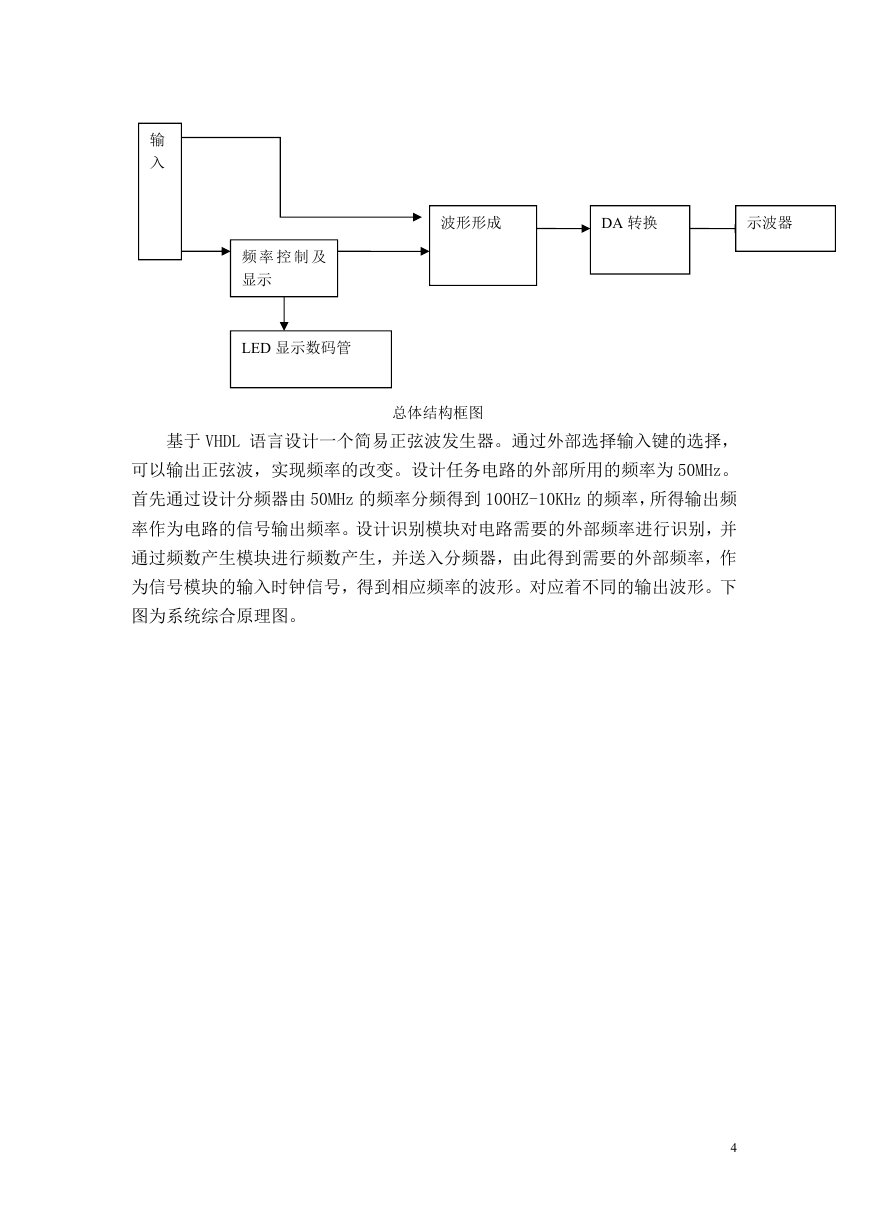

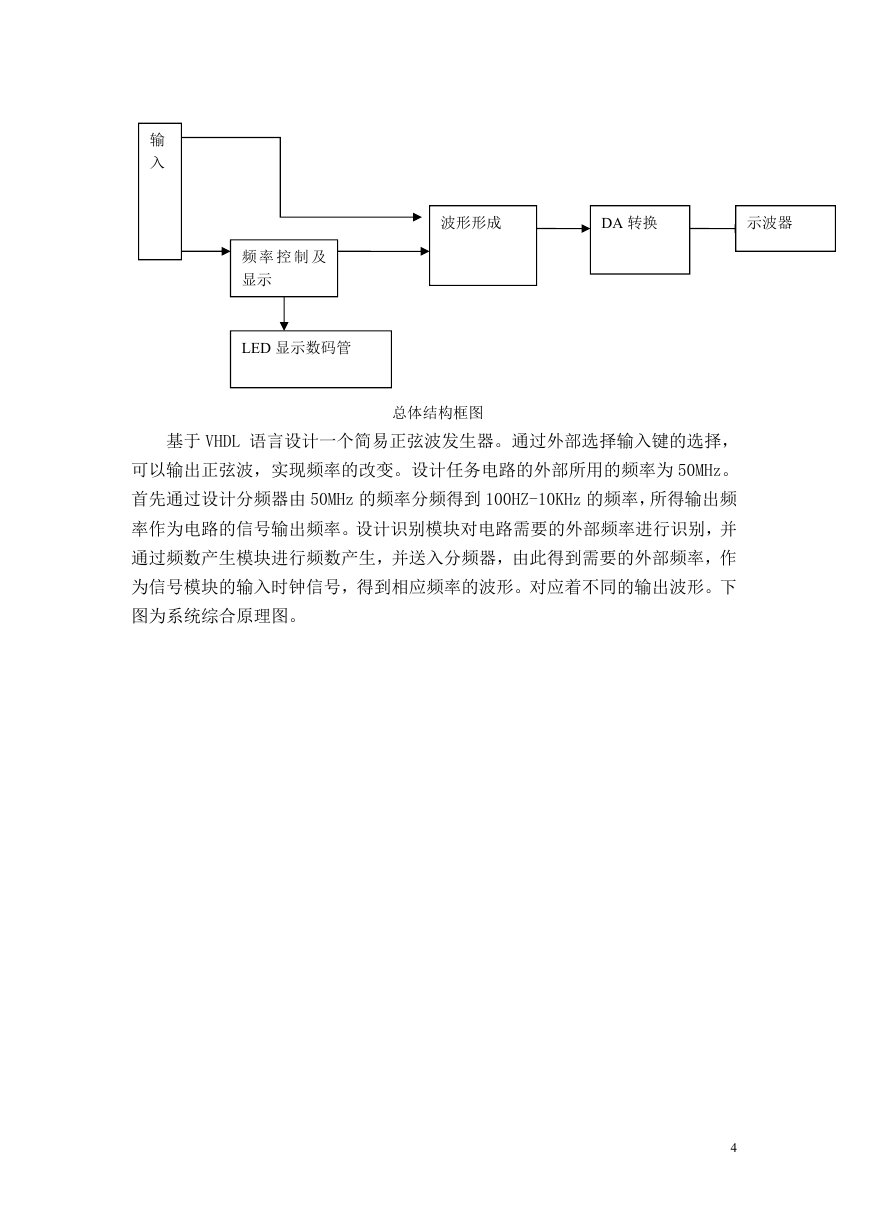

基于 VHDL 语言设计一个简易正弦波发生器。通过外部选择输入键的选择,

可以输出正弦波,实现频率的改变。设计任务电路的外部所用的频率为 50MHz。

首先通过设计分频器由 50MHz 的频率分频得到 100HZ-10KHz 的频率,所得输出频

率作为电路的信号输出频率。设计识别模块对电路需要的外部频率进行识别,并

通过频数产生模块进行频数产生,并送入分频器,由此得到需要的外部频率,作

为信号模块的输入时钟信号,得到相应频率的波形。对应着不同的输出波形。下

图为系统综合原理图。

4

�

fen100

clk

qout

clk_out

inst10

reg

clk

btn[1..0]

highh

loww

inst2

INPUT

VCC

INPUT

VCC

INPUT

VCC

INPUT

VCC

clk

btn[1..0]

highh

loww

PIN_23

PIN_12

PIN_13

PIN_31

PIN_33

xinhao

clk

d[7..0]

OUTPUT

shuju[7..0]

inst

addr[5..0]

pinshu

address[5..0]

inst3

shu[9..0]

w[3..0]

q[3..0]

b[3..0]

s[3..0]

g[3..0]

PIN_41

PIN_44

PIN_45

PIN_46

PIN_47

PIN_48

PIN_60

PIN_61

fenpin

clkout

shu[9..0]

clk

inst4

sel

clk_out

g[3..0]

s[3..0]

b[3..0]

q[3..0]

w[3..0]

w[3..0]

q[3..0]

b[3..0]

s[3..0]

g[3..0]

clk

qin1[3..0]

qin2[3..0]

qin3[3..0]

qin4[3..0]

qin5[3..0]

inst1

qout[3..0]

qout[3..0]

sel[4..0]

decode47

qin[3..0]

qout[7..0]

OUTPUT

duan[7..0]

PIN_4

PIN_5

PIN_6

PIN_8

PIN_10

PIN_15

PIN_14

PIN_30

inst5

OUTPUT

wei[4..0]

PIN_63

PIN_64

PIN_69

PIN_68

PIN_70

系统综合原理图。

2.3 各个控制单元的实现

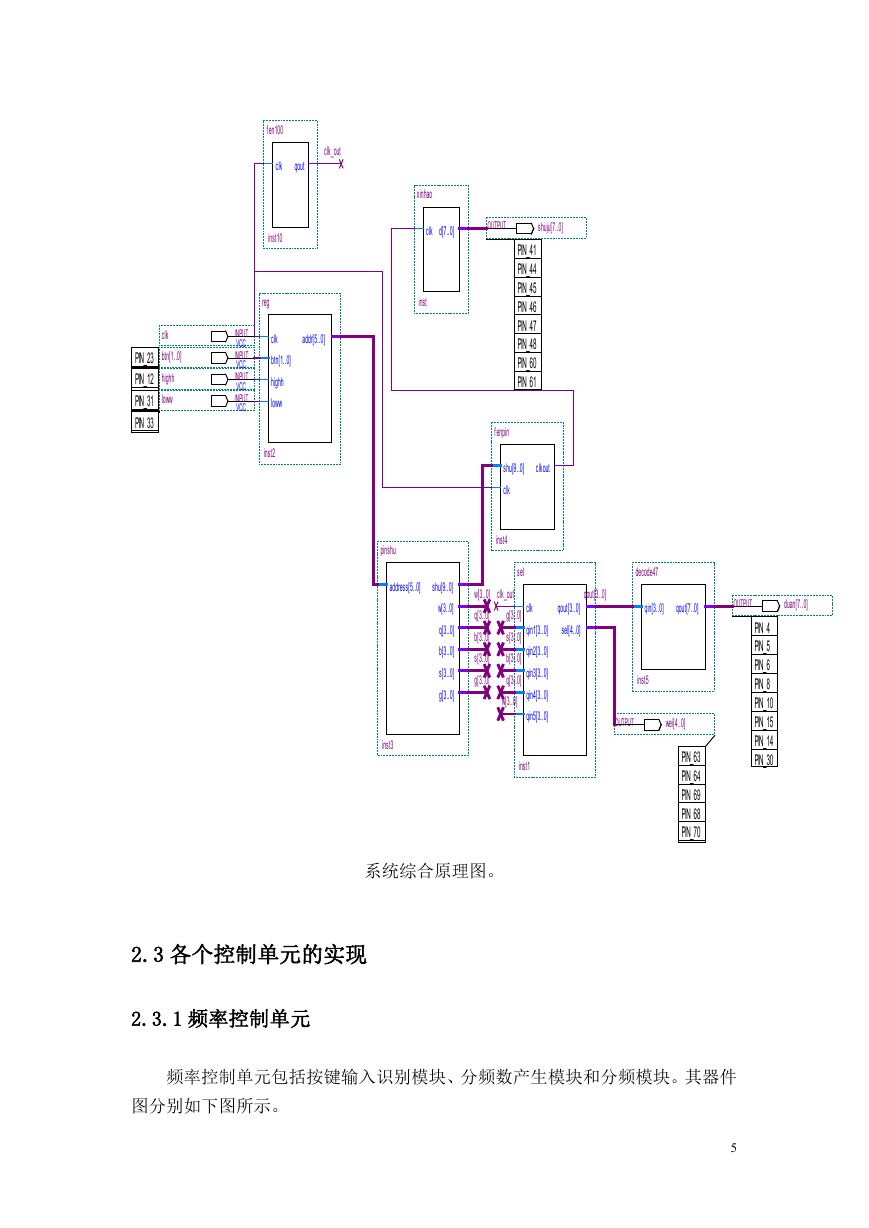

2.3.1 频率控制单元

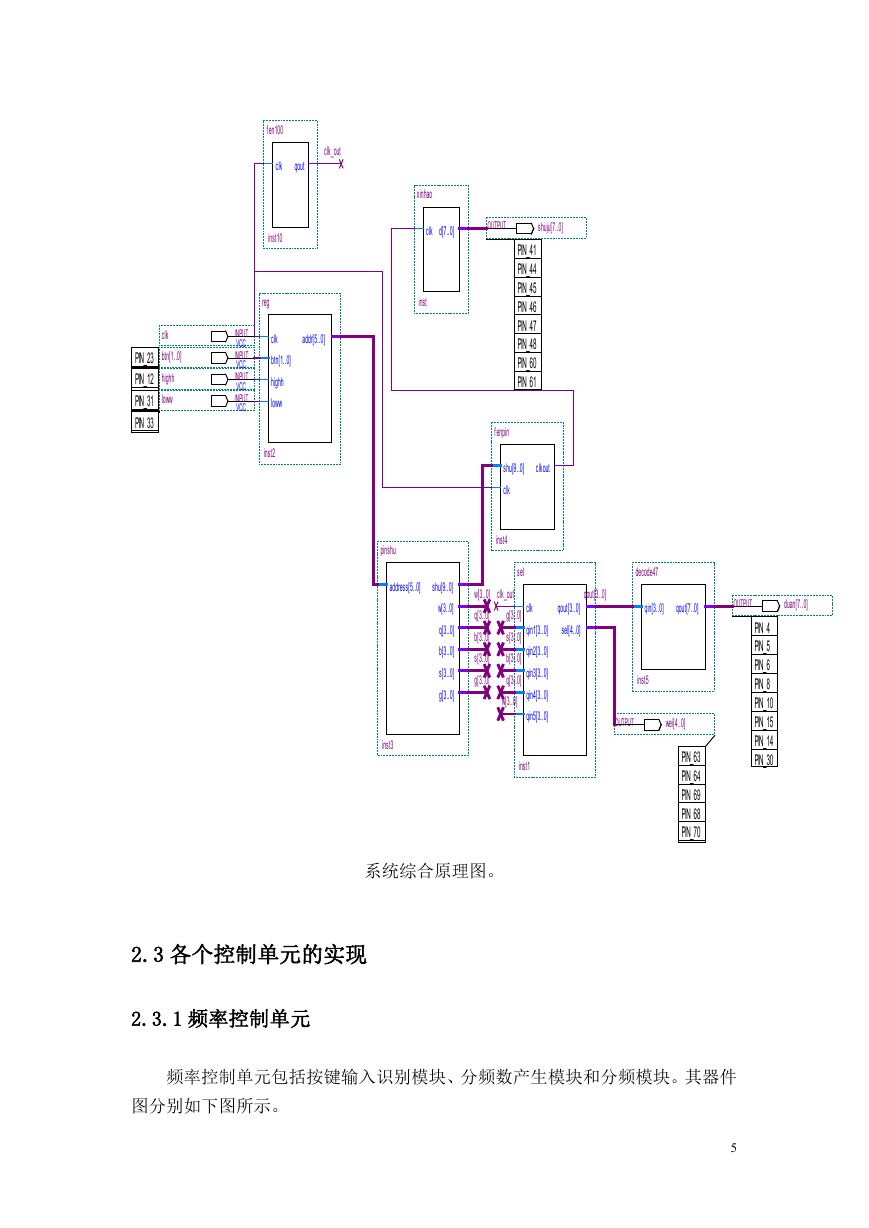

频率控制单元包括按键输入识别模块、分频数产生模块和分频模块。其器件

图分别如下图所示。

5

�

在按键输入识别模块中共有 4 个输入端。其中一个时钟输入端,以一个频率

调节输入端,一个使系统输出波形的频率为最大的控制输入端和一个使系统输出

波形的频率为最小的控制输入端。本课程设计要求输出波形的频率在每按一次相

应的按键时,就增加或减少 500Hz。而实验室的硬件设备上的按键都是拨码是按

键,即按键按下后一直有效,这显然不能满足要求。于是按键输入识别模块中用

如下的代码实现按键没按一次都能有效的功能。

pinshu

address[5..0]

addr[5..0]

reg

clk

btn[1..0]

highh

loww

shu[9..0]

w[3..0]

q[3..0]

b[3..0]

s[3..0]

g[3..0]

inst2

输入识别模块

inst

频数产生模块

decode47

qin[3..0]

qout[7..0]

inst

qout[3..0]

sel[4..0]

sel

clk

qin1[3..0]

qin2[3..0]

qin3[3..0]

qin4[3..0]

qin5[3..0]

inst

f enpin

clkout

shu[9..0]

clk

inst1

分频模块

f en100

clk

qout

inst

译码段选模块

译码位选模块

分频模块

【1】在输入识别模块中共有 4 个输入端,一个输出端。

其中:

clk 为系统基本时钟频率:50MHz;

btn[1..0]为使频率增减的按键以实现频率增加或减少的功能;

highh 为使系统输出最大频率的波形的控制输入端;

loww 为使系统输出最小频率的波形的控制输入端;

addr[5..0]为输出频率编号值的输出信号端

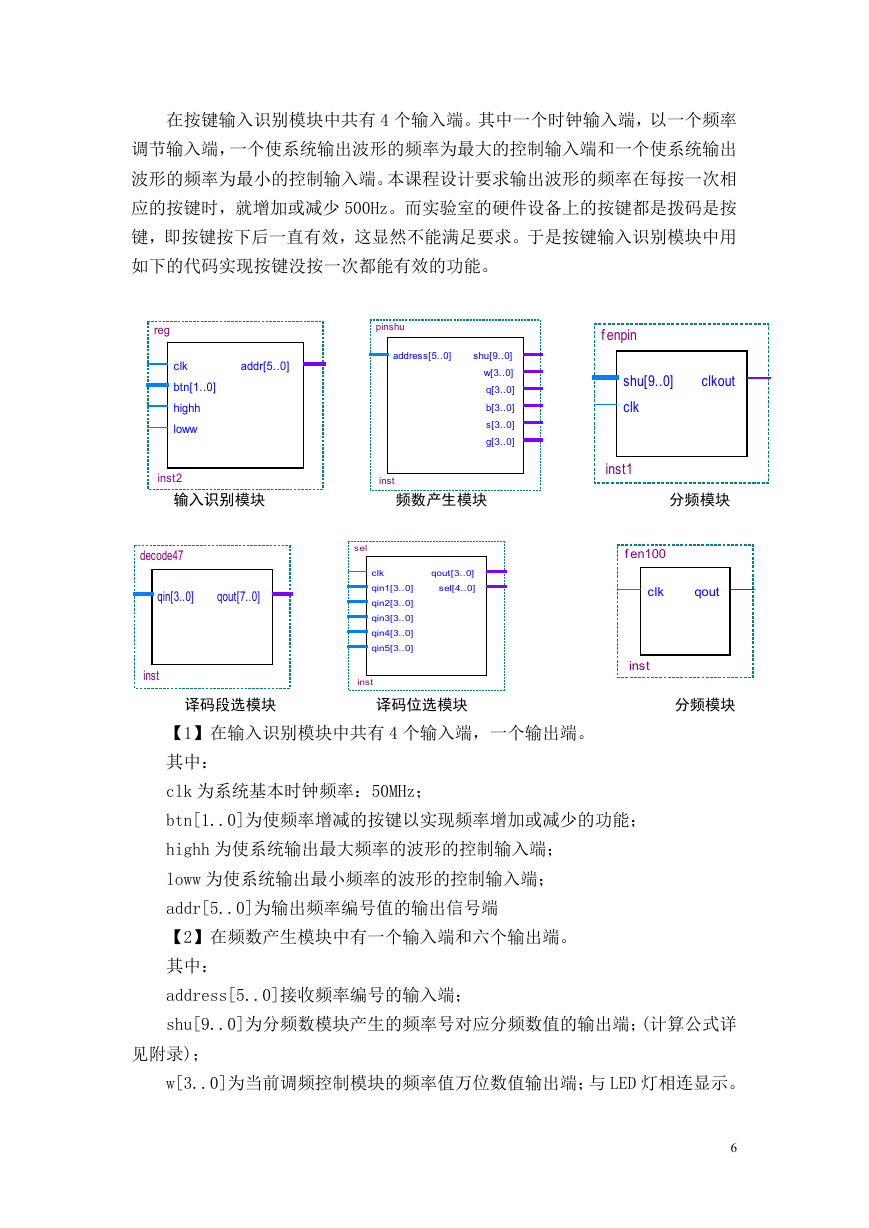

【2】在频数产生模块中有一个输入端和六个输出端。

其中:

address[5..0]接收频率编号的输入端;

shu[9..0]为分频数模块产生的频率号对应分频数值的输出端;(计算公式详

见附录);

w[3..0]为当前调频控制模块的频率值万位数值输出端;与 LED 灯相连显示。

6

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc