于博士信号完整性研究网�

信号完整性研究

作者:于争 博士

2009 年 4 月 10

�

信号完整性研究 原创:于争 博士

目录

信号完整性研究:什么是信号完整性? ................................................................................. 1

信号完整性研究:何时会遇到信号完整性问题 ................................................................... 2

信号完整性研究:重视信号上升时间 ................................................................................... 5

信号完整性研究:信号上升时间与带宽 ............................................................................... 5

信号完整性研究:电压容限 ................................................................................................. 10

信号完整性研究:什么是地弹 ............................................................................................. 11

信号完整性研究:反射现象 ................................................................................................. 12

信号完整性研究:理解临界长度 ......................................................................................... 13

电源完整性研究:电容的去耦时间 ..................................................................................... 14

信号完整性研究:特性阻抗 ................................................................................................. 16

信号完整性研究:多长的走线才是传输线 ......................................................................... 17

信号完整性研究:信号反射 ................................................................................................. 19

信号完整性研究:信号振铃是怎么产生的 ......................................................................... 20

信号完整性研究:PCB 走线宽度变化产生的反射.............................................................. 22

信号完整性研究:接收端容性负载的反射 ......................................................................... 23

信号完整性研究:PCB 走线中途容性负载反射.................................................................. 26

信号完整性研究:特性阻抗和频率有关吗? ..................................................................... 28

转载自:http://www.sig007.com

�

信号完整性研究 原创:于争 博士

信号完整性研究:什么是信号完整性?

如果你发现,以前低速时代积累的设计经验现在似乎都不灵了,同样的设计,以前

没问题,可是现在却无法工作,那么恭喜你,你碰到了硬件设计中最核心的问题:信号完整

性。早一天遇到,对你来说是好事。

在过去的低速时代,电平跳变时信号上升时间较长,通常几个 ns。器件间的互连线

不至于影响电路的功能,没必要关心信号完整性问题。但在今天的高速时代,随着 IC 输出

开关速度的提高,很多都在皮秒级,不管信号周期如何,几乎所有设计都遇到了信号完整性

问题。另外,对低功耗追求使得内核电压越来越低,1.2v 内核电压已经很常见了。因此系统

能容忍的噪声余量越来越小,这也使得信号完整性问题更加突出。

广义上讲,信号完整性是指在电路设计中互连线引起的所有问题,它主要研究互连

线的电气特性参数与数字信号的电压电流波形相互作用后,如何影响到产品性能的问题。主

要表现在对时序的影响、信号振铃、信号反射、近端串扰、远端串扰、开关噪声、非单调性、

地弹、电源反弹、衰减、容性负载、电磁辐射、电磁干扰等。

信号完整性问题的根源在于信号上升时间的减小。即使布线拓扑结构没有变化,如

果采用了信号上升时间很小的 IC 芯片,现有设计也将处于临界状态或者停止工作。

下面谈谈几种常见的信号完整性问题。

反射:

图 1 显示了信号反射引起的波形畸变。看起来就像振铃,拿出你制作的电路板,测

一测各种信号,比如时钟输出或是高速数据线输出,看看是不是存在这种波形。如果有,那

么你该对信号完整性问题有个感性的认识了,对,这就是一种信号完整性问题。

很多硬件工程师都会在时钟输出信号上串接一个小电阻,至于为什么,他们中很多

人都说不清楚,他们会说,很多成熟设计上都有,照着做的。或许你知道,可是确实很多人

说不清这个小小电阻的作用,包括很多有了三四年经验的硬件工程师,很惊讶么?可这确实

是事实,我碰到过很多。其实这个小电阻的作用就是为了解决信号反射问题。而且随着电阻

的加大,振铃会消失,但你会发现信号上升沿不再那么陡峭了。这个解决方法叫阻抗匹配,

奥,对了,一定要注意阻抗匹配,阻抗在信号完整性问题中占据着极其重要的地位。

串扰:

如果足够细心你会发现,有时对于某根信号线,从功能上来说并没有输出信号,但

测量时,会有幅度很小的规则波形,就像有信号输出。这时你测量一下与它邻近的信号线,

看看是不是有某种相似的规律!对,如果两根信号线靠的很近的话,通常会的。这就是串扰。

当然,被串扰影响的信号线上的波形不一定和邻近信号波形相似,也不一定有明显的规律,

更多的是表现为噪声形式。串扰在当今的高密度电路板中一直是个让人头疼的问题,由于布

线空间小,信号必然靠得很近,因此你比须面对它,只能控制但无法消除。对于受到串扰的

信号线,邻近信号的干扰对他来说就相当于噪声。

整理发布:Baidu 文库 浩书 1 / 32

http://passport.baidu.com/?business&aid=6&un=qust_scs#7

�

信号完整性研究 原创:于争 博士

串扰大小和电路板上的很多因素有关,并不是仅仅因为两根信号线间的距离。当然,距离最

容易控制,也是最常用的解决串扰的方法,但不是唯一方法。这也是很多工程师容易误解的

地方。更深入的讨论,我会在后续文章中陆续推出,如果你感兴趣,可以常来于博士信号完

整性研究网 http://www.sig007.com,关注博士讲坛栏目。

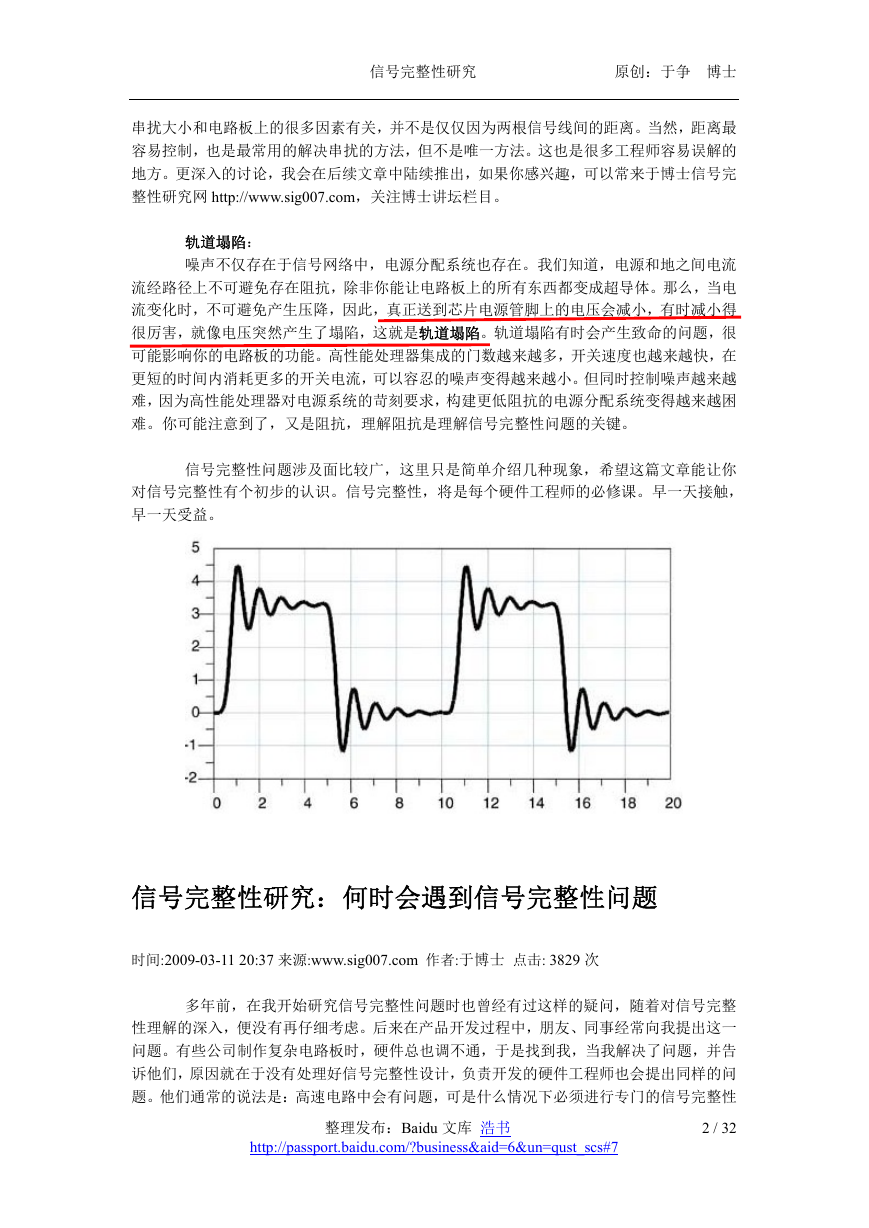

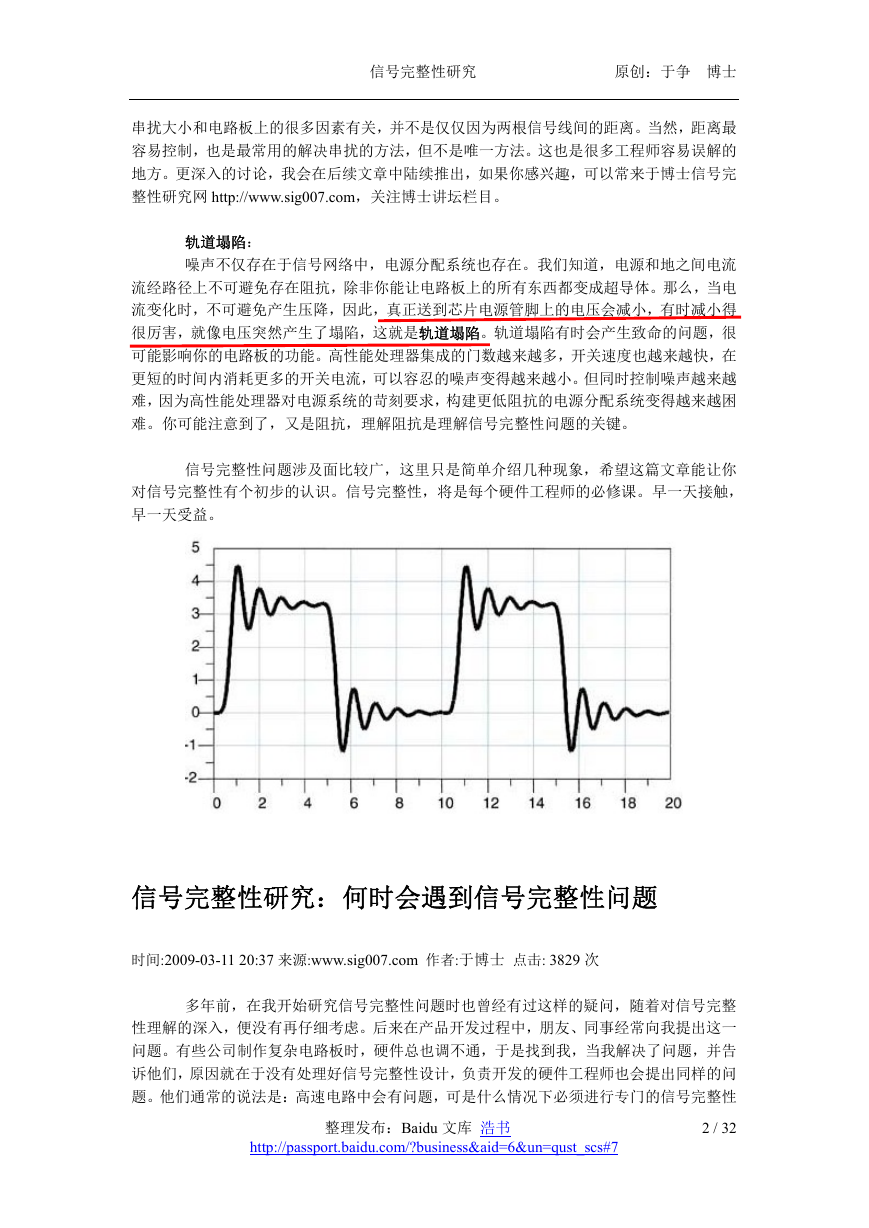

轨道塌陷:

噪声不仅存在于信号网络中,电源分配系统也存在。我们知道,电源和地之间电流

流经路径上不可避免存在阻抗,除非你能让电路板上的所有东西都变成超导体。那么,当电

流变化时,不可避免产生压降,因此,真正送到芯片电源管脚上的电压会减小,有时减小得

很厉害,就像电压突然产生了塌陷,这就是轨道塌陷。轨道塌陷有时会产生致命的问题,很

可能影响你的电路板的功能。高性能处理器集成的门数越来越多,开关速度也越来越快,在

更短的时间内消耗更多的开关电流,可以容忍的噪声变得越来越小。但同时控制噪声越来越

难,因为高性能处理器对电源系统的苛刻要求,构建更低阻抗的电源分配系统变得越来越困

难。你可能注意到了,又是阻抗,理解阻抗是理解信号完整性问题的关键。

信号完整性问题涉及面比较广,这里只是简单介绍几种现象,希望这篇文章能让你

对信号完整性有个初步的认识。信号完整性,将是每个硬件工程师的必修课。早一天接触,

早一天受益。

信号完整性研究:何时会遇到信号完整性问题

时间:2009-03-11 20:37 来源:www.sig007.com 作者:于博士 点击: 3829 次

多年前,在我开始研究信号完整性问题时也曾经有过这样的疑问,随着对信号完整

性理解的深入,便没有再仔细考虑。后来在产品开发过程中,朋友、同事经常向我提出这一

问题。有些公司制作复杂电路板时,硬件总也调不通,于是找到我,当我解决了问题,并告

诉他们,原因就在于没有处理好信号完整性设计,负责开发的硬件工程师也会提出同样的问

题。他们通常的说法是:高速电路中会有问题,可是什么情况下必须进行专门的信号完整性

整理发布:Baidu 文库 浩书 2 / 32

http://passport.baidu.com/?business&aid=6&un=qust_scs#7

�

信号完整性研究 原创:于争 博士

设计?

不断的有人问我,我不得不作更深入的思考。说实话,这个问题很难回答,或者说

他们这种问法很难回答。他们的意思可以解释为,速度高了就要考虑信号完整性,低速板不

存在这个问题,那总要有个临界频率,这个频率是多少?有人曾提出过这样的论点,当外部

总线频率超过 80MHz 时,就要进行专门的分析设计,低于这一频率,不用考虑信号完整性

问题。对这一论点,我不敢苟同。仔细分析,他们这种问法的背后是对信号完整性的一种误

解。

如果必须有一个答案的话,我想答案应该是:只要信号畸变到了无法容忍的程度就

要考虑信号完整性问题。呵呵,看起来像是在胡说八道,不过这确实是能找到的最好的答案

了。

要想弄清这个问题,必须先了解信号完整性的实质到底是什么。产生信号完整性的

原因很多,频率(值得推敲,暂且借用提问者的说法)只不过是其中的一个而已,怎么能单

单用频率来强行地划分界线!顺便说一句,很多人说频率的影响,其实这个词很值得推敲。

频率到底指的是哪个部分的频率?电路板上有主时钟频率,芯片内部主频,外部总线带宽,

数字信号波形带宽,电磁辐射频率,影响信号完整性的频率到底指的是哪一个?问题根源在

于信号上升时间。如果你不是很理解,可以到于博士信号完整性研究网学习。

信号完整性最原始的含义应该是:信号是否能保持其应该具有的波形。很多因素都

会导致信号波形的畸变,如果畸变较小,对于电路板不会产生影响,可是如果畸变很大,就

可能影响电路的功能。系统频率(芯片内部主频以及外部频率)、电磁干扰、电源波纹噪声,

数字器件开关噪声、系统热噪声等都会对信号产生影响,频率并不具有特殊的地位,你不能

把所有的注意力都放在频率这个因素上。

那么这里又会出现另一个问题,波形畸变多大,会对电路板功能产生影响。这没有

确定统一的指标,和具体应用以及电路板的其他电气指标有关。对于数字信号而言,对畸变

的容忍度较大。能有多大的容忍度,还要考虑电路板上的电源系统供电电压波纹有多大,系

统的噪声余量有多大,所用器件对于信号建立时间和保持时间的要求是多少等等。对于模拟

信号,相对比较敏感,容忍度较小,至于能容忍多大的畸变,和系统噪声,器件非线性特性,

电源质量等等有关。

是不是听起来很晦涩!确实,要说清楚这个问题并不容易,因为牵

扯到了太多的因素在内。下面这个数字信号波形的例子能让你有一个简单直观的理解。

整理发布:Baidu 文库 浩书 3 / 32

http://passport.baidu.com/?business&aid=6&un=qust_scs#7

�

信号完整性研究 原创:于争 博士

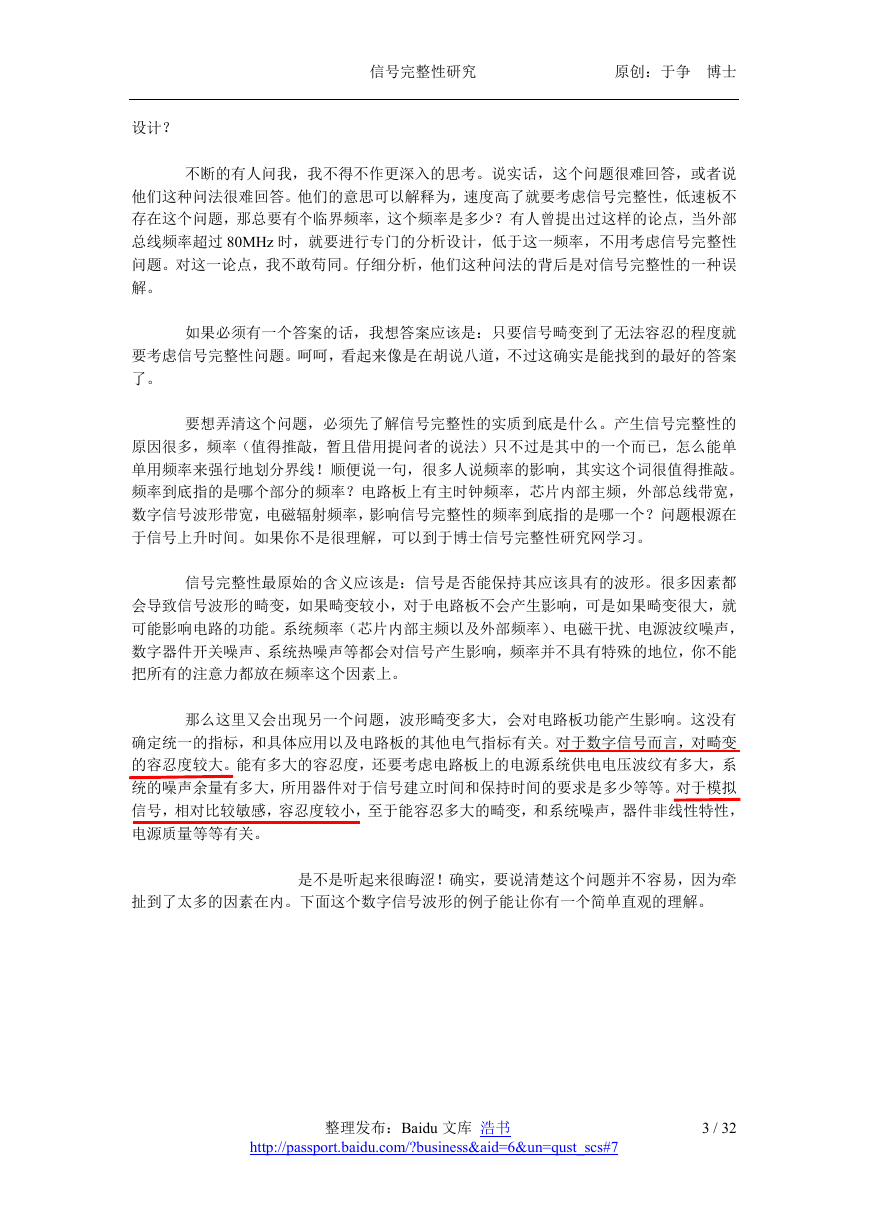

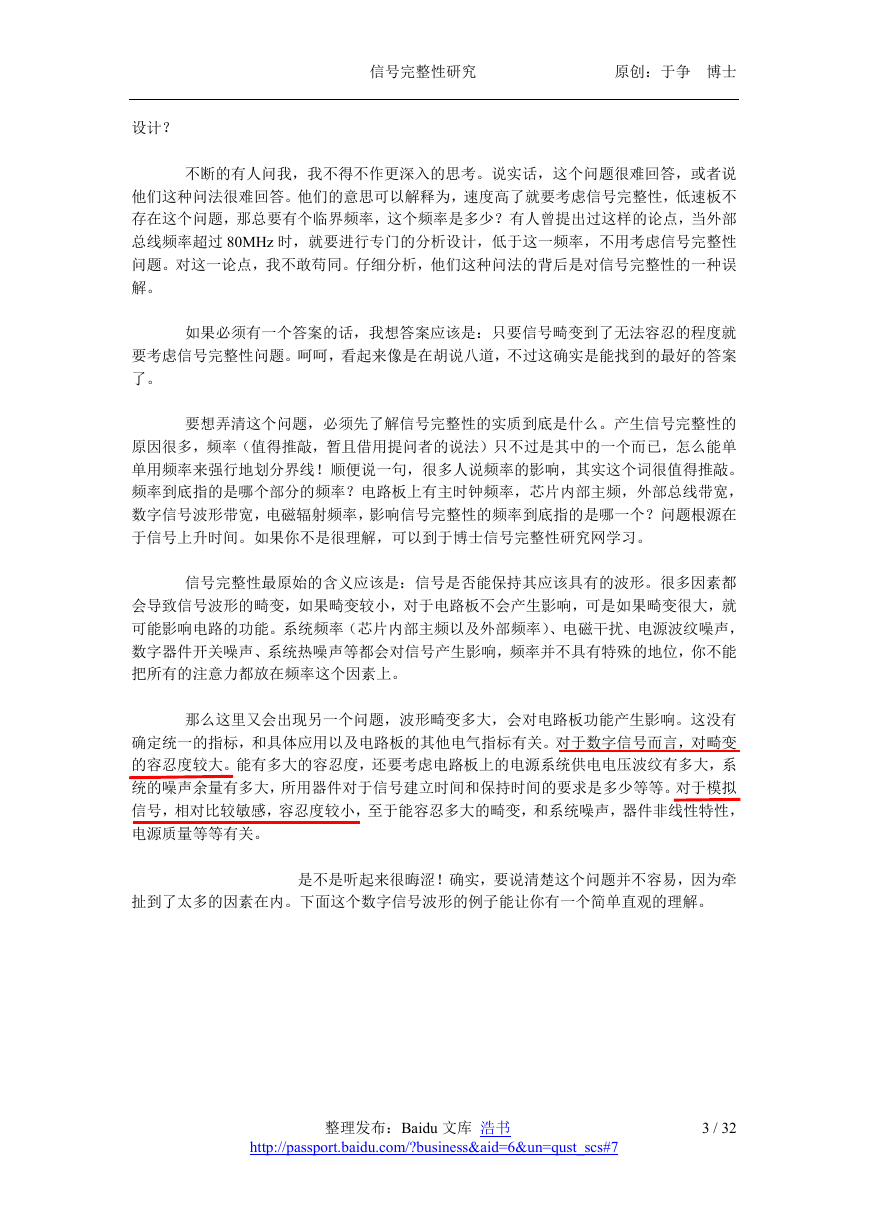

这是一个受反射影响的方波数字信号,波形的畸变仅仅是反射的结果,没有迭加其

他噪声。假设低电平逻辑小于 0.7v,高电平大于 2v。对于高电平来说,震荡的低谷部分可

能会冲到 2v 以下,此时电路处于不定态,可能引起电路误动作。所以,迭加在高电平上的

波纹幅度不能太大。由于电路存在噪声,电源也有波纹,这些最终都会迭加到信号波形上,

所以你计算波纹幅度的时候要考虑这些因素,而这些因素和你的电路板其他部分设计有关。

所以你无法确定一个统一的畸变标准,只能根据你具体电路的设计和应用综合考虑。最终的

原则只有一个:通过信号完整性设计、电源完整完整性设计等手段,将总的信号畸变控制在

一定范围内,保证电路板正常稳定工作。

工程中,解决信号完整性的问题是一个系统的工程,并不是一两种方法就可以包打天

下的。什么时候会碰到信号完整性问题也不是可以硬性的划一道线来区分,一句话,要根据

你的实际情况来定。

可能你会感觉,这么多不确定的因素,还怎么在最初设计的时候考虑信号完整性问

题?嗯,没问题的,其实对于所有影响信号质量的因素,你都可以通过一定的设计技术来控

制。对于电源波纹问题,那是电源完整性的问题,又是一个系统的工程。而其他的电磁干扰,

电磁兼容等则是另外一个系统工程。

总之,信号完整性问题涉及的知识较多,是一个跨学科的知识体系。网上关于信号

完整性基础知识讲解很多,但很少有讲得很深入的。要想学好信号完整性,你需要有一定的

精力投入,但可以告诉你,只要掌握学习方法,其实不难。一旦你学好它,回报是非常高的,

毕竟这方面的人才现在是奇缺阿,很多公司给信号完整性工程师开价都在 25W 以上,如果

你很牛的话,呵呵,决不是这个价。

好了,废话就不多说了。对于信号完整性技术问题,我会在于博

士信号完整性研究网的博士讲坛栏目进行深入探讨。

整理发布:Baidu 文库 浩书 4 / 32

http://passport.baidu.com/?business&aid=6&un=qust_scs#7

�

信号完整性研究 原创:于争 博士

信号完整性研究:重视信号上升时间

时间:2009-03-12 17:33 来源:未知 作者:于博士 点击: 3603 次

信号的上升时间,对于理解信号完整性问题至关重要,高速 pcb 设计中的绝大多数问题都

和它有关,你必须对他足够重视。

信号上升时间并不是信号从低电平上升到高电平所经历的时间,而是其中的一部分。业

界对它的定义尚未统一,最好的办法就是跟随上游的芯片厂商的定义,毕竟这些巨头有话语

权。通常有两种:第一种定义为 10-90 上升时间,即信号从高电平的 10%上升到 90%所经历

的时间。另一种是 20-80 上升时间,即信号从高电平的 20%上升到 80%所经历的时间。两种

都被采用,从 IBIS 模型中可看到这点。对于同一种波形,自然 20-80 上升时间要更短。

好了,只要了解这些就够了。对于我们终端应用来说,精确的数字有时并不是很重要,

而且这个数值芯片厂商通常也不会直接给我们列出,当然有些芯片可以从 IBIS 模型中大致

估计这个值,不幸的是,不是每种芯片你都能找到 IBIS 模型。

重要的是我们必须建立这样的概念:上升时间对电路性能有重要的影响,只要小到某一

范围,就必须引起注意,哪怕是一个很模糊的范围。没有必要精确定义这个范围标准,也没

有实际意义。你只需记住,现在的芯片加工工艺使得这个时间很短,已经到了 ps 级,你应

该重视他的影响的时候了。

随着信号上升时间的减小,反射、串扰、轨道塌陷、电磁辐射、地弹等问题变得更严重,

噪声问题更难于解决,上一代产品中设计方案在这一代产品中可能不适用了。

信号上升时间的减小,从频谱分析的角度来说,相当于信号带宽的增加,也就是信号中

有更多的高频分量,正是这些高频分量才使得设计变得困难。互连线必须作为传输线来对待,

从而产生了很多以前没有的问题。

因此,学习信号完整性,你必须有这样的概念:信号陡峭的上升沿,是产生信号完整性

问题的罪魁祸首。

信号完整性研究:信号上升时间与带宽

时间:2009-03-13 19:49 来源:未知 作者:于博士 点击: 4211 次

在前文中我提到过,要重视信号上升时间,很多信号完整性问题都是由信号

上升时间短引起的。本文就谈谈一个基础概念:信号上升时间和信号带宽的关

系。

整理发布:Baidu 文库 浩书 5 / 32

http://passport.baidu.com/?business&aid=6&un=qust_scs#7

�

信号完整性研究 原创:于争 博士

对于数字电路,输出的通常是方波信号。方波的上升边沿非常陡峭,根据傅

立叶分析,任何信号都可以分解成一系列不同频率的正弦信号,方波中包含了非

常丰富的频谱成分。

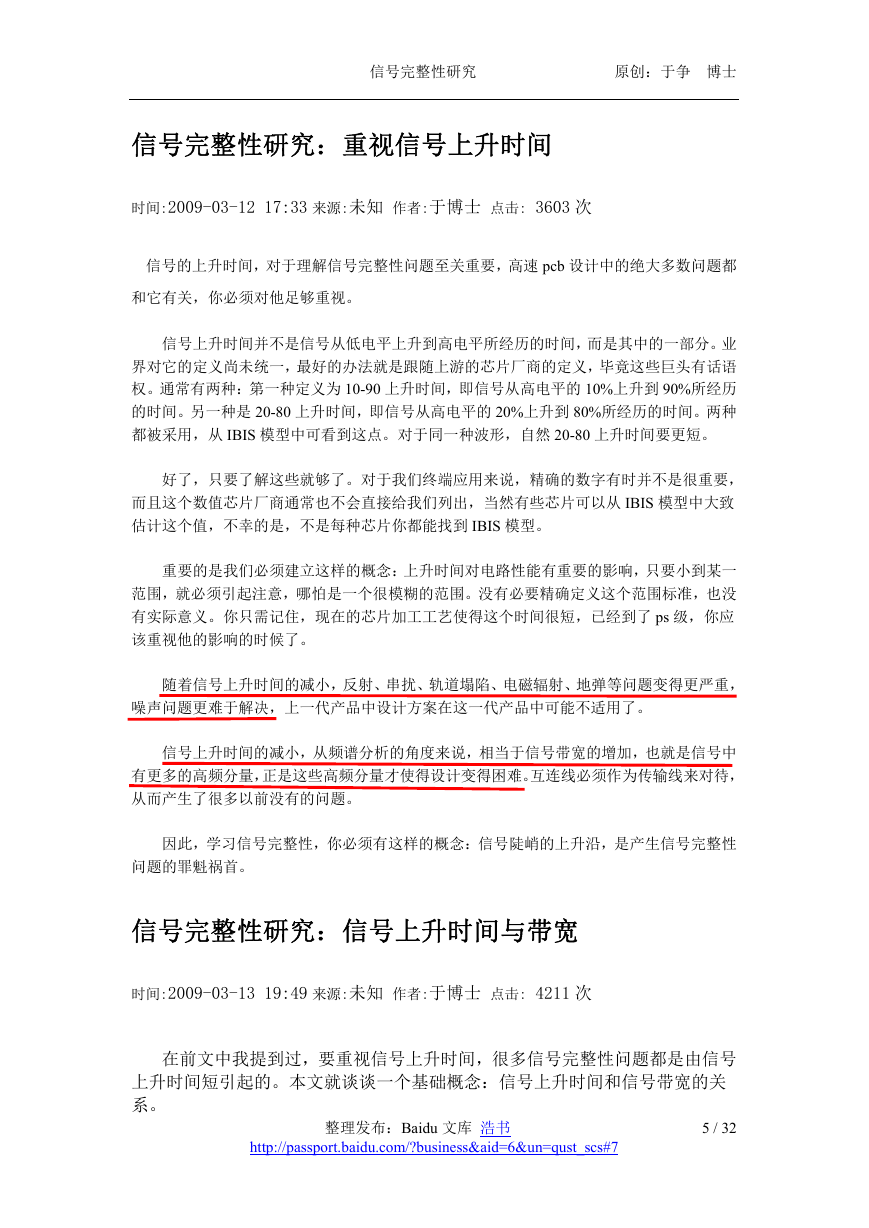

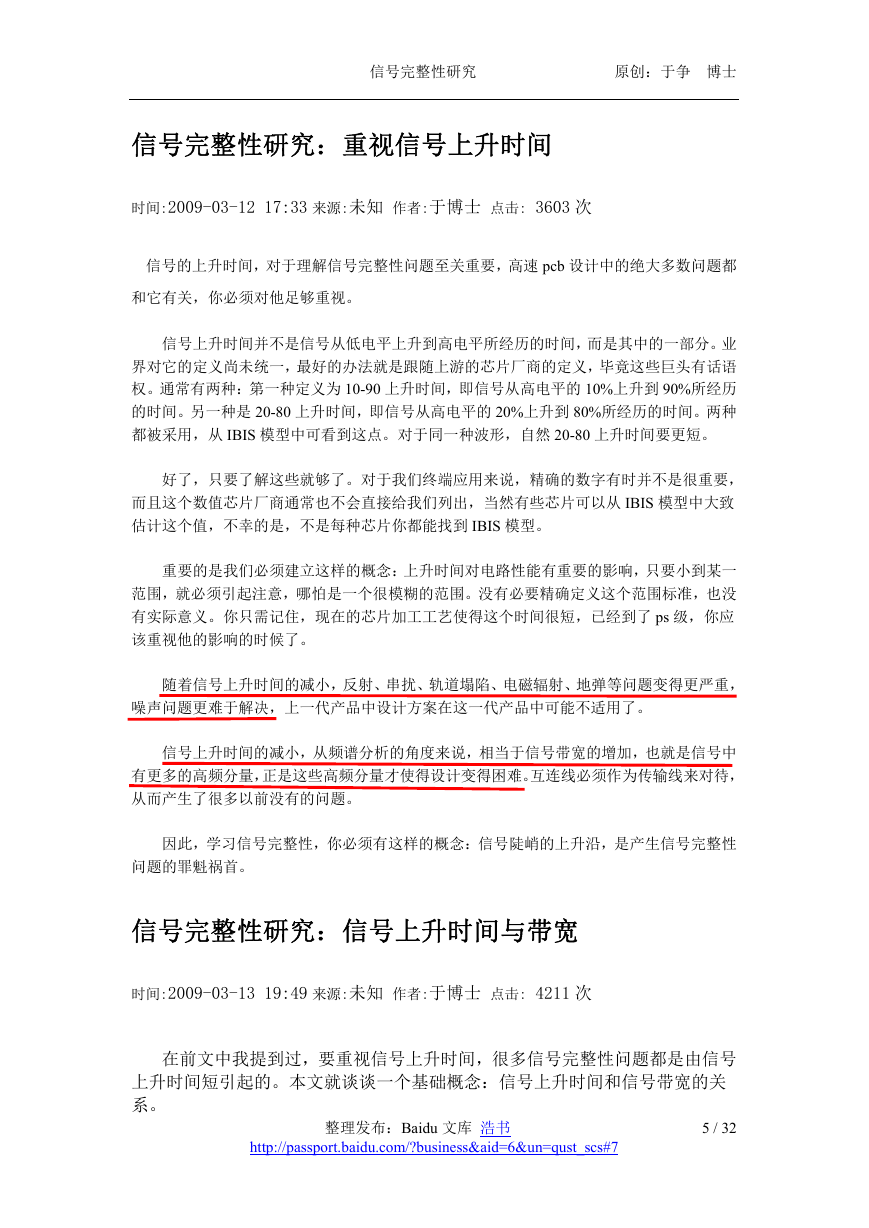

抛开枯燥的理论分析,我们用实验来直观的分析方波中的频率成分,看看不

同频率的正弦信号是如何叠加成为方波的。首先我们把一个 1.65v 的直流和一个

100MHz 的正弦波形叠加,得到一个直流偏置为 1.65v 的单频正弦波。我们给这

一信号叠加整数倍频率的正弦信号,也就是通常所说的谐波。3 次谐波的频率为

300MHz,5 次谐波的频率为 500MHz,以此类推,高次谐波都是 100MHz 的整数倍。

图 1 是叠加不同谐波前后的比较,左上角的是直流偏置的 100MHz 基频波形,右

上角时基频叠加了 3 次谐波后的波形,有点类似于方波了。左下角是基频+3 次

谐波+5 次谐波的波形,右下角是基频+3 次谐波+5 次谐波+7 次谐波的波形。这里

可以直观的看到叠加的谐波成分越多,波形就越像方波。

图 1

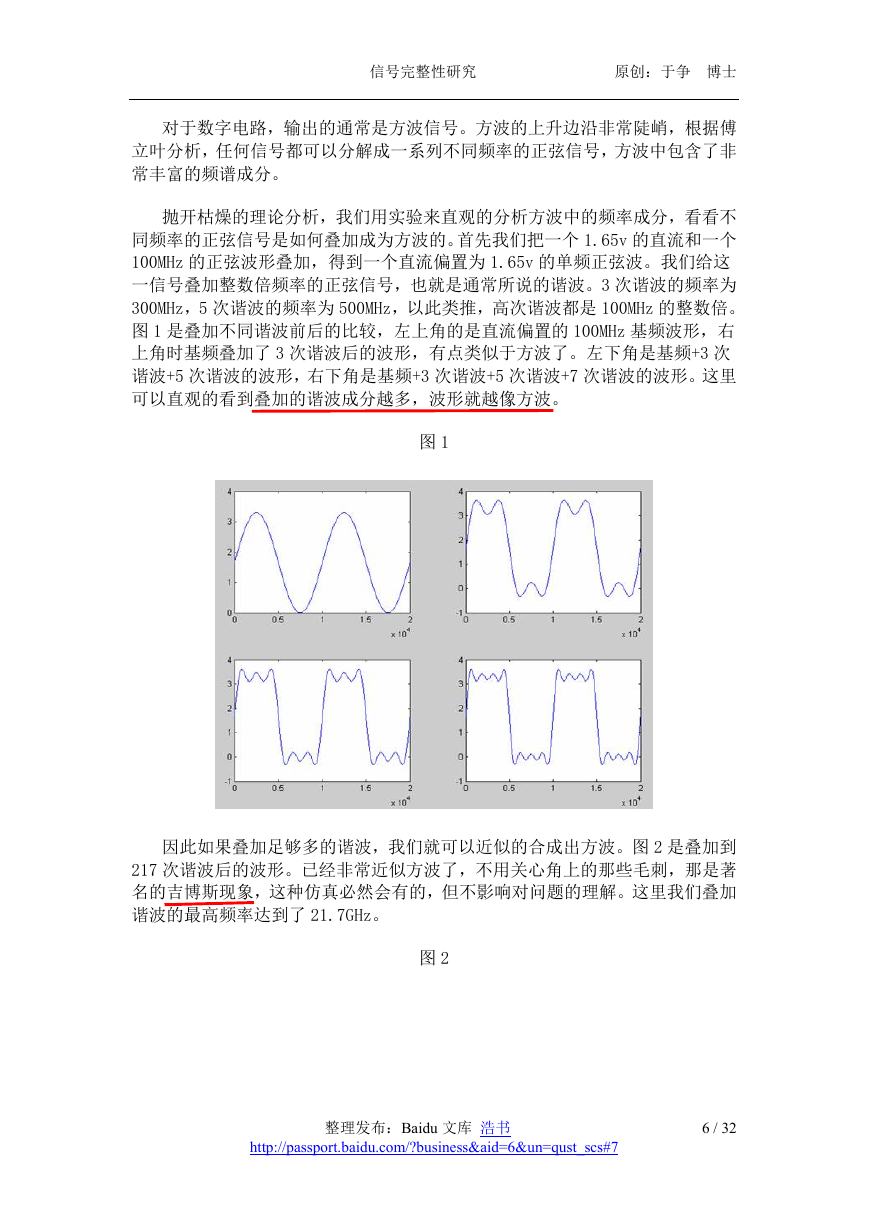

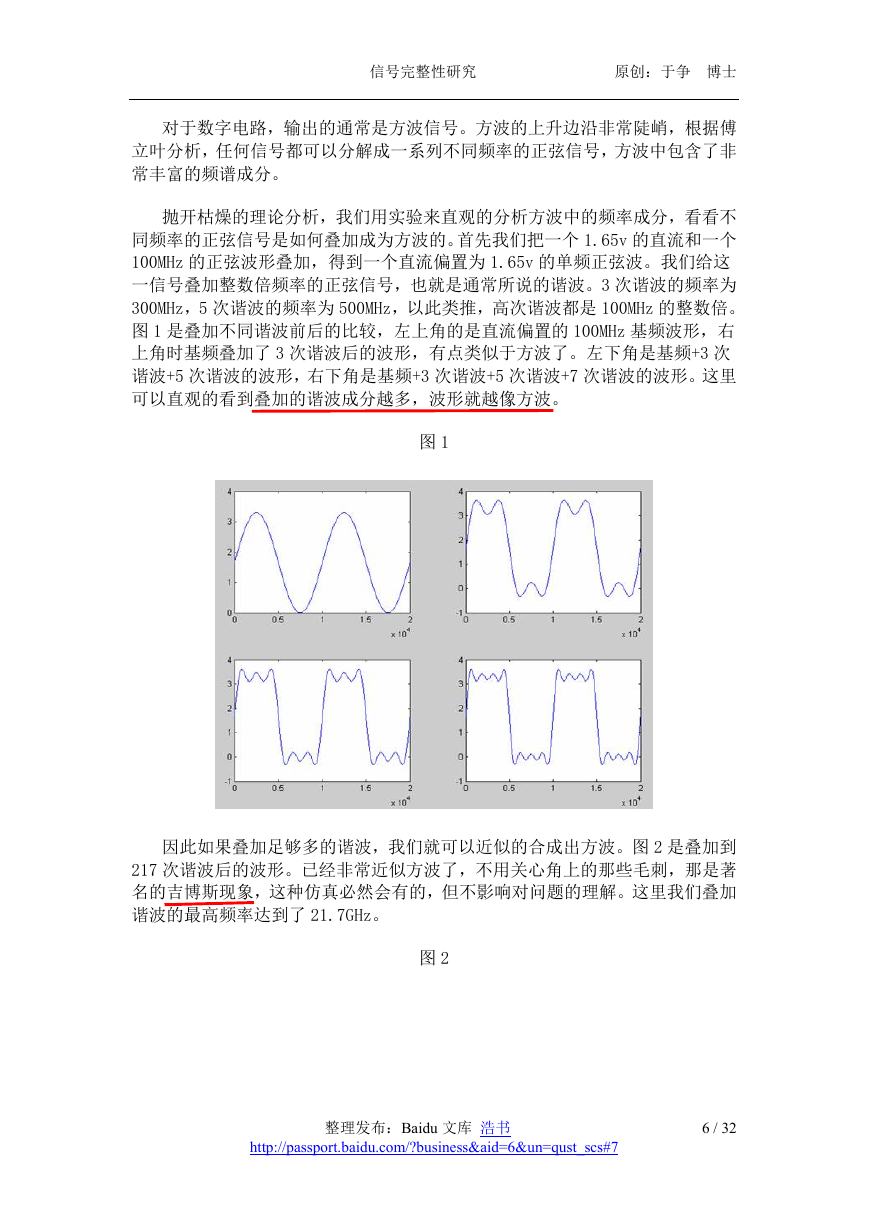

因此如果叠加足够多的谐波,我们就可以近似的合成出方波。图 2 是叠加到

217 次谐波后的波形。已经非常近似方波了,不用关心角上的那些毛刺,那是著

名的吉博斯现象,这种仿真必然会有的,但不影响对问题的理解。这里我们叠加

谐波的最高频率达到了 21.7GHz。

图 2

整理发布:Baidu 文库 浩书 6 / 32

http://passport.baidu.com/?business&aid=6&un=qust_scs#7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc