1

制造与设计

刘剑科等: 基于D SP 的信号发生器的设计与实现

基于D SP 的信号发生器的设计与实现

刘剑科, 王艳芬, 王胜利

(中国矿业大学 信息与电气工程学院 江苏 徐州 221008)

摘 要: 阐述了基于 TM S320V C5402 D SP 实现信号发生器的设计原理和实现方法, 详细介绍了所设计的信号发生器的

硬件电路结构和程序设计流程图。该信号发生器可以产生任意复杂的波形, 且信号的幅度和频率全部由 D SP 程序控制, 易

于修改, 弥补了通常信号发生器模式固定、波形不可编程以及精度低的不足。此外, 还运用了 D SP 的外部并行 16 位 FLA SH

引导装载设计方法, 通过在线 FLA SH 编程, 使得所设计的D SP 目标系统成为一个独立的脱机运行系统, 灵活性大大增强,

使用也更加方便。

关键词: 数字信号处理器; 信号发生器; 多通道缓冲串口; 引导装载; D

中图分类号: TN 911

25 文献标识码: B 文章编号: 1004

A 转换

373X (2005) 16

126

03

D esign and Rea l iza tion of Signa l Genera tor Ba sed on D SP

L IU J ianke, W AN G Yanfen, W AN G Shengli

(Schoo l of Info rm ation & Engineering, Ch ina U n iversity of M in ing and T echno logy, Xuzhou, 221008, Ch ina)

A bs tra c t: T h is p ap er expounds the design and realization of signal generato r based on TM S320V C5402 D SP

T he hardw are circu it

fixed,

structu re and the p rogram flow charts are also given in th is p ap er

it has unp rogram ab le and low p recision, th is signal generato r can generate com p lex w avefo rm s, and the vo ltage and frequency of the

signal generated by th is signal generato r are con tro lled by D SP p rogram s w h ich can be easily m odified

In o rder to im p rove the

indep endence of th is D SP system and the flex ib ility of its app lication, the design of p arallel boo t (16 b ) is also app lied to the D SP

system by in

U n like the general signal generato rs w h ich are often m ode

system p rogramm ing

Ke yw o rds: D SP; signal generato r; M cB SP; boo t load; D

A conversion

信号发生器在现代工程中应用非常广泛。在实际中常需

要产生一些特殊波形, 用于仿真实际信号的波形, 以检测和调

试测量装置。然而, 通常实验室的信号发生器模式固定, 波形

不可编程, 难以实现上述要求, 本文介绍的这种基于

TM S320V C5402 D SP 的信号发生器精度高、稳定性好、调整

信号波形及频率方便, 可以满足科研与实验的需要。

1 系统硬件组成

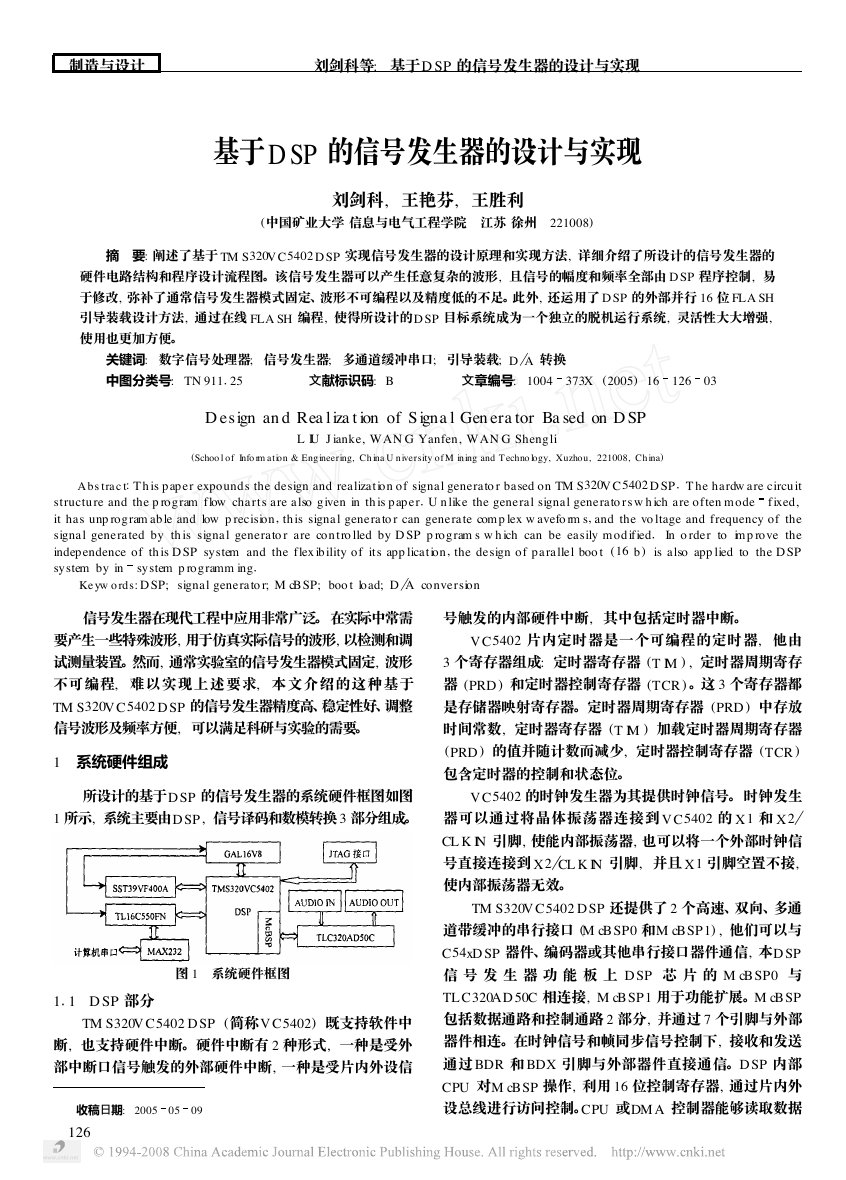

所设计的基于D SP 的信号发生器的系统硬件框图如图

1 所示, 系统主要由D SP, 信号译码和数模转换 3 部分组成。

图 1 系统硬件框图

1

1 D SP 部分

TM S320V C5402 D SP (简称 V C5402) 既支持软件中

断, 也支持硬件中断。硬件中断有 2 种形式, 一种是受外

部中断口信号触发的外部硬件中断, 一种是受片内外设信

收稿日期: 2005

05

09

621

号触发的内部硬件中断, 其中包括定时器中断。

V C5402 片内定时器是一个可编程的定时器, 他由

3 个寄存器组成: 定时器寄存器 (T IM ) , 定时器周期寄存

器 (PRD ) 和定时器控制寄存器 (TCR )。这 3 个寄存器都

是存储器映射寄存器。定时器周期寄存器 (PRD ) 中存放

时间常数, 定时器寄存器 (T IM ) 加载定时器周期寄存器

(PRD ) 的值并随计数而减少, 定时器控制寄存器 (TCR )

包含定时器的控制和状态位。

V C5402 的时钟发生器为其提供时钟信号。时钟发生

器可以通过将晶体振荡器连接到 V C5402 的 X1 和 X2

CL K IN 引脚, 使能内部振荡器, 也可以将一个外部时钟信

号直接连接到 X2

CL K IN 引脚, 并且 X1 引脚空置不接,

使内部振荡器无效。

TM S320V C5402 D SP 还提供了 2 个高速、双向、多通

道带缓冲的串行接口 (M cBSP0 和M cBSP1) , 他们可以与

C54xD SP 器件、编码器或其他串行接口器件通信, 本D SP

信 号 发 生 器 功 能 板 上 D SP 芯 片 的 M cBSP0 与

TL C320AD 50C 相连接, M cBSP1 用于功能扩展。M cBSP

包括数据通路和控制通路 2 部分, 并通过 7 个引脚与外部

器件相连。在时钟信号和帧同步信号控制下, 接收和发送

通过 BDR 和 BDX 引脚与外部器件直接通信。D SP 内部

CPU 对M cBSP 操作, 利用 16 位控制寄存器, 通过片内外

设总线进行访问控制。CPU 或DM A 控制器能够读取数据

�

《现代电子技术》2005 年第 16 期总第 207 期

接收寄存器 DRR 1 和 DRR 2 中的内容并向数据发送寄存

器 DXR 1 和 DXR 2 中写入数据。DXR 中的内容会通过发

送移位寄存器 XSR 输出到BDX 引脚。同样, BDR 引脚上

接收的数据总是先移位进入接收移位寄存器R SR , 然后复

制到 DRR 中。这种多级缓冲的方式使得片内数据搬移和

片外数据通信能够同时进行 1, 2 。

1

2 信号译码部分

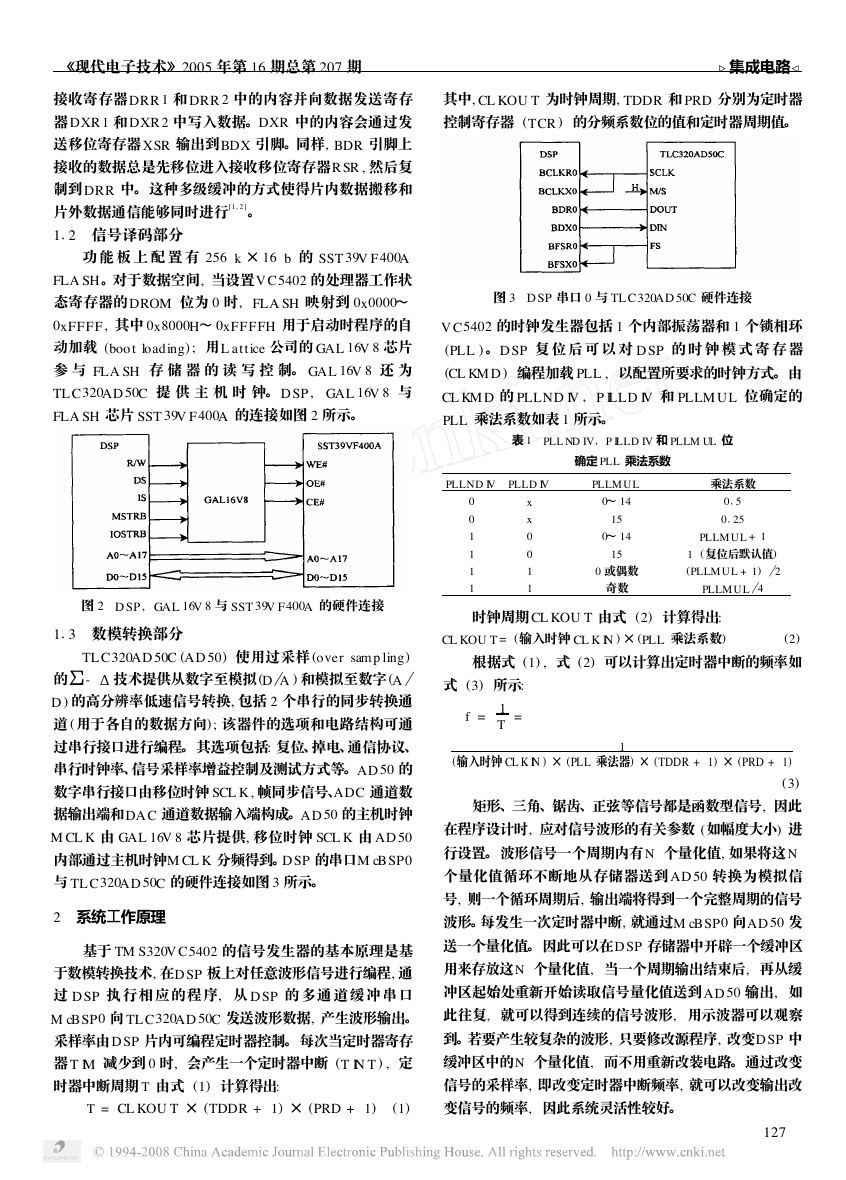

功 能 板 上 配 置 有 256 k × 16 b 的 SST 39V F400A

FLA SH。对于数据空间, 当设置V C5402 的处理器工作状

态寄存器的 DROM 位为 0 时, FLA SH 映射到 0x0000~

0xFFFF, 其中 0x8000H~ 0xFFFFH 用于启动时程序的自

动加载 (boo t loading) ; 用L attice 公司的 GAL 16V 8 芯片

参 与 FLA SH 存 储 器 的 读 写 控 制。 GAL 16V 8 还 为

TL C320AD 50C 提 供 主 机 时 钟。 D SP, GAL 16V 8 与

FLA SH 芯片 SST 39V F400A 的连接如图 2 所示。

图 2 D SP, GAL 16V 8 与 SST 39V F400A 的硬件连接

1

3 数模转换部分

技术提供从数字至模拟 (D

TL C320AD 50C (AD 50) 使用过采样 (over sam p ling)

A ) 和模拟至数字 (A

的∑-

D ) 的高分辨率低速信号转换, 包括 2 个串行的同步转换通

道 (用于各自的数据方向) ; 该器件的选项和电路结构可通

过串行接口进行编程。其选项包括: 复位、掉电、通信协议、

串行时钟率、信号采样率增益控制及测试方式等。AD 50 的

数字串行接口由移位时钟 SCL K, 帧同步信号、ADC 通道数

据输出端和DA C 通道数据输入端构成。AD 50 的主机时钟

M CL K 由 GAL 16V 8 芯片提供, 移位时钟 SCL K 由 AD 50

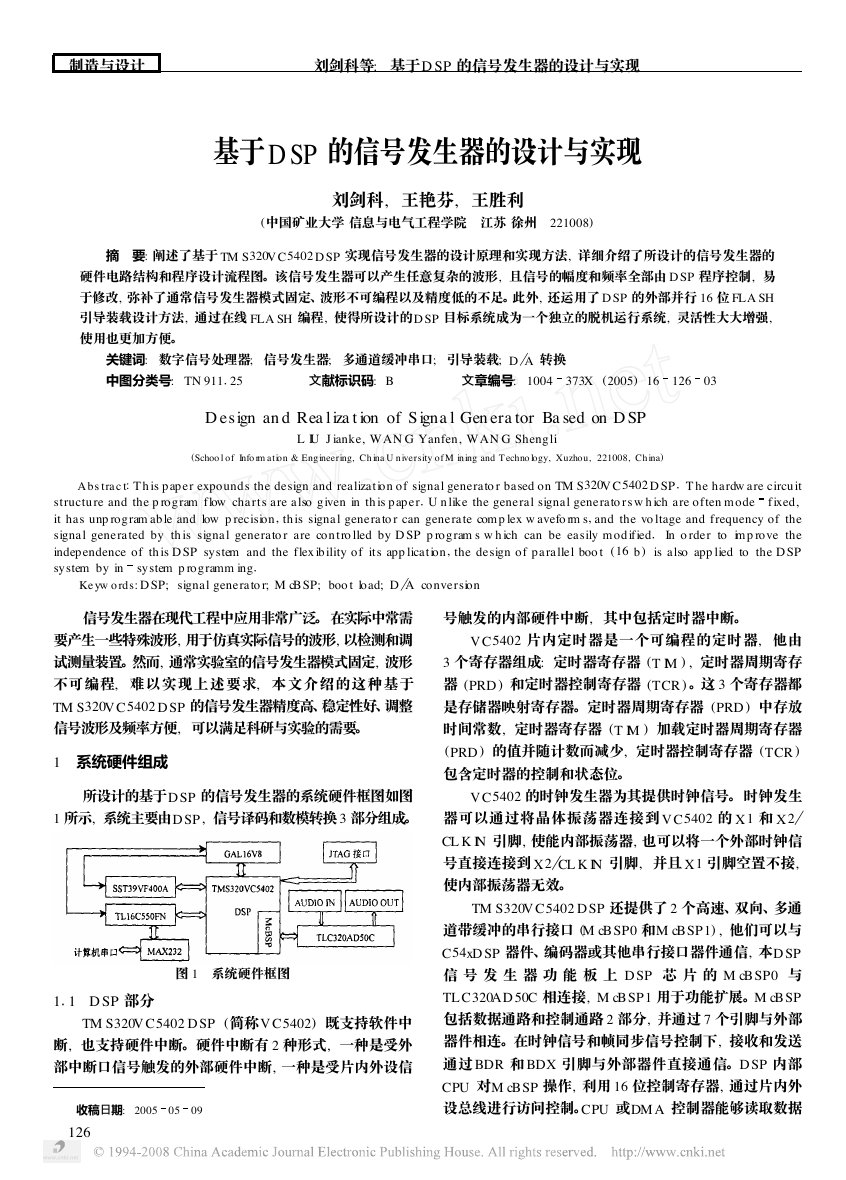

内部通过主机时钟M CL K 分频得到。D SP 的串口M cBSP0

与 TL C320AD 50C 的硬件连接如图 3 所示。

2 系统工作原理

基于 TM S320V C5402 的信号发生器的基本原理是基

于数模转换技术, 在D SP 板上对任意波形信号进行编程, 通

过 D SP 执行相应的程序, 从 D SP 的多 通 道 缓 冲 串 口

M cBSP0 向 TL C320AD 50C 发送波形数据, 产生波形输出。

采样率由D SP 片内可编程定时器控制。每次当定时器寄存

器 T IM 减少到 0 时, 会产生一个定时器中断 (T IN T ) , 定

时器中断周期 T 由式 (1) 计算得出:

T = CL KOU T × (TDDR + 1) × (PRD + 1)

(1)

集成电路

其中, CL KOU T 为时钟周期, TDDR 和 PRD 分别为定时器

控制寄存器 (TCR ) 的分频系数位的值和定时器周期值。

图 3 D SP 串口 0 与 TL C320AD 50C 硬件连接

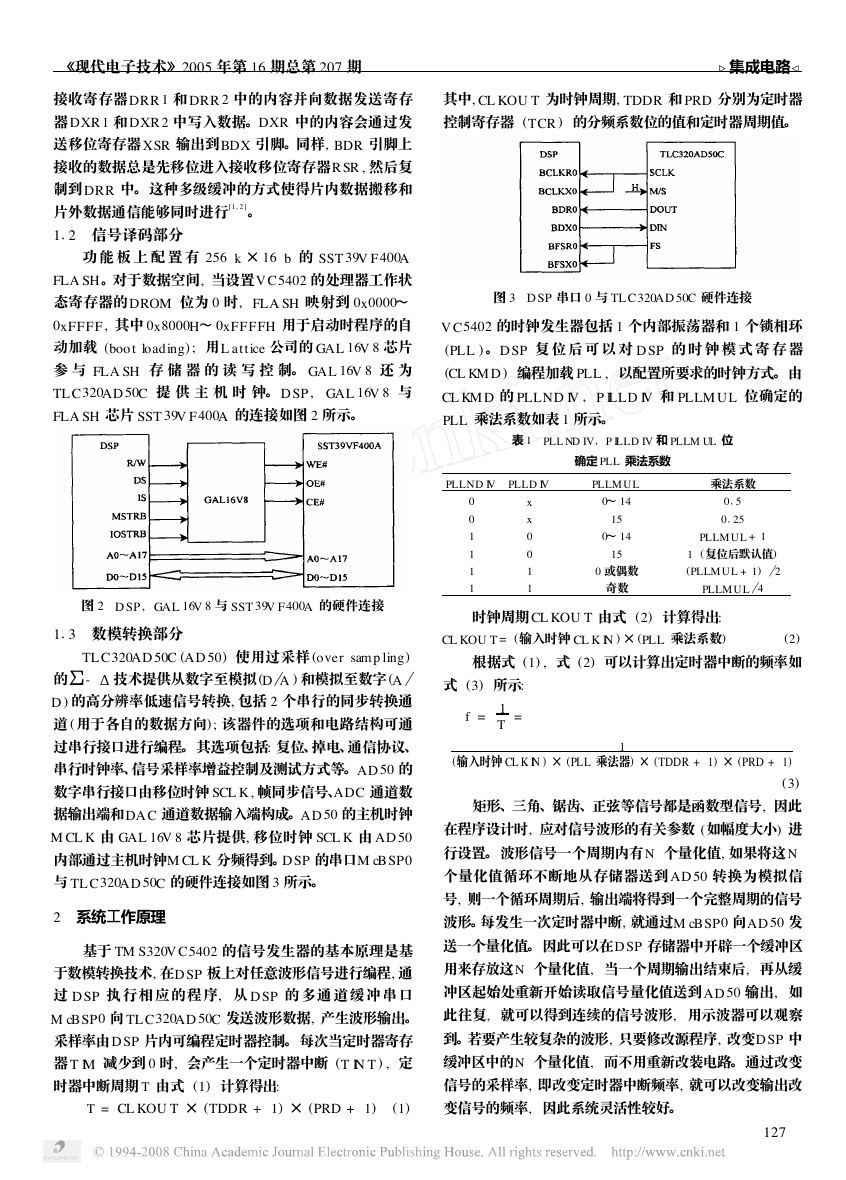

V C5402 的时钟发生器包括 1 个内部振荡器和 1 个锁相环

(PLL )。D SP 复 位 后 可 以 对 D SP 的 时 钟 模 式 寄 存 器

(CL KM D ) 编程加载 PLL , 以配置所要求的时钟方式。由

CL KM D 的 PLLND IV , P ILLD IV 和 PLLM U L 位确定的

PLL 乘法系数如表 1 所示。

表 1 PLL ND IV, P ILLD IV 和 PLLM UL 位

确定 PLL 乘法系数

PLLND IV PLLD IV

PLLM UL

0

0

1

1

1

1

x

x

0

0

1

1

0~ 14

15

0~ 14

15

0 或偶数

奇数

乘法系数

0

0

5

25

PLLM UL + 1

1 (复位后默认值)

(PLLM UL + 1)

2

4

PLLM UL

时钟周期 CL KOU T 由式 (2) 计算得出:

CL KOU T = (输入时钟 CL K IN ) × (PLL 乘法系数)

(2)

根据式 (1) , 式 (2) 可以计算出定时器中断的频率如

式 (3) 所示:

f =

1

T

=

1

(输入时钟 CL K IN ) × (PLL 乘法器) × (TDDR + 1) × (PRD + 1)

(3)

矩形、三角、锯齿、正弦等信号都是函数型信号, 因此

在程序设计时, 应对信号波形的有关参数 (如幅度大小) 进

行设置。波形信号一个周期内有 N 个量化值, 如果将这 N

个量化值循环不断地从存储器送到 AD 50 转换为模拟信

号, 则一个循环周期后, 输出端将得到一个完整周期的信号

波形。每发生一次定时器中断, 就通过M cBSP0 向AD 50 发

送一个量化值。因此可以在D SP 存储器中开辟一个缓冲区

用来存放这N 个量化值, 当一个周期输出结束后, 再从缓

冲区起始处重新开始读取信号量化值送到AD 50 输出, 如

此往复, 就可以得到连续的信号波形, 用示波器可以观察

到。若要产生较复杂的波形, 只要修改源程序, 改变D SP 中

缓冲区中的N 个量化值, 而不用重新改装电路。通过改变

信号的采样率, 即改变定时器中断频率, 就可以改变输出改

变信号的频率, 因此系统灵活性较好。

721

�

1

1

1

1

1

1

Ù

1

1

1

刘剑科等: 基于D SP 的信号发生器的设计与实现

制造与设计

3 程序设计与流程图

软件系统采用模块化结构设计, 主要是由主程序、D SP

初始化子程序、AD 50 初始化子程序和中断矢量表程序组

成。主程序用 C 语言编写, 流程图如图 4 所示; D SP 初始化

子程序流程图如图 5 所示。

言工具包中的H EX 转换工具完成。对源文件进行编译和链

接, 将生成的 signal

ou t 文件作为输入文件, 利用CCS ID E

自带的H ex500 程序包, 在命令行模式下生成这个引导装载

表。相应的转换配置文件 2hex

cm d 内容如下:

ou t

hex

m xp

signal

- a

- m ap signal

- o signal

- boo to rg PA RALL EL

- e 0x100

- boo t

- m emw idth 16

-

romw idth 16

转换的文件名

输出文件A SC II- H EX 格式

生成的映射文件名

指定输出的引导装载表文件名

采用并行口BOO T 模式

程序运行的起始地址 0x100

将段转换为引导装载表方式

16 位存储器宽度

16 位 FLA SH

在命令行模式下执行命令行:

hex500 2hex

cm d

即可以得到 signal

件。 可以将生成的 signal

法写入到功能板的 FLA SH 存储器内部。

m xp 文件和Boo t 表 signal

hex 文

hex 通过在线 FLA SH 编程的方

图 4 主程序流程图

图 5 D SP 初始化子程序流程图

在线 FLA SH 编程是指通过仿真器和 J TA G 接口, 借

助D SP 芯片将Boo t 表写入 FLA SH 的过程。这个过程不需

要将 FLA SH 芯片从D SP 功能板上取下来, 使得修改和加

载程序代码更加方便, 系统的灵活性大大加强。 但在线

FLA SH 编程对整个系统有一定的要求, 即必须将 FLA SH

与D SP 芯片的并口或串口等数据通道引脚相连接。本功能

板 FLA SH 与D SP 芯片的并口相连接, 如图 2 所示。 依据

BOO TLOAD 的流程, 通过在线编程, 将 Boo t 表写入到

SST 39V F400A FLA SH 的 0x8000 开始的地址空间内, 并

修改数据空间 0xFFFF 地址单元中的值为 0x8000 (即Boo t

表地址)。在线编程成功后, 所设计的基于D SP 的信号发生

器就可以脱机运行, 成为一个独立的应用系统。

4 外部并行 8 位 FLASH 引导装载设计

5 结 语

TM S320V C5402 D SP 引导装载的目的, 是使系统上电

后程序代码能从外部存储器 (如 FLA SH , EPROM 等) 引

导装载到D SP 内部或者外部程序存储器中脱机运行。目标

系统板上采用了常用的高档 FLA SH 芯片 SST 39V F400A

来实现外部并行 16 位 BOO TLOAD , 具有代表性。 并行

BOO TLOAD 的流程是: V C5402 上电复位后, 当 IN T 2 和

IN T 3 没有中断触发, 且功能板工作在微计算机模式 (M P

M C = 0) 时, BOO TLOAD 程序首先读入外部数据存储器

FLA SH 的 0xFFFFH 地址, 当这个地址包含了有效的地址

内容 时, BOO TLOAD 程 序 将 该 地 址 中 的 内 容 当 作 是

FLA SH 中程序的首地址, 并从这个首地址开始读取数据并

复制到D SP 内部程序空间中去。FLA SH 中的程序是有规

律排列的, 称为Boo t 表, Boo t 表就是所有要下载到D SP 内

部程序空间的程序代码。Boo t 表由 TM S320C54x 的汇编语

基于D SP 的信号发生器充分利用了D SP 高速而精确

的运算能力以及内部操作极大的灵活性, 使得产生的信号

波形精度高、稳定性好, 编程简单、灵活, 在实际应用中取

得了很好的效果。

参 考 文 献

1 清源科技

TM S320C54x D SP 硬件开发教程 [M ]

北京:

2

机械工业出版社, 2003

TM S320C54x D SP R eference Set: CPU and Perip herals

(L iteratu re N um ber SPRU 131) [M ]

T exas In strum en ts

Inc, 1997, 1.

3 刘益成

TM S320C54x D SP 应用程序设计与开发 [M ]

北

4

京: 北京航空航天大学出版社, 2002

TM S320C54x O p tim izing C

[M ]

T EXA S In strum en ts Inc, 2001

C + + Com p iler U ser′s Gu ider

作者简介 刘剑科 男, 江苏常州人, 中国矿业大学硕士研究生。 主要从事信息处理方面的研究。

821

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc