Wm8960 ,三星平台 s5pv210 移植记录 (本记录参考记录来源于网络)

S5pv210 支持 iis5.1 版本协议

Cpu 端

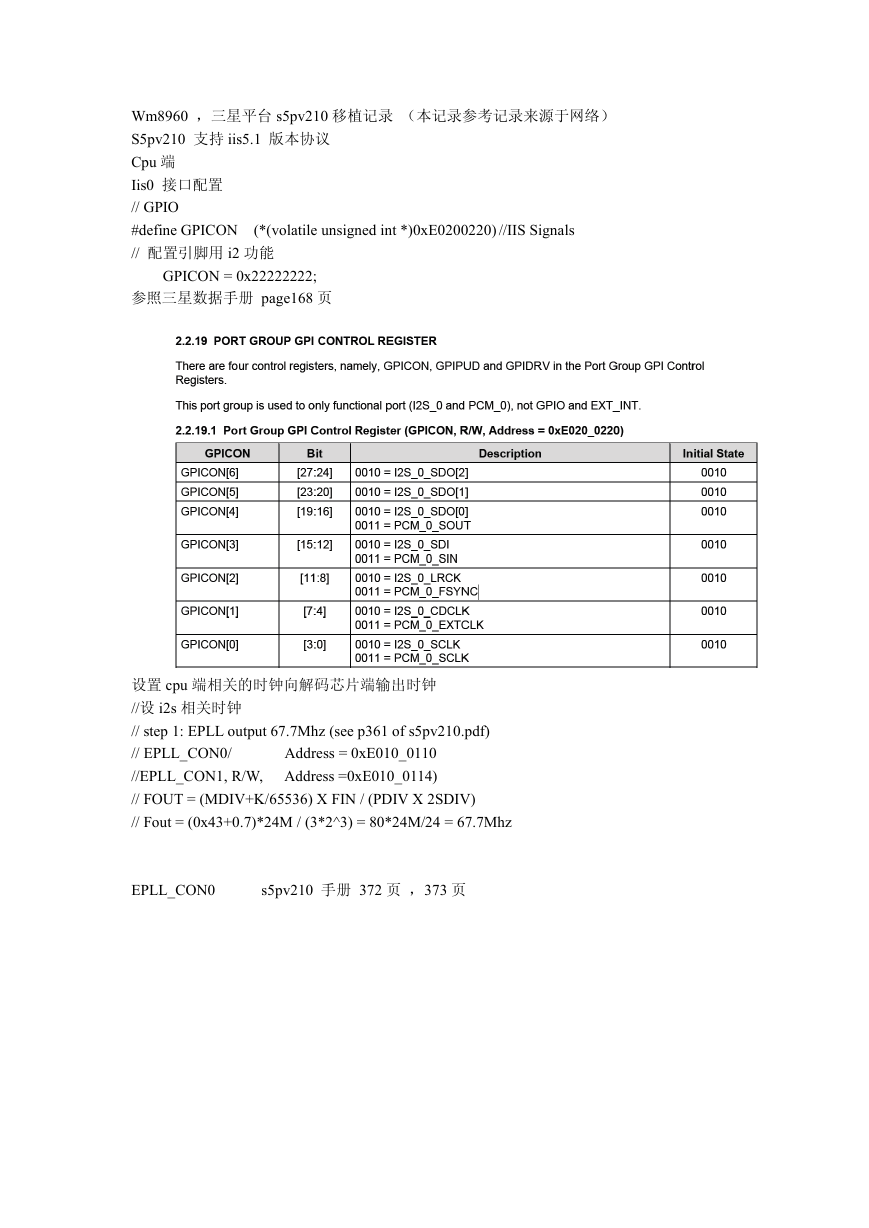

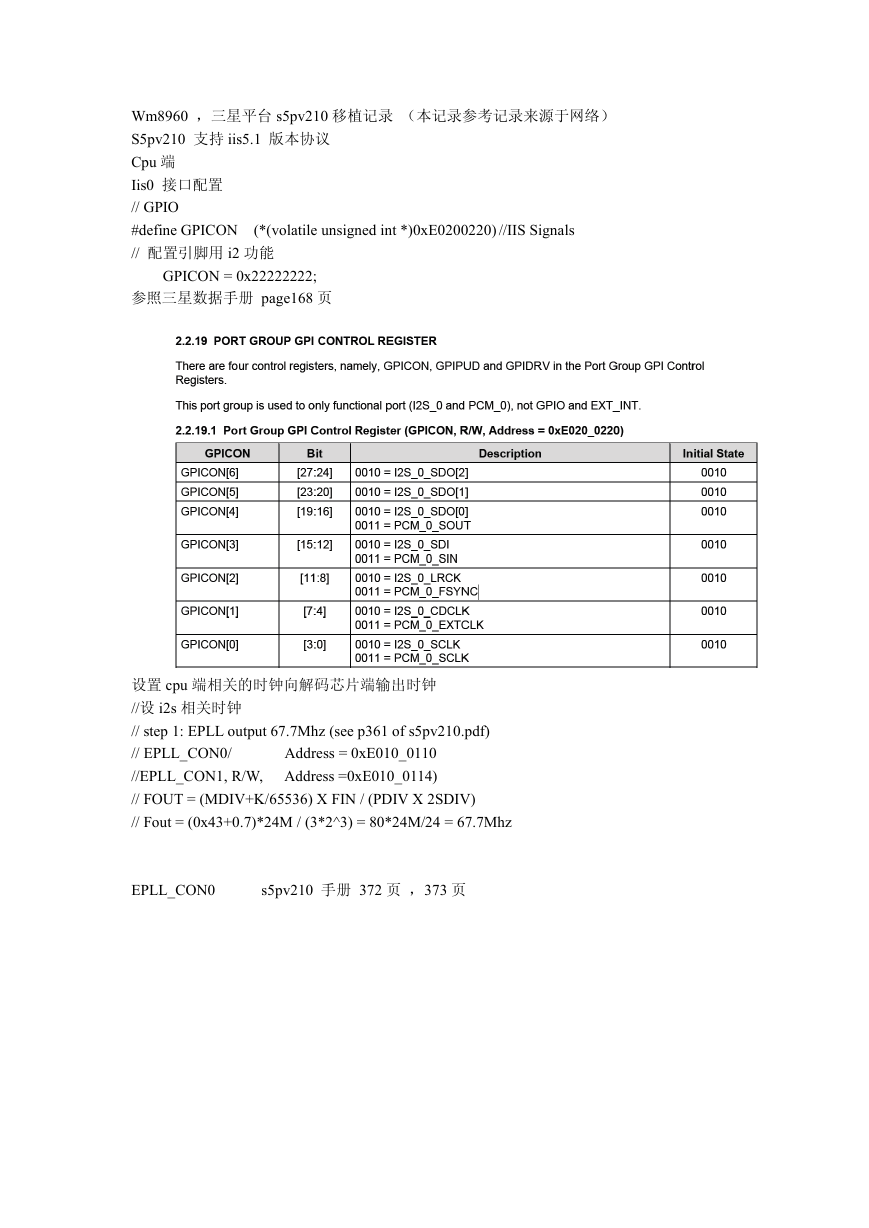

Iis0 接口配置

// GPIO

#define GPICON (*(volatile unsigned int *)0xE0200220) //IIS Signals

// 配置引脚用 i2 功能

GPICON = 0x22222222;

参照三星数据手册 page168 页

设置 cpu 端相关的时钟向解码芯片端输出时钟

//设 i2s 相关时钟

// step 1: EPLL output 67.7Mhz (see p361 of s5pv210.pdf)

// EPLL_CON0/

Address = 0xE010_0110

//EPLL_CON1, R/W, Address =0xE010_0114)

// FOUT = (MDIV+K/65536) X FIN / (PDIV X 2SDIV)

// Fout = (0x43+0.7)*24M / (3*2^3) = 80*24M/24 = 67.7Mhz

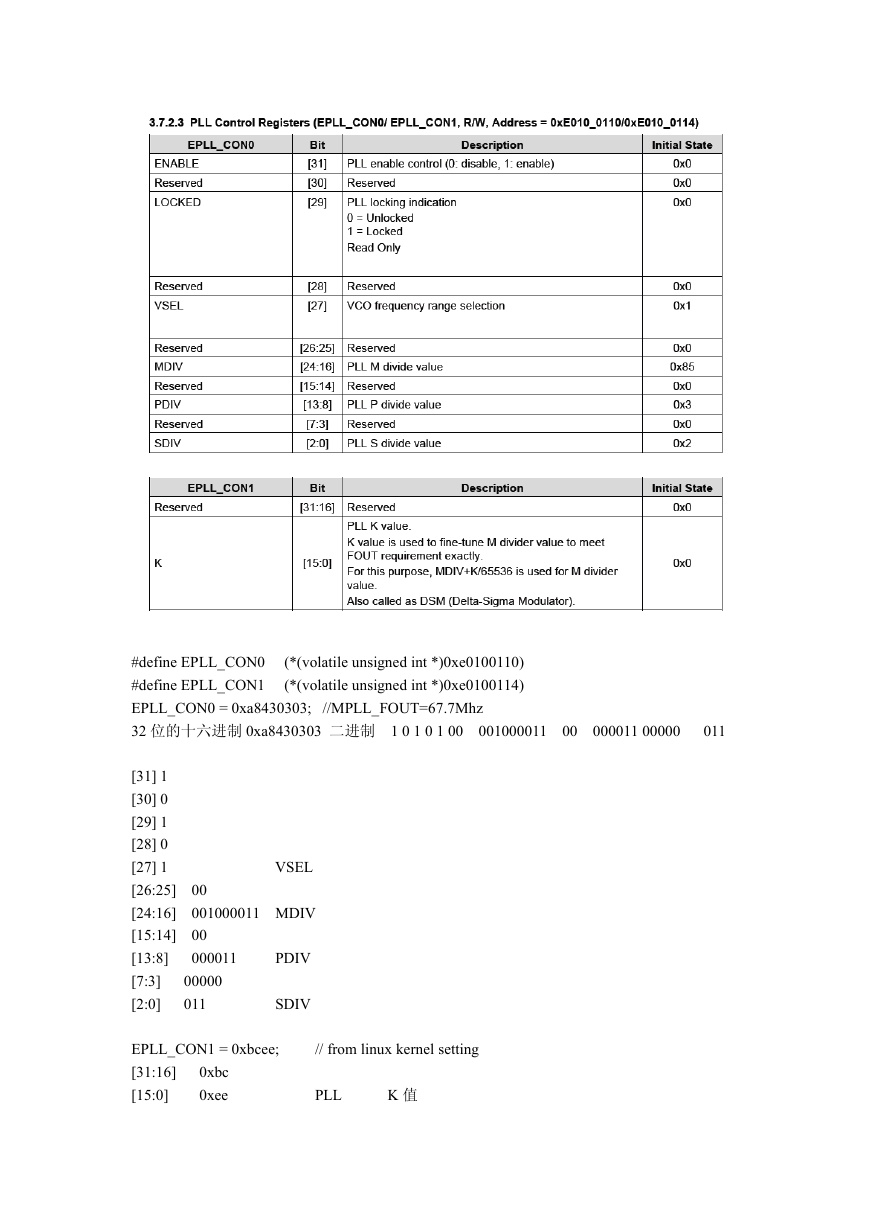

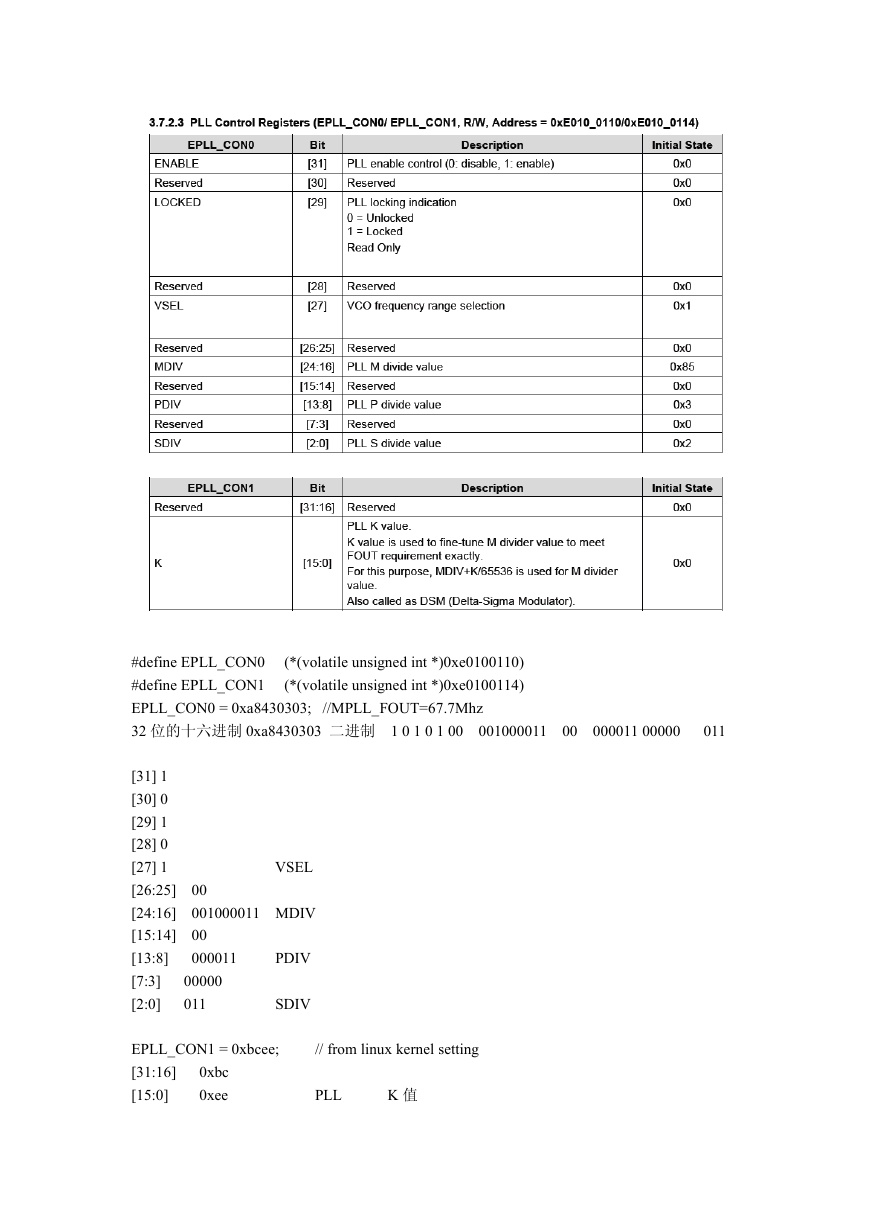

EPLL_CON0

s5pv210 手册 372 页 ,373 页

�

#define EPLL_CON0

#define EPLL_CON1

EPLL_CON0 = 0xa8430303;

32 位的十六进制 0xa8430303 二进制 1 0 1 0 1 00

(*(volatile unsigned int *)0xe0100110)

(*(volatile unsigned int *)0xe0100114)

//MPLL_FOUT=67.7Mhz

001000011 00

000011 00000

011

[31] 1

[30] 0

[29] 1

[28] 0

[27] 1

[26:25]

[24:16]

[15:14]

[13:8]

[7:3]

[2:0]

VSEL

00

001000011 MDIV

00

000011

00000

011

PDIV

SDIV

EPLL_CON1 = 0xbcee;

[31:16]

[15:0]

0xbc

0xee

// from linux kernel setting

PLL

K 值

�

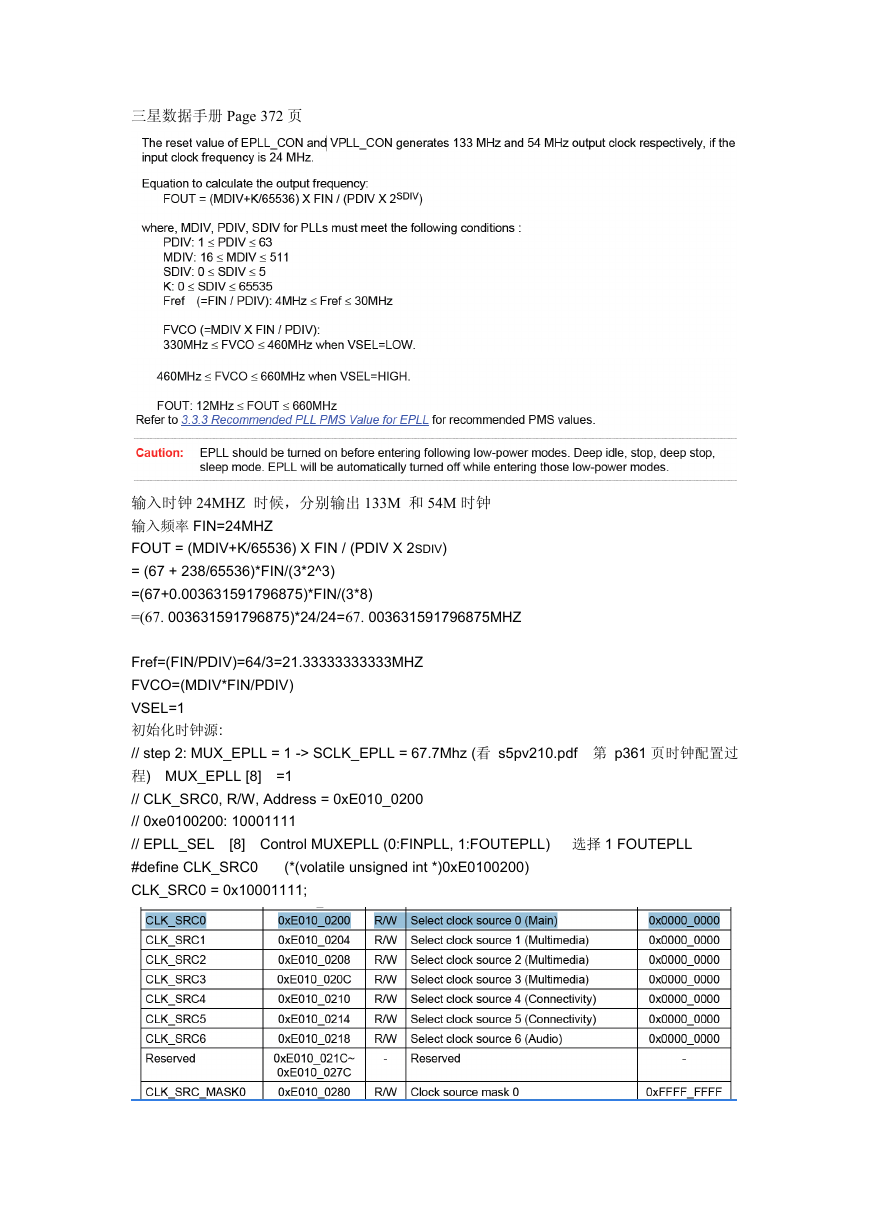

三星数据手册 Page 372 页

输入时钟 24MHZ 时候,分别输出 133M 和 54M 时钟

输入频率 FIN=24MHZ

FOUT = (MDIV+K/65536) X FIN / (PDIV X 2SDIV)

= (67 + 238/65536)*FIN/(3*2^3)

=(67+0.003631591796875)*FIN/(3*8)

=(67. 003631591796875)*24/24=67. 003631591796875MHZ

Fref=(FIN/PDIV)=64/3=21.33333333333MHZ

FVCO=(MDIV*FIN/PDIV)

VSEL=1

初始化时钟源:

// step 2: MUX_EPLL = 1 -> SCLK_EPLL = 67.7Mhz (看 s5pv210.pdf 第 p361 页时钟配置过

程) MUX_EPLL [8] =1

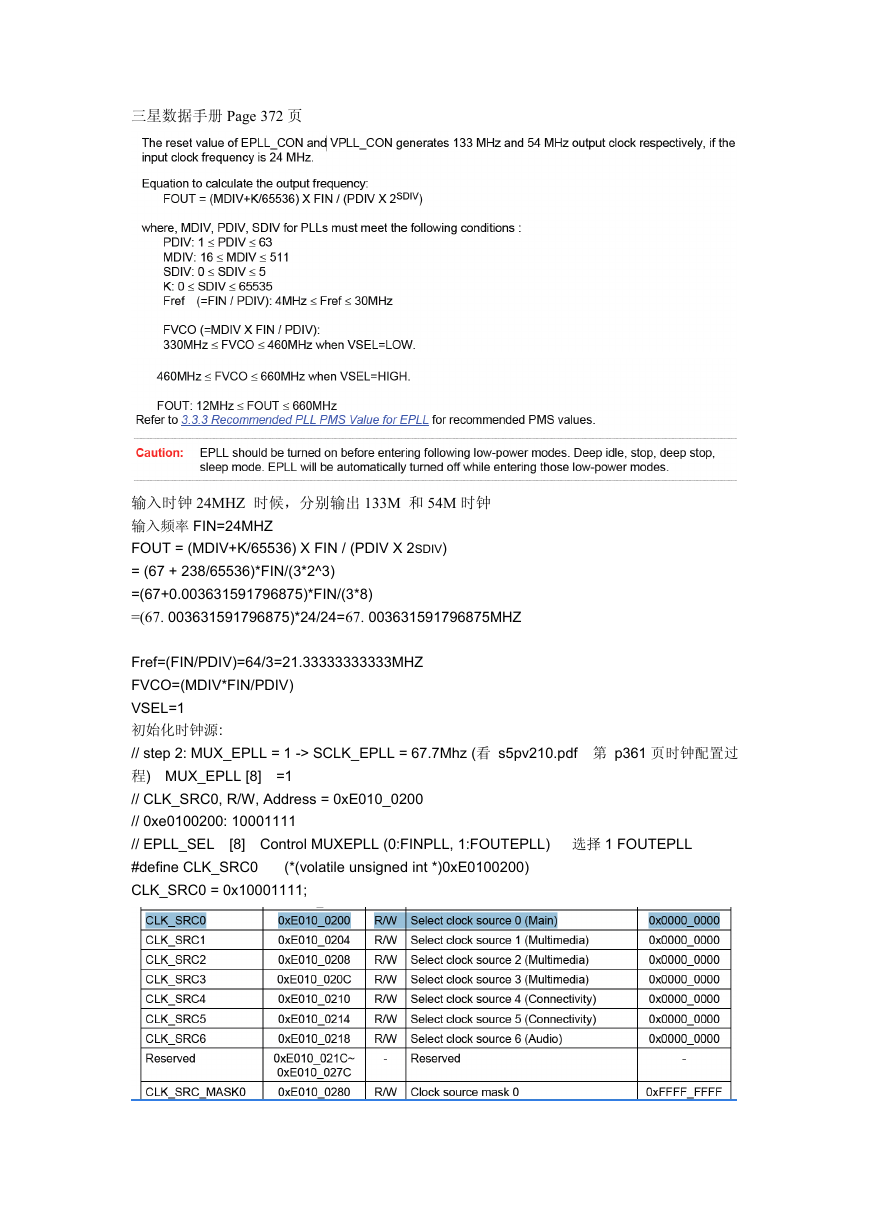

// CLK_SRC0, R/W, Address = 0xE010_0200

// 0xe0100200: 10001111

// EPLL_SEL [8] Control MUXEPLL (0:FINPLL, 1:FOUTEPLL) 选择 1 FOUTEPLL

#define CLK_SRC0

CLK_SRC0 = 0x10001111;

(*(volatile unsigned int *)0xE0100200)

�

HCLK_DSYS

SCLKMPLL

FOUTVPLL

1 VPLL_SEL=

ONENAND_SEL

0 MUX_PSYS=

000

0 MUX_D_SYS_SEL= SCLKMPLL

000

0 MUX_MSYS_SEL= SCLKAPLL

000

CLK_SRC0 = 0x10001111;

2 进制=10000000000000001000100010001

[28] 1

[27:25] 000

[24]

[23:21]

[20]

[19:17]

[16]

[15:13]

[12]

[11:9] 000

[8] 1

[7:5] 000

[4] 1 MPLL_SEL=

[3:1] 000

APLL_SEL =

[0] 1

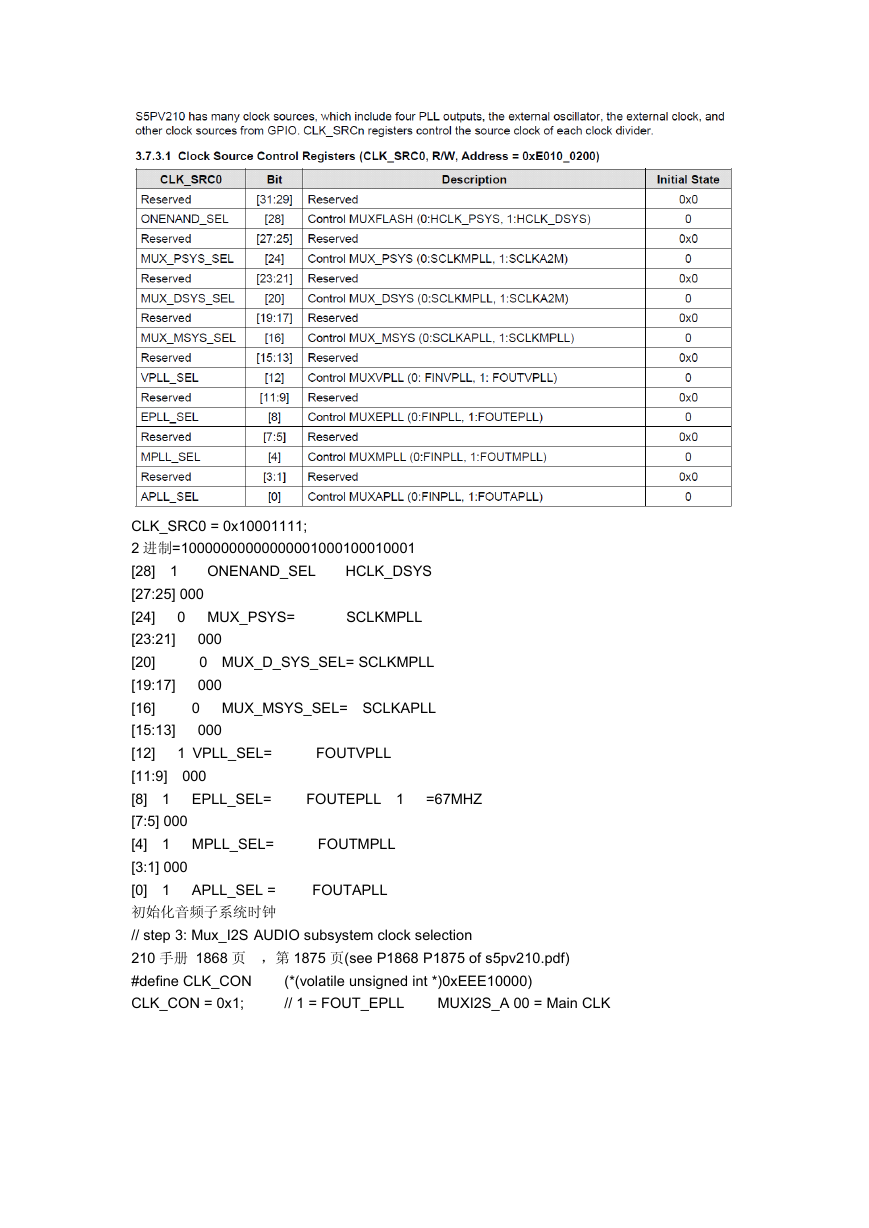

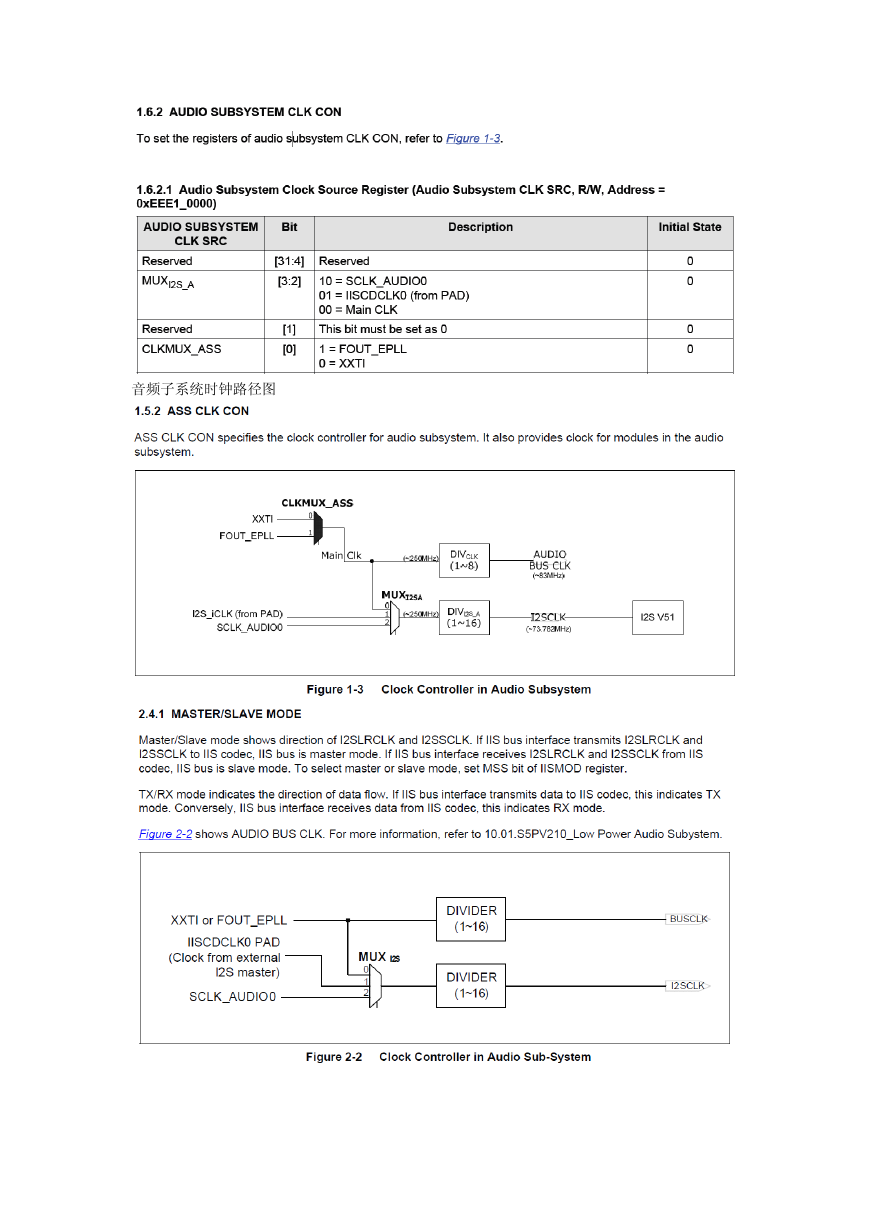

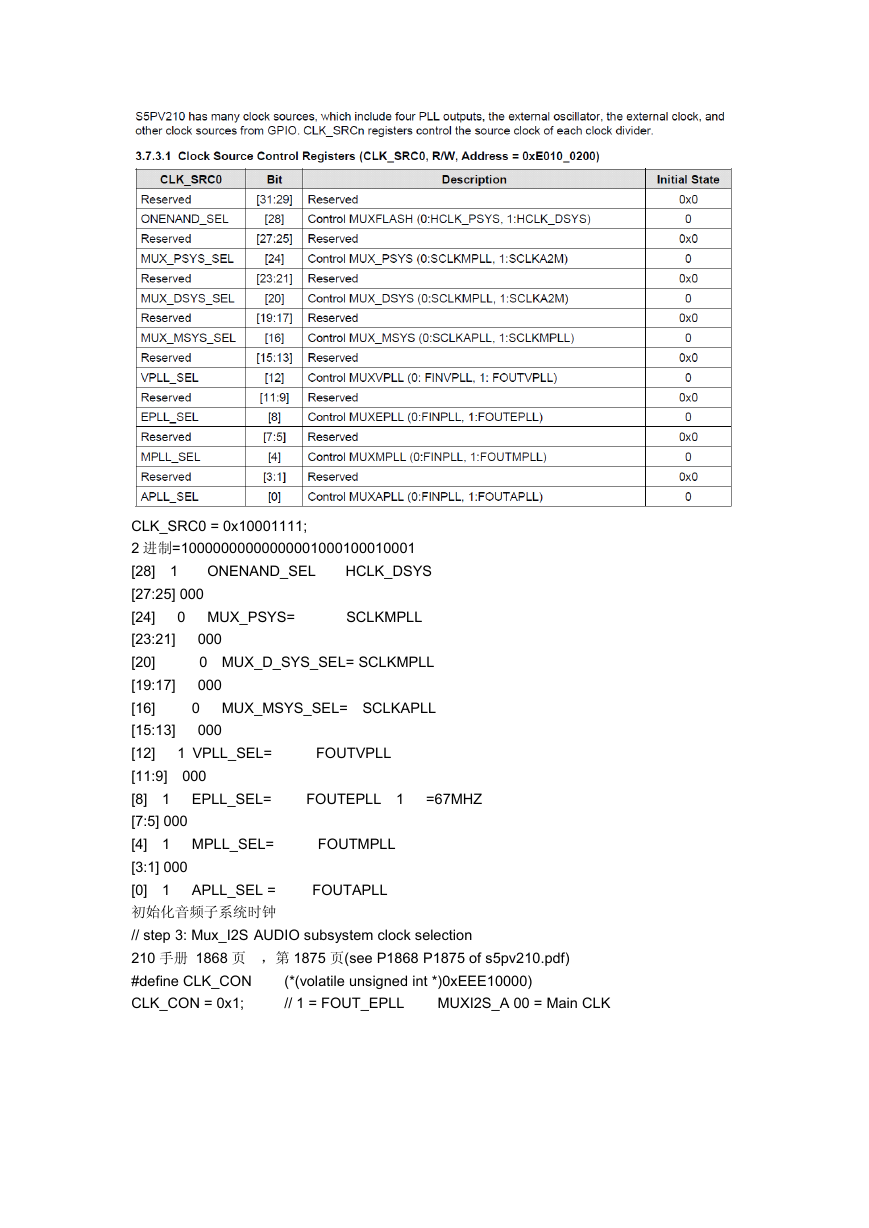

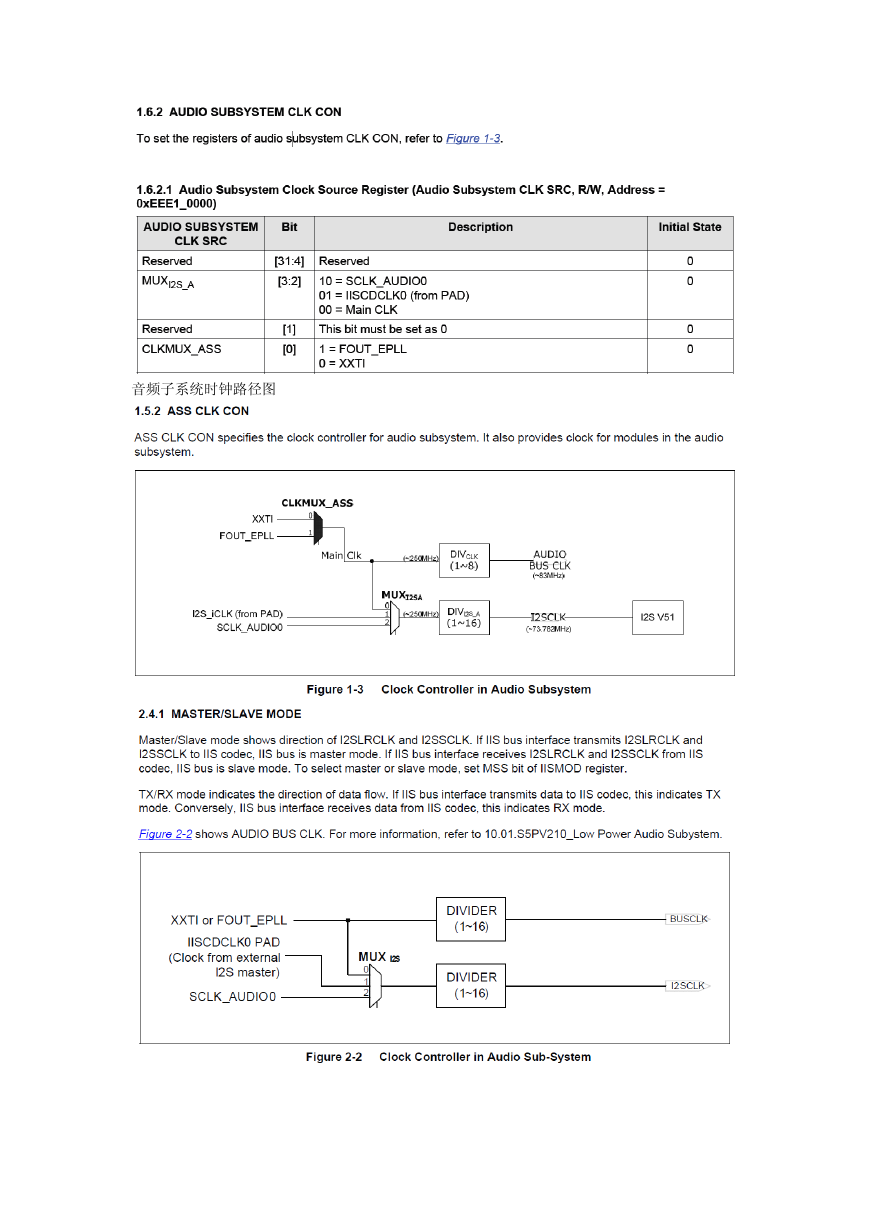

初始化音频子系统时钟

// step 3: Mux_I2S AUDIO subsystem clock selection

210 手册 1868 页 ,第 1875 页(see P1868 P1875 of s5pv210.pdf)

#define CLK_CON

CLK_CON = 0x1;

EPLL_SEL=

FOUTEPLL 1

=67MHZ

FOUTMPLL

FOUTAPLL

(*(volatile unsigned int *)0xEEE10000)

// 1 = FOUT_EPLL

MUXI2S_A 00 = Main CLK

�

音频子系统时钟路径图

�

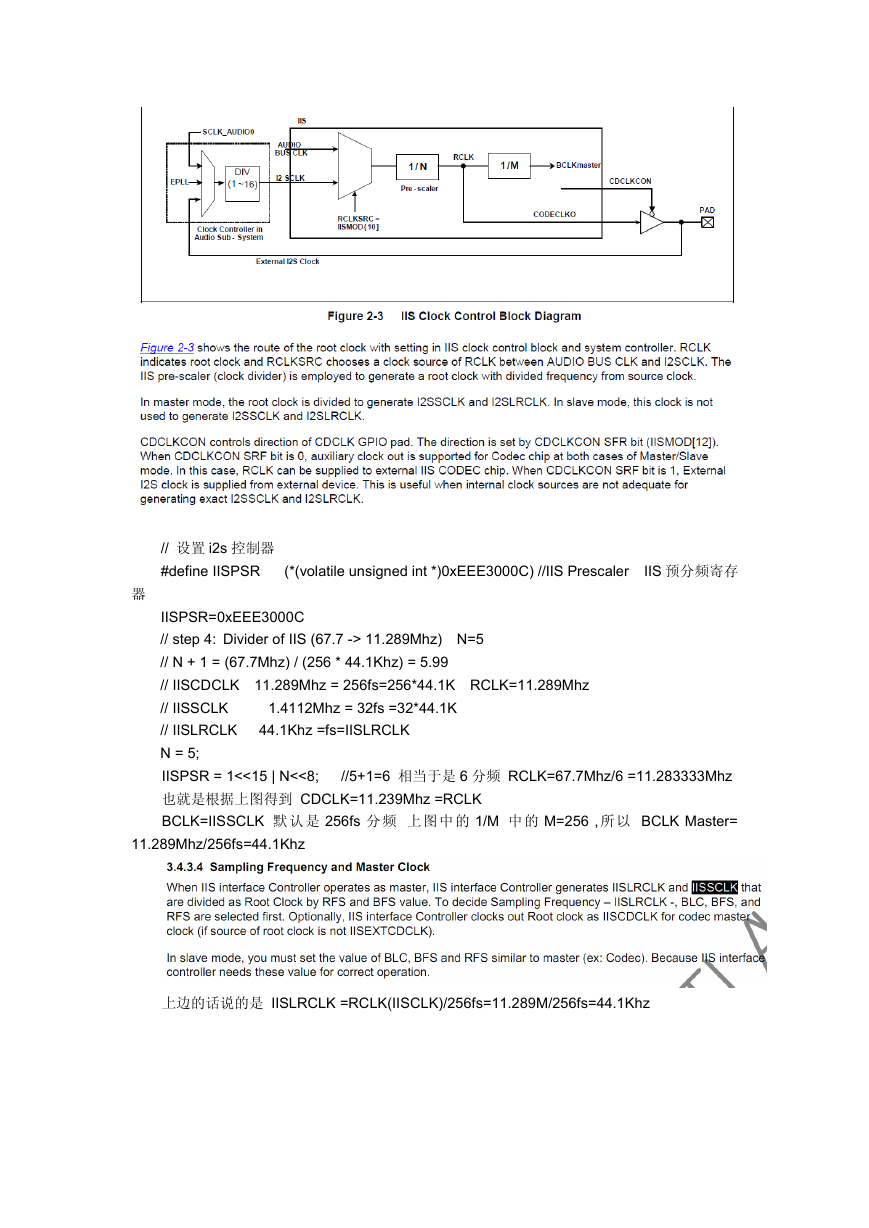

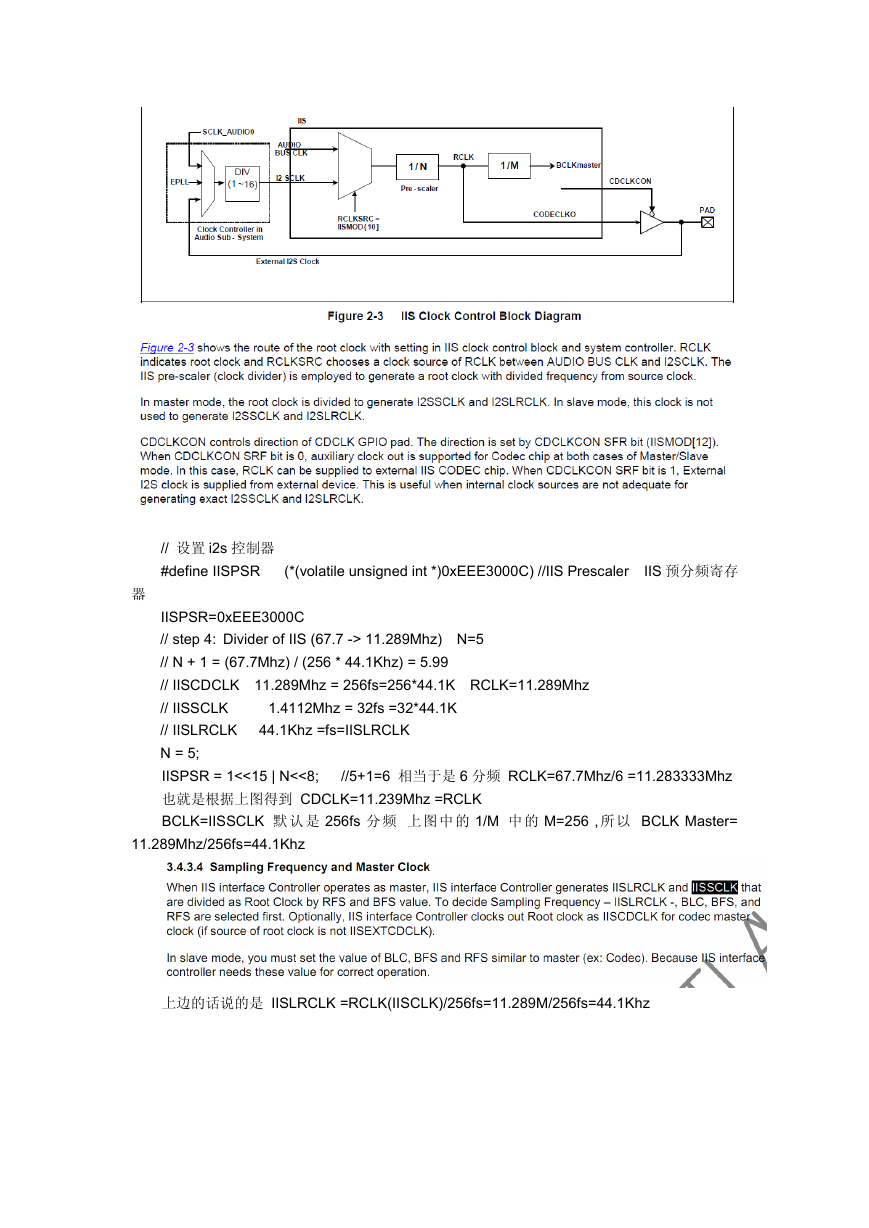

// 设置 i2s 控制器

#define IISPSR

器

(*(volatile unsigned int *)0xEEE3000C) //IIS Prescaler

IIS 预分频寄存

IISPSR=0xEEE3000C

// step 4: Divider of IIS (67.7 -> 11.289Mhz) N=5

// N + 1 = (67.7Mhz) / (256 * 44.1Khz) = 5.99

// IISCDCLK 11.289Mhz = 256fs=256*44.1K RCLK=11.289Mhz

// IISSCLK

// IISLRCLK

N = 5;

IISPSR = 1<<15 | N<<8;

也就是根据上图得到 CDCLK=11.239Mhz =RCLK

BCLK=IISSCLK 默 认 是 256fs 分 频 上 图 中 的 1/M 中 的 M=256 , 所 以 BCLK Master=

1.4112Mhz = 32fs =32*44.1K

44.1Khz =fs=IISLRCLK

//5+1=6 相当于是 6 分频 RCLK=67.7Mhz/6 =11.283333Mhz

11.289Mhz/256fs=44.1Khz

上边的话说的是 IISLRCLK =RCLK(IISCLK)/256fs=11.289M/256fs=44.1Khz

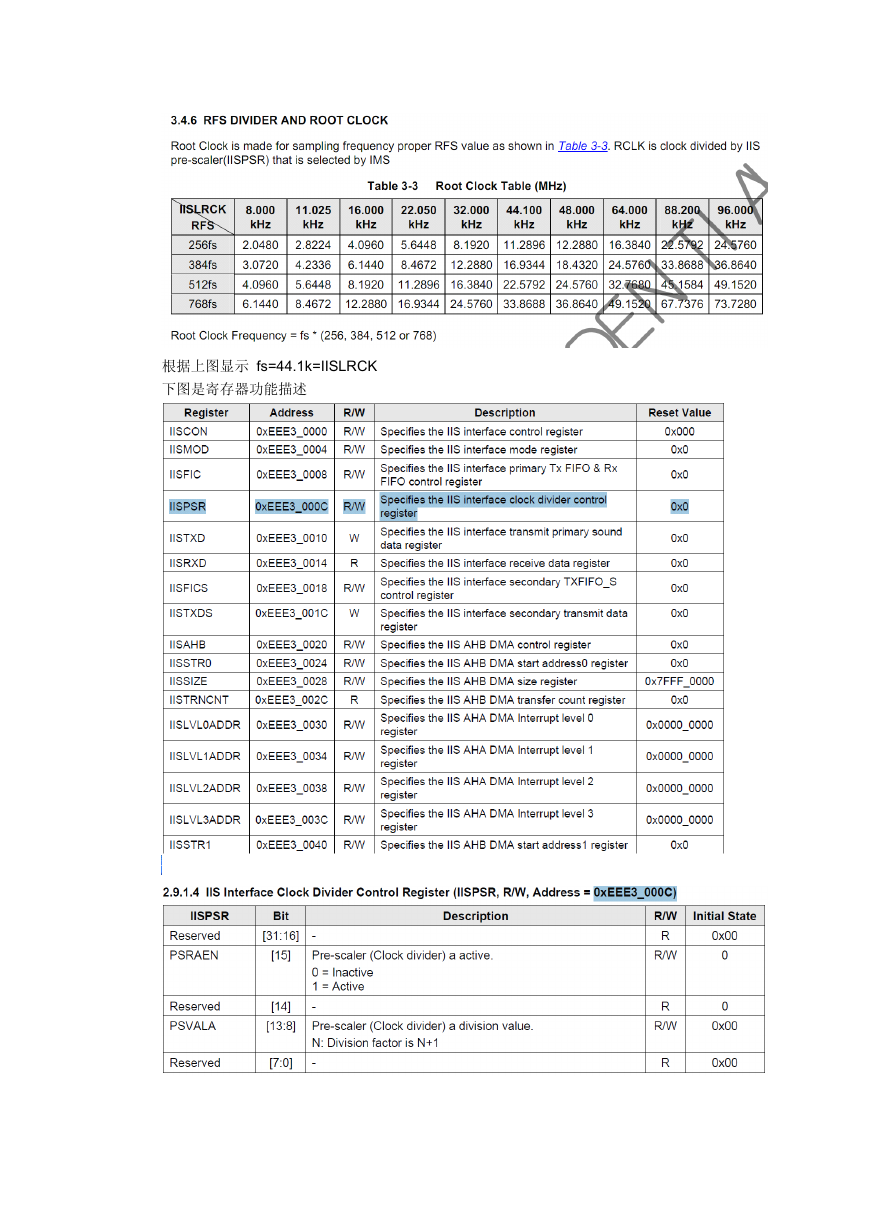

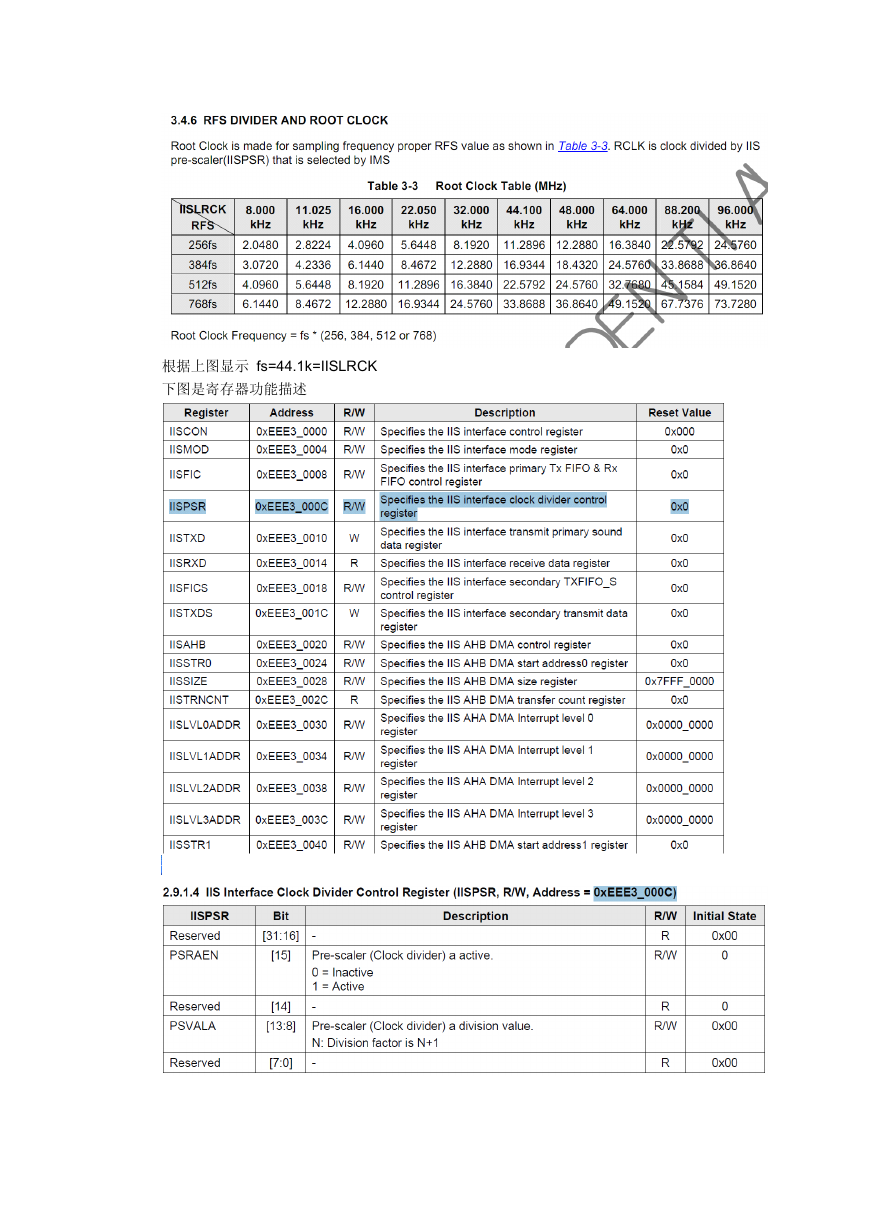

�

根据上图显示 fs=44.1k=IISLRCK

下图是寄存器功能描述

�

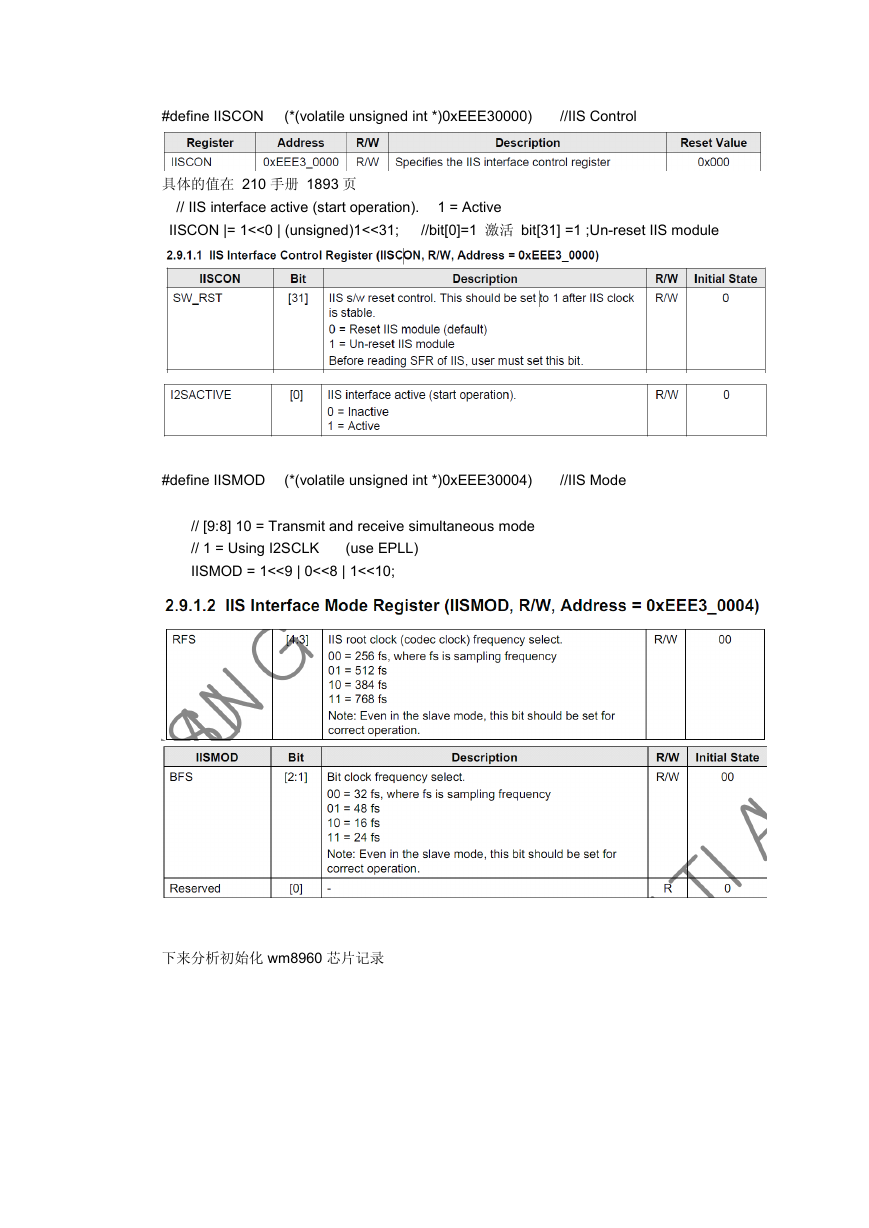

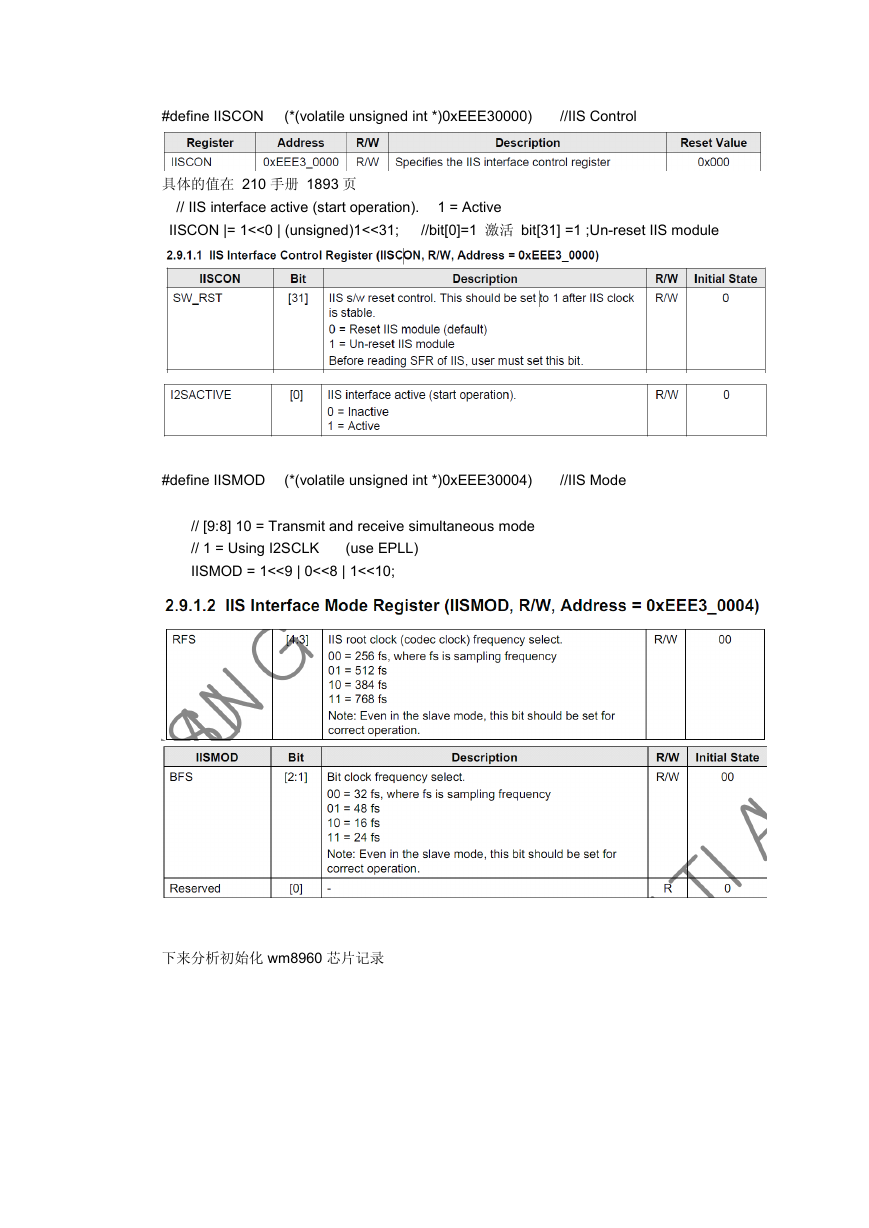

#define IISCON (*(volatile unsigned int *)0xEEE30000)

//IIS Control

具体的值在 210 手册 1893 页

// IIS interface active (start operation).

IISCON |= 1<<0 | (unsigned)1<<31;

1 = Active

//bit[0]=1 激活 bit[31] =1 ;Un-reset IIS module

#define IISMOD (*(volatile unsigned int *)0xEEE30004)

//IIS Mode

// [9:8] 10 = Transmit and receive simultaneous mode

// 1 = Using I2SCLK

IISMOD = 1<<9 | 0<<8 | 1<<10;

(use EPLL)

下来分析初始化 wm8960 芯片记录

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc