06 级计算机科学与技术 班 姓名:

2009/1/15

华 北 科 技 学 院

课程设计说明书

计算机 B06

沈旭辉

200607014223

班级:

姓名:

学号:

设计题目:TEC-2000A 汇编指令设计及验证

设计时间: ___2008-12-22 至 2009-1-15

指导教师: 席振元、余生晨、赵竞雄、邵铁军

语:_______________________________

________________________________________

________________________________________

________________________________________

________________________________________

评阅成绩:___________评阅教师: ___________

评

1

�

06 级计算机科学与技术 班 姓名:

2009/1/15

课程设计报告

1. 课程设计目的

通过对《计算机组成原理》的课程设计,进一步熟练掌握计算机各功能部

件的内部构造和相互之间的联系(部件配置、相互连接和作用)、各功能部件的

性能参数的相互匹配、机器指令级的各种功能和特性。将所学知识融会贯通、进

一步系统化,进一步提高硬件系统设计的能力,为以后更高的一级硬件设计打下

坚实基础。

2. 课程设计任务

在现有的 TEC-2000 教学机系统上,扩展 2 条 CPU 的机器指令,并在系

统监控程序中扩充相应的汇编指令,使软硬件均支持扩展的指令。

3. 系统组成原理及实现

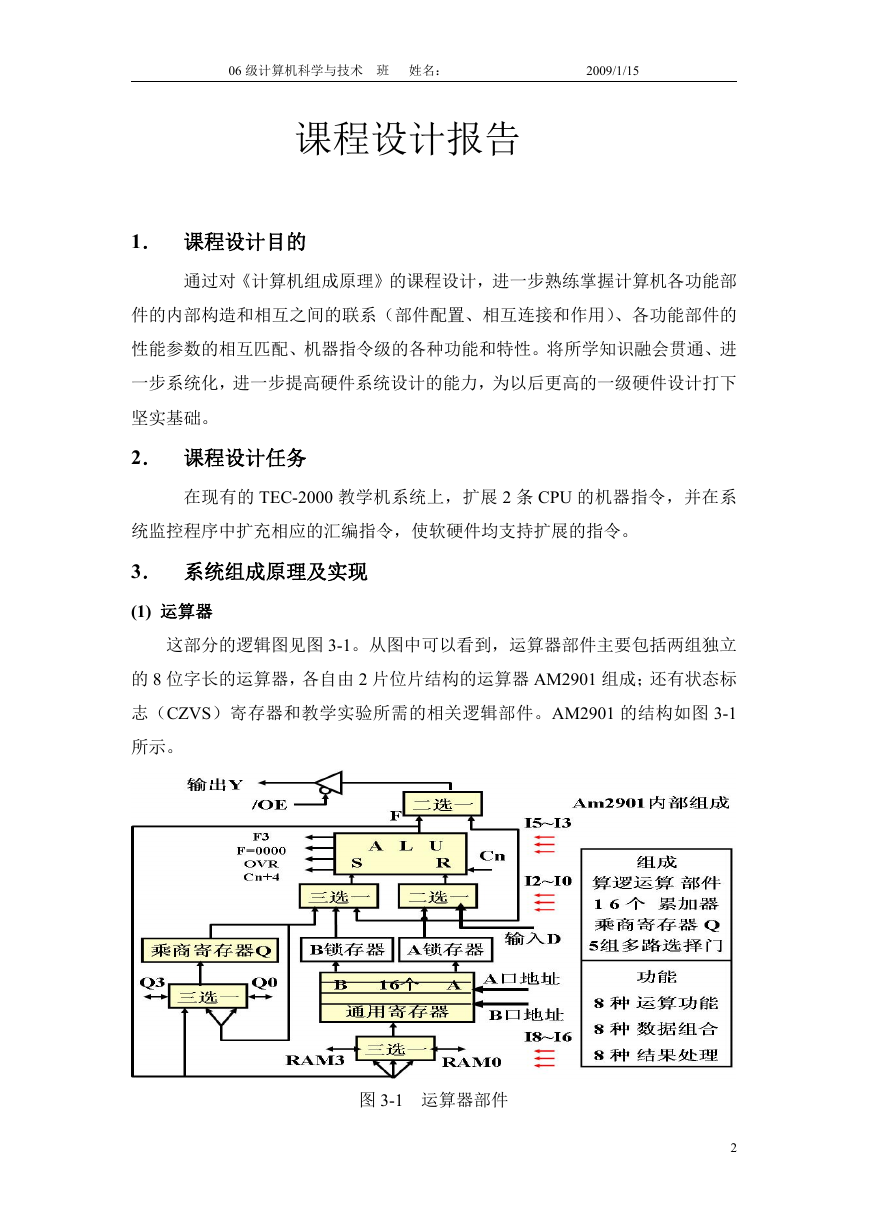

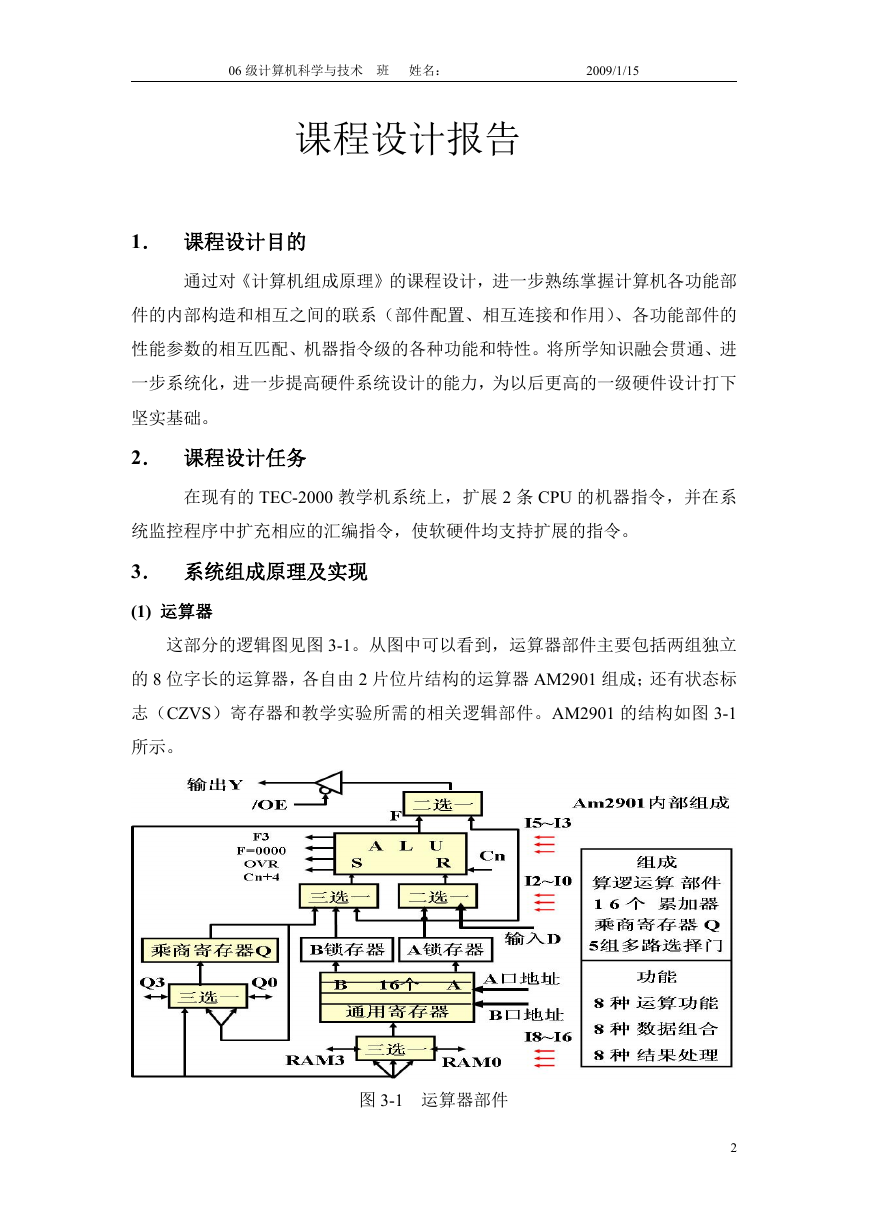

(1) 运算器

这部分的逻辑图见图 3-1。从图中可以看到,运算器部件主要包括两组独立

的 8 位字长的运算器,各自由 2 片位片结构的运算器 AM2901 组成;还有状态标

志(CZVS)寄存器和教学实验所需的相关逻辑部件。AM2901 的结构如图 3-1

所示。

图 3-1 运算器部件

2

�

06 级计算机科学与技术 班 姓名:

2009/1/15

十六位教学机运算器的设计与实现:

十六位教学机的运算器是用 4 片 AM2901 芯片组成的,最低位芯片的

RAMO 与 Q0 是该 16 位的运算器的最低位的移位入/出信号,最高位芯片的

RAM3 与 Q3 是 16 位的运算器最高位的移为入/出信号,它们通过短路子与

SHIFT GAL 相连。

最低位芯片的 CN 是整个 16 位运算器的最低位进位输入信号,最高位芯片

的 CN+4 是整个 16 位运算器的最低位进位输入信号,它们通过短路子与 SHIFT

GAL 相连。同理,只有最高位芯片的 F3 和 OVR 有意义,低位的三个芯片的

F3 和 OVR 不被使用。

B55

~

微下地址

B40

B39

~

B48

B32

SCC3~0

0/MIO/REQ/WE 0

I2~I0

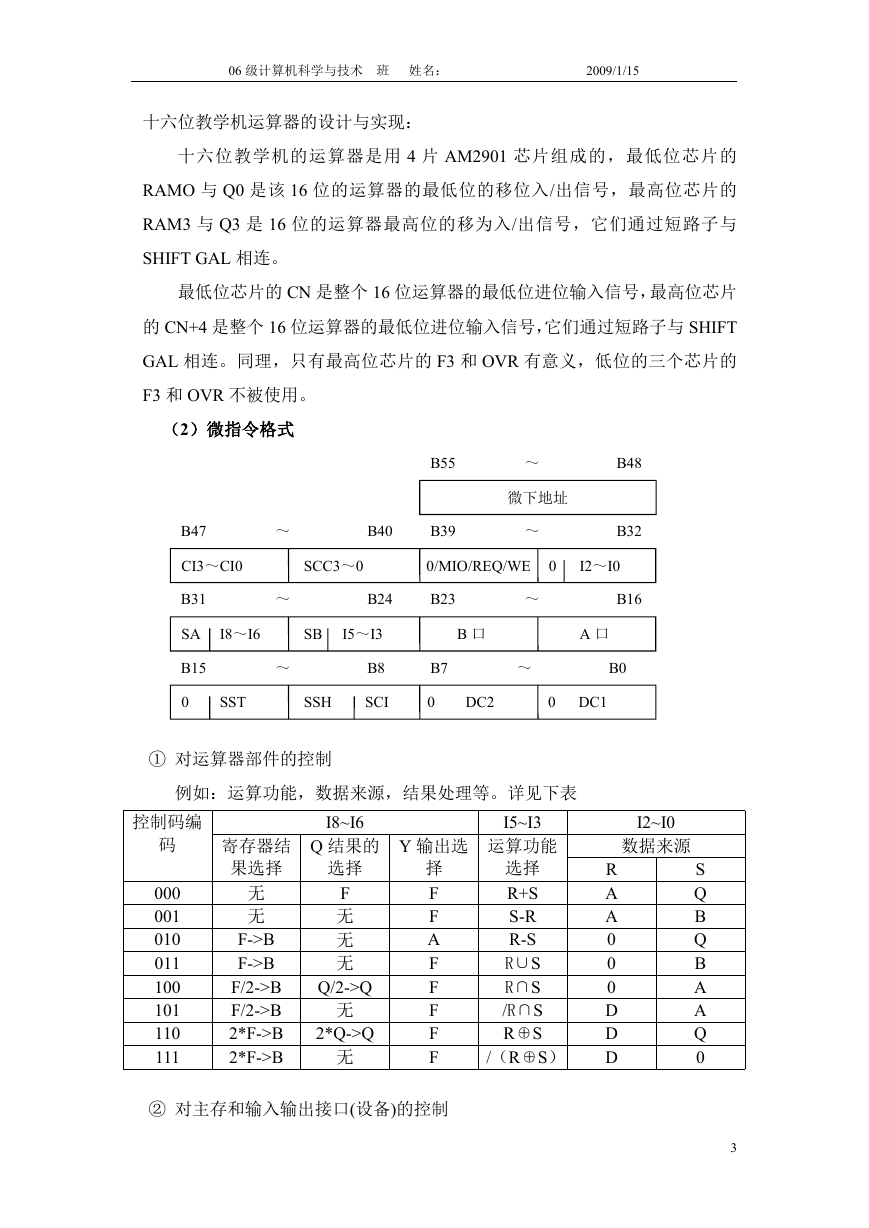

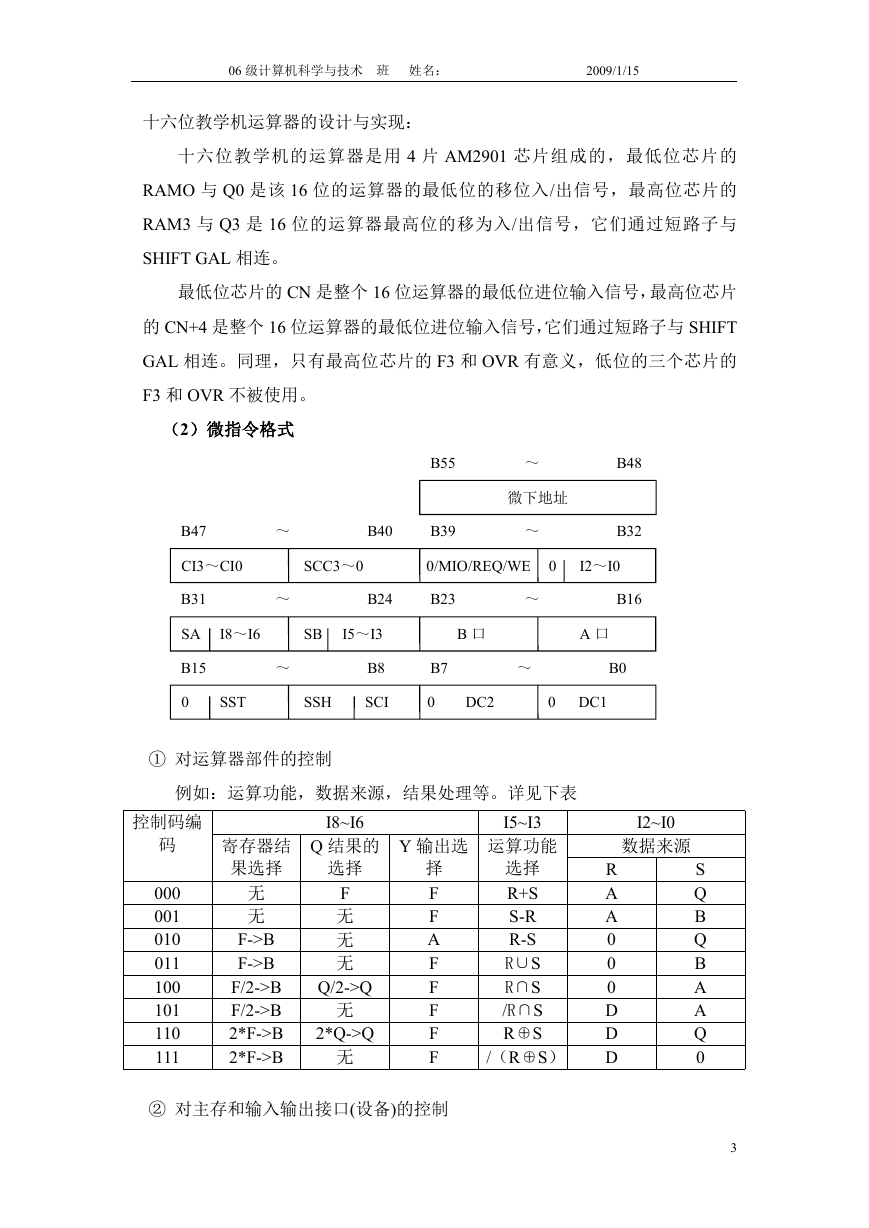

(2)微指令格式

B47

CI3~CI0

B31

SA I8~I6

B15

~

~

~

0

SST

SSH

① 对运算器部件的控制

B24

B23

SB I5~I3

B 口

~

~

B16

A 口

B0

B8

SCI

B7

0

DC2

0

DC1

I2~I0

数据来源

例如:运算功能,数据来源,结果处理等。详见下表

控制码编

码

000

001

010

011

100

101

110

111

寄存器结

果选择

无

无

F->B

F->B

F/2->B

F/2->B

2*F->B

2*F->B

I8~I6

Q 结果的

选择

F

无

无

无

Q/2->Q

无

2*Q->Q

无

Y 输出选

I5~I3

运算功能

择

F

F

A

F

F

F

F

F

选择

R+S

S-R

R-S

R∪S

R∩S

/R∩S

R⊕S

/(R⊕S)

R

A

A

0

0

0

D

D

D

② 对主存和输入输出接口(设备)的控制

S

Q

B

Q

B

A

A

Q

0

3

�

06 级计算机科学与技术 班 姓名:

2009/1/15

例如: 是主存读、写还是入出设备读、写

对内存和 I/O 接口的读写

/MIO(0:有内存或串口读写 1:无)

REQ(0:读写内存 1:读写穿行口)

/WE(0:写操作 1:读操作)

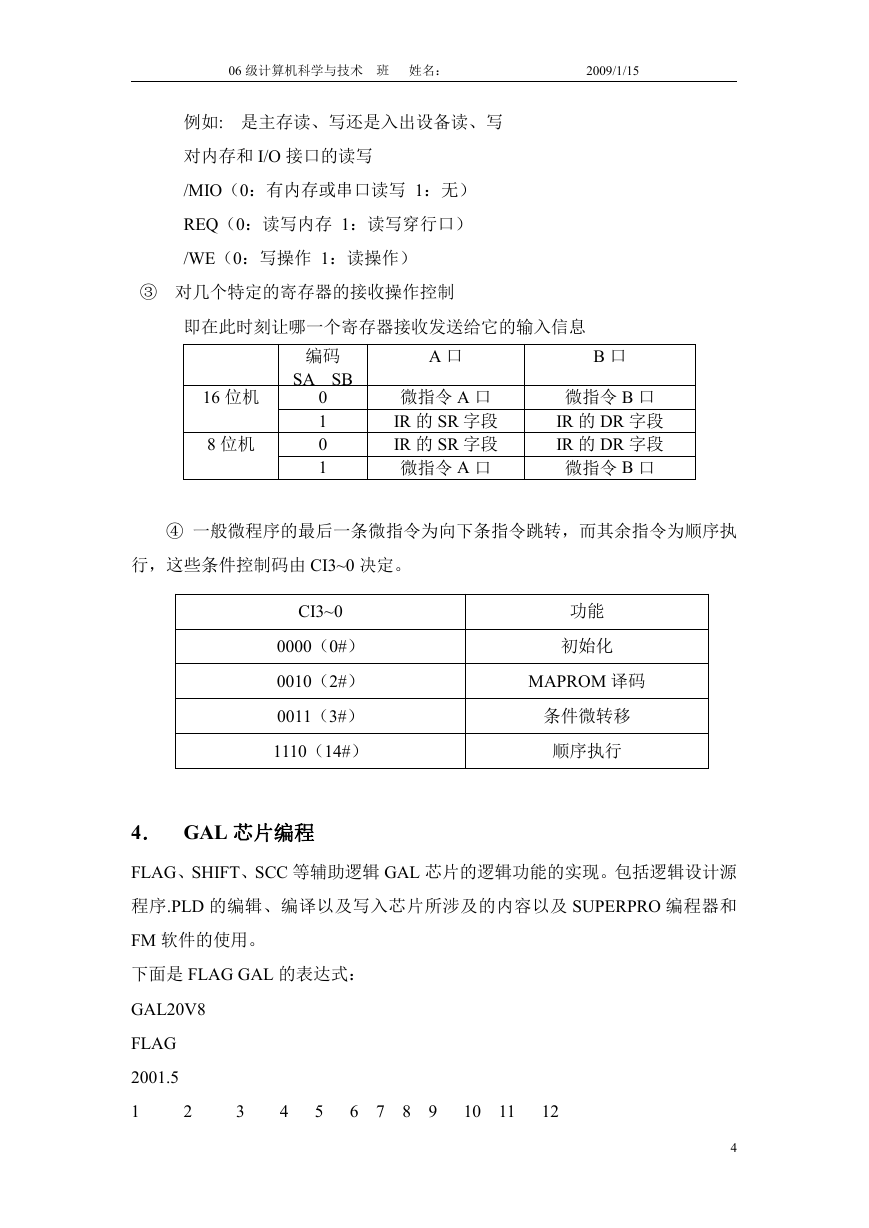

③ 对几个特定的寄存器的接收操作控制

即在此时刻让哪一个寄存器接收发送给它的输入信息

16 位机

8 位机

编码

SA SB

0

1

0

1

A 口

B 口

微指令 A 口

IR 的 SR 字段

IR 的 SR 字段

微指令 A 口

微指令 B 口

IR 的 DR 字段

IR 的 DR 字段

微指令 B 口

④ 一般微程序的最后一条微指令为向下条指令跳转,而其余指令为顺序执

行,这些条件控制码由 CI3~0 决定。

CI3~0

0000(0#)

0010(2#)

0011(3#)

1110(14#)

功能

初始化

MAPROM 译码

条件微转移

顺序执行

4. GAL 芯片编程

FLAG、SHIFT、SCC 等辅助逻辑 GAL 芯片的逻辑功能的实现。包括逻辑设计源

程序.PLD 的编辑、编译以及写入芯片所涉及的内容以及 SUPERPRO 编程器和

FM 软件的使用。

下面是 FLAG GAL 的表达式:

GAL20V8

FLAG

2001.5

1

10

12

6

7

8

9

11

2

3

4

5

4

�

06 级计算机科学与技术 班 姓名:

2009/1/15

CLK SST2 SST1 SST0 IB7 IB6 IB5 IB4 CY ZR OV GND

F3 NC CO C Z V S Q0 RAM0 RAM3 VCC

OE

C0 :=CY

C :=/SST2*/SST1*/SST0*C

+/SST2*/SST1*SST0*CY

+/SST2*SST1*/SST0*IB7

+ SST2*/SST1*/SST0

+ SST2*/SST1* SST0*RAM0

+SST2*SST1*/SST0*RAM3

+SST2*SST1*SST0*Q0

Z := /SST2*/SST1*/SST0*Z

+/SST2*/SST1*SST0*ZR

+/SST2*SST1*/SST0*IB6

+ /SST2*SST1*SST0*Z

+SST2*Z

V := /SST2*/SST1*/SST0*V

+/SST2*/SST1*SST0*OV

+/SST2*SST1*/SST0*IB5

+/ SST2*SST1*SST0*V

+SST2*Z

S := /SST2*/SST1*/SST0*S

+/SST2*/SST1*SST0*F3

+/SST2*SST1*/SST0*IB4

+ /SST2*SST1*SST0*S

+SST2*S

DESCRIPTION

生成 PLD 文件以后再用 FM 进行编译生成 JED 文件就可写入 GAL 芯片了 。

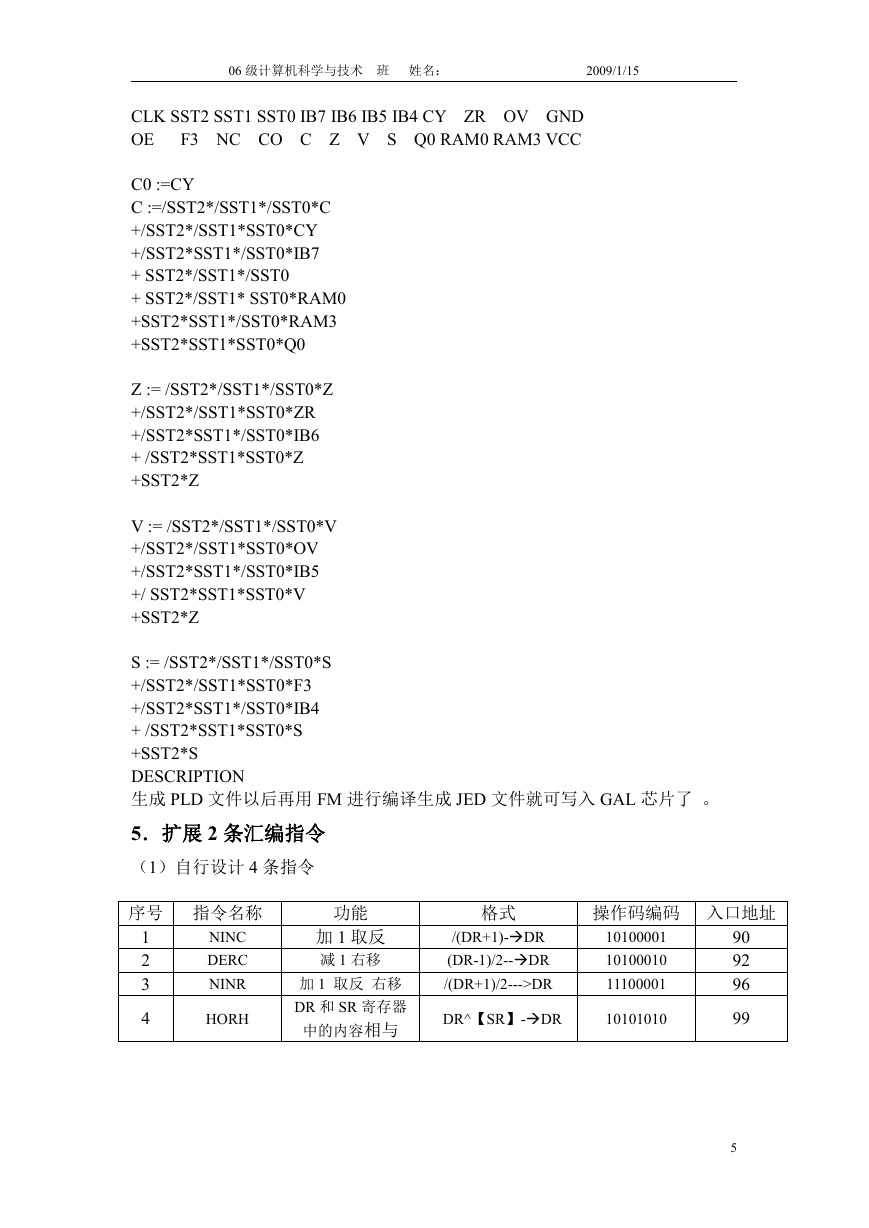

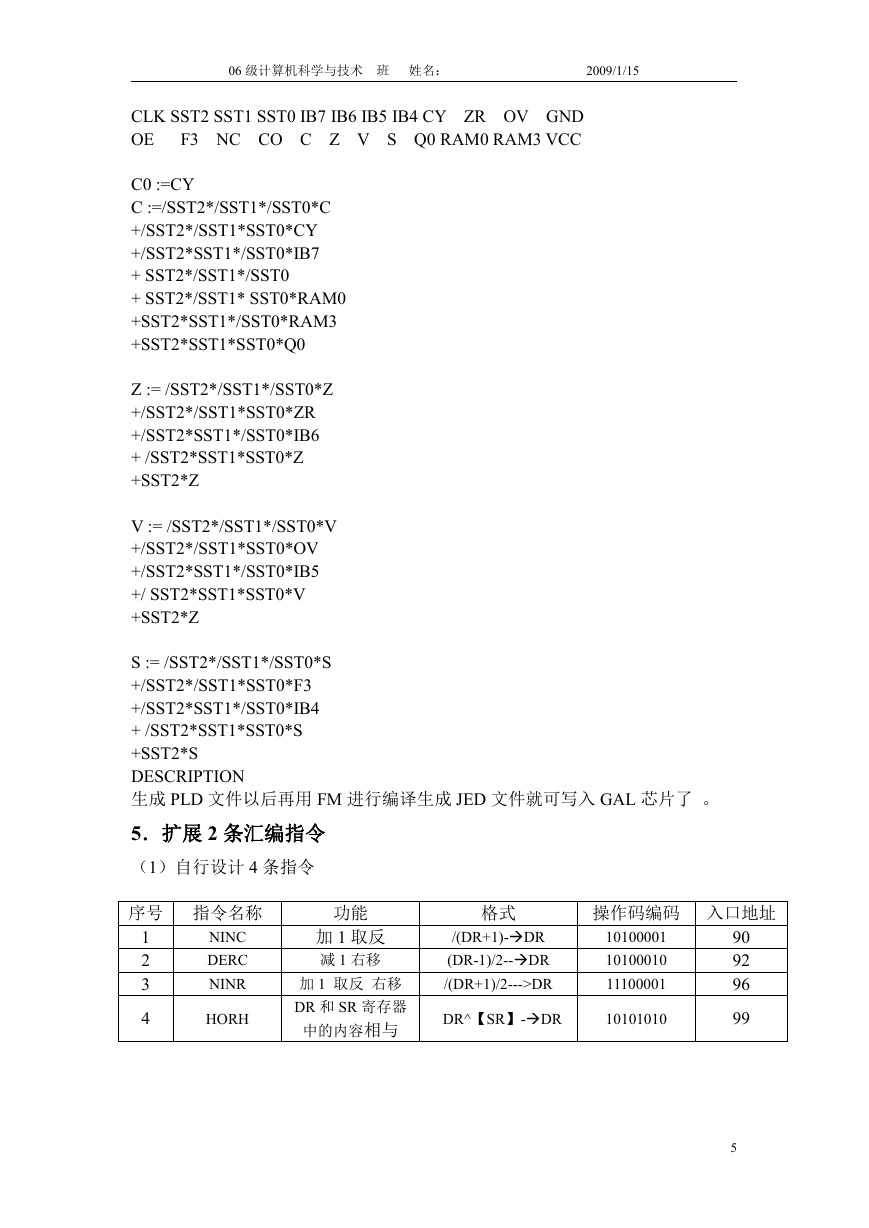

5.扩展 2 条汇编指令

(1)自行设计 4 条指令

序号 指令名称

1

2

3

4

NINC

DERC

NINR

HORH

功能

加 1 取反

减 1 右移

加 1 取反 右移

DR 和 SR 寄存器

中的内容相与

格式

操作码编码 入口地址

/(DR+1)-DR

(DR-1)/2--DR

/(DR+1)/2--->DR

DR^【SR】-DR

10100001

10100010

11100001

10101010

90

92

96

99

5

�

06 级计算机科学与技术 班 姓名:

2009/1/15

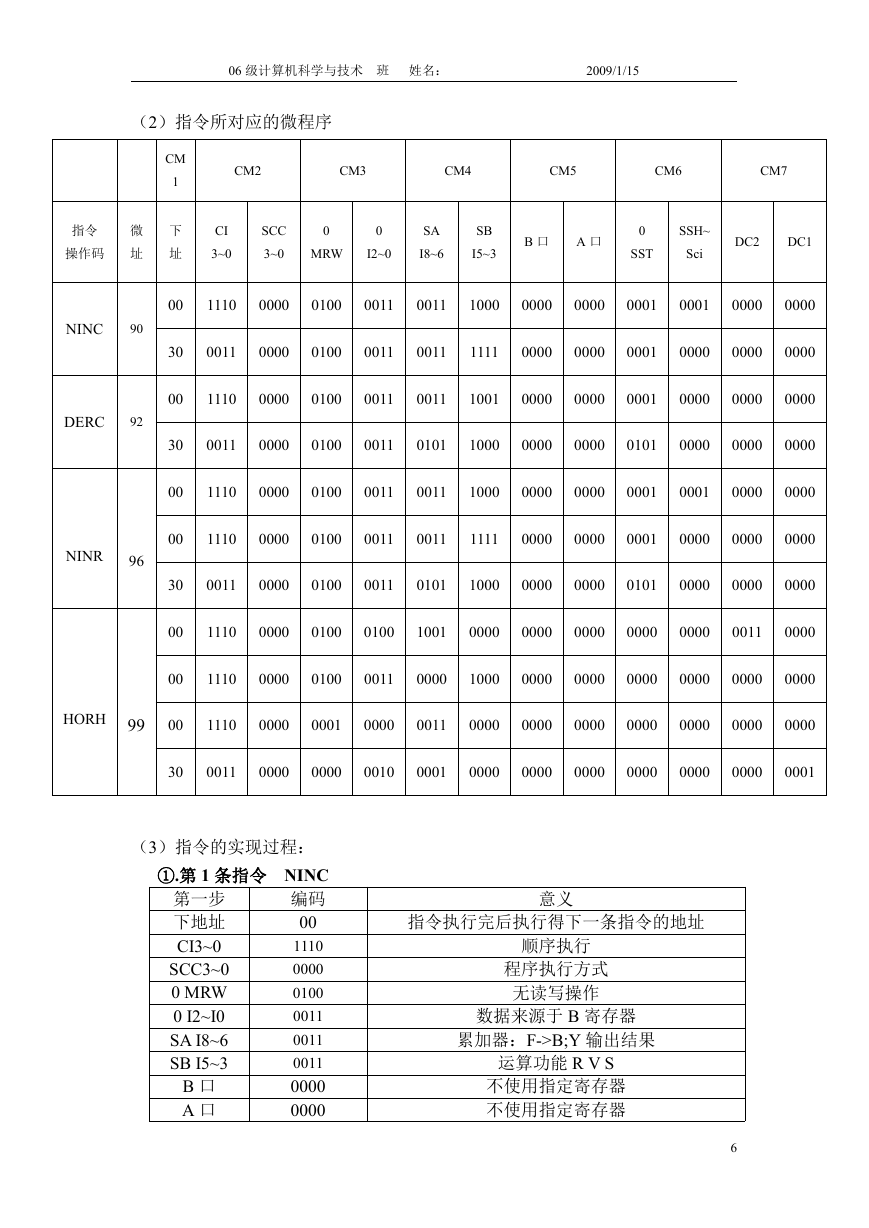

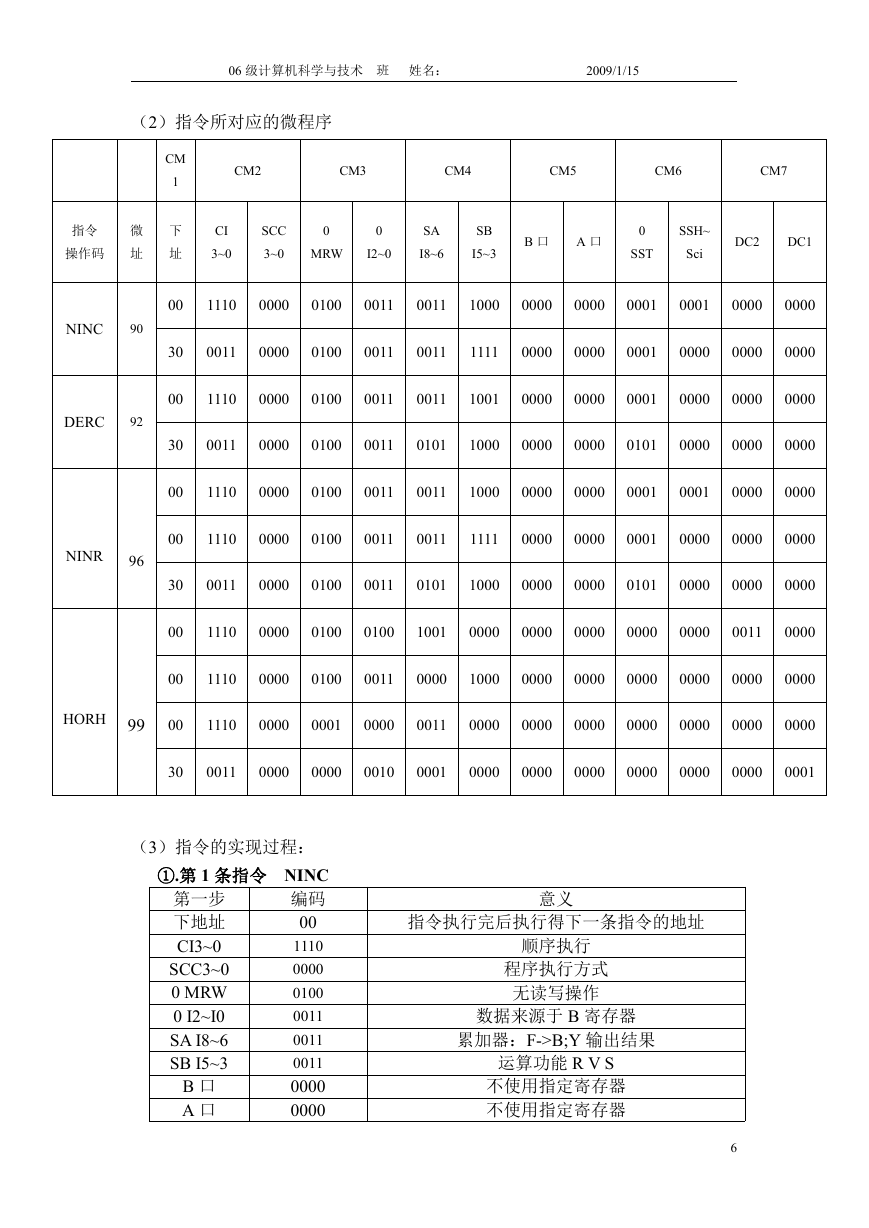

(2)指令所对应的微程序

指令

操作码

微

址

NINC

90

DERC

92

NINR

96

HORH 99

CM

1

下

址

00

30

00

30

00

00

30

00

00

00

30

CM2

CM3

CM4

CM5

CM6

CM7

CI

3~0

SCC

3~0

0

0

MRW

I2~0

SA

I8~6

SB

I5~3

B 口

A 口

0

SST

SSH~

Sci

DC2

DC1

1110

0000

0100

0011

0011

1000

0000

0000

0001

0001

0000

0000

0011

0000

0100

0011

0011

1111

0000

0000

0001

0000

0000

0000

1110

0000

0100

0011

0011

1001

0000

0000

0001

0000

0000

0000

0011

0000

0100

0011

0101

1000

0000

0000

0101

0000

0000

0000

1110

0000

0100

0011

0011

1000

0000

0000

0001

0001

0000

0000

1110

0000

0100

0011

0011

1111

0000

0000

0001

0000

0000

0000

0011

0000

0100

0011

0101

1000

0000

0000

0101

0000

0000

0000

1110

0000

0100

0100

1001

0000

0000

0000

0000

0000

0011

0000

1110

0000

0100

0011

0000

1000

0000

0000

0000

0000

0000

0000

1110

0000

0001

0000

0011

0000

0000

0000

0000

0000

0000

0000

0011

0000

0000

0010

0001

0000

0000

0000

0000

0000

0000

0001

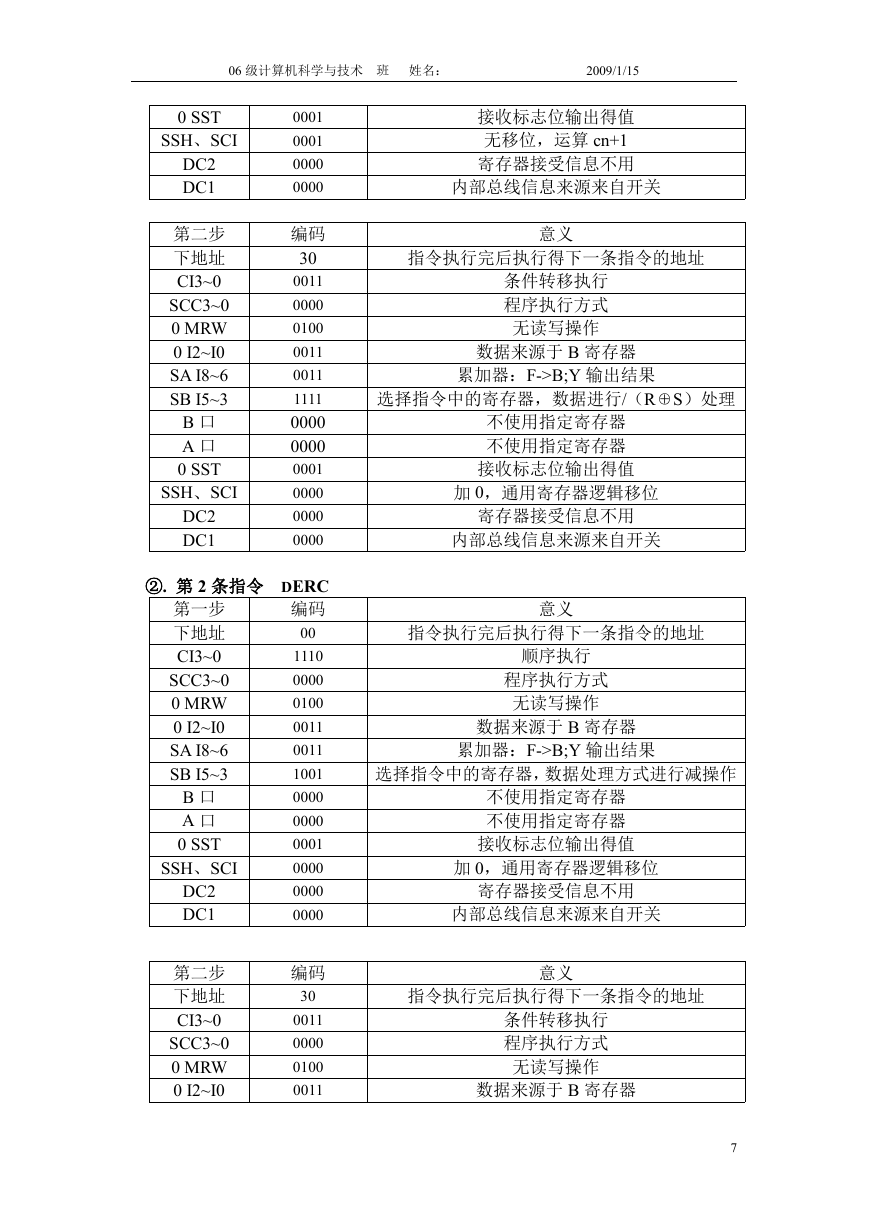

(3)指令的实现过程:

第一步

下地址

CI3~0

SCC3~0

0 MRW

0 I2~I0

SA I8~6

SB I5~3

①.第 1 条指令 NINC

编码

00

1110

0000

0100

0011

0011

0011

0000

0000

B 口

A 口

意义

指令执行完后执行得下一条指令的地址

顺序执行

程序执行方式

无读写操作

数据来源于 B 寄存器

累加器:F->B;Y 输出结果

运算功能 R V S

不使用指定寄存器

不使用指定寄存器

6

�

06 级计算机科学与技术 班 姓名:

2009/1/15

0 SST

SSH、SCI

DC2

DC1

第二步

下地址

CI3~0

SCC3~0

0 MRW

0 I2~I0

SA I8~6

SB I5~3

B 口

A 口

0 SST

SSH、SCI

DC2

DC1

0001

0001

0000

0000

编码

30

0011

0000

0100

0011

0011

1111

0000

0000

0001

0000

0000

0000

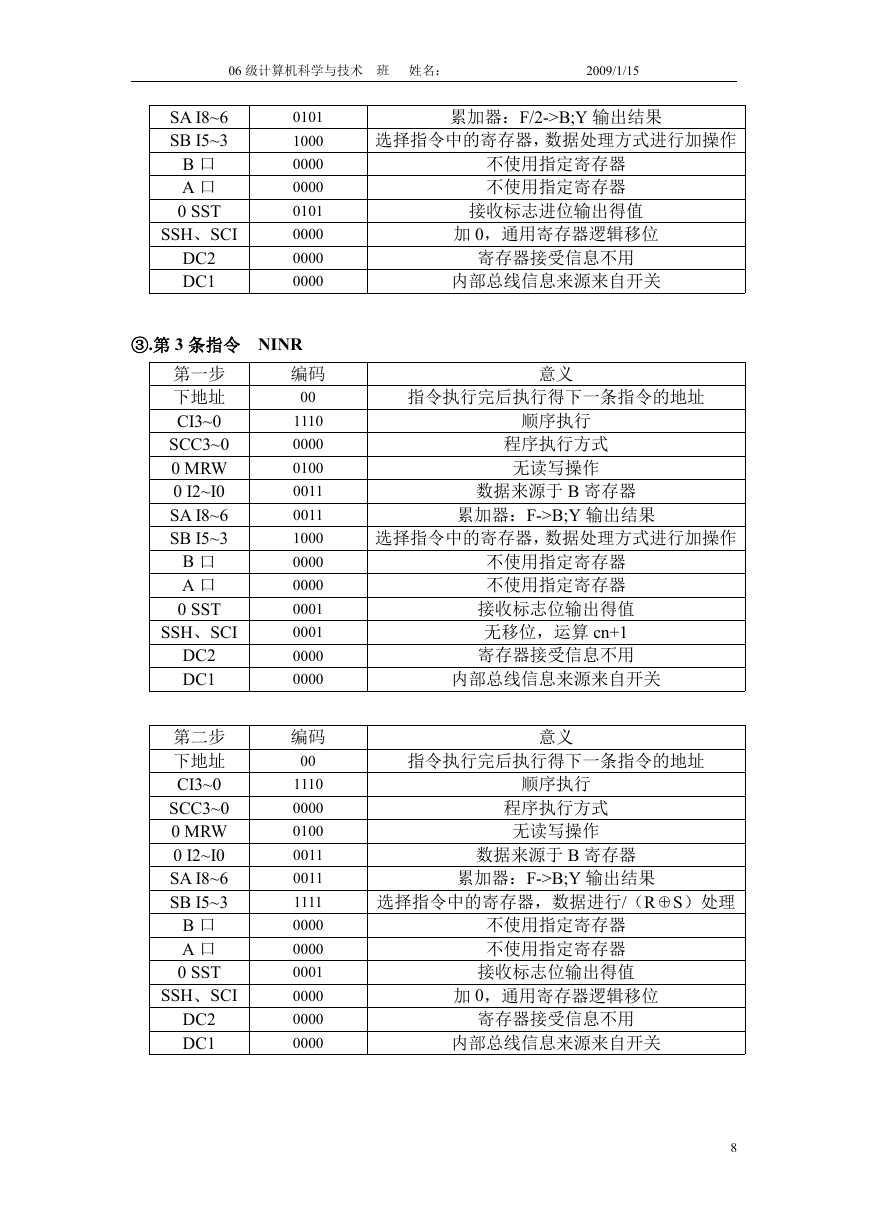

第一步

下地址

CI3~0

SCC3~0

0 MRW

0 I2~I0

SA I8~6

SB I5~3

②. 第 2 条指令 DERC

编码

00

1110

0000

0100

0011

0011

1001

0000

0000

0001

0000

0000

0000

B 口

A 口

0 SST

SSH、SCI

DC2

DC1

接收标志位输出得值

无移位,运算 cn+1

寄存器接受信息不用

内部总线信息来源来自开关

意义

指令执行完后执行得下一条指令的地址

条件转移执行

程序执行方式

无读写操作

数据来源于 B 寄存器

累加器:F->B;Y 输出结果

选择指令中的寄存器,数据进行/(R⊕S)处理

不使用指定寄存器

不使用指定寄存器

接收标志位输出得值

加 0,通用寄存器逻辑移位

寄存器接受信息不用

内部总线信息来源来自开关

意义

指令执行完后执行得下一条指令的地址

顺序执行

程序执行方式

无读写操作

数据来源于 B 寄存器

累加器:F->B;Y 输出结果

选择指令中的寄存器,数据处理方式进行减操作

不使用指定寄存器

不使用指定寄存器

接收标志位输出得值

加 0,通用寄存器逻辑移位

寄存器接受信息不用

内部总线信息来源来自开关

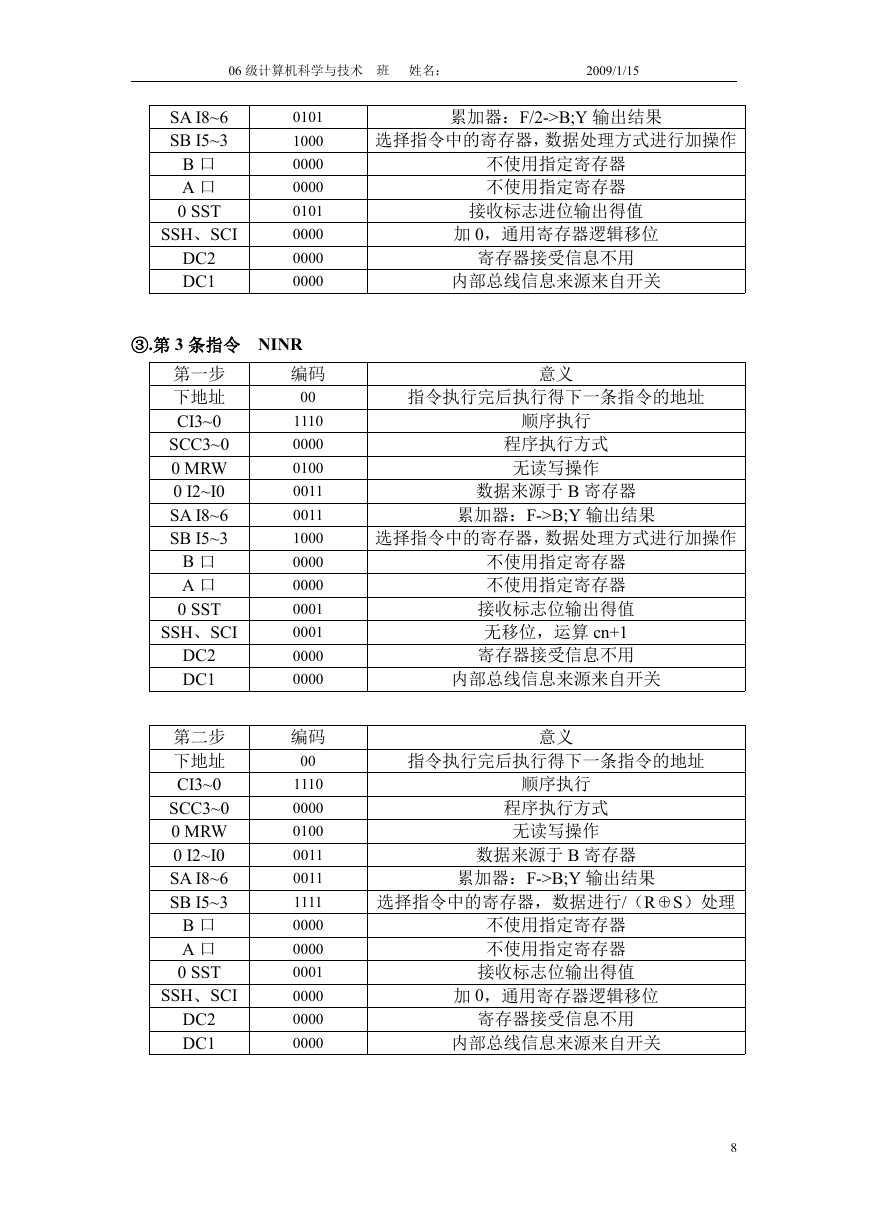

第二步

下地址

CI3~0

SCC3~0

0 MRW

0 I2~I0

编码

30

0011

0000

0100

0011

意义

指令执行完后执行得下一条指令的地址

条件转移执行

程序执行方式

无读写操作

数据来源于 B 寄存器

7

�

06 级计算机科学与技术 班 姓名:

2009/1/15

SA I8~6

SB I5~3

B 口

A 口

0 SST

SSH、SCI

DC2

DC1

0101

1000

0000

0000

0101

0000

0000

0000

累加器:F/2->B;Y 输出结果

选择指令中的寄存器,数据处理方式进行加操作

不使用指定寄存器

不使用指定寄存器

接收标志进位输出得值

加 0,通用寄存器逻辑移位

寄存器接受信息不用

内部总线信息来源来自开关

③.第 3 条指令 NINR

第一步

下地址

CI3~0

SCC3~0

0 MRW

0 I2~I0

SA I8~6

SB I5~3

B 口

A 口

0 SST

SSH、SCI

DC2

DC1

第二步

下地址

CI3~0

SCC3~0

0 MRW

0 I2~I0

SA I8~6

SB I5~3

B 口

A 口

0 SST

SSH、SCI

DC2

DC1

编码

00

1110

0000

0100

0011

0011

1000

0000

0000

0001

0001

0000

0000

编码

00

1110

0000

0100

0011

0011

1111

0000

0000

0001

0000

0000

0000

意义

指令执行完后执行得下一条指令的地址

顺序执行

程序执行方式

无读写操作

数据来源于 B 寄存器

累加器:F->B;Y 输出结果

选择指令中的寄存器,数据处理方式进行加操作

不使用指定寄存器

不使用指定寄存器

接收标志位输出得值

无移位,运算 cn+1

寄存器接受信息不用

内部总线信息来源来自开关

意义

指令执行完后执行得下一条指令的地址

顺序执行

程序执行方式

无读写操作

数据来源于 B 寄存器

累加器:F->B;Y 输出结果

选择指令中的寄存器,数据进行/(R⊕S)处理

不使用指定寄存器

不使用指定寄存器

接收标志位输出得值

加 0,通用寄存器逻辑移位

寄存器接受信息不用

内部总线信息来源来自开关

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc