沈阳航空航天大学

课 程 设 计 报 告

课程设计名称:计算机组成原理课设

课程设计题目:阵列除法器的设计

学 院: 计算机学院

专 业: 计算机科学与技术

班 级: 1634010105

学 号: 163401010523

姓 名: 牛斌帅

指导教师: 訾学博

指导教师评语:

课设成绩:

签名

年

月

日

�

沈阳航空航天大学课程设计报告

沈阳航空航天大学

课程设计任务书

课程名称 计 算 机 组 成 原 理 课 程 设 计

专 业 计算机科学与技术

学生姓名

牛斌帅

班级

计算机 1605

学号

163401010523

题目名称 阵列除法器的设计

起止日期 2017 年 12 月 11 日起至 2017 年 12 月 22 日止

课设内容和要求:

一、课程设计内容

采用 Quartus 可编程器件开发工具软件,伟福 COP2000 实验箱,设计并实现阵列除法器功能。

二、课程设计要求

1.采用自上而下的设计方法,顶层设计使用原理图设计输入方式;底层设计输入方式自行

选定;

2.课程设计的电路主要应包括:细胞模块和门电路等。其中控制信号可用外部开关或用

VHDL 语言以控制器方式实现,其它部分可以调用系统资源库中的器件;

3.被除数和除数皆为四位;

4.对设计电路进行仿真并验证其正确性,仿真数据由指导教师给出;

5.实现编程下载和硬件测试;

6.独立设计、调试、仿真、下载和硬件测试并通过指导教师现场验收;

7.撰写课程设计报告。

参考资料:

[1] 曹昕燕. EDA 技术实验与课程设计[M].北京:清华大学出版社,2006

[2] 范延滨.微型计算机系统原理、接口与 EDA 设计技术[M].北京:北京邮电大学出版社,2006

[3] 王爱英.计算机组成与结构(第 4 版)[M].北京:清华大学出版社,2006

教 研 室 审 核 意 见 : 同 意 立 题

教 研 室 主 任 签 字 :

指导教师(签名)

学

生(签名)

年

年

月

月

日

日

I

�

沈阳航空航天大学课程设计报告

课程设计总结:

本次课程设计,我受益匪浅。当拿到课设题目后,我犯了一个最基本的错误:

乐观的认为,题目很简单,原理很简单。但在具体实行时却遇到许多困难,对

Quartus II 9.1 设计软件的陌生更加阻碍着我的进程。于是,我决定塌下心来好好

研究原理及软件的运用。用了一天的时间将软件中的自带芯片的功能查询了一遍,

基本找到需要的芯片。之后,又学习了对电路封装的方法,再后来就能灵活的操

作该软件,这对整个电路的设计很有帮助。随后开始将各个部件连接到一起,这

里也充满学问,不是单单的组合在一起,而虑整体电路的节拍,以是要综合考保

证各个部件有序工作。

我参考各种资料和别人的设计进行电路设计。设计的过程还真是痛苦,头脑

中不断出现想法,但有一个个被现实否定,只能另寻方法。不过,功夫不负有心

人。终于,我的想法终于在现实中实现了,就这样我完成了我的设计,那时的我

有一种释然的感觉,不过,我知道这只是一小步,要想最终完成还有很长的路要

走,所以要继续努力。

在课设期间,我认为老师和同学都给予我很大的帮助,老师总是不厌其烦的

为我们解决疑惑,同学们也总是在我旁边指导我,有这些才使我的课设顺利完成,

在这里我要衷心说声谢谢,这份珍贵的经历,我会永远记在心中。

在这次课设中,我对与门、或门、异或门等芯片等芯片和全加器都有了一定

的了解。原本听老师讲课教受的一些理论东西还是不能很好运用,现在经过自己

亲手的练习对知识的掌握加深了、也能较好的运用了。

在这次课设中,我也知道了自己学习组成原理这门课程上的不足,对每个知

识都是半知半解没有把知识彻底的搞懂也不能把知识熟练的联系起来。在这次专

课设中我把各种知识总和起来学习更好的学习了这门课程。在以后的学习中我也

会坚持这种学习方法,让自己对自己所学的知识融会贯通。我相信,只要我们在

每一次实践中都能仔细思考,亲自动手,现在学到的任何一点知识在将来都会成

为一笔宝贵的财富。因此,我会认真地对待我的每一次课设和实验。

II

�

沈阳航空航天大学课程设计报告

目

录

第 1 章 总体设计方案.................................................................................................. 1

1.1 设计原理...............................................................................................................1

1.2 设计思路...............................................................................................................2

1.3 设计环境...............................................................................................................3

第 2 章 详细设计方案.................................................................................................. 6

2.1 顶层方案图的设计与实现...................................................................................6

2.1.1 创建顶层图形设计文件...................................................................................6

2.1.2 器件的选择与引脚锁定...................................................................................7

2.1.3 编译、综合、适配...........................................................................................8

2.2 功能模块的设计与实现.......................................................................................8

2.3 仿真调试.............................................................................................................10

第 3 章 编程下载与硬件测试.................................................................................... 12

3.1 编程下载.............................................................................................................12

3.2 硬件测试及结果分析.........................................................................................12

参考文献.........................................................................................................................15

附 录 (电路原理图) ............................................................................................ 16

III

�

沈阳航空航天大学课程设计报告

第 1 章 总体设计方案

1.1 设计原理

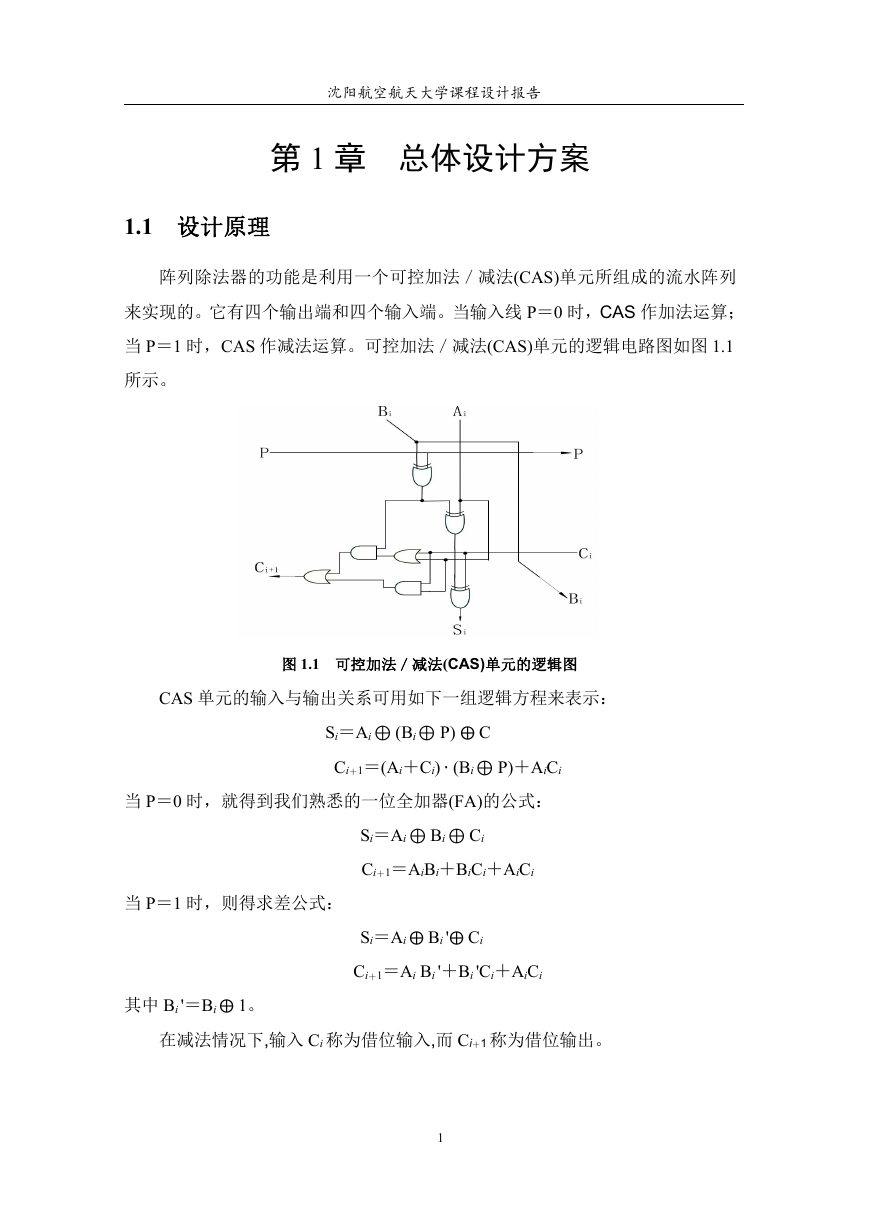

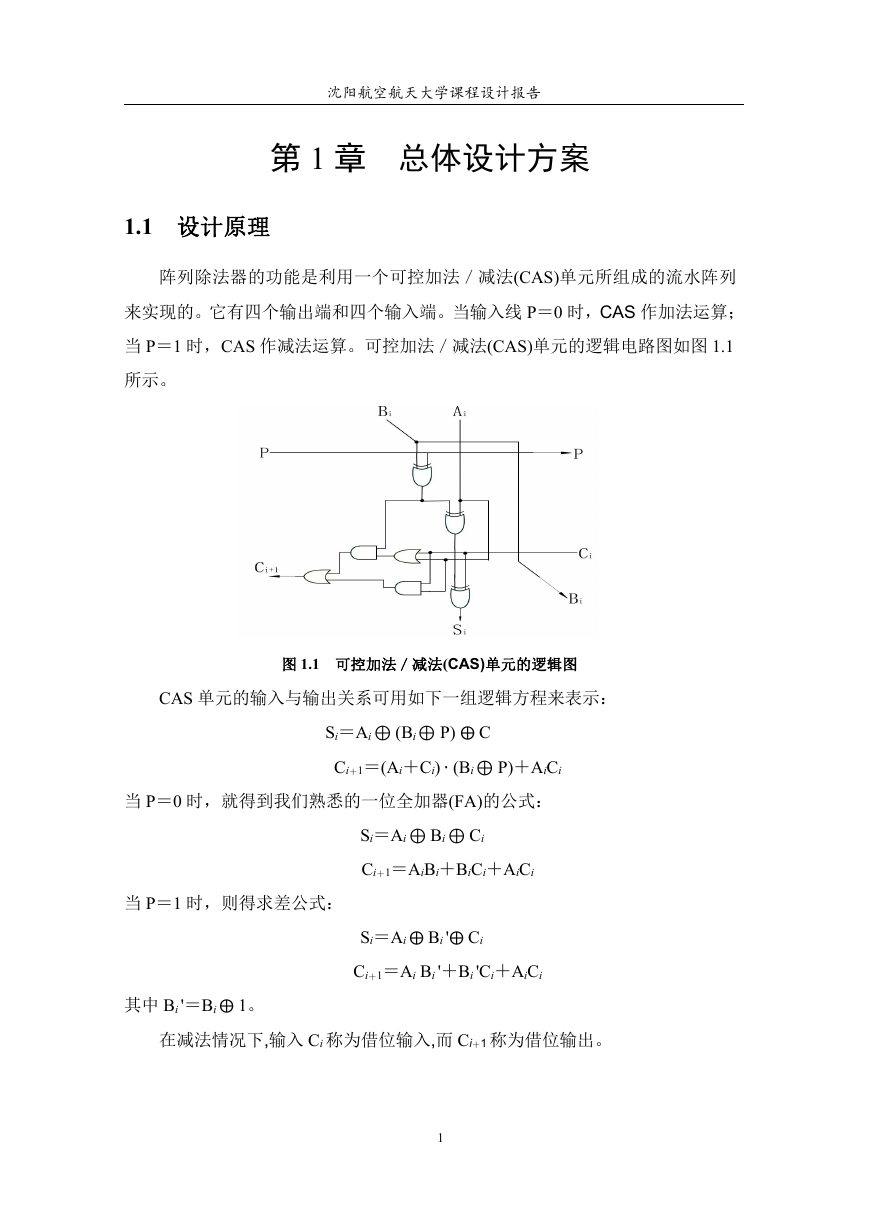

阵列除法器的功能是利用一个可控加法/减法(CAS)单元所组成的流水阵列

来实现的。它有四个输出端和四个输入端。当输入线 P=0 时,CAS 作加法运算;

当 P=1 时,CAS 作减法运算。可控加法/减法(CAS)单元的逻辑电路图如图 1.1

所示。

图 1.1 可控加法/减法(CAS)单元的逻辑图

CAS 单元的输入与输出关系可用如下一组逻辑方程来表示:

当 P=0 时,就得到我们熟悉的一位全加器(FA)的公式:

Si=Ai⊕ (Bi⊕ P)⨁ C

Ci+1=(Ai+Ci)∙ (Bi⊕ P)+AiCi

Si=Ai⊕ Bi⊕ Ci

Si=Ai⨁ Bi '⨁ Ci

Ci+1=Ai Bi '+Bi 'Ci+AiCi

Ci+1=AiBi+BiCi+AiCi

1

当 P=1 时,则得求差公式:

其中 Bi '=Bi⨁ 1。

在减法情况下,输入 Ci 称为借位输入,而 Ci+1 称为借位输出。

�

沈阳航空航天大学课程设计报告

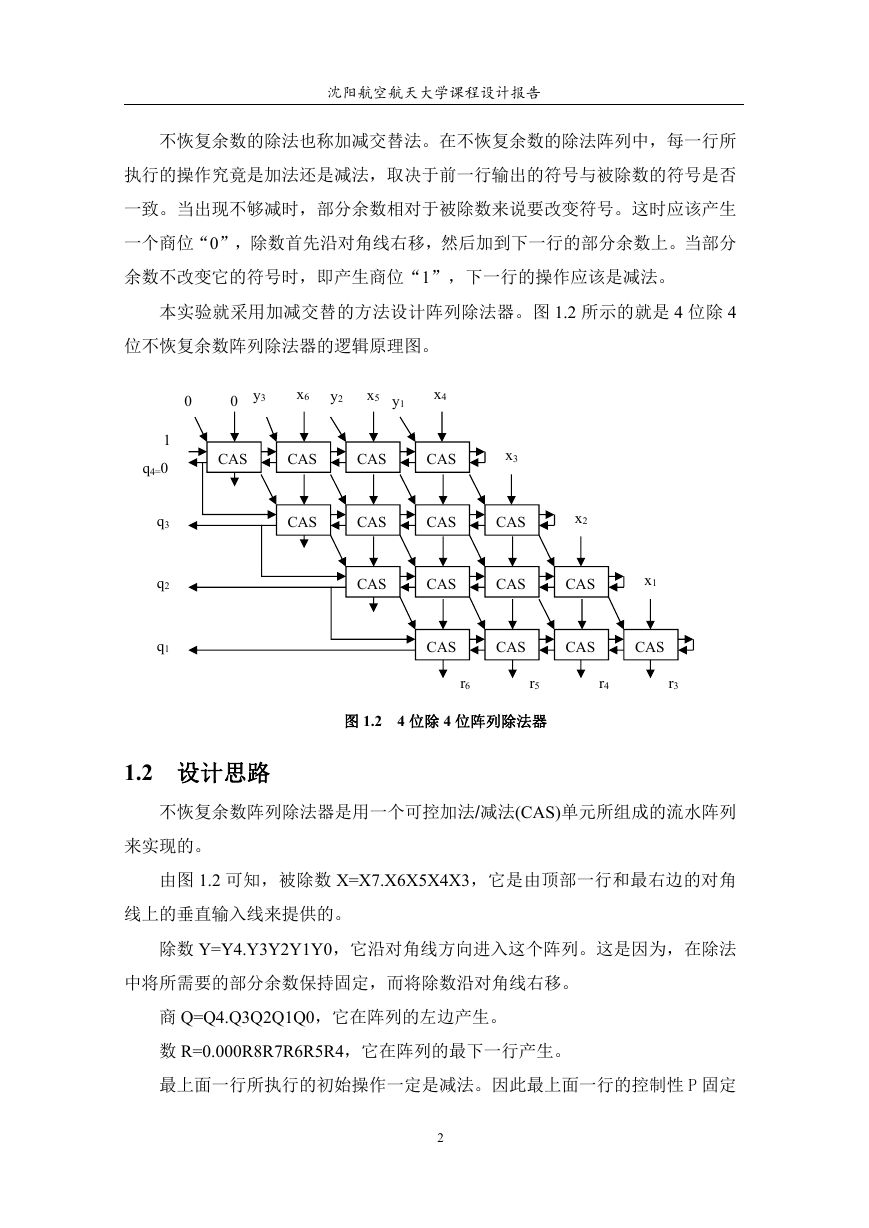

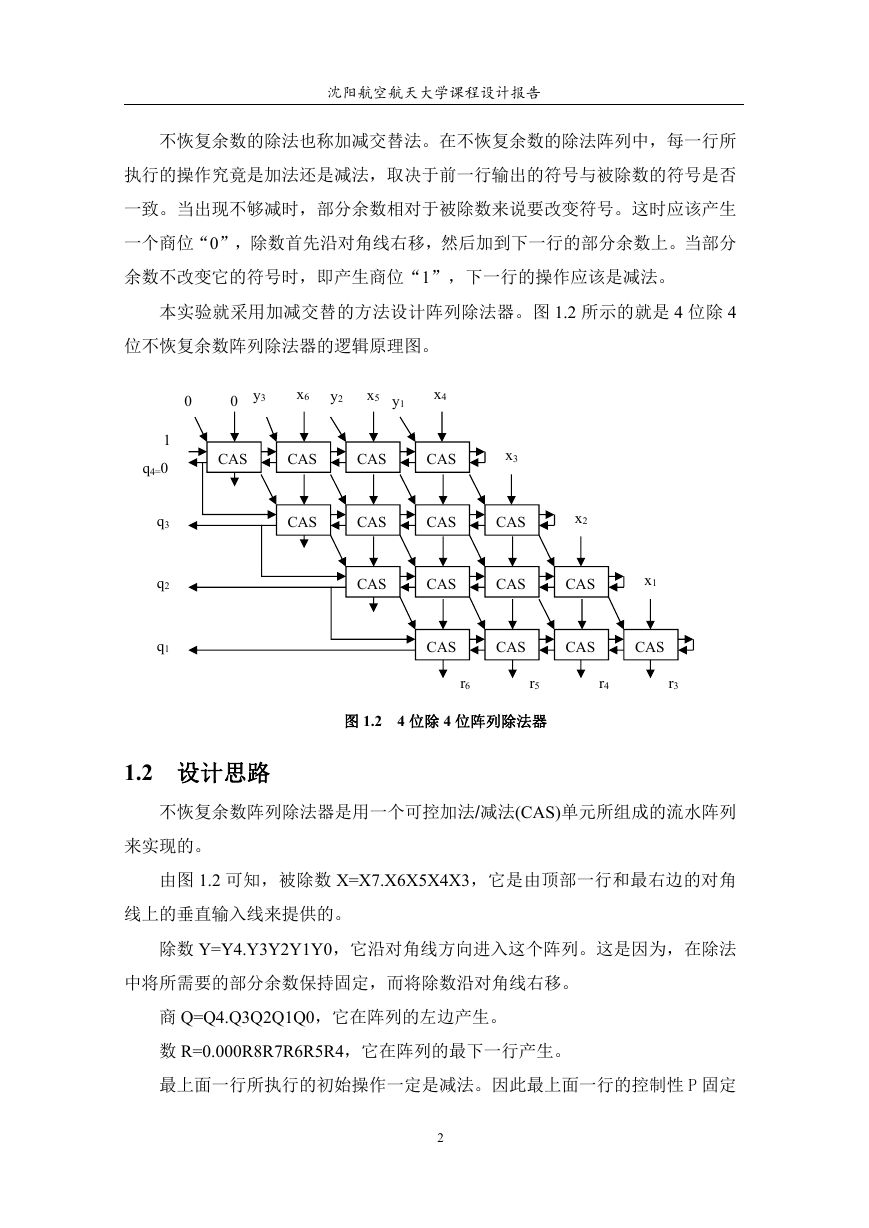

不恢复余数的除法也称加减交替法。在不恢复余数的除法阵列中,每一行所

执行的操作究竟是加法还是减法,取决于前一行输出的符号与被除数的符号是否

一致。当出现不够减时,部分余数相对于被除数来说要改变符号。这时应该产生

一个商位“0”,除数首先沿对角线右移,然后加到下一行的部分余数上。当部分

余数不改变它的符号时,即产生商位“1”,下一行的操作应该是减法。

本实验就采用加减交替的方法设计阵列除法器。图 1.2 所示的就是 4 位除 4

位不恢复余数阵列除法器的逻辑原理图。

0

y3

0

x6

y2

x5

y1

x4

1

q4=0

q3

q2

q1

CAS

CAS

CAS

CAS

x3

CAS

CAS

CAS

CAS

x2

CAS

CAS

CAS

CAS

x1

CAS

CAS

CAS

CAS

r6

r5

r4

r3

图 1.2 4 位除 4 位阵列除法器

1.2 设计思路

不恢复余数阵列除法器是用一个可控加法/减法(CAS)单元所组成的流水阵列

来实现的。

由图 1.2 可知,被除数 X=X7.X6X5X4X3,它是由顶部一行和最右边的对角

线上的垂直输入线来提供的。

除数 Y=Y4.Y3Y2Y1Y0,它沿对角线方向进入这个阵列。这是因为,在除法

中将所需要的部分余数保持固定,而将除数沿对角线右移。

商 Q=Q4.Q3Q2Q1Q0,它在阵列的左边产生。

数 R=0.000R8R7R6R5R4,它在阵列的最下一行产生。

最上面一行所执行的初始操作一定是减法。因此最上面一行的控制性 P 固定

2

�

沈阳航空航天大学课程设计报告

1.3 设计环境

(1) 硬件环境

CPT20 实验板

CPT20 实验板是用于韦福 COP2000 计算机组成实验仪上的扩展实验板,是用

ALTERA 的 EP3C16 作为核心 FPGA 配以必须的外围器件,来进行计算机组成

原理的高级实验。此实验板不但可以用在 COP2000 计算机组成原理实验仪上,而

且还可以单独使用,用来进行各类 SOPC(片上可编程系统)实验。

实验板主要包括 Altera EP3C16 FPGA、EPCS4 配置芯片以及 AS 编程接口、

JTAG 编程接口、64M 字节 SDRAM、1M 字节 SRAM、4M 字节 FLASH、8 个八段数

码管、8 位 LED 发光管、40 位拨码开关、UART 串口、128x64 液晶屏接口、48M

有源晶振和 8 位扩展输入/输出等资源。

实验板上共享地址和数据线,但片选不能共用,为了方便,设计也没有把读

写信号全局共用,两片 SRAM 存储器共用读写信号,两片 FLASH 存储器共用读写

信号,两片 SDRAM 共用刷新控制和读写信号。并且供给的 SDRAM 的 SDCLK 时钟

信号和控制 SDRAM 读写的时钟信号不能同相位,SDCLK 信号相位要提前 1ns 到

3ns 左右,否则会造成 SDRAM 的读写错误;LCD 接口是按存储器方式访问的,所

以其 8 位数据线与存储器的低 8 位共用,控制线共用了三根地址线 D/I 接 A0,

R/W 接 A1,LCS1 接 A2。

COP2000 型计算机组成原理实验仪

COP2000 计算机组成原理实验系统由实验平台、开关电源、软件三大部分组

成。实验平台上有寄存器组 R0-R3、运算单元、累加器 A、暂存器 B、直通/左移/

右移单元、地址寄存器、程序计数器、堆栈、中断源、输入/输出单元、存储器单

元、微地址寄存器、指令寄存器、微程序控制器、组合逻辑控制器、扩展座、总

线插孔区、微动开关/指示灯、逻辑笔、脉冲源、20 个按键、字符式 LCD、RS232 口。

COP2000 计算机组成原理实验系统各单元部件都以计算机结构模型布局,清

晰明了,系统在实验时即使不借助 PC 机,也可实时监控数据流状态及正确与否,

实验系统的软硬件对用户的实验设计具有完全的开放特性,系统提供了微程序控

3

�

沈阳航空航天大学课程设计报告

制器和组合逻辑控制器两种控制器方式, 系统还支持手动方式、联机方式、模拟

方式三种工作方式,系统具备完善的寻址方式、指令系统和强大的模拟调试功能。

(2)软件环境

Quartus

II 9.1 设计软件

Quartus 是 Altera 公司的综合性 PLD/FPGA 开发软件,原理图、VHDL、

VerilogHDL 以及 AHDL 等多种设计输入形式,内嵌综合器以及仿真器,可以

完成从设计输入到硬件配置的完整 PLD 设计流程。

Quartus II 9.1 拥有多种接口的与或非等门电路和用门电路集成的芯片。该

系统拥有画图工具,可以自行设计电路图,又拥有电路图仿真功能,又诸多的信

号脉冲,也可以手动画脉冲信号,因此,可以对电路图设计进行仿真,通过观察

电路图的输入输出脉冲信号来测试电路设计真确与否。

顺带了解一下,Quartus II 9.0 也拥有多种接口的与或非等门电路和用门电

路集成的芯片。该系统拥有画图工具,也可以自行设计电路图,又拥有电路图仿

真功能,又诸多的信号脉冲,也可以手动画脉冲信号,因此,也可以对电路图设

计进行仿真,通过观察电路图的输入输出脉冲信号来测试电路设计真确与否。

Quartus II 可以在 Windows、Linux、以及 Unix 上使用,除了可以使用 Tcl

脚本完成设计流程外,提供了完善的用户图形界面设计方式。具有运行速度快,界

面统一,功能集中,易学易用等特点。Quartus II 支持 Altera 的 IP 核,包含

了 LPM/MegaFunction 宏功能模块库,是用户可以充分利用成熟的模块,简化了

设计的复杂性、加快了设计速度。对第三方 EDA 工具的良好支持也使用户可以在

设计流程的各个阶段使用熟悉的第三方 EDA 工具。此外,Quartus II 通过和 DSP

Builder 工具与 Mat lab/Simulink 相结合,可以方便地实现各种 DSP 应用系

统;支持 Altera 的片上可编程系统开发,集系统级设计、嵌入式开发、可编程

逻辑于一体,是一种综合性的开发平台。

Quartus II 9.1 拥有多种接口的与或非等门电路和用门电路集成的芯片。该

系统拥有画图工具,可以自行设计电路图,又拥有电路图仿真功能,又诸多的信

号脉冲,也可以手动画脉冲信号,因此,可以对电路图设计进行仿真,通过观察

电路图的输入输出脉冲信号来测试电路设计真确与否。

4

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc