Preface

Scope

Related Documents

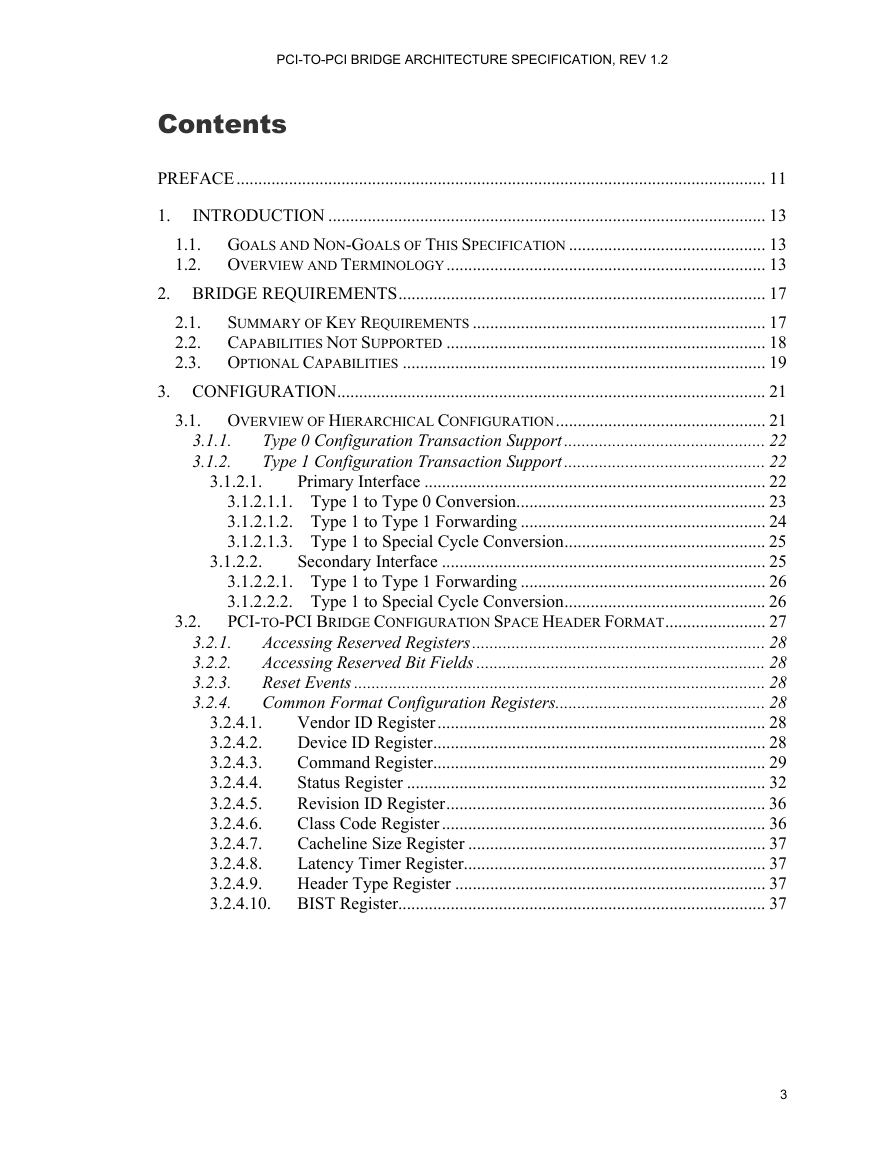

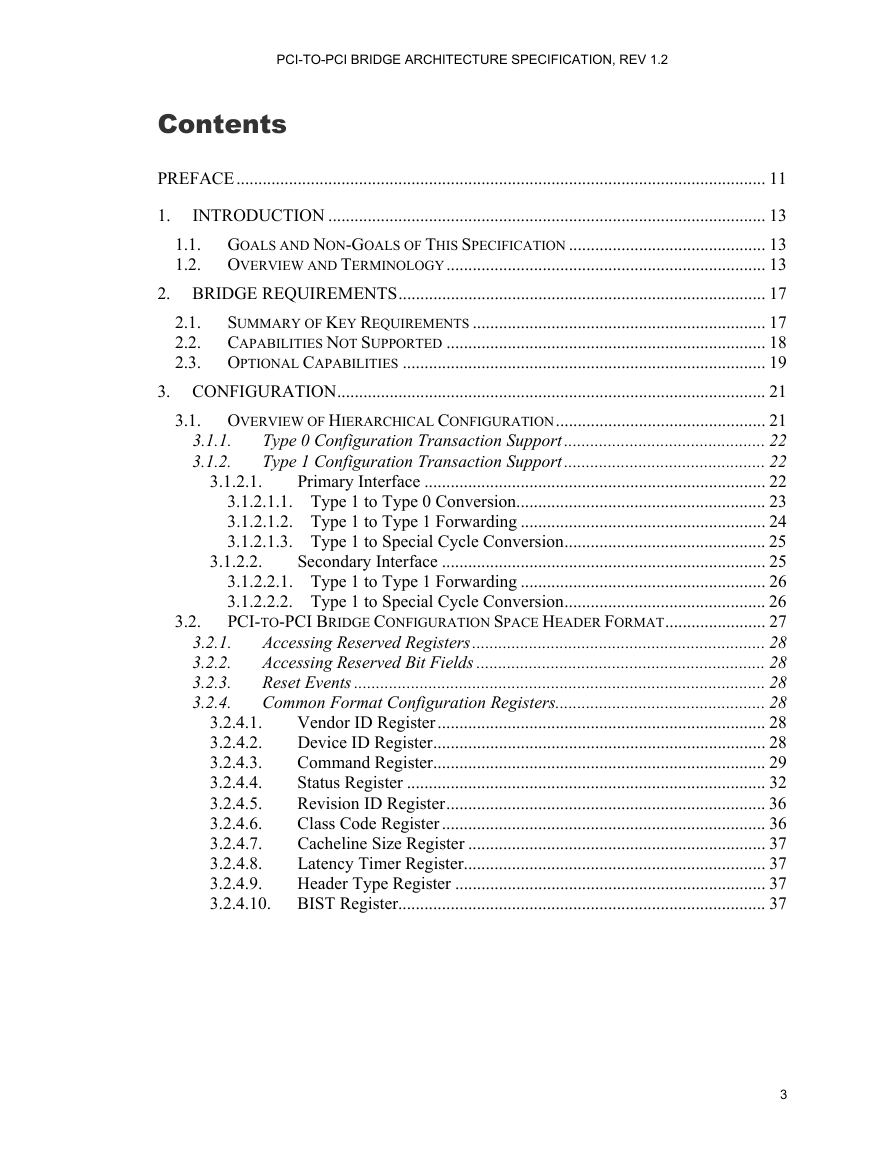

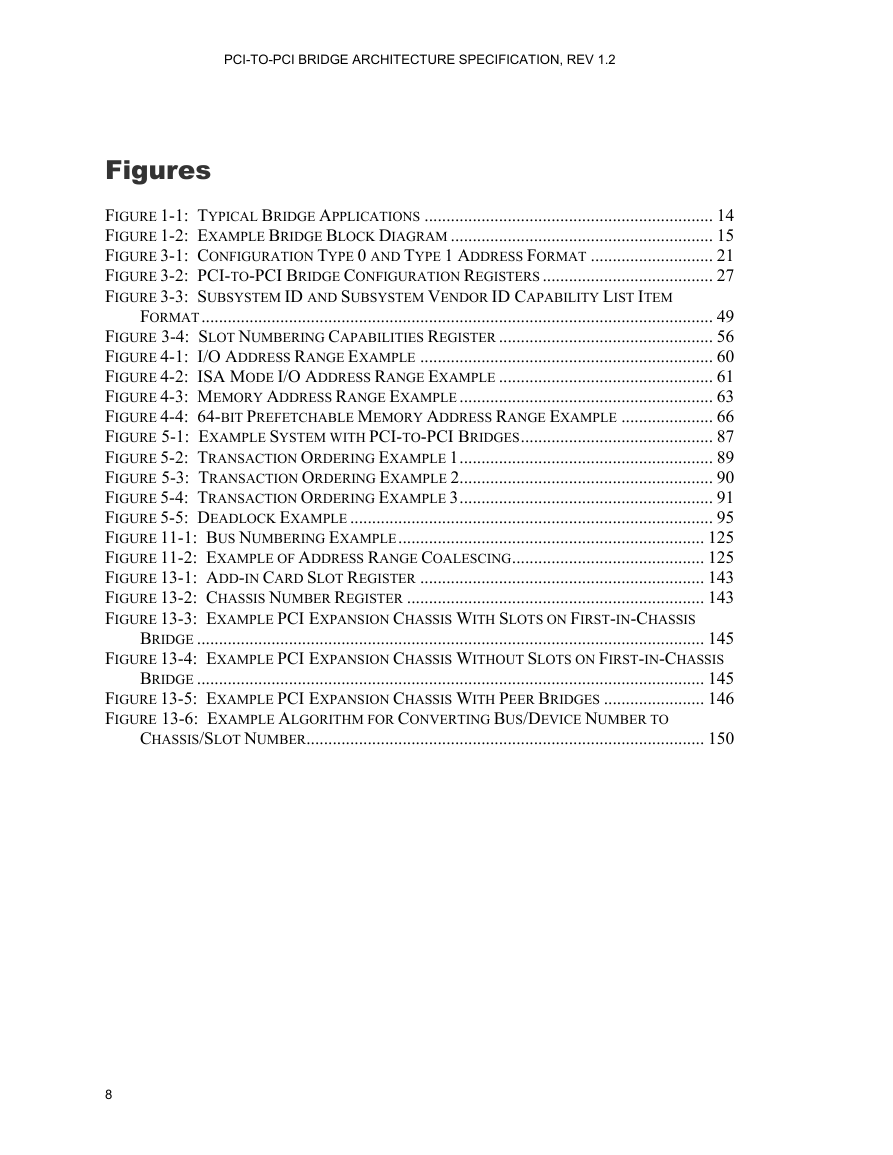

1. Introduction

1.1. Goals and Non-Goals of This Specification

1.2. Overview and Terminology

2. Bridge Requirements

2.1. Summary of Key Requirements

2.2. Capabilities Not Supported

2.3. Optional Capabilities

3. Configuration

3.1. Overview of Hierarchical Configuration

3.1.1. Type 0 Configuration Transaction Support

3.1.2. Type 1 Configuration Transaction Support

3.1.2.1. Primary Interface

3.1.2.1.1. Type 1 to Type 0 Conversion

3.1.2.1.2. Type 1 to Type 1 Forwarding

3.1.2.1.3. Type 1 to Special Cycle Conversion

3.1.2.2. Secondary Interface

3.1.2.2.1. Type 1 to Type 1 Forwarding

3.1.2.2.2. Type 1 to Special Cycle Conversion

3.2. PCI-to-PCI Bridge Configuration Space Header Format

3.2.1. Accessing Reserved Registers

3.2.2. Accessing Reserved Bit Fields

3.2.3. Reset Events

3.2.4. Common Format Configuration Registers

3.2.4.1. Vendor ID Register

3.2.4.2. Device ID Register

3.2.4.3. Command Register

3.2.4.4. Status Register

3.2.4.5. Revision ID Register

3.2.4.6. Class Code Register

3.2.4.7. Cacheline Size Register

3.2.4.8. Latency Timer Register

3.2.4.9. Header Type Register

3.2.4.10. BIST Register

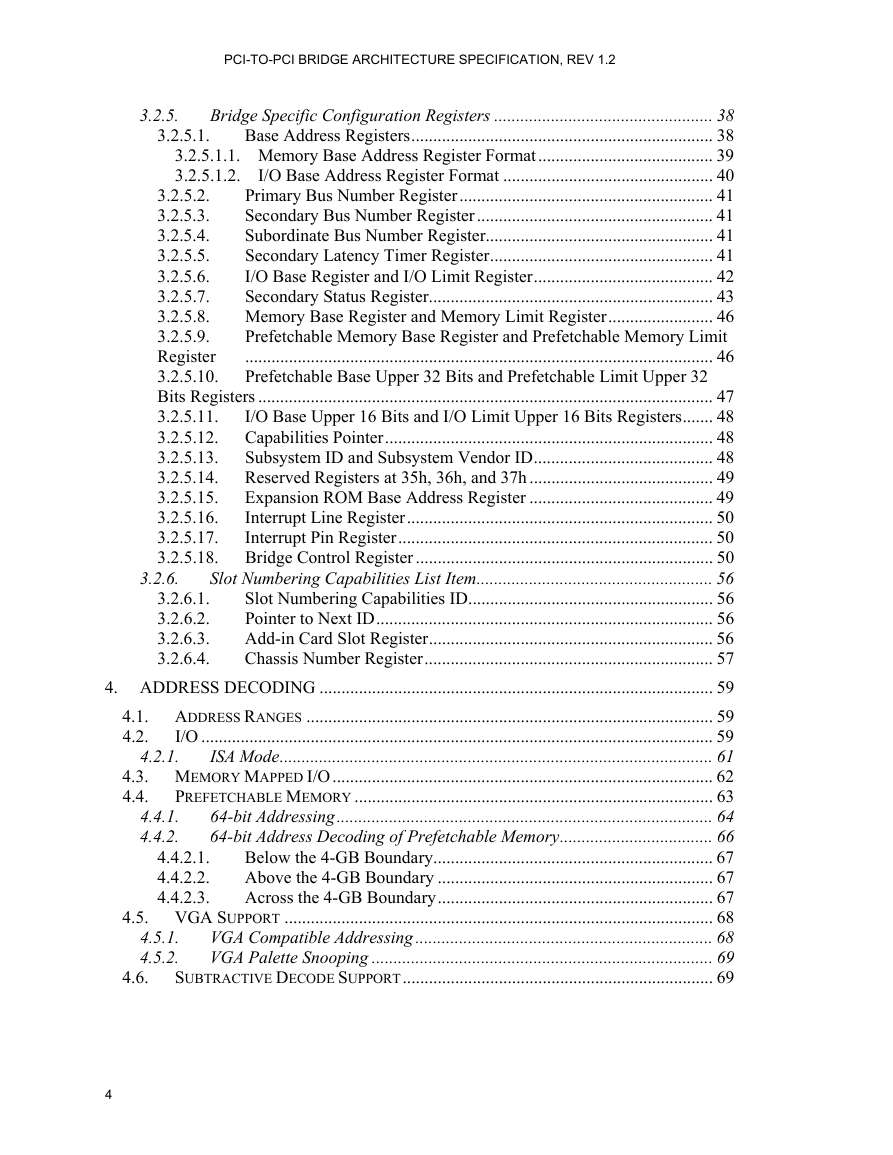

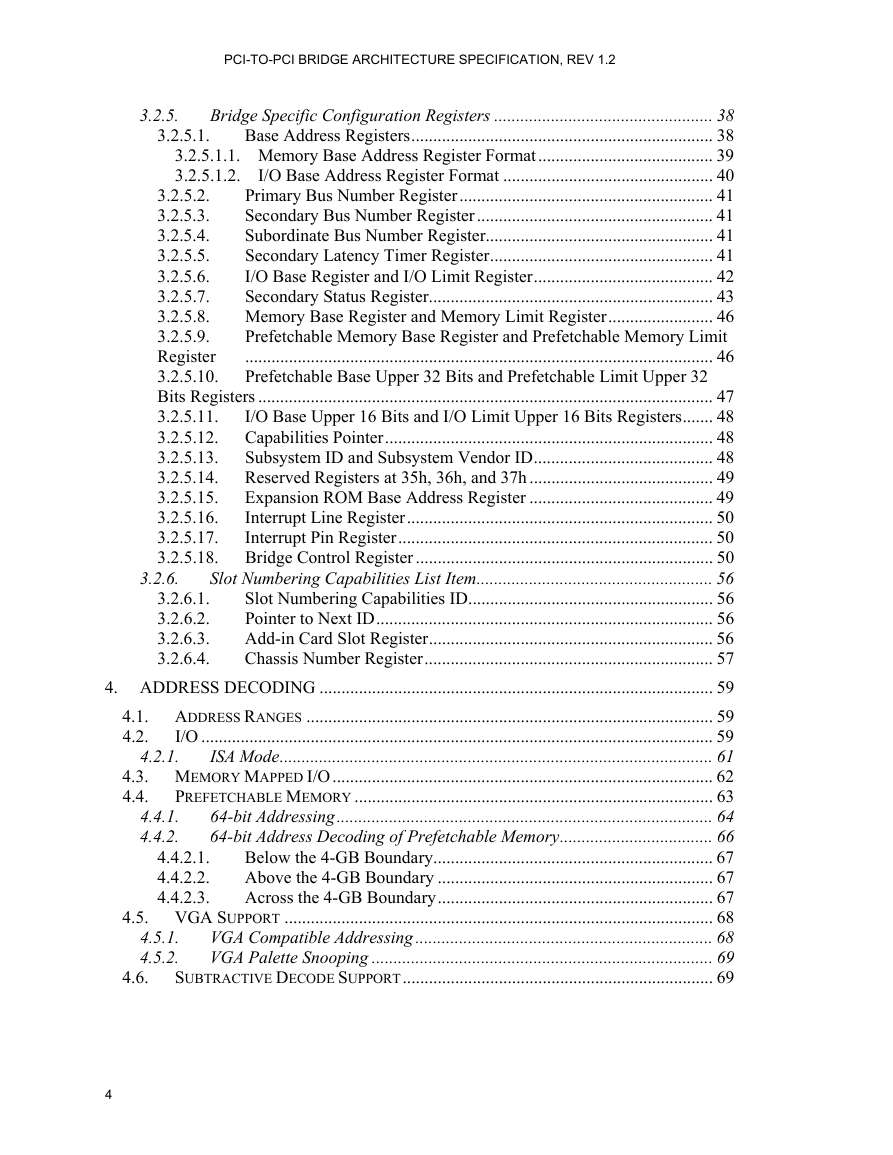

3.2.5. Bridge Specific Configuration Registers

3.2.5.1. Base Address Registers

3.2.5.1.1. Memory Base Address Register Format

3.2.5.1.2. I/O Base Address Register Format

3.2.5.2. Primary Bus Number Register

3.2.5.3. Secondary Bus Number Register

3.2.5.4. Subordinate Bus Number Register

3.2.5.5. Secondary Latency Timer Register

3.2.5.6. I/O Base Register and I/O Limit Register

3.2.5.7. Secondary Status Register

3.2.5.8. Memory Base Register and Memory Limit

Register

3.2.5.9. Prefetchable Memory Base Register and

Prefetchable Memory Limit Register

3.2.5.10. Prefetchable Base Upper 32 Bits and

Prefetchable Limit Upper 32 Bits Registers

3.2.5.11. I/O Base Upper 16 Bits and I/O Limit Upper 16

Bits Registers

3.2.5.12. Capabilities Pointer

3.2.5.13. Subsystem ID and Subsystem Vendor ID

3.2.5.14. Reserved Registers at 35h, 36h, and 37h

3.2.5.15. Expansion ROM Base Address Register

3.2.5.16. Interrupt Line Register

3.2.5.17. Interrupt Pin Register

3.2.5.18. Bridge Control Register

3.2.6. Slot Numbering Capabilities List Item

3.2.6.1. Slot Numbering Capabilities ID

3.2.6.2. Pointer to Next ID

3.2.6.3. Add-in Card Slot Register

3.2.6.4. Chassis Number Register

4. Address Decoding

4.1. Address Ranges

4.2. I/O

4.2.1. ISA Mode

4.3. Memory Mapped I/O

4.4. Prefetchable Memory

4.4.1. 64-bit Addressing

4.4.2. 64-bit Address Decoding of Prefetchable Memory

4.4.2.1. Below the 4-GB Boundary

4.4.2.2. Above the 4-GB Boundary

4.4.2.3. Across the 4-GB Boundary

4.5. VGA Support

4.5.1. VGA Compatible Addressing

4.5.2. VGA Palette Snooping

4.6. Subtractive Decode Support

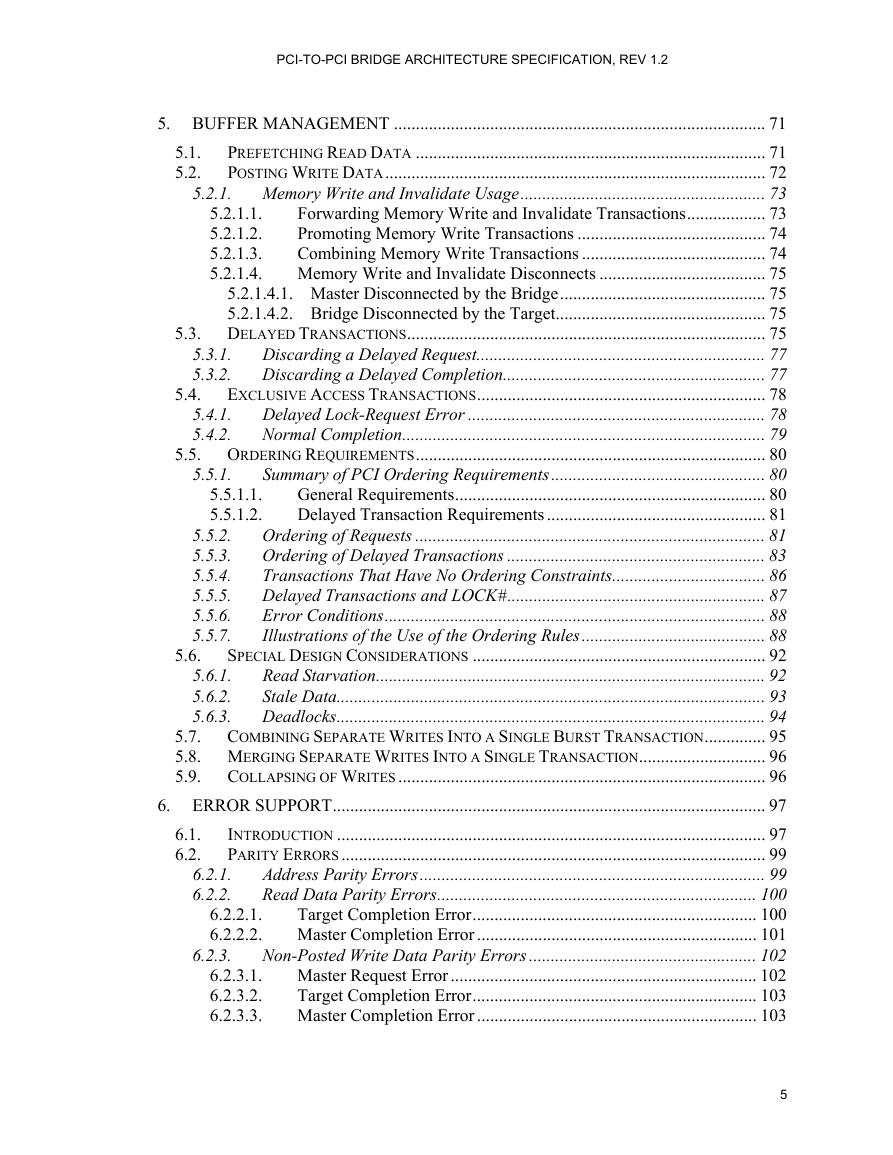

5. Buffer Management

5.1. Prefetching Read Data

5.2. Posting Write Data

5.2.1. Memory Write and Invalidate Usage

5.2.1.1. Forwarding Memory Write and Invalidate

Transactions

5.2.1.2. Promoting Memory Write Transactions

5.2.1.3. Combining Memory Write Transactions

5.2.1.4. Memory Write and Invalidate Disconnects

5.2.1.4.1. Master Disconnected by the Bridge

5.2.1.4.2. Bridge Disconnected by the Target

5.3. Delayed Transactions

5.3.1. Discarding a Delayed Request

5.3.2. Discarding a Delayed Completion

5.4. Exclusive Access Transactions

5.4.1. Delayed Lock-Request Error

5.4.2. Normal Completion

5.5. Ordering Requirements

5.5.1. Summary of PCI Ordering Requirements

5.5.1.1. General Requirements

5.5.1.2. Delayed Transaction Requirements

5.5.2. Ordering of Requests

5.5.3. Ordering of Delayed Transactions

5.5.4. Transactions That Have No Ordering Constraints

5.5.5. Delayed Transactions and LOCK#

5.5.6. Error Conditions

5.5.7. Illustrations of the Use of the Ordering Rules

5.6. Special Design Considerations

5.6.1. Read Starvation

5.6.2. Stale Data

5.6.3. Deadlocks

5.7. Combining Separate Writes Into a Single Burst Transaction

5.8. Merging Separate Writes Into a Single Transaction

5.9. Collapsing of Writes

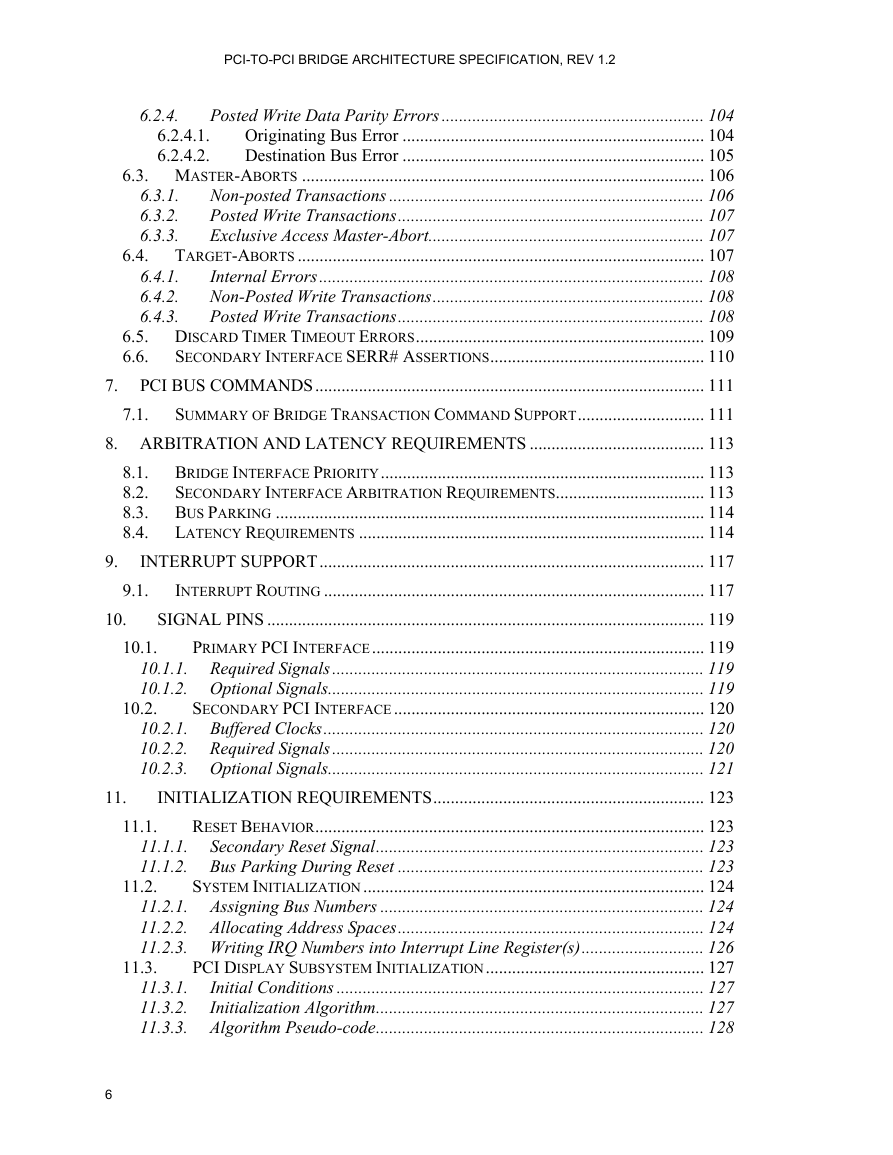

6. Error Support

6.1. Introduction

6.2. Parity Errors

6.2.1. Address Parity Errors

6.2.2. Read Data Parity Errors

6.2.2.1. Target Completion Error

6.2.2.2. Master Completion Error

6.2.3. Non-Posted Write Data Parity Errors

6.2.3.1. Master Request Error

6.2.3.2. Target Completion Error

6.2.3.3. Master Completion Error

6.2.4. Posted Write Data Parity Errors

6.2.4.1. Originating Bus Error

6.2.4.2. Destination Bus Error

6.3. Master-Aborts

6.3.1. Non-posted Transactions

6.3.2. Posted Write Transactions

6.3.3. Exclusive Access Master-Abort

6.4. Target-Aborts

6.4.1. Internal Errors

6.4.2. Non-Posted Write Transactions

6.4.3. Posted Write Transactions

6.5. Discard Timer Timeout Errors

6.6. Secondary Interface SERR# Assertions

7. PCI Bus Commands

7.1. Summary of Bridge Transaction Command Support

8. Arbitration and Latency Requirements

8.1. Bridge Interface Priority

8.2. Secondary Interface Arbitration Requirements

8.3. Bus Parking

8.4. Latency Requirements

9. Interrupt Support

9.1. Interrupt Routing

10. Signal Pins

10.1. Primary PCI Interface

10.1.1. Required Signals

10.1.2. Optional Signals

10.2. Secondary PCI Interface

10.2.1. Buffered Clocks

10.2.2. Required Signals

10.2.3. Optional Signals

11. Initialization Requirements

11.1. Reset Behavior

11.1.1. Secondary Reset Signal

11.1.2. Bus Parking During Reset

11.2. System Initialization

11.2.1. Assigning Bus Numbers

11.2.2. Allocating Address Spaces

11.2.3. Writing IRQ Numbers into Interrupt Line Register( s)

11.3. PCI Display Subsystem Initialization

11.3.1. Initial Conditions

11.3.2. Initialization Algorithm

11.3.3. Algorithm Pseudo-code

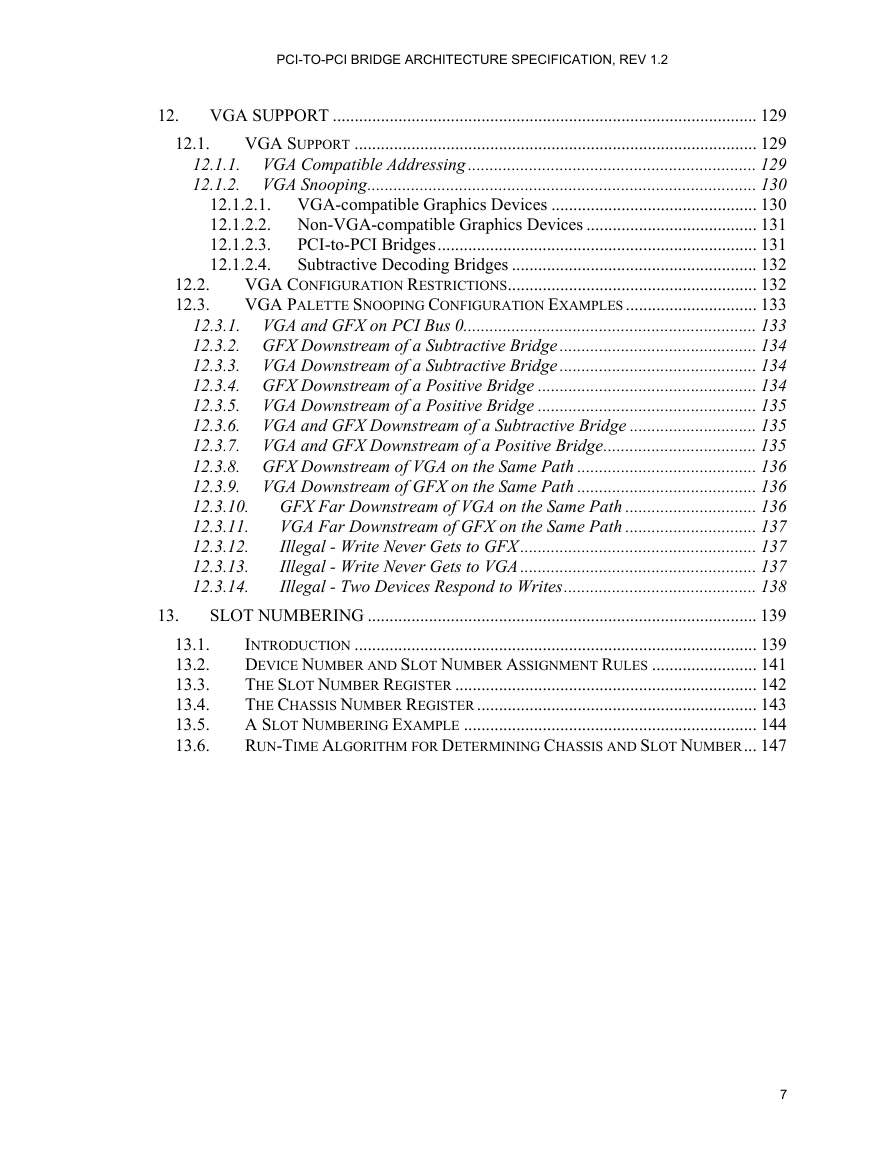

12. VGA Support

12.1. VGA Support

12.1.1. VGA Compatible Addressing

12.1.2. VGA Snooping

12.1.2.1. VGA-compatible Graphics Devices

12.1.2.2. Non-VGA-compatible Graphics Devices

12.1.2.3. PCI-to-PCI Bridges

12.1.2.4. Subtractive Decoding Bridges

12.2. VGA Configuration Restrictions

12.3. VGA Palette Snooping Configuration Examples

12.3.1. VGA and GFX on PCI Bus 0

12.3.2. GFX Downstream of a Subtractive Bridge

12.3.3. VGA Downstream of a Subtractive Bridge

12.3.4. GFX Downstream of a Positive Bridge

12.3.5. VGA Downstream of a Positive Bridge

12.3.6. VGA and GFX Downstream of a Subtractive Bridge

12.3.7. VGA and GFX Downstream of a Positive Bridge

12.3.8. GFX Downstream of VGA on the Same Path

12.3.9. VGA Downstream of GFX on the Same Path

12.3.10. GFX Far Downstream of VGA on the Same Path

12.3.11. VGA Far Downstream of GFX on the Same Path

12.3.12. Illegal - Write Never Gets to GFX

12.3.13. Illegal - Write Never Gets to VGA

12.3.14. Illegal - Two Devices Respond to Writes

13. Slot Numbering

13.1. Introduction

13.2. Device Number and Slot Number Assignment Rules

13.3. The Slot Number Register

13.4. The Chassis Number Register

13.5. A Slot Numbering Example

13.6. Run-Time Algorithm for Determining Chassis and Slot Number

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc