SPI 接口简介

作者: 未知 时间: 2007-10-12 08:34:59

来自:网上转载 浏览次数: 1132 文字大小: 【大 】【中 】

【小 】

这几天碰到了使用 SPI 接口的 flash, 才知道 flash 还可以是串行的 ,看来以前真是井底之蛙啊 ,找了一些 SP

I 接口的资料都不全 ,后来找到一点英文资料 ,翻译了一下 , 加上我的个人理解 ,凑成一篇了 ,希望对初学者有

点帮助。

SPI 接口的全称是 "Serial Peripheral Interface",

意为串行外围接口 ,是 Motorola 首先在其 MC68H

CXX 系列处理器上定义的。 SPI 接口主要应用在 EEPROM,FLASH, 实时时钟 ,AD 转换器 , 还有数字信号处

理器和数字信号解码器之间。

SPI 接口是在 CPU 和外围低速器件之间进行同步串行数据传输

,在主器件的移位脉冲下 ,数据按位传输 ,

高位在前 ,地位在后 , 为全双工通信 ,数据传输速度总体来说比 I2C 总线要快 ,速度可达到几 Mbps 。

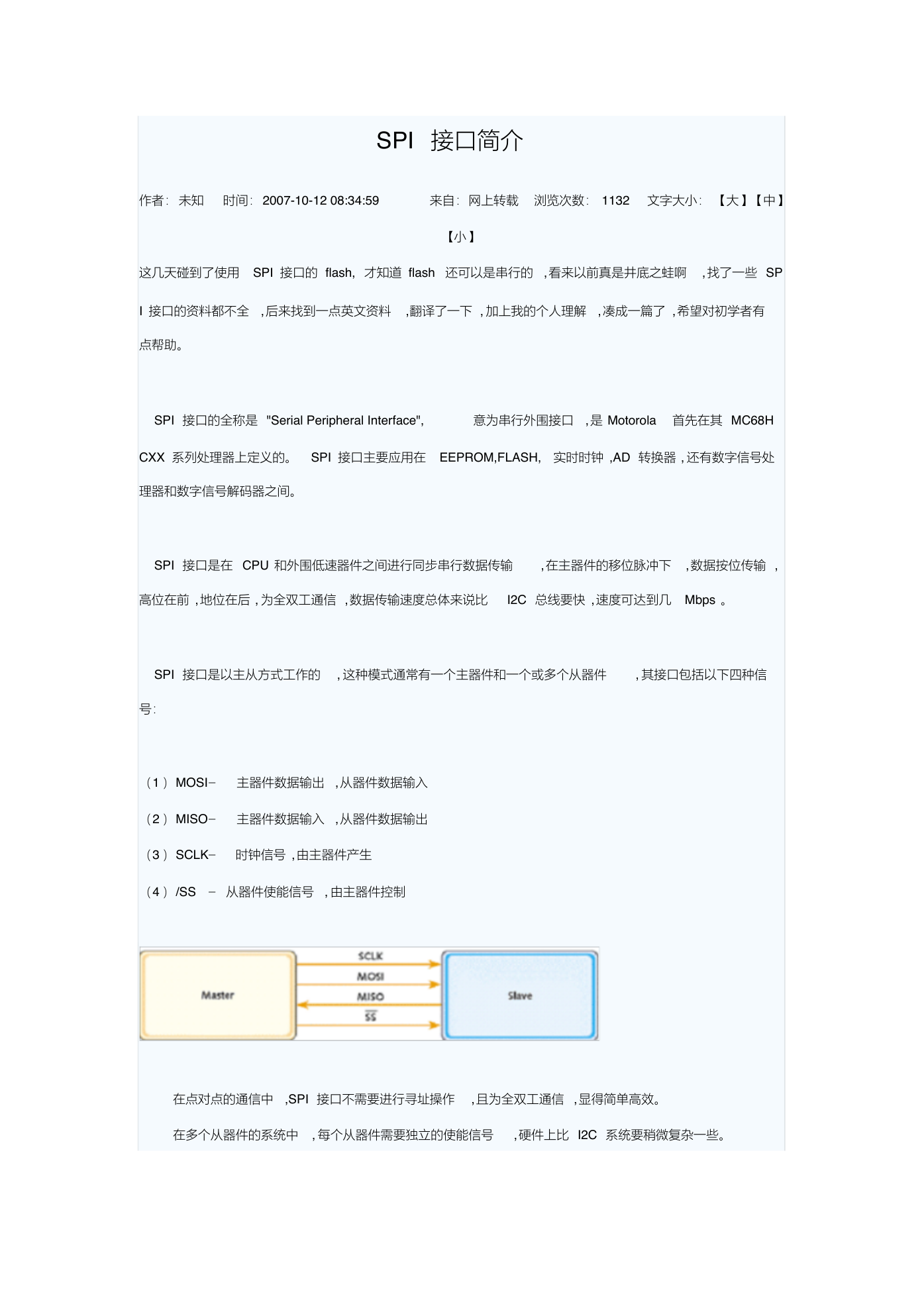

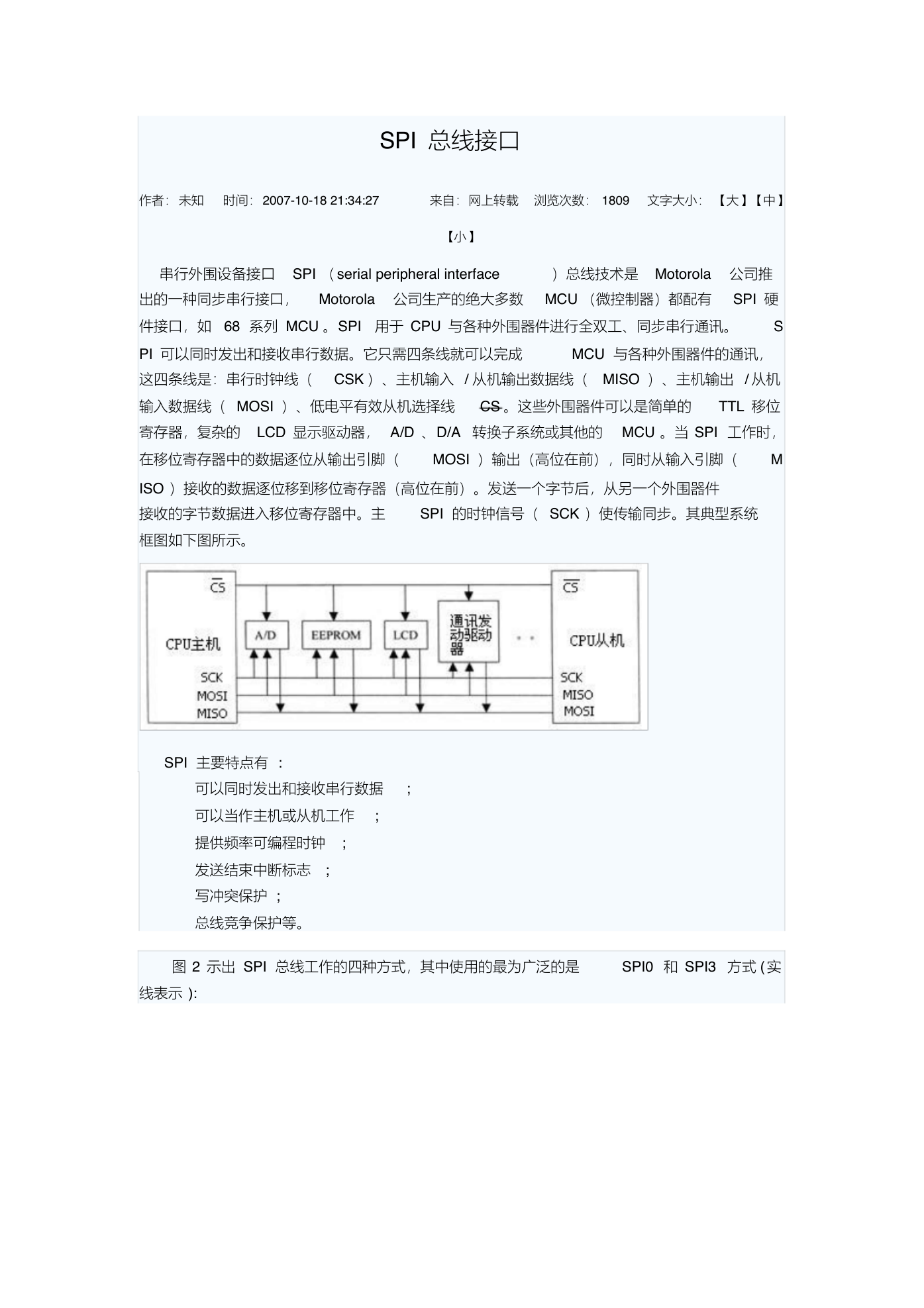

SPI 接口是以主从方式工作的 , 这种模式通常有一个主器件和一个或多个从器件

, 其接口包括以下四种信

号:

(1 )MOSI – 主器件数据输出 ,从器件数据输入

(2 )MISO – 主器件数据输入 ,从器件数据输出

(3 )SCLK – 时钟信号 ,由主器件产生

(4 )/SS – 从器件使能信号 , 由主器件控制

在点对点的通信中 ,SPI 接口不需要进行寻址操作 ,且为全双工通信 ,显得简单高效。

在多个从器件的系统中 , 每个从器件需要独立的使能信号 ,硬件上比 I2C 系统要稍微复杂一些。

�

SPI 接口在内部硬件实际上是两个简单的移位寄存器

, 传输的数据为 8 位,在主器件产生的从器件使能

信号和移位脉冲下 ,按位传输 , 高位在前 ,低位在后。如下图所示 ,在 SCLK 的下降沿上数据改变 , 同时一位数

据被存入移位寄存器。

SPI 接口内部硬件图示:

最后 ,SPI 接口的一个缺点:没有指定的流控制 , 没有应答机制确认是否接收到数据。

�

SPI 接口单线应用

作者: 未知 时间: 2007-10-18 21:39:24

来自:网上转载 浏览次数: 1477 文字大小: 【大 】【中 】

1 SPI 通信

SPI 信号线 : 一般的 SPI 接口使用 4 条信号线与外围设备接口,其具体功能如下:

【小 】

SCLOCK : 主机的时钟线, 为数据的发送和接收提供同步时钟信号。

每一位数据的

传输都需要 1 次时钟作用, 因而发送或接收 1 个字节的数据都需要 8 个时钟作用。主

机的时钟可以通过固件进行设置,并和从机的时钟线相连。

MISO :主机输入 / 从机输出数据线。主机的 MOSO 应与从机的发送数据端相连,

进行高位在前的数据交换。

SS :低电平有效的从机选择线。当该线置低时,才能跟从机进行通信。

SPI 工作模式 :SPI 的工作模式分为:主模式和从模式。

主模式的特点是不论发送还是接收始终有

SCLOCK 信号, SS 信号不是必需的,

由于 SPI 只能有一个主机, 因而不存在主机的选择问题。

从模式的特点是无论发送还是接收必须在时钟信号

SCLOCK 的作用下才能进行, 并

且 SS 信号必须有效。

不论是在主模式下还是在从模式下,都要在时钟极性和时钟相位的配合下才能有效

的完成一次数据传输。

2 SPI 接口的单线应用

在标准的 SPI 接口间进行通信时, SPI 总线的四条信号线中: 主机 SCLOCK 与从机 S

CLOCK 相连; 主机 MISO 与从机 MOSI 相连;主机 MOSI

与从机 MISO 相连; 主机控制信号线与从机的 SS 相连。在 SPI 接口与非标准接口进行

通信时,例如与有的串行 RAM 接口,由于双向 I/O 数据线只有一条,时钟和片选信号线

都有,那么如何利用 SPI 的高速特性进行数据的读出和写入呢

?

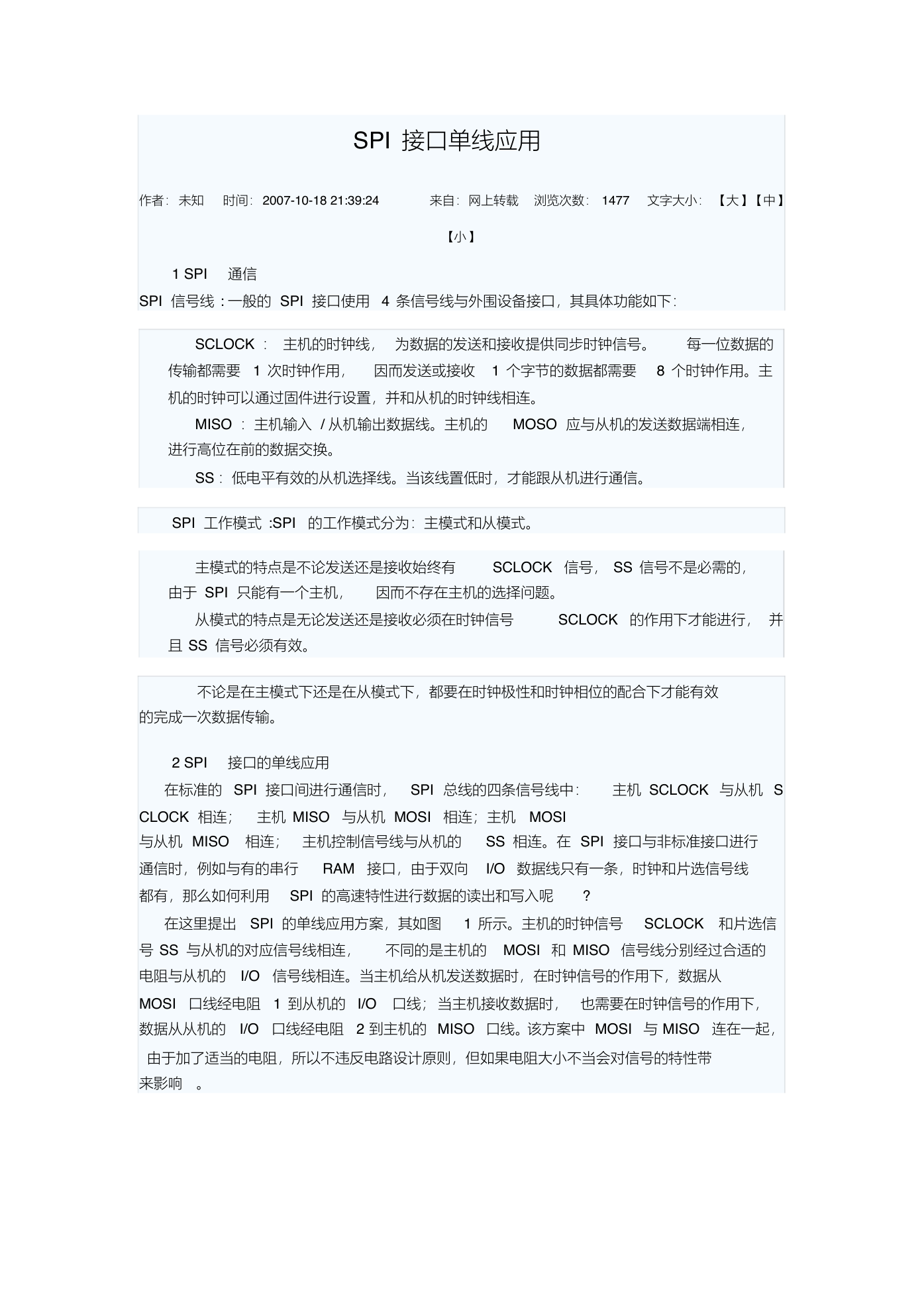

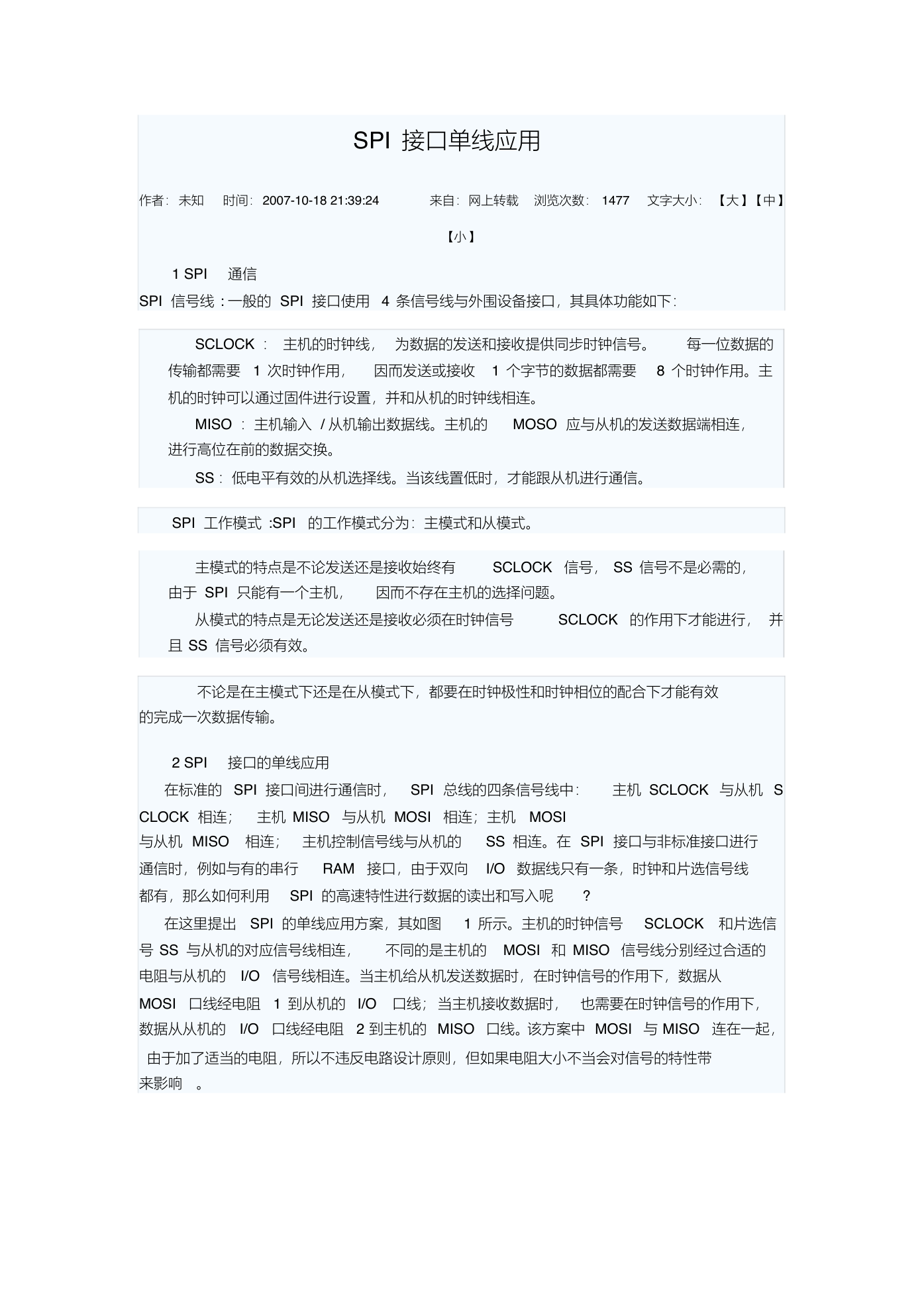

在这里提出 SPI 的单线应用方案,其如图 1 所示。主机的时钟信号 SCLOCK 和片选信

号 SS 与从机的对应信号线相连, 不同的是主机的 MOSI 和 MISO 信号线分别经过合适的

电阻与从机的 I/O 信号线相连。当主机给从机发送数据时,在时钟信号的作用下,数据从

MOSI 口线经电阻 1 到从机的 I/O 口线; 当主机接收数据时, 也需要在时钟信号的作用下,

数据从从机的 I/O 口线经电阻 2 到主机的 MISO 口线。该方案中 MOSI 与 MISO 连在一起,

由于加了适当的电阻,所以不违反电路设计原则,但如果电阻大小不当会对信号的特性带

来影响 。

�

图 1 SPI 单线应用方案

3 SPI 接口的单线应用举例

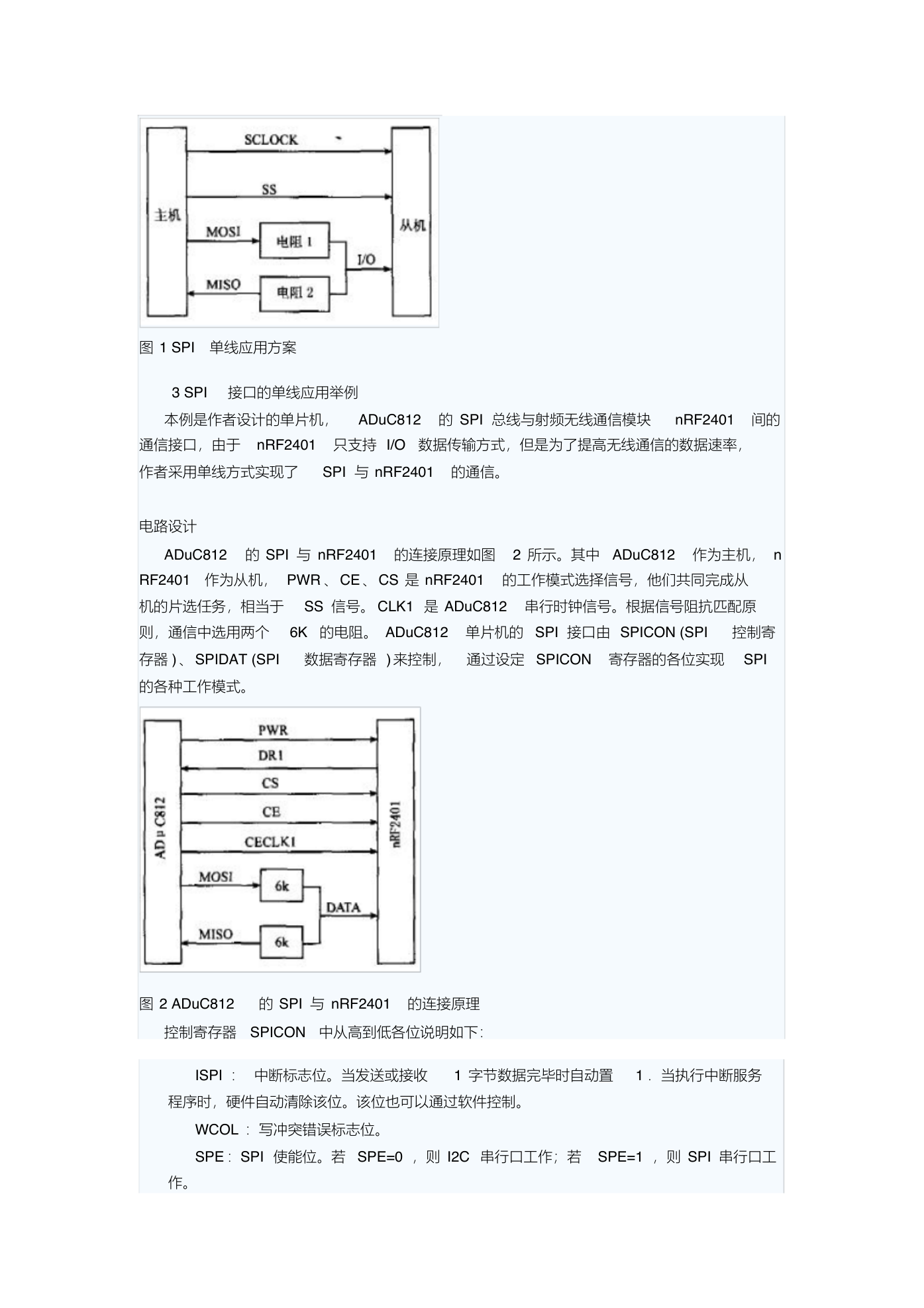

本例是作者设计的单片机, ADuC812 的 SPI 总线与射频无线通信模块 nRF2401 间的

通信接口,由于 nRF2401 只支持 I/O 数据传输方式,但是为了提高无线通信的数据速率,

作者采用单线方式实现了 SPI 与 nRF2401 的通信。

电路设计

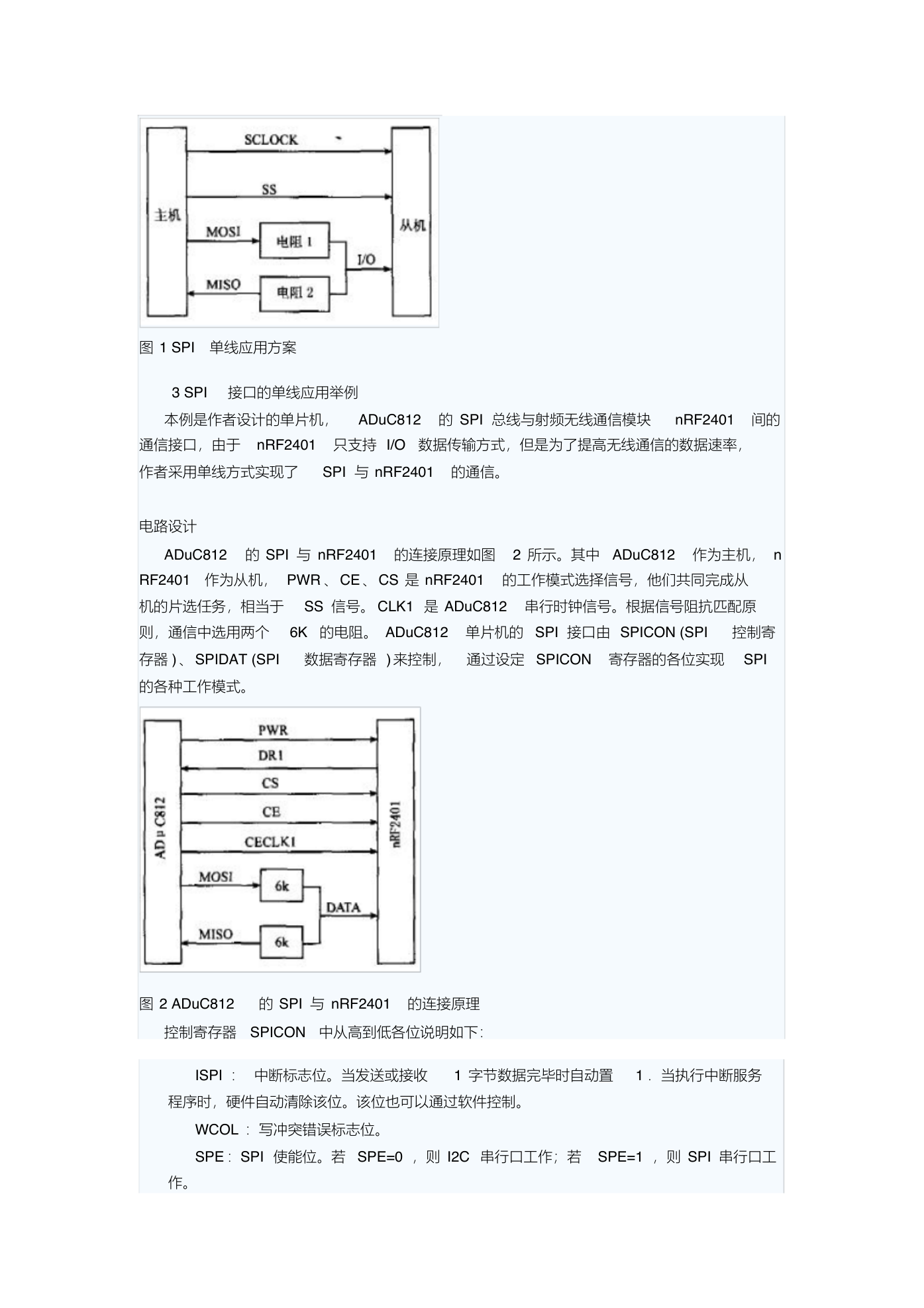

ADuC812 的 SPI 与 nRF2401 的连接原理如图 2 所示。其中 ADuC812 作为主机, n

RF2401 作为从机, PWR 、 CE 、 CS 是 nRF2401 的工作模式选择信号,他们共同完成从

机的片选任务,相当于 SS 信号。 CLK1 是 ADuC812 串行时钟信号。根据信号阻抗匹配原

则,通信中选用两个 6K 的电阻。 ADuC812 单片机的 SPI 接口由 SPICON (SPI 控制寄

存器 ) 、 SPIDAT (SPI 数据寄存器 ) 来控制, 通过设定 SPICON 寄存器的各位实现 SPI

的各种工作模式。

图 2 ADuC812 的 SPI 与 nRF2401 的连接原理

控制寄存器 SPICON 中从高到低各位说明如下:

ISPI : 中断标志位。当发送或接收 1 字节数据完毕时自动置 1 .当执行中断服务

程序时,硬件自动清除该位。该位也可以通过软件控制。

WCOL :写冲突错误标志位。

SPE :SPI 使能位。若 SPE=0 ,则 I2C 串行口工作;若 SPE=1 ,则 SPI 串行口工

作。

�

SPIM :主模式选择位。若 SPIM=0 ,则 SPI 工作于从模式;若 SPIM=1 ,则 SPI

工作于主模式。

CPOL :时钟极性选择位。 CPOL=0 ,在主机时钟下降沿时读取数据,各数据字节

之间传输时,时钟处于高电平空闲状态;

CPOL=1 ,在主机时钟上升沿时读取数据,各

数据字节之间传输时,时钟处于低电平空闲状态。

CPHA ;时钟相位选择位。 CPHA=0 ,传输数据的最高位在 SS 的下降沿出现,在

时钟第 1 个前沿读入,之后的下一个数据位在时钟后沿出现,

在下一个前沿读入,直到 8 位数据读完; CPHA=1 ,传输数据在时钟前沿出现,在同

一时钟周期的后沿读入。

SPR1 、 SPR0 :SPI 波特率选择位。

接口程序设计 固件程序主要包括: SPI 口初始化程序 INITSPI ,送数据程序 SEN

DDATA ,接收数据程 RECEIVEDATA 。

在 SPI 初始化程序中,控制寄存器 SPICON 设置为 33H , 即 CPOL=0 ,CPHA=0 ,

当设置 CPOL= 1 , CPHA=1 时, 由于干扰脉冲的存在,

ADuC812 与 NRF2401 不能很好的同步。

在发送数据子程序中,向数据寄存器

SPIDAT 写数据,如产生中断标志,说明数据传输

完毕,则可以发送下一个数据。

在接收子程序中, 由于 nRF2401 送数据的时钟是由 ADuC812 的 SCLOCK 产生的,

所以执行接收数据指令 MOVA , SPIDAT 时先要对数据寄存器 SPIDAT 写数据 0 ,也就

是执行指令 MOVA,SPIDAT ,其目的是为了产生接收数据时的时钟信号,

当单片机向 SPI

DAT 写数据 0 时, nRF2401 通过 DATA 口向单片机送数据,改写 SPIDAT 的内容,这

就是所接收的数据。

SPI 单线方案在实际应用应注意以下问题:

(1) 时钟相位与时钟极性的设置。 其设置要跟从机的数据读写时序相一致,

意干扰问题。

在一致时也要注

(2) 所加电阻值的大小。阻值的大小关系到信号传输的阻抗匹配问题,同时也影响数据传输

的速率,所以在选用电阻时一般取几

K 的电阻 .

�

SPI 总线接口

作者: 未知 时间: 2007-10-18 21:34:27

来自:网上转载 浏览次数: 1809 文字大小: 【大 】【中 】

【小 】

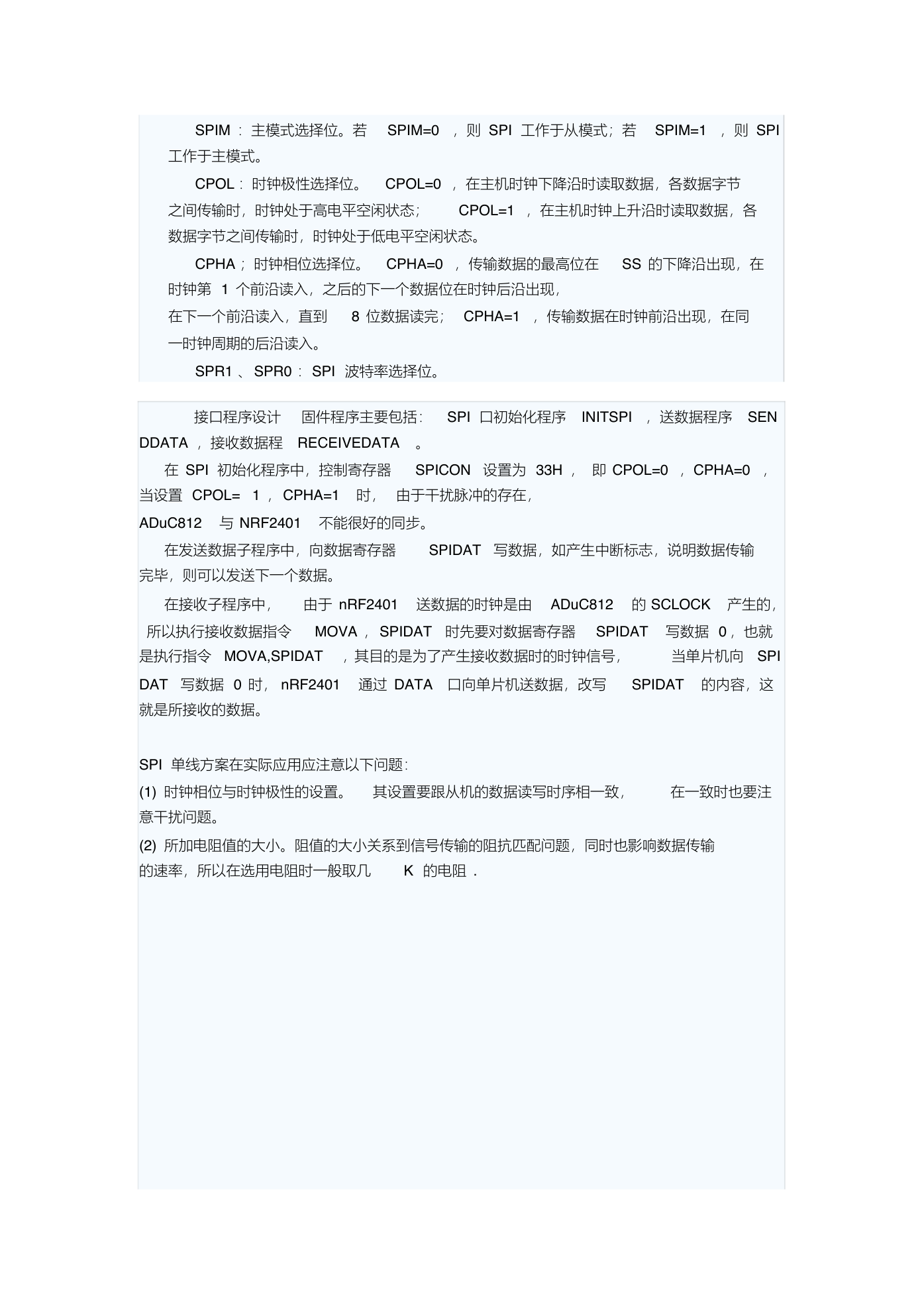

串行外围设备接口 SPI ( serial peripheral interface

)总线技术是 Motorola 公司推

出的一种同步串行接口, Motorola 公司生产的绝大多数 MCU (微控制器)都配有 SPI 硬

件接口,如 68 系列 MCU 。SPI 用于 CPU 与各种外围器件进行全双工、同步串行通讯。

S

PI 可以同时发出和接收串行数据。它只需四条线就可以完成

MCU 与各种外围器件的通讯,

这四条线是:串行时钟线( CSK )、主机输入 / 从机输出数据线( MISO )、主机输出 / 从机

输入数据线( MOSI )、低电平有效从机选择线 CS 。这些外围器件可以是简单的 TTL 移位

寄存器,复杂的 LCD 显示驱动器, A/D 、D/A 转换子系统或其他的 MCU 。当 SPI 工作时,

在移位寄存器中的数据逐位从输出引脚(

MOSI )输出(高位在前),同时从输入引脚(

M

ISO )接收的数据逐位移到移位寄存器(高位在前)。发送一个字节后,从另一个外围器件

接收的字节数据进入移位寄存器中。主

SPI 的时钟信号( SCK )使传输同步。其典型系统

框图如下图所示。

SPI 主要特点有 :

可以同时发出和接收串行数据 ;

可以当作主机或从机工作 ;

提供频率可编程时钟 ;

发送结束中断标志 ;

写冲突保护 ;

总线竞争保护等。

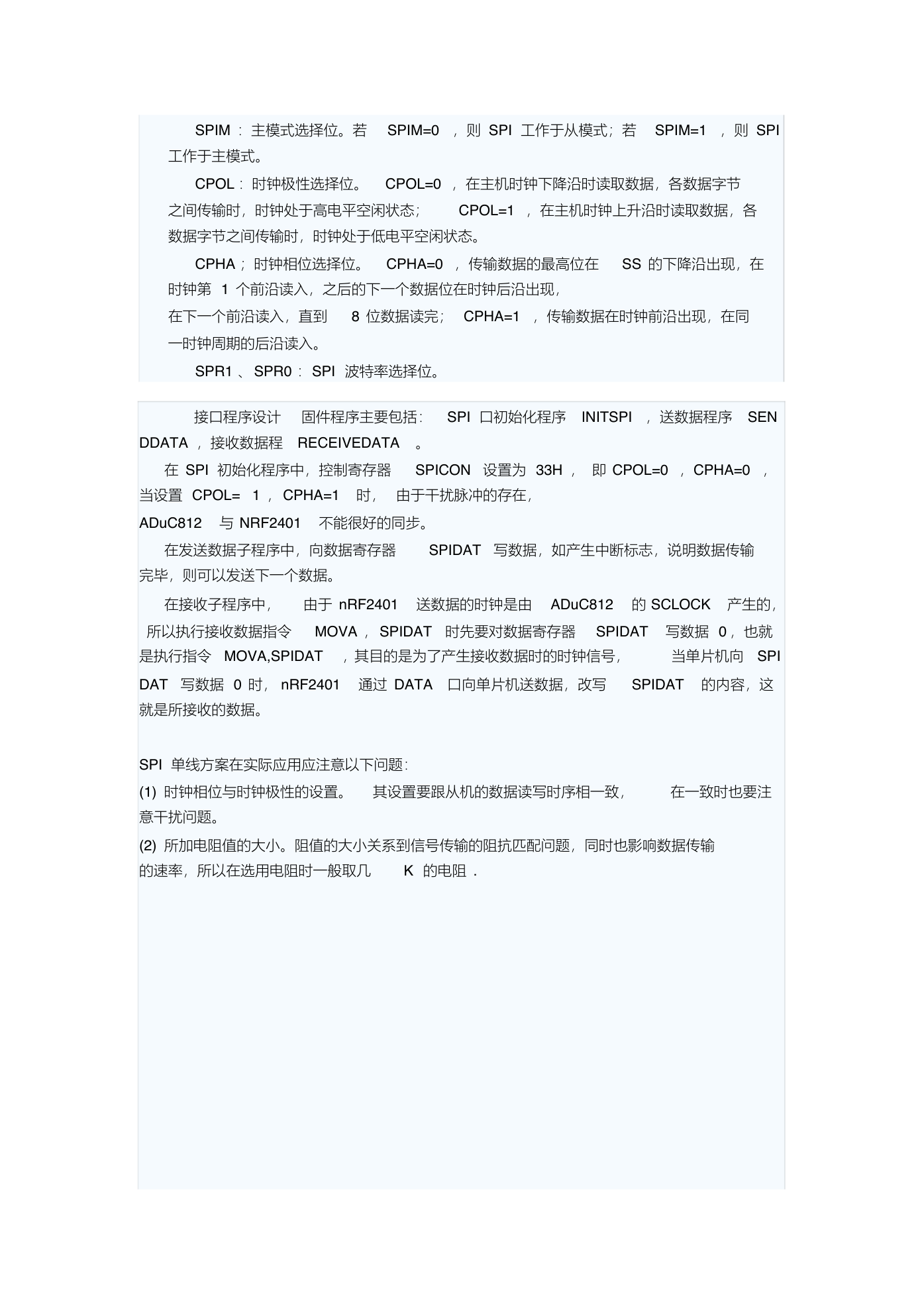

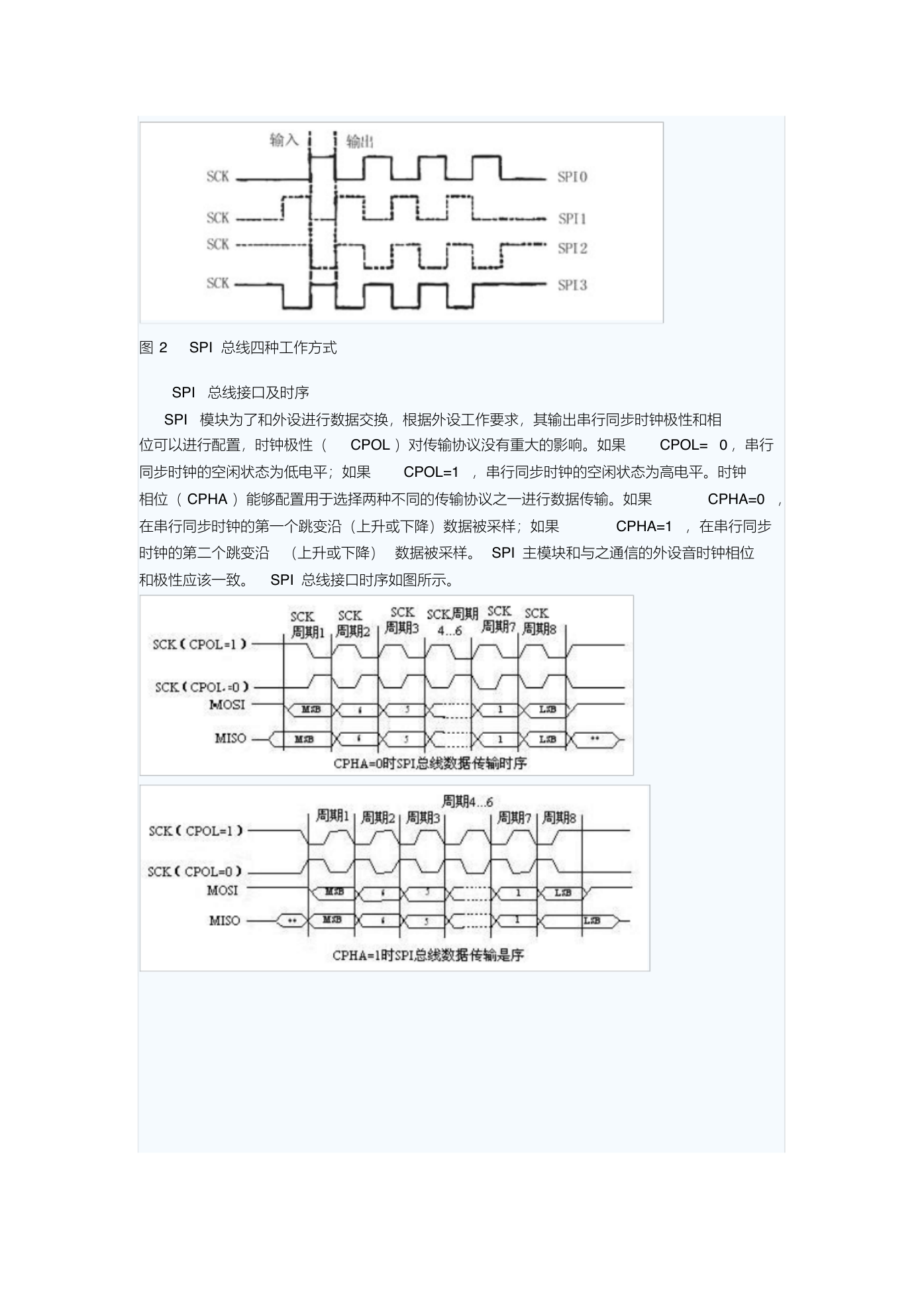

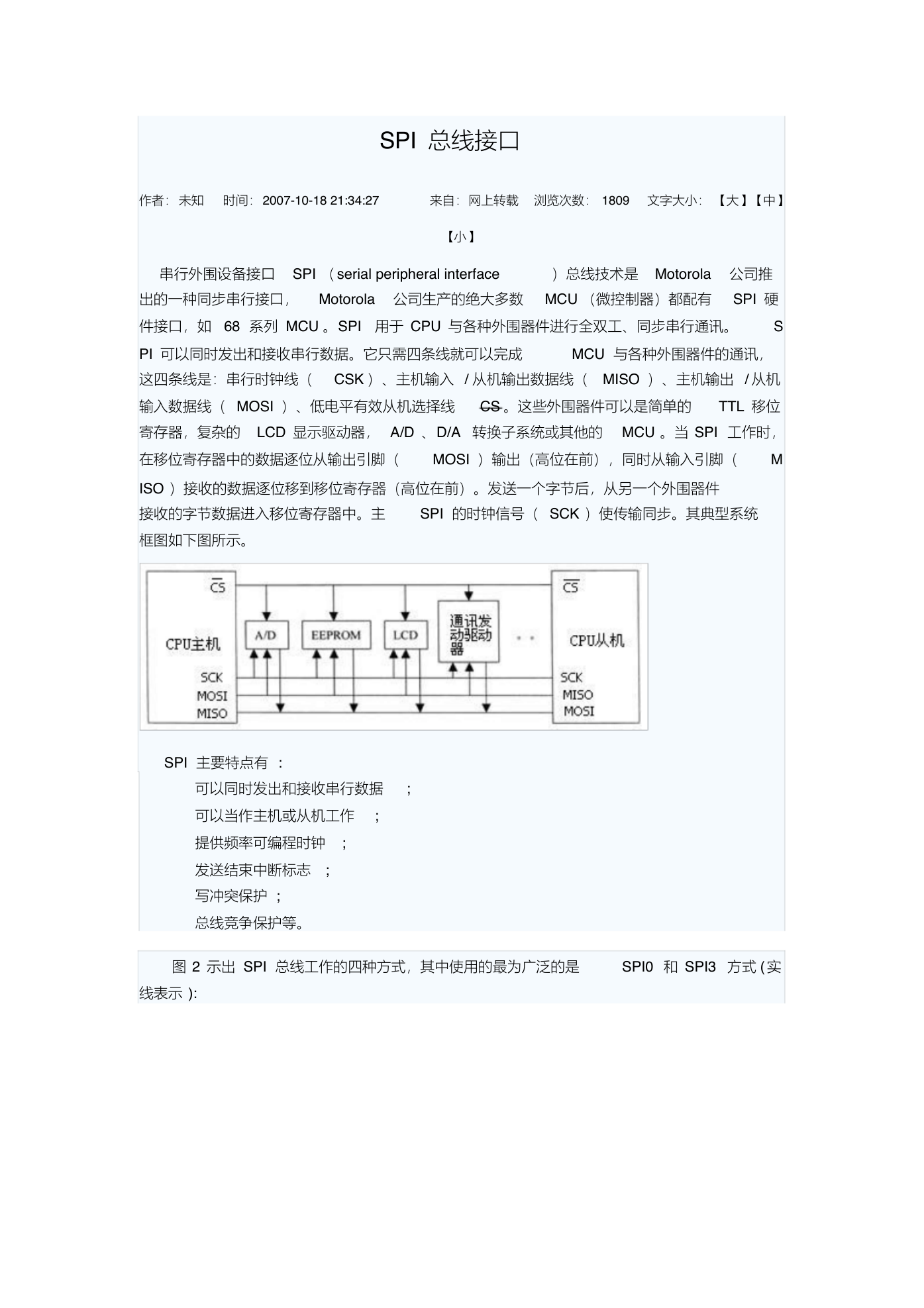

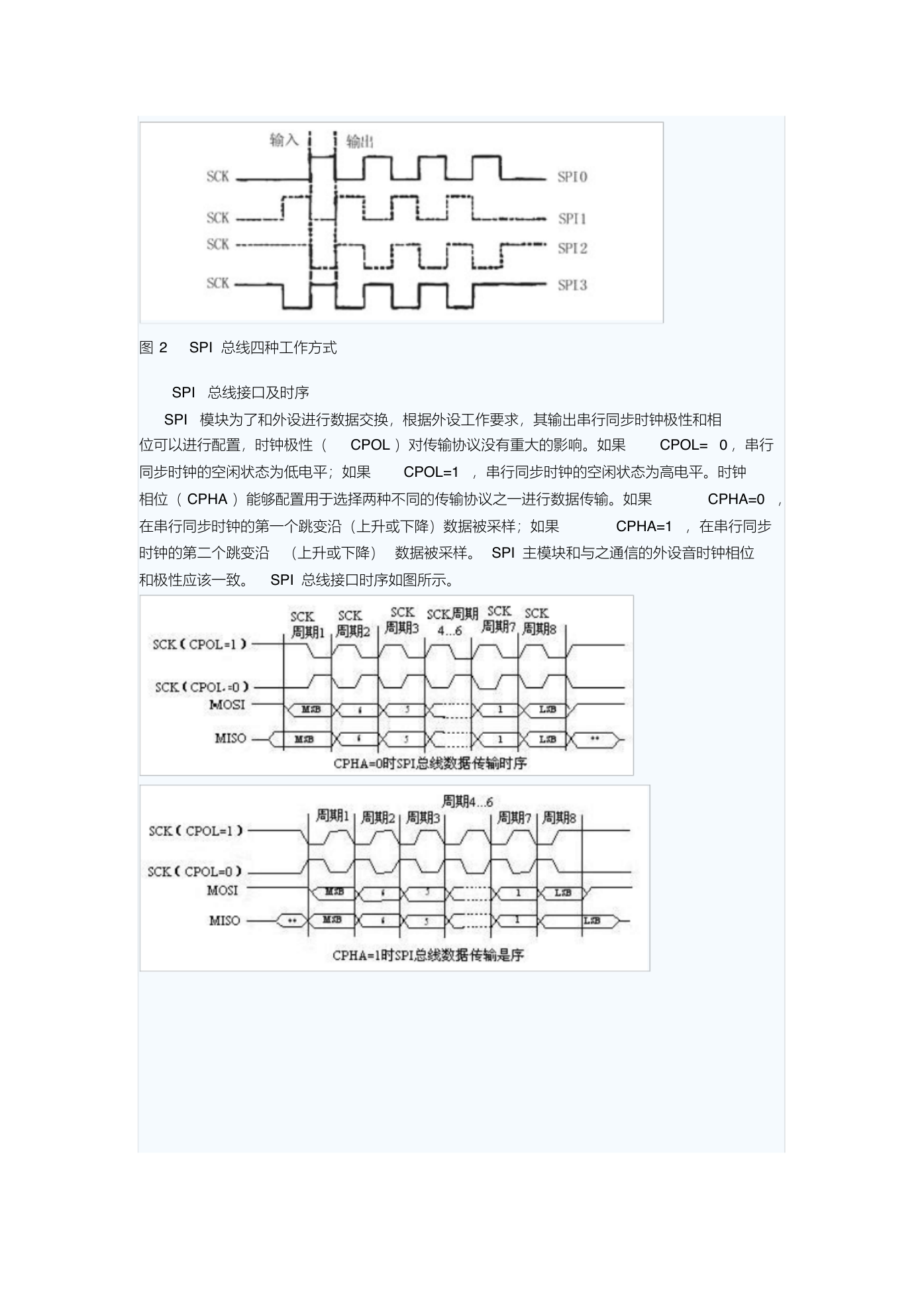

图 2 示出 SPI 总线工作的四种方式,其中使用的最为广泛的是

SPI0 和 SPI3 方式 ( 实

线表示 ):

�

图 2 SPI 总线四种工作方式

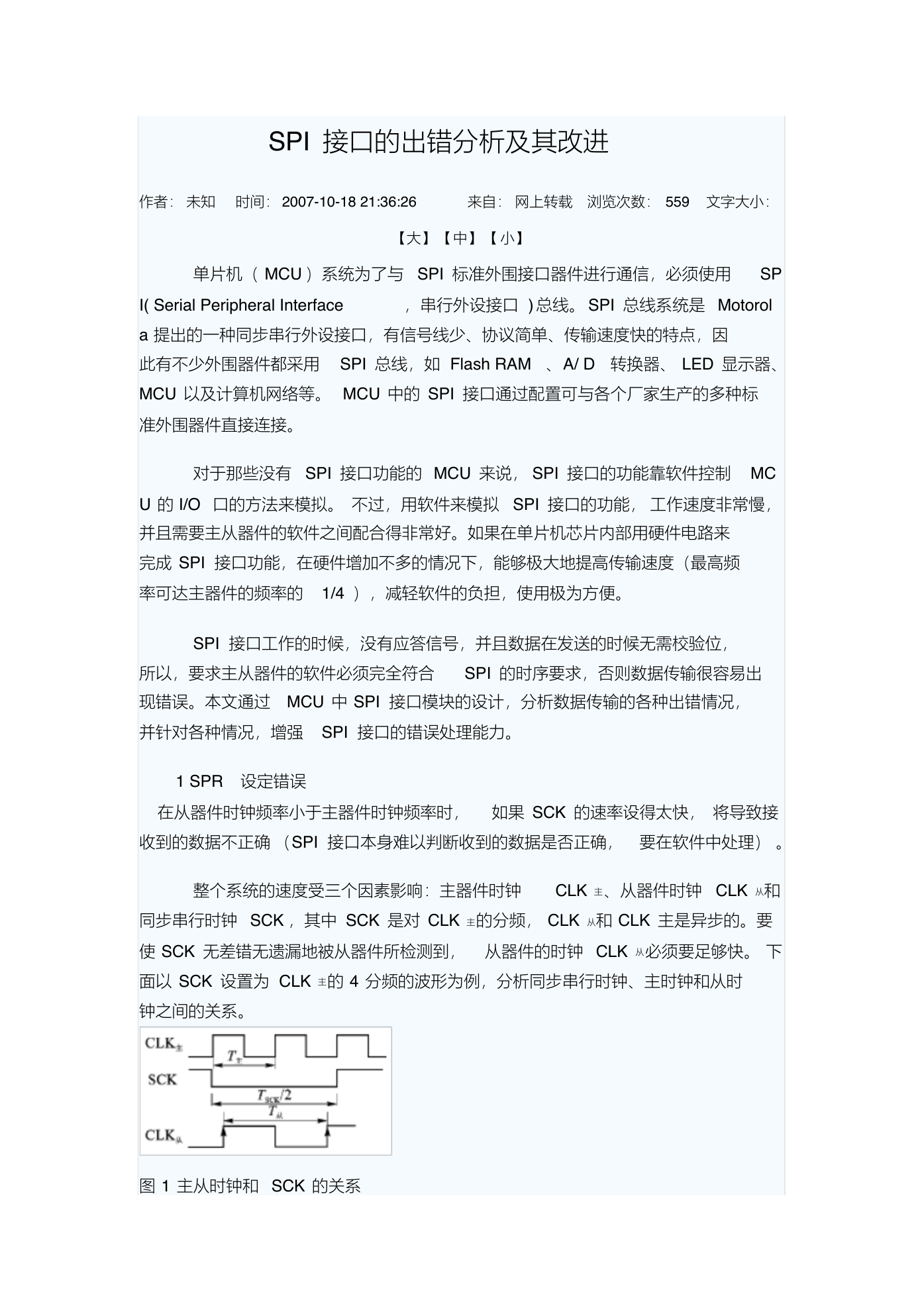

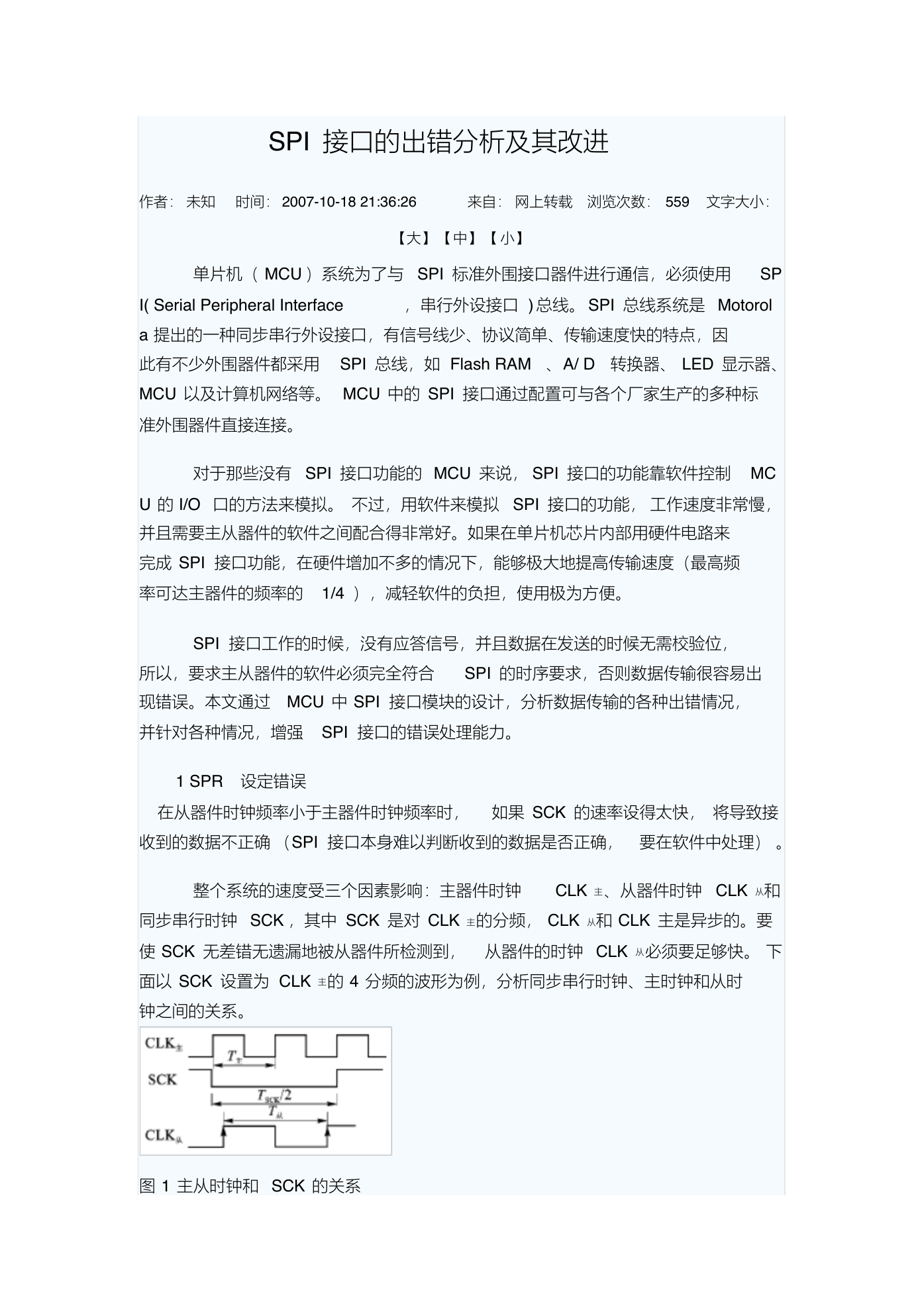

SPI 总线接口及时序

SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相

位可以进行配置,时钟极性( CPOL )对传输协议没有重大的影响。如果

CPOL= 0 ,串行

同步时钟的空闲状态为低电平;如果

CPOL=1 ,串行同步时钟的空闲状态为高电平。时钟

相位( CPHA )能够配置用于选择两种不同的传输协议之一进行数据传输。如果

CPHA=0 ,

在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果

CPHA=1 ,在串行同步

时钟的第二个跳变沿 (上升或下降) 数据被采样。 SPI 主模块和与之通信的外设音时钟相位

和极性应该一致。 SPI 总线接口时序如图所示。

�

SPI 接口的出错分析及其改进

作者: 未知 时间: 2007-10-18 21:36:26

来自: 网上转载 浏览次数: 559 文字大小:

【大】【 中】【 小】

单片机( MCU )系统为了与 SPI 标准外围接口器件进行通信,必须使用 SP

I( Serial Peripheral Interface

,串行外设接口 ) 总线。 SPI 总线系统是 Motorol

a 提出的一种同步串行外设接口,有信号线少、协议简单、传输速度快的特点,因

此有不少外围器件都采用 SPI 总线,如 Flash RAM 、A/ D 转换器、 LED 显示器、

MCU 以及计算机网络等。 MCU 中的 SPI 接口通过配置可与各个厂家生产的多种标

准外围器件直接连接。

对于那些没有 SPI 接口功能的 MCU 来说, SPI 接口的功能靠软件控制 MC

U 的 I/O 口的方法来模拟。 不过,用软件来模拟 SPI 接口的功能, 工作速度非常慢,

并且需要主从器件的软件之间配合得非常好。如果在单片机芯片内部用硬件电路来

完成 SPI 接口功能,在硬件增加不多的情况下,能够极大地提高传输速度(最高频

率可达主器件的频率的 1/4 ),减轻软件的负担,使用极为方便。

SPI 接口工作的时候,没有应答信号,并且数据在发送的时候无需校验位,

所以,要求主从器件的软件必须完全符合 SPI 的时序要求,否则数据传输很容易出

现错误。本文通过 MCU 中 SPI 接口模块的设计,分析数据传输的各种出错情况,

并针对各种情况,增强 SPI 接口的错误处理能力。

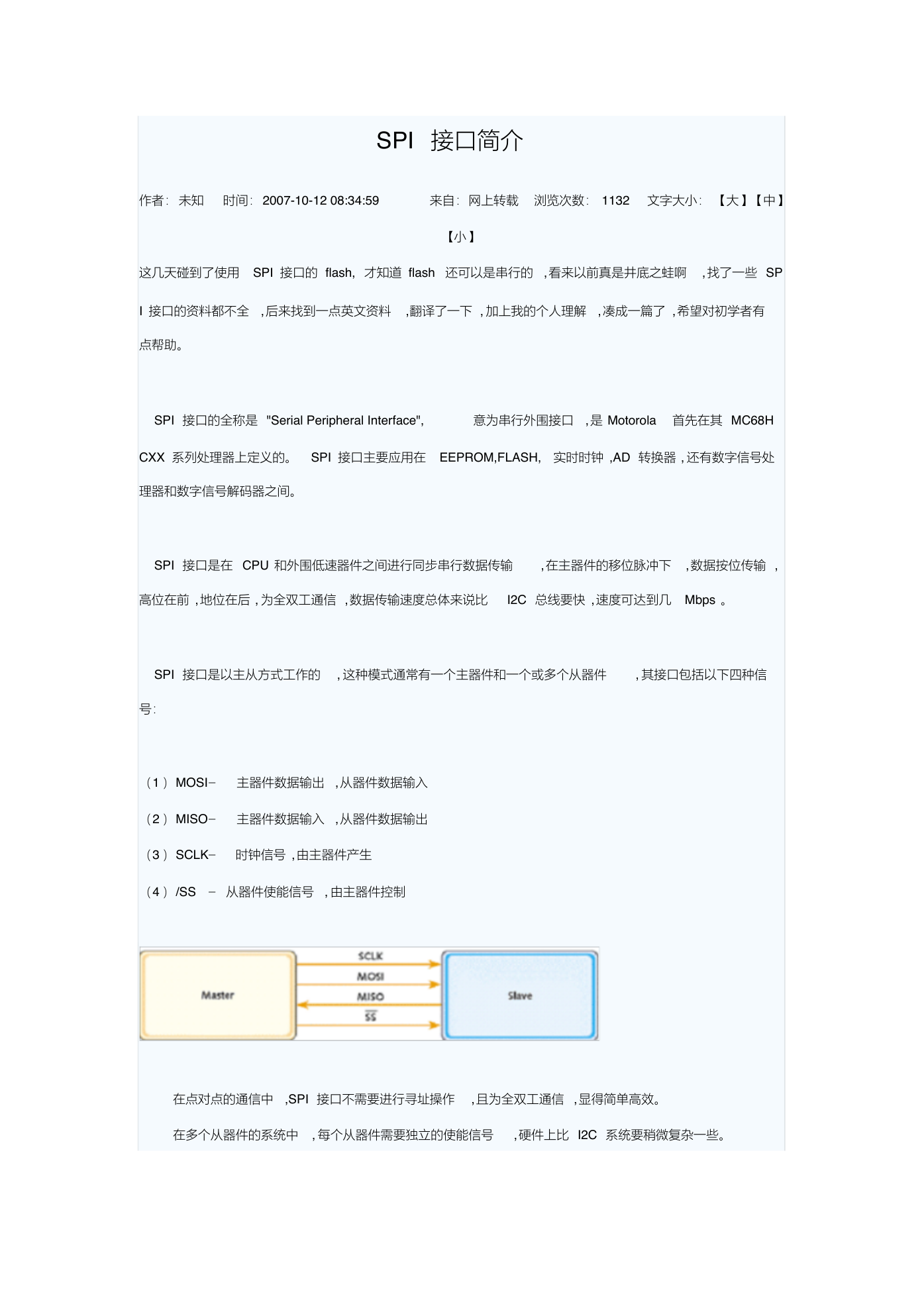

1 SPR 设定错误

在从器件时钟频率小于主器件时钟频率时, 如果 SCK 的速率设得太快, 将导致接

收到的数据不正确 (SPI 接口本身难以判断收到的数据是否正确, 要在软件中处理) 。

整个系统的速度受三个因素影响:主器件时钟

CLK 主、从器件时钟 CLK 从和

同步串行时钟 SCK ,其中 SCK 是对 CLK 主的分频, CLK 从和 CLK 主是异步的。要

使 SCK 无差错无遗漏地被从器件所检测到, 从器件的时钟 CLK 从必须要足够快。 下

面以 SCK 设置为 CLK 主的 4 分频的波形为例,分析同步串行时钟、主时钟和从时

钟之间的关系。

图 1 主从时钟和 SCK 的关系

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc