卷积码的编解码 Matlab 仿真

摘要

卷积码是一种性能优越的信道编码。它的编码器和译码器都比较容易实现,

同时它具有较强的纠错能力。随着纠错编码理论研究的不断深入,卷积码的实际

应用越来越广泛。本文简明地介绍了卷积码的编码原理和译码原理。并在

SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的

模块仿真。最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积

码的这些参数对卷积码的误码性能的影响。经过仿真和实测,并对测试结果作了

分析。得出了以下三个结论:

(1)当改变卷积码的码率时,系统的误码性能也将随之发生变化。

(2)对于码率一定的卷积码,当约束长度N 发生变化时,系统的误码性能

也会随之发生变化。

(3)回溯长度也会不同程度上地影响误码性能。

关键词:卷积码;码率;约束长度;回溯长度

�

Simulation and Research on Encoding and Decoding of

Convolution Code

Abstract

Convolution code has a superior performance of the channel code. It is easy to

coding and decoding. And it has a strong ability to correct errors. As correcting coding

theory has a long development, the practice of convolution code is more and more

extensive. In this thesis,

the principle of convolution coding and decoding is

introduced simply firstly. Then the whole simulation module process of encoding,

decoding and the Error Rate Calculation is completed in this design. Finally, in order

to understand their performances of error rate, many changes in parameters of

convolution code are calculated in the simulation process. After simulation and

measure, an analysis of test results is presented. The following three conclusions are

draw:

(1) When the rate of convolution Code changes, BER performance of the system

will change.

(2) For a certain rate of convolution code, when there is a change in the

constraint length of N, BER performance of the system will change.

(3) Retrospective length will affect BER.

Key words: convolution code; rate; constraint length; retrospective length;

�

目 录

论文总页数:21 页

1 引言 ....................................................................... 1

1.1 课题背景 ............................................................. 1

1.2 国内外研究现状 ....................................................... 1

1.3 本课题的意义 ......................................................... 1

1.4 本课题的研究方法 ..................................................... 1

2 卷积码的基本概念 ........................................................... 2

2.1 信道 ................................................................. 2

2.2 纠错编码 ............................................................. 2

2.3 卷积码的基本概念 ..................................................... 2

2.4 卷积码编码的概念 ..................................................... 2

2.4.1 卷积编码 ....................................................... 2

2.4.2 卷积码的树状图 ................................................. 3

2.4.3 卷积码的网格图 ................................................. 4

2.4.4 卷积码的解析表示 ............................................... 5

3 卷积码的译码 ............................................................... 6

3.1 卷积码译码的概述 ..................................................... 6

3.2 卷积码的最大似然译码 ................................................. 6

3.3 VITEBI 译码的关键步骤 ................................................ 7

3.3.1 输入与同步单元 ................................................. 7

3.3.2 支路量度计算 ................................................... 7

3.3.3 路径量度的存储与更新 ........................................... 7

3.3.4 信息序列的存储与更新 ........................................... 8

3.3.5 判决与输出单元 ................................................. 8

4 结论 ....................................................................... 9

4.1 卷积码的仿真 ......................................................... 9

4.1.1 SIMULINK 仿真模块的参数设置以及重要参数的意义 ...................9

4.2 改变卷积码的参数仿真以及结论 ........................................ 12

4.2.1 不同回溯长度对卷积码性能的影响 ................................ 12

4.2.2 不同码率对卷积码误码性能的响 .................................. 14

4.2.3 不同约束长度对卷积码的误码性能影响 ............................ 15

结 论 ..................................................................... 17

参考文献 .................................................................... 18

致

谢 ............................................................. 错误!未定义书签。

明 ............................................................. 错误!未定义书签。

声

�

1 引言

1.1 课题背景

随着现代通信的发展,高速信息传输和高可靠性传输成为信息传输的两个主

要方面,而可靠性尤其重要。卷积码以其高速性和可靠性在实际应用中越来越广

泛。1967年Viterbi译码算法的提出,使卷积码成为信道编码中最重要的编码方

式之一[1]。

1.2 国内外研究现状

在对卷积码的研究中,其中编码器较简单,模式也很统一。主要是研究提高

卷积码的译码速度和可靠度。译码算法中最重要的卷积码的Viterbi算法问世以

来,软件仿真和实现都得到了迅速发展。目前,利用计算机仿真Viterbi算法,

模拟在各种不同情况下(使用不同码率、不同约束度等)卷积编码时的译码性能,

寻找Viterbi算法的最佳适用信道和不同要求(如误码率)下最优编码。

1.3 本课题的意义

在卷积码中,因为Viterbi算法效率高,速度快,结构相对简单等特点,被

广泛应用于各种数据传输系统。特别是深空通信、卫星通信系统中。在现代信息

处理系统中,需要处理的信息量越来越大,实时性要求越来越高。为减少对主处

理器各种资源的占用,要求通信模块方面的大部分工作能独立完成。因此采用

Viterbi译码算法具有非常现实的意义。

1.4 本课题的研究方法

本文通过基于MATLAB的SIMULINK下的模块对卷积编码,解码进行仿真。通过

仿真可以更清楚的认识到卷积码的编码,解码的各个环节,并对仿真结果进行了

分析。得出卷积码Viterbi译码的误比特性能和回溯长度,码率,约束长度的关

系。

第 1 页 共 21 页

�

2 卷积码的基本概念

2.1 信道

信道是任何一个通信系统所必不可少的组成部分。由于信道中可能存在着各

种干扰,通信设备中也可能存在种种造成错码的因素。随着数据处理、计算机通

信、卫星通信以及高速数据通信网的飞速发展,用户对数据传输的可靠性提出了

越来越高的要求。因此如何在保证数据传输速率的前提下,提高传输数据的可靠

性,就成为一个迫切需要解决的问题。根据干扰对数据传输影响可分为随机干扰

和突发干扰。其中,电子热噪声产生的干扰可以看作是随机的高斯白噪声,它对

信道主要的影响是产生码元的随机错误[6]。

2.2 纠错编码

因为信道状况的恶劣,信号不可避免会受到干扰而出错。为实现可靠性通信,

主要有两种途径:一种是增加发送信号的功率,提高接收端的信号噪声比;另一种

是采用编码的方法对信道差错进行控制。前者常常受条件限制,不是所有情况都

能采用。编码理论可以解决这个问题,使得成本降低,实用性增强。

2.3 卷积码的基本概念

卷积码是一种性能优越的信道编码。(n ,k ,N) 表示把 k 个信息比特编成 n

个比特,N 为编码约束长度,说明编码过程中互相约束的码段个数。卷积码编码

后的 n 个码元不仅与当前组的 k 个信息比特有关,而且与前 N - 1 个输入组的

信息比特有关[6]。编码过程中相互关联的码元有 N ×n 个。R = k/ n 是卷积码

的码率,码率和约束长度是衡量卷积码的两个重要参数[1]。

2.4 卷积码编码的概念

卷积码的编码描述方法有 5 种:冲激响应描述法、生成矩阵描述法、多项式

乘积描述法、状态图描述法和网格图描述法[1]。卷积码的纠错能力随着 N 的增加

而增大,而差错率随着 N 的增加而指数下降。在编码器复杂性相同的情况下,卷

积码的性能优于分组码。分组码有严格的代数结构,但卷积码至今尚未找到如此

严密的数学手段。分组码的译码算法可以由其代数特性得到。卷积码虽然可以采

用适用于分组码的门限译码(即大数逻辑译码),但性能不如维特比译码和序列译

码[6]。

2.4.1 卷积编码

卷积码的编码器一般都比较简单。

第 2 页 共 21 页

�

图2-1是一般情况下的卷积码编码器框图。它包括NK级的输入移位器,一组n

个模2和加法器和n级的输出移位寄存器 [6]。对应于每段k比特的输入序列,输出n

个比特。由图可知,n个输出比特不但与当前的k个输入比特有关,而且与以前的

(N-1)k个输入信息比特有关。整个编码过程可以看成是输入信息序列与由移位寄

存器和模2加法器的连接方式所决定的另一个序列的卷积,卷积码由此得名。本

文采用的是冲击响应描述法编码思想。

如图 2-2 是卷积码(2,1,3)卷积编码器的一个框图[6]。左边是信息的输

入。下面分别是系统位输出和校验位输出。其中间是 3 个移位寄存器和一个模 2

加法器。简单的说就是信息位经过移位寄存器和一个模 2 加法器产生一个系统位

和校验位加在一起输出。可以看出:每输入一个比特,移位寄存器中就向右移动

一个位子。原来的第三个寄存器就被移出。可见卷积编码不只与现在的输入比特

有关还与前面的 3-1 个比特有关。所以约束长度是 3。在这里,其中 K=1 ,n=2

所以码率 R=K/ n=1/2。

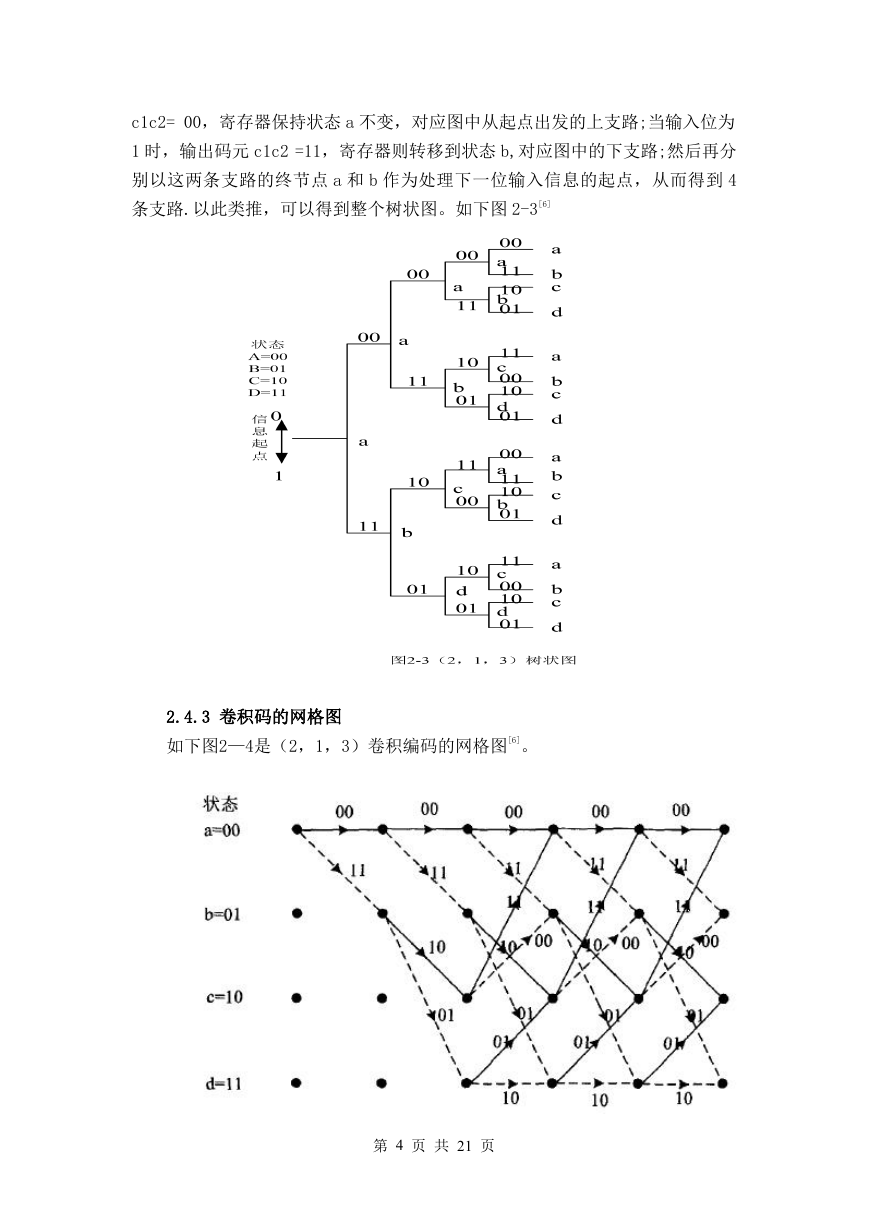

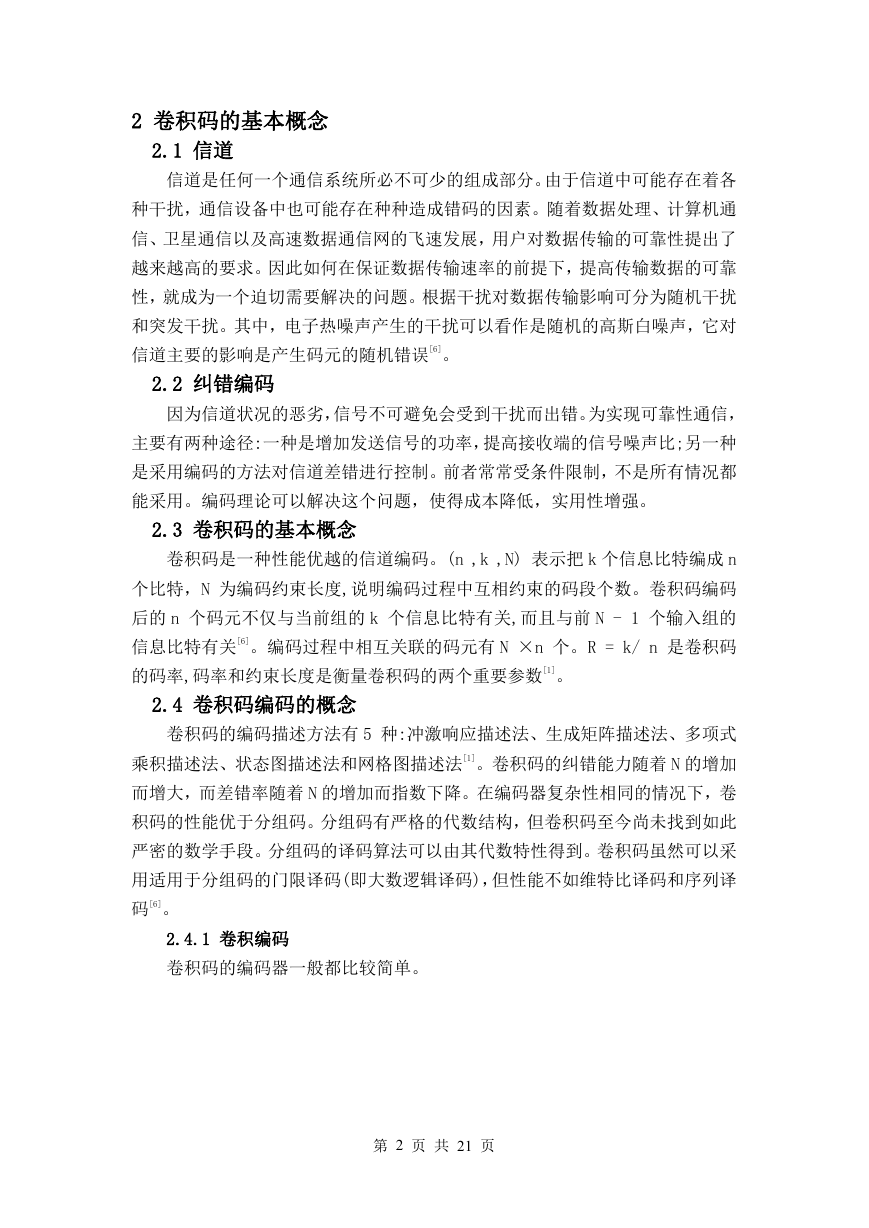

2.4.2 卷积码的树状图

对于图 2-2 所示的(2,1,3 )卷积码编码电路,其树状图如下图 3-3 所示。这

里,分别用 a,b,c 和 d 表示寄存器的 4 种状态:00, 01, 10,和 11,作为树状图

中每条支路的节点。以全零状态 a 为起点,当输入位信息位为 0 时,输出码元

第 3 页 共 21 页

�

c1c2= 00,寄存器保持状态 a 不变,对应图中从起点出发的上支路;当输入位为

1 时,输出码元 c1c2 =11,寄存器则转移到状态 b,对应图中的下支路;然后再分

别以这两条支路的终节点 a 和 b 作为处理下一位输入信息的起点,从而得到 4

条支路.以此类推,可以得到整个树状图。如下图 2-3[6]

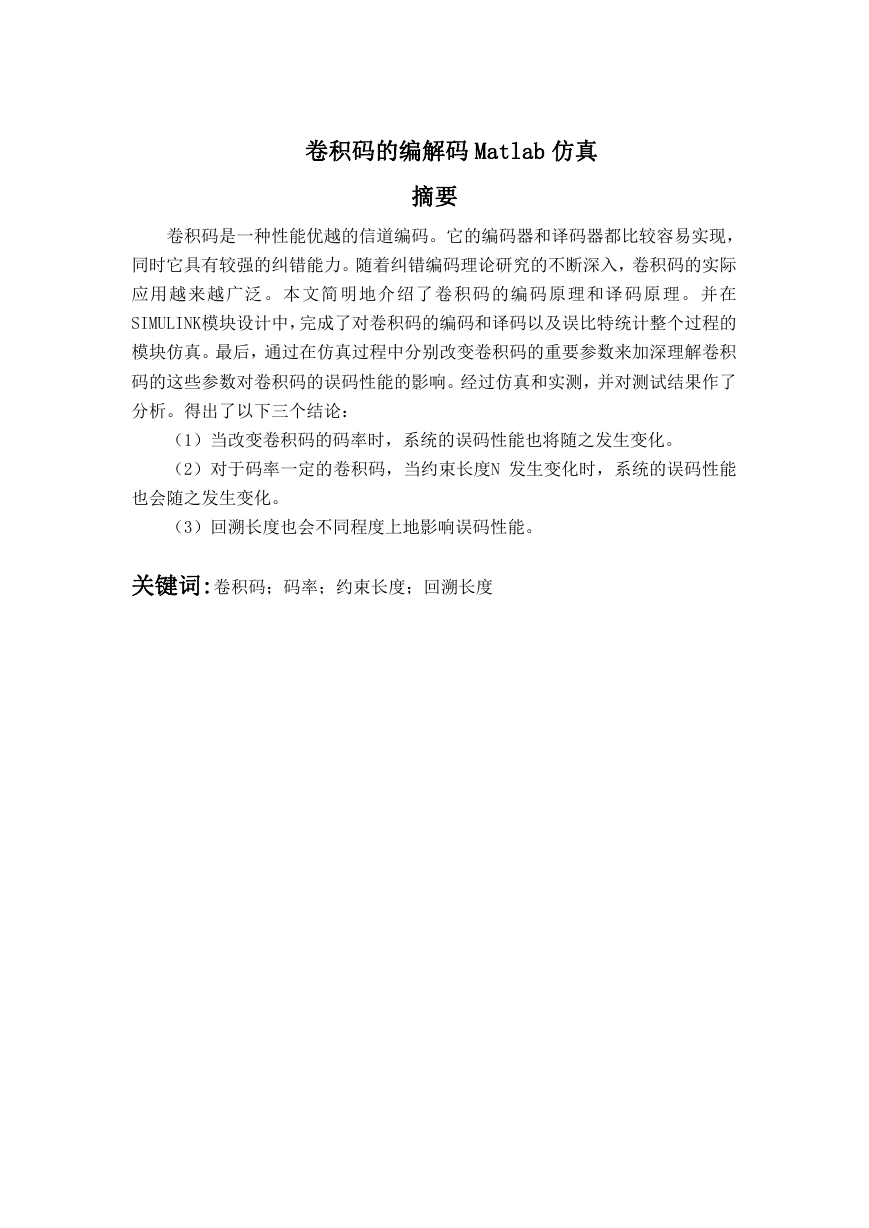

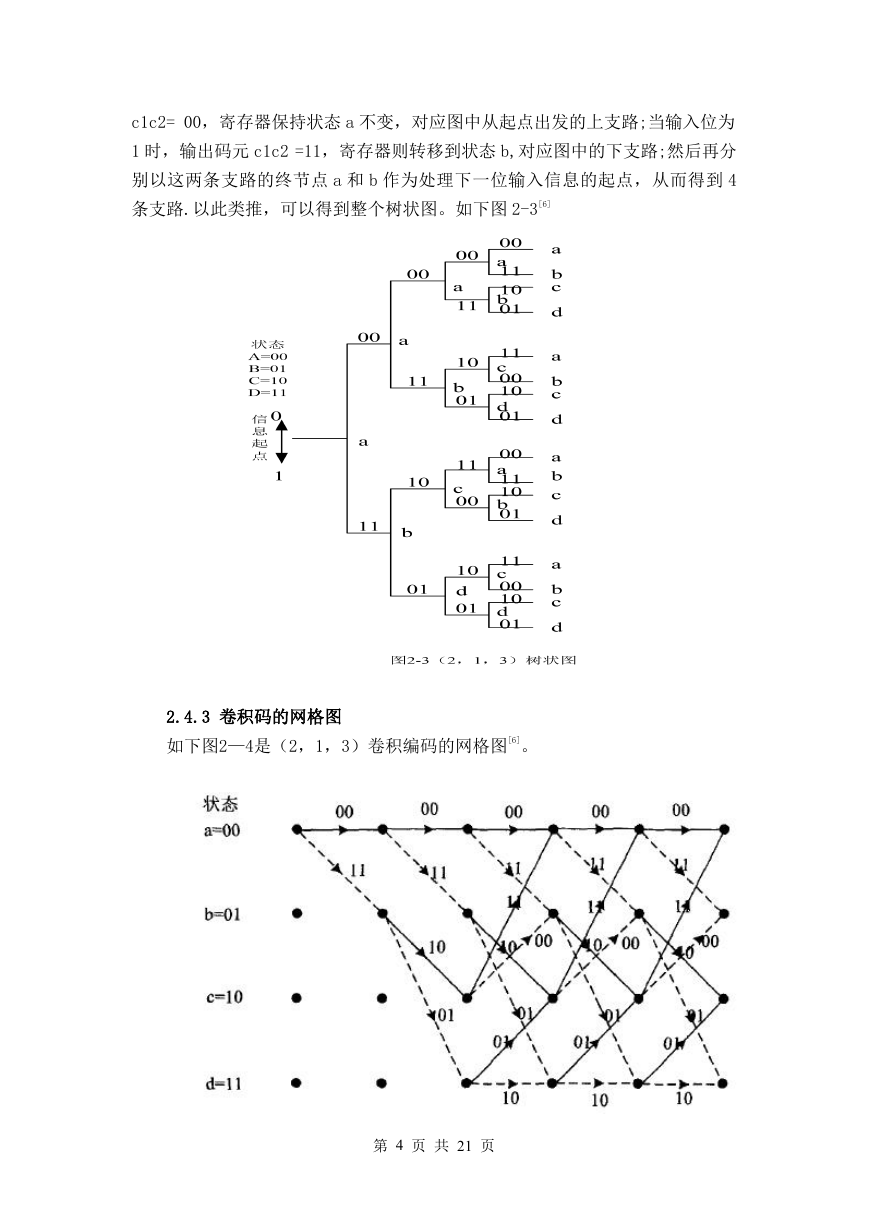

2.4.3 卷积码的网格图

如下图2—4是(2,1,3)卷积编码的网格图[6]。

第 4 页 共 21 页

�

图 2-4 (2,1,3)卷积编码的网格图

2.4.4 卷积码的解析表示

图 2-5 卷积码状态图[6]

除上述三种图解表示方法外,常常还用解析表示方法描述卷积码,即延时算

子多项式。在延时算子多项式表示中,编码器中的移位寄存器与模2加法器的连

接关系以及输入、输出序列都表示为延时算子D的多项式。在一般情况下,输入

序列可表示为[6]:

M(D)

DmDmm

1

3

2

2

...

(2-1)

变量D的幂的次数等于相对于时间起点的单位延时数目,时间起点通常选在

第1个输出比特,ml,m2,m3,m...为输入比特的二进制表示(1或0)。用D算子多项

式表示移位寄存器各级与各模2项连接关系时。若某级寄存器与某模2和相连,则

多项式中相应项的系数为1,否则为0(表示无连接)。以图3.2所示(2,1,3)卷积码

为例,左、右两个模2和与寄存器各级的连接关系可表达为[6]:

1

(

DG

(

DG

1)

1)

2

2

D

DD

(2-2)

2

通常把表示移位寄存器与模2和连接关系的多项式称为生成多项式,因为由

它们可以用多项式相乘计算出输出序列。卷积码的图解与解析表示方法各有特

点。用延时算子多项式表示卷积码编码器的生成多项式最为方便。网格图对于分

析卷积码的译码算法十分有用。

第 5 页 共 21 页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc