I现 代 建 设 l Mode rn Con st ruction

基 于ARM的LED屏显示控制 系统 的设计

(武汉工业学院电气与电子工程 学院 。湖北 ,武汉 430024)

任蓉 吕强

摘 要 :本 文 根据 LED显 示模 块 的 结 构特 点 ,结合 CPLD技 术 以实 现 LED显 示 屏 动态 扫 描 显 示 。设 计 出基 于

ARM+FPGA的 LED屏显 示 系统 。从 硬 件和 软件 两个 方 面设 计 ,实 现 LED屏 的显 示。 硬件 方 面采 用ARM9芯 片

$3C2440A为主控制单元 ,FPGA为扫描控制单元 。完成数据存储 。更新 以及与上位机的通信等 。软件方面包括上 位

机应用软件和嵌入式控制软件 。上位机软 件编辑LED显示屏 上显 示的数据信息 ,实现与下位机的通信 :嵌 入式控制软

件 实现数据接收和存储 ,数据输出和 图像显示 ,从而实现对LED屏的控制。

关 键 词 :ARM;LED;嵌 入 式

中图分类号 :TN873 文献标识码 :A 文章编号 :1671—8089(2012)03—0042—03

Design of LED·-screen Display Control System based on ARM

(Electrical and Electronics Engineering College,Wuhan Polytechnic University Wuhan 430024,China)

RenRong LuQiang

Abstract:According to the structural features of the LED display module an d CPLD techn ology to accomplish the dynamic scanning

display of the LED screen,the ARM +FPGA LDE screen display system is designed.The dynam ic display of th e LED screen is

carried out from two ways:h~ dwar e an d software.H~ dwar e wise,the ARM 9 chip $3C2440A is the m ain control unit,FPGA is the

SCan control unit.They can store data,upda te an d comm un ication w ith th e upper com puter.Software including the upper com puter

application software an d embedded control software,are providing quality service.Upper computer complies the dates from the LDE

screen to communication with the subordinate part.Embedded control software is able to receive and store the da ta,transmit the da ta

and display th e im age.

Key words:ARM ;LED ;Embedded

引言

信 息 化 社 会 的 到 来 ,促 进 了现 代 信 息 显 示 技 术 的 发

展 ,信 息传 播 具有越 来 越重 要 的地 位 , 同时受 众对 视觉媒

体 的要 求 也愈 来愈 高 ,要求传 播 媒体 反映 迅速 、现 实 (实

时性 ) 、醒 目 (色 彩丰 富 、栩栩 如 生 )。而 随着微 电子 技

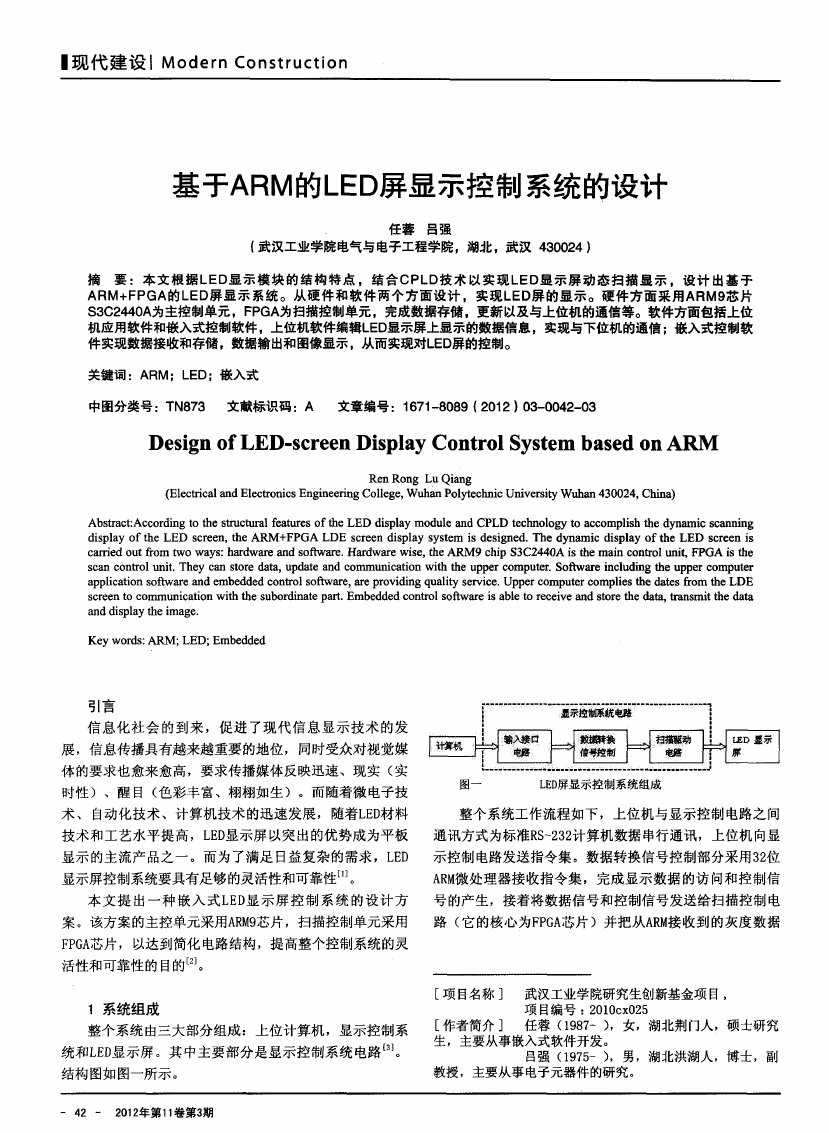

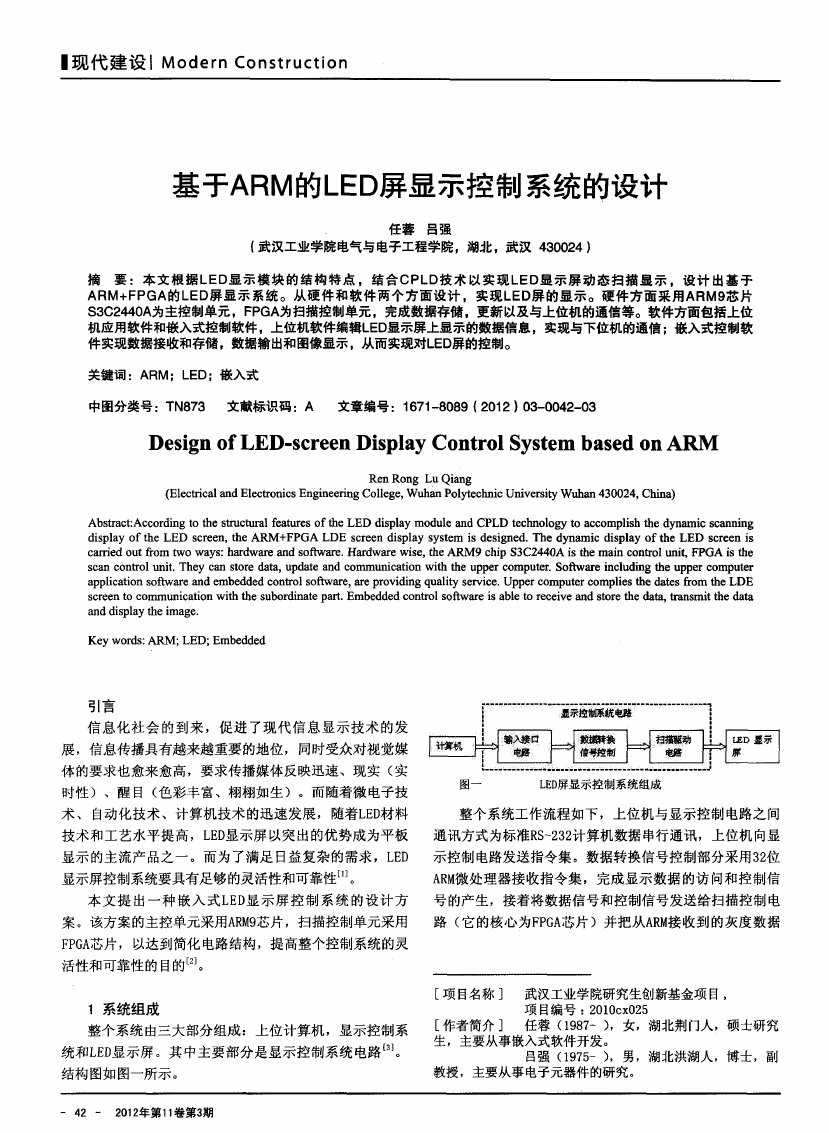

图 一

LED屏 显 不 控 制 系 统 组 成

术 、 自动化 技 术 、计 算机 技 术 的迅 速 发 展 ,随着 LED材 料

整个 系 统工 作流 程 如下 ,上 位机 与 显示 控制 电路之 间

技 术 和 工 艺水 平提 高 ,LED显示 屏 以突 出的优 势 成 为平 板

通 讯方 式 为标准 RS~232计算 机数 据 串行通 讯 ,上位 机 向显

显 示 的 主流 产 品之 一 。而 为 了满 足 日益 复杂 的 需求 ,LED

示控 制 电路 发送 指令 集 。数据 转换 信 号控制 部 分采 用32位

显 示屏 控制 系统 要具有 足够 的灵 活性和 可靠 性 。

ARM微 处 理器 接 收指 令 集 ,完 成 显示 数 据 的访 问和控 制 信

本 文 提 出一 种 嵌 入 式 LED显 示 屏 控 制 系 统 的 设 计 方

号的产生,接着将数据信号和控制信号发送给扫描控制 电

案 。该方 案 的主控 单元 采用ARM9芯 片 ,扫 描控 制 单元采 用

路 (它 的核 心 为FPGA芯 片 )并 把从 ARM接 收 到 的灰度 数 据

FPGA芯片,以达到简化 电路结构,提高整个控制系统的灵

活 性和 可靠 性 的 目的 。

1系统组成

[项 目名称 ] 武汉 工业 学院研究生创新基金项 目 ,

项目编号 :2010cx025

统和

…

嵌 萋 ~/'~ l I )1/A o 北 认 塌究

整个 三

LED显示屏。其中主要部分是显示控制系统电路∞ 。 … 一… 一百 (1975一),男,湖北洪湖人,博士,副

, 兰 曼 系

:

结 构 图如 图一所示 。

教授 ,主要从事电子元器件 的研究 。

42 — 2012年第 11卷第3期

�

Mode rn Con st ruction I现 代 建 设 -

信 号分 时存储 到FPGA外部 扩展 的两 片SRAM中 ,扫描控 制 电

路将从SRAM中读 出的灰度数据信号转换 成LED显示屏 能够

识别 的数 据信 号 ,发送 ~IJLED显 示屏 上显 示 。

要在 LED屏 幕 上 显示 出一 幅完 整 的图 形 图像 ,FPGA和

ARM必 须 要 协 同 一 致 ,完 成 存 储 器 中 图形 图像 数 据 的 读

取 、解压 ,灰度 调制 和 生成 显示 屏的 驱动 逻辑 等各 个 部分

的 功能 。

2 LED屏显示系统 的硬件设计

2.1 ARM的硬 件 电路设 计

2.1.1 ARM微 处理 器选 型

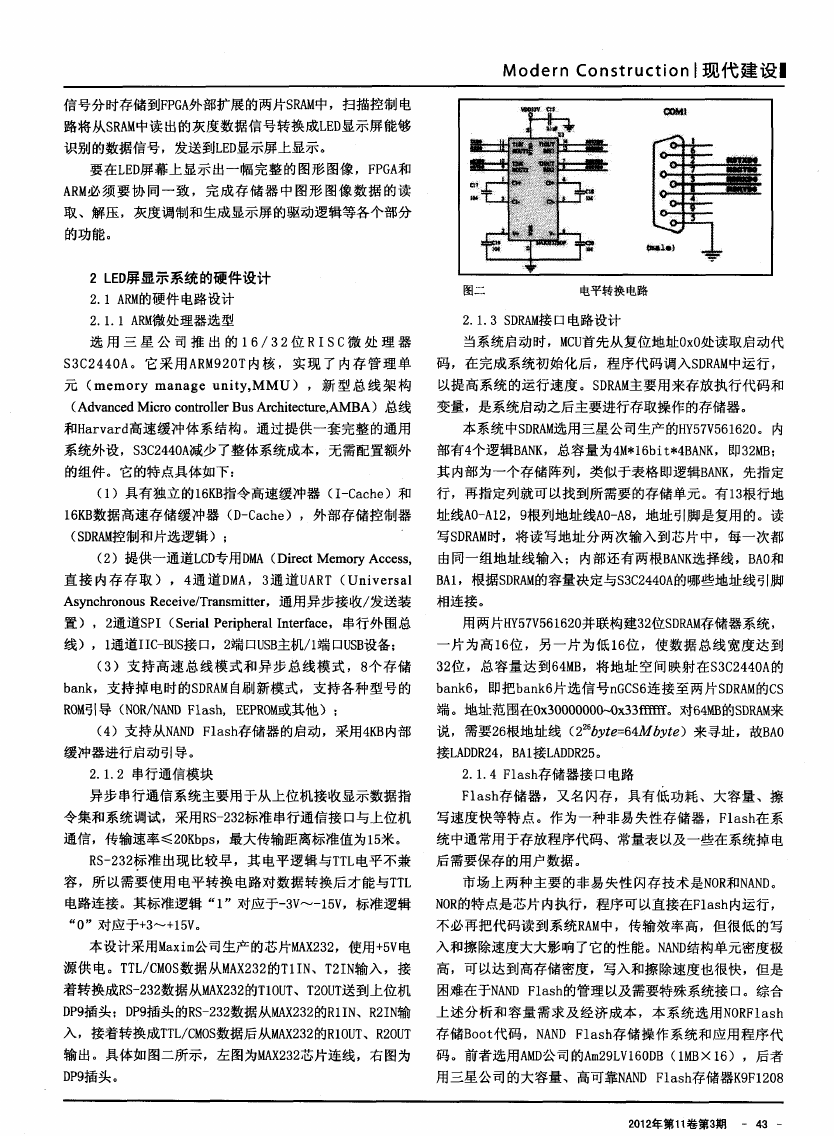

图二

电 平 转换 电 路

2.1.3 SDRAM接 口电路设计

选 用 三 星 公 司 推 出 的 1 6/3 2位 R I S C微 处 理 器

当系统 启动 时,MCU首先 从 复位 地址 OxO处 读取 启 动代

$3C2440A。它采 用ARM920T内核 ,实现 了内存管 理单

码 ,在完 成 系 统初 始 化后 ,程 序代 码 调入 SDRAM中运行 ,

元 (memory manage unity,MM U) , 新 型 总 线 架 构

以提 高 系统 的运行 速 度 。SDRAM主 要 用来 存 放执 行 代码 和

(Advanced Micro controller Bus Architecture,AMBA)总线

变量,是系统启动之后主要进行存取操作的存储器。

和Harvard高速 缓 冲体 系 结构 。通 过提 供 一套 完 整 的通 用

本 系统 中SDRAM选 用 三星 公 司生产 的HY57V561620。 内

系 统外 设 ,$3C2440A减少 了整 体 系统 成本 ,无 需配 置额 外

部 有4个逻 辑BANK,总容 量 为4M*16bit*4BANK,即 32MB;

的组件 。它 的特 点具体 如下 :

其 内部 为 一个 存储 阵列 ,类 似 于表格 即逻 辑BANK,先 指定

(1)具有 独立 的16l(B指令 高速 缓 冲器 (I-Cache)和

行 ,再 指 定列 就可 以找 到所 需要 的存 储 单元 。有 13根 行地

16KB数据高速存储缓冲器 (D—Cache),外部存储控制器

址 线A0一AI2,9根 列地 址 线A0一A8,地 址 引脚 是复用 的。读

(SDRAM控制 和 片选逻 辑 );

写SDRAM时 ,将 读 写地 址 分 两次 输 入到 芯 片 中 ,每 一次 都

(2)提 供 一通 道LCD专 用DMA (Direct Memory Access。

由 同一 组地 址 线输 入 ; 内部 还 有两 根BANK选 择 线 ,BAO和

直 接 内存 存 取 ) ,4通 道 DMA, 3通 道 UART (Universal

BA1,根 据SDRAM的容量 决定 与$3C2440A的哪些 地址 线 引脚

Asynchronous Receive/Transmitter,通 用异 步 接 收/发送 装

相 连接 。

置 ) ,2通 道SPI(Serial Peripheral Interface,串行 外 围总

用两 片HY57V561620并联 构 建32位 SDRAM存 储器 系统 ,

线 ),1通道 IIC-BUS接 口,2端 HUSB主机/1端 口USB设备 ;

一 片 为 高 l6位 ,另 一 片 为 低 16位 ,使 数据 总线 宽度 达 到

(3)支持高速总线模式和异步 总线模 式,8个存储

32位 ,总容量达~U64MB,将地址空间映射在$3C2440A的

bank,支 持 掉 电 时的 SDRAM自刷 新模 式 ,支持 各 种型 号 的

bank6, 即把 bank6片 选 信 号nGCS6连接 至 两 片SDRAM的CS

RoM引导 (N0R/NAND Flash,EEPROM或其他 );

端 。地 址范 围在 ox3OOO0Oo0~ox33姗 。对64她 的SDRAM来

(4)支 持 从NAND Flash存 储器 的 启动 ,采用 4KB内部

说 ,需 要26根地 址 线 (22Sbyte=64M byte)来 寻址 ,故BA0

缓冲 器进 行启 动引 导 。

2.1.2 串行 通信模 块

接LADDR24,BA1接 LADDR25。

2.1.4 Flash存储 器接 口电路

异步 串行 通信 系 统主 要用 于 从上 位机 接 收显 示数 据 指

Flash存 储 器 ,又 名 闪 存 ,具 有 低 功耗 、大容 量 、擦

令集 和系 统 调试 ,采用 RS一232标准 串行 通信 接 口与 上位 机

写 速度 快 等 特 点 。作 为一 种 非 易失 性存 储 器 ,Flash在 系

通信 ,传 输速 率~20Kbps,最 大传 输距离 标准 值为 15米 。

统 中通 常用 于存 放程 序代 码 、常量 表 以及 一些 在系 统掉 电

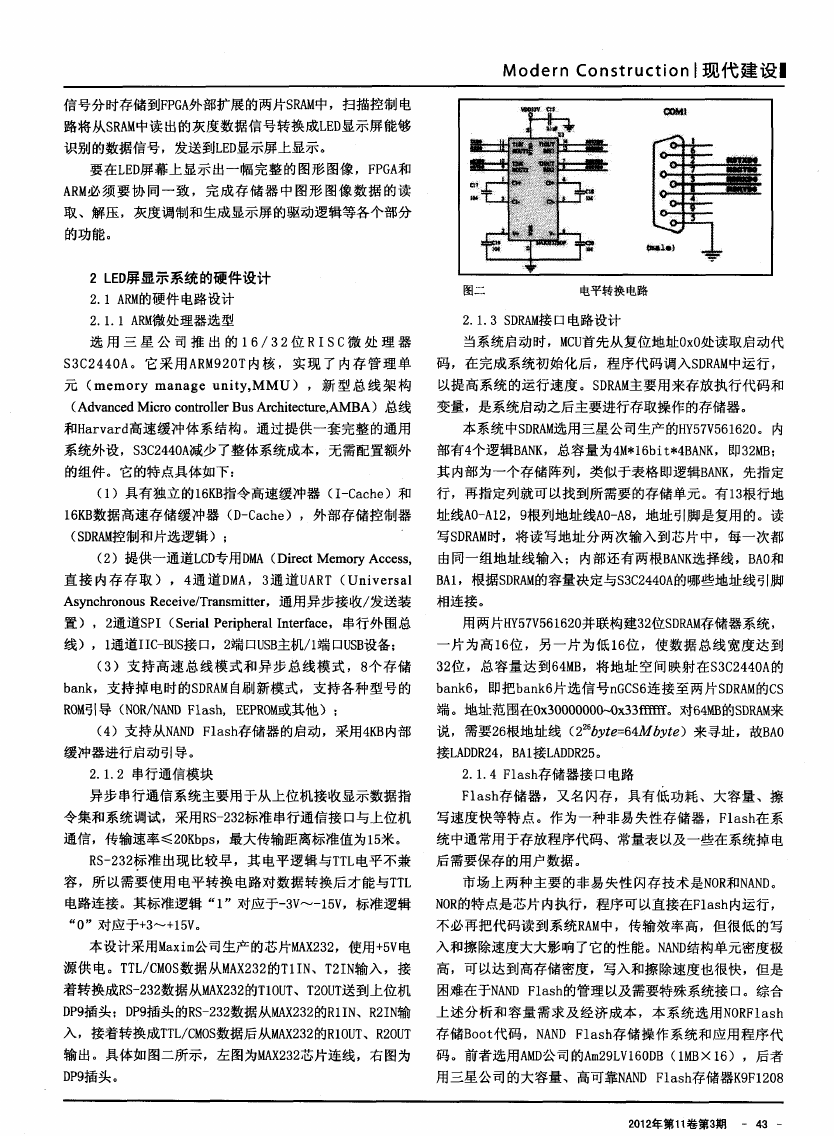

RS一232标 准 出现 比较 早 ,其 电平 逻 辑 与TTL电平 不 兼

后 需要保 存 的用户 数据 。

容 ,所 以需要 使 用 电平 转 换 电路 对 数据 转 换后 才 能 与TTL

市 场上 两 种 主 要 的非 易 失性 闪存 技术 是NOR和NAND。

电路 连接 。其 标准 逻辑 “1”对应 于一3V~一15V,标准 逻 辑

NOR的特 点是 芯片 内执 行 ,程 序 可 以直接 在Flash~运行 ,

“0”对 应于 +3~+15V。

不 必再 把 代 码读 到 系统 RAM中 ,传输 效 率 高 ,但很 低 的写

本 设计 采用 Maxim公 司 生产 的芯 片MAX232,使用 +5V电

入和 擦 除速度 大 大影 响 了它 的性 能 。NAND结构 单元 密度 极

源供 电。TTL/CMOS数据从MAX232的T1IN、T2IN输入 ,接

高 ,可 以达 到高 存储 密度 ,写入和 擦 除速度 也 很快 ,但 是

着 转 换成 RS一232数 据从MAX232的T10UT、T2OUT送 到上 位机

困难 在 于NAND Flash的 管理 以及需 要特 殊系统 接 口。综 合

DP9插头 :DP9插头 的RS一232数据 从MAX232的RI lN、R2 1N输

上 述 分 析和 容 量 需 求 及 经 济成 本 ,本 系 统选 用 NORFlash

入 ,接着转换成TTL/CMOS数据后从MAX232的RIOUT、R2OUT

存储 Boot代码 ,NAND Flash存 储 操 作系 统 和应 用 程 序 代

输 出 。具 体如 图二所 示 ,左 图为MAX232芯 片连线 ,右 图为

码 。前 者 选用 AMD公 司 的Am29LVI60DB (1MB× 16),后 者

DP9插头 。

用 三星 公 司 的大容 量 、高 可靠 NAND Flash存 储器 K9F1208

2012年第11卷第3期 一 43 —

�

_现 代 建 设 I Modern Con st ruction

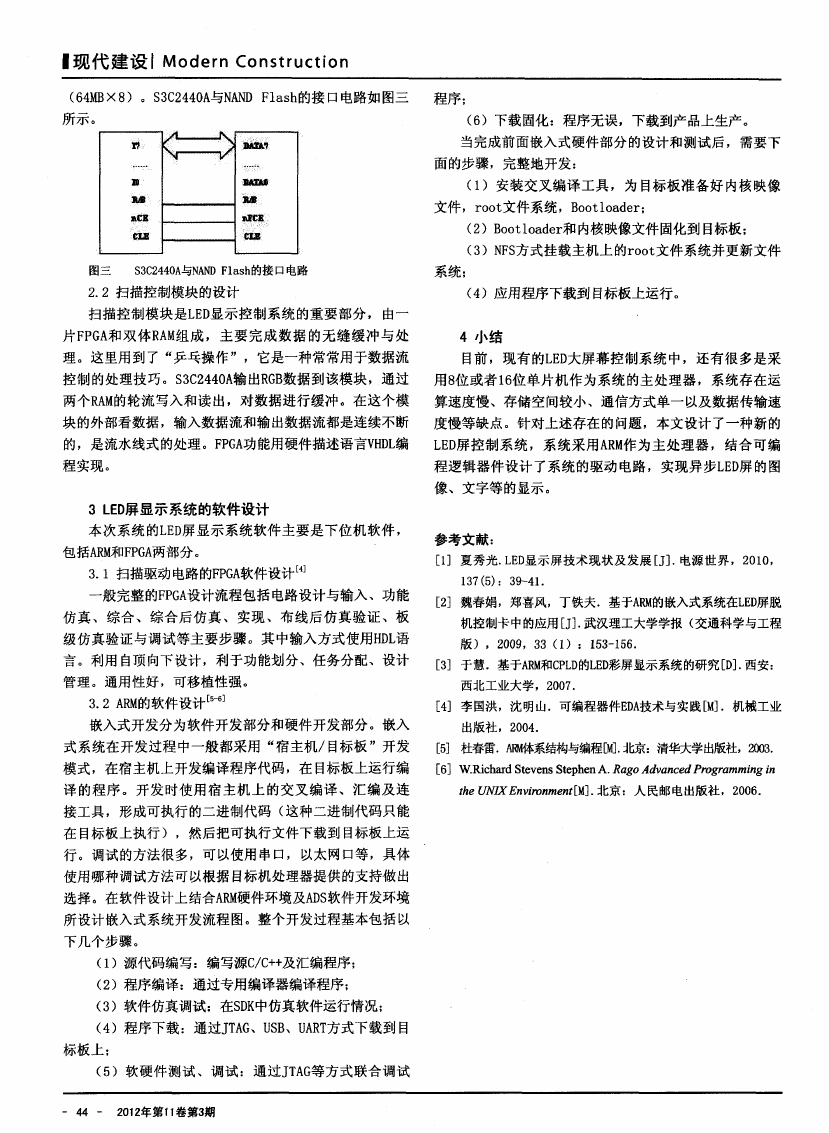

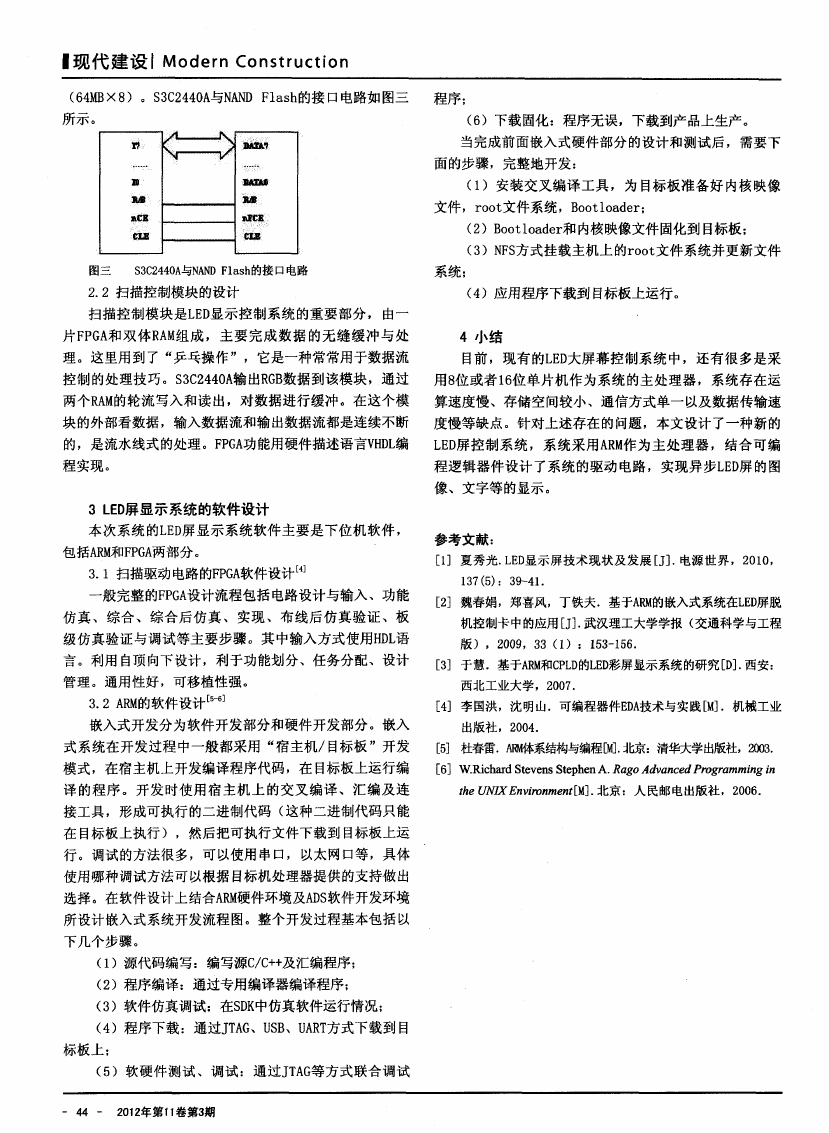

(64MBX8) 。$3C2440A与 NAND Flash的接 口电路 如 图三 程 序 ;

所示 。

—

—

—

井 \广——1/

.

m

髓

1 t

l童

蕾 瞳嚣

m

稍睫 嚣

C基矗

(6)下载 固化 :程 序无误 ,下 载到 产 品上生产 。

当完 成前 面嵌 入 式硬 件部 分 的设 计和 测试 后 ,需 要 下

面 的步骤 ,完整 地开 发 :

(1)安 装 交叉 编 译 工具 ,为 目标板 准 备 好 内核 映像

文件 ,root文件 系统 ,Bootloader:

(2)Bootloader和 内核 映像文 件 固化到 目标板 ;

(3)NFS方式 挂 载主 机上 的root文件 系 统并 更新 文件

图 三

$3C2440A与 NAND Flash的 接 口电 路

系统 ;

2.2扫 描控 制模 块 的设计

(4)应用 程序 下载 到 目标 板上 运行 。

扫 描控 制 模块 是LED显 示 控 制系 统 的重要 部 分 , 由一

片 FPGA和 双 体RAM组 成 , 主 要 完 成 数 据 的无 缝 缓 冲 与 处

4 小 结

理 。这 里用 到 了 “乒 乓操 作 ” ,它 是~ 种常 常用 于数 据流

目前 ,现有 的LED大 屏 幕 控制 系 统 中 ,还 有 很 多 是采

控 制 的处 理技 巧 。$3C2440A输 出RGB数 据 到该 模块 ,通过

用8位 或 者 16位 单 片 机作 为 系 统 的主 处理 器 ,系统 存 在运

两 个RAM的轮 流 写入 和 读 出 ,对数 据 进 行缓 冲 。在 这 个模

算速 度慢 、存 储 空 间较 小 、通信 方 式单 一 以及数 据传 输速

块 的外 部看 数据 ,输 入数 据流 和输 出数 据流 都 是连续 不 断

度慢 等缺 点 。针对 上述 存在 的 问题 ,本 文设 计 了一种 新 的

的 ,是 流水 线式 的处 理 。FPGA功 能用硬 件描 述语 言VHDL编

LED屏 控 制 系 统 ,系 统 采 用 ARM作 为主 处 理 器 , 结 合可 编

程 实现 。

程逻 辑 器件 设 计 了 系统 的 驱动 电路 ,实 现 异步 LED屏 的 图

3 LED屏显示系统的软件设计

本 次 系统 的LED屏 显示 系 统 软件 主 要 是 下位 机 软 件 , 参考 文献

:

像 、文字 等 的显 示 。

包 括ARM和FPGA两 部分 。

3.1扫描 驱动 电路 的FPGA软件 设计

.

[1] 夏秀 光 .LED显 示 屏技 术 现状 及 发 展 [J].电源 世 界 ,2010,

137(5): 39~41.

一 般完整的FPGA设计流程包括电路设计与输入、功能 [2]魏春娟

, 郑喜风 ,丁铁 夫.基 于ARM的 嵌入式 系统 在LED屏 脱

仿 真 、综 合 、综 合 后 仿 真 、 实现 、布 线 后 仿 真 验 证 、 板

机控制卡中的应用 [J]

. 武汉理 工大 学学 报 (交通 科学 与工 程

级 仿 真验 证 与 调试 等 主要 步 骤 。其 中输 入 方 式使 用HDL语

版)

, 2009,33 (1) : 153—156.

言 。利 用 自顶 向下 设计 ,利 于功 能划 分 、任务 分配 、设 计 [3] 于慧

. 基 于ARM和cPLD的LED彩 屏显 示系 统 的研 究 [D].西安 :

管 理 。通用性 好 ,可移 植性 强 。

3.2 ARM的软件设计

西北工业大学,2007.

[4]李国洪,沈明山.可编程器件EDA技术与实践[M].机械工业

嵌 入 式开 发分 为软 件 开发 部分 和硬 件 开发 部分 。嵌 入

出版社,2004.

式 系统 在 开发 过 程 中一 般都 采 用 “宿 主 机/目标 板 ”开 发 [5] 杜春雷. 系结构与编程[M].北京:清华大学出版社,2003.

模式,在宿主机上开发编译程序代码,在 目标板上运行编 [6]W.RichardStevens StephenA.RagoAdvancedProgrammingin

译 的程 序 。开 发 时使 用 宿 主机 上 的交 叉 编 译 、汇 编 及 连

P UNIXEnvironment[M].北京:人民邮电出版社 ,2006.

接工具,形成可执行的二进制代码 (这种二进制代码只能

在 目标板 上执 行 ) ,然 后把 可执 行文 件下 载 到 目标 板 上运

行 。调试 的方 法很 多 ,可 以使 用 串 口,以太 网 口等 ,具体

使用 哪种 调试 方法 可 以根据 目标 机处 理器 提供 的支 持做 出

选择。在软件设计上结合ARM硬件环境及ADS软件开发环境

所设 计嵌 入式 系统 开 发流程 图。整个 开 发过程 基 本包 括 以

下几 个步骤 。

(i)源 代码 编写 :编写 源C/C++及 汇编 程序 ;

(2)程 序编 译 :通 过专 用编 译器编 译程 序 ;

(3)软件 仿真 调试 :在SDK中仿真 软件 运行情 况 ;

(4)程序下载:通过JTAG、USB、UART方式下载到 目

标 板上 :

(5)软 硬件 测 试 、调试 :通 过JTAG等方 式 联合 调 试

一 44 — 2012年 第11卷 第3期

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc