目录

一 设计任务及要求

二 总体设计方案

三 控制电路设计

3.1 控制电路工作原理

3.2 控制电路设计过程

四 倒计时电路设计

4.1 具有同步置数功能的十进制减法计数器设计

4.2 主干道和支干道倒计时电路设计

五 译码显示电路设计

5.1 动态显示工作原理

5.2 动态显示及译码电路设计

六 总体电路设计

6.1 总体电路

6.2 电路工作说明

七 电路仿真调试

7.1 控制电路仿真调试

7.2 倒计时电路仿真调试

7.3 译码显示电路仿真调试

7.4 总体电路仿真调试,下载验证

八 改进意见及收获体会

参考文献

�

一、设计任务及要求

1.设计一个用于十字路口的交通灯控制器。能显示十字路口东西、南北两

个方向的红、黄、绿的指示状态。

2.具有倒计时功能。用两组数码管作为东西和南北方向的倒计时显示,主干

道每次放行(绿灯)60 秒,支干道每次放行(绿灯)45 秒,在每次由绿灯

变成红灯的转换过程中,要亮黄灯 5 秒作为过渡。

3.黄灯每秒闪亮一次。

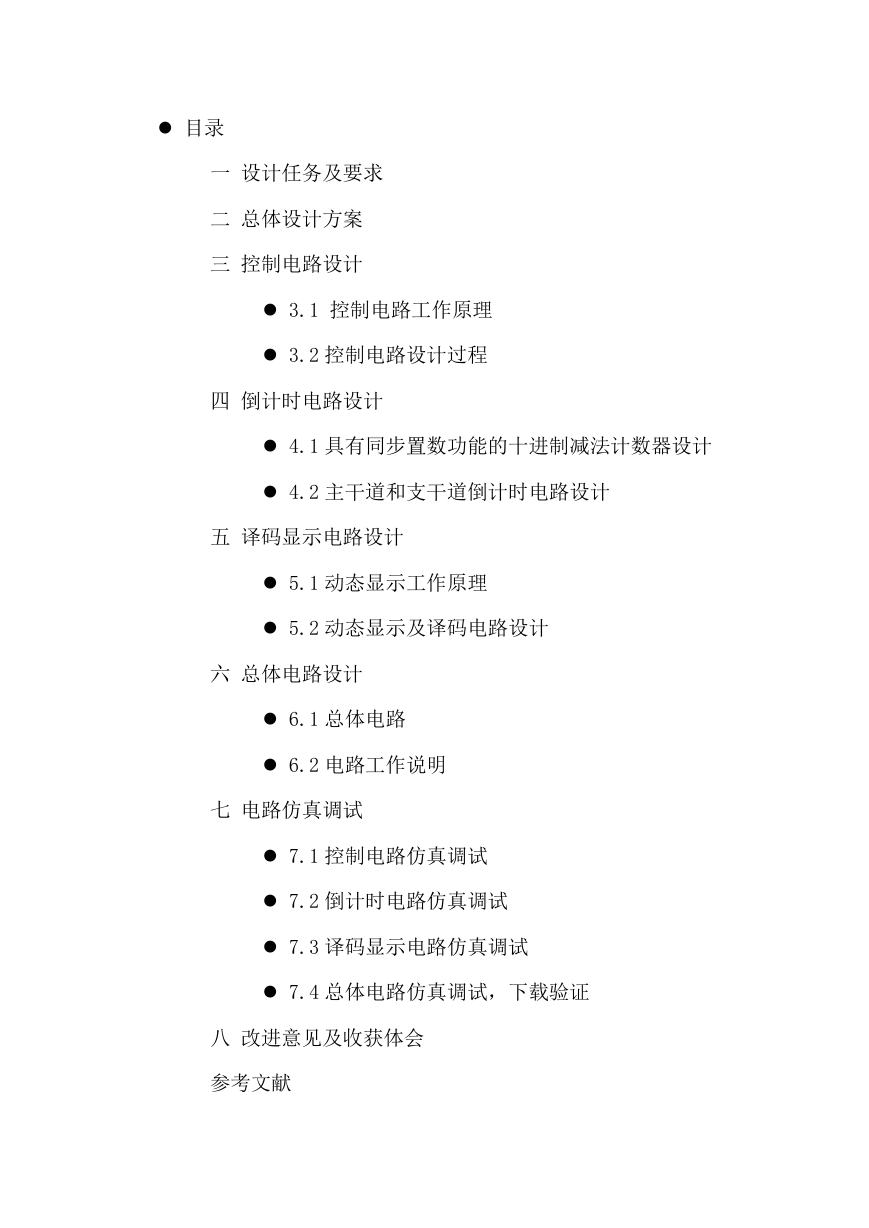

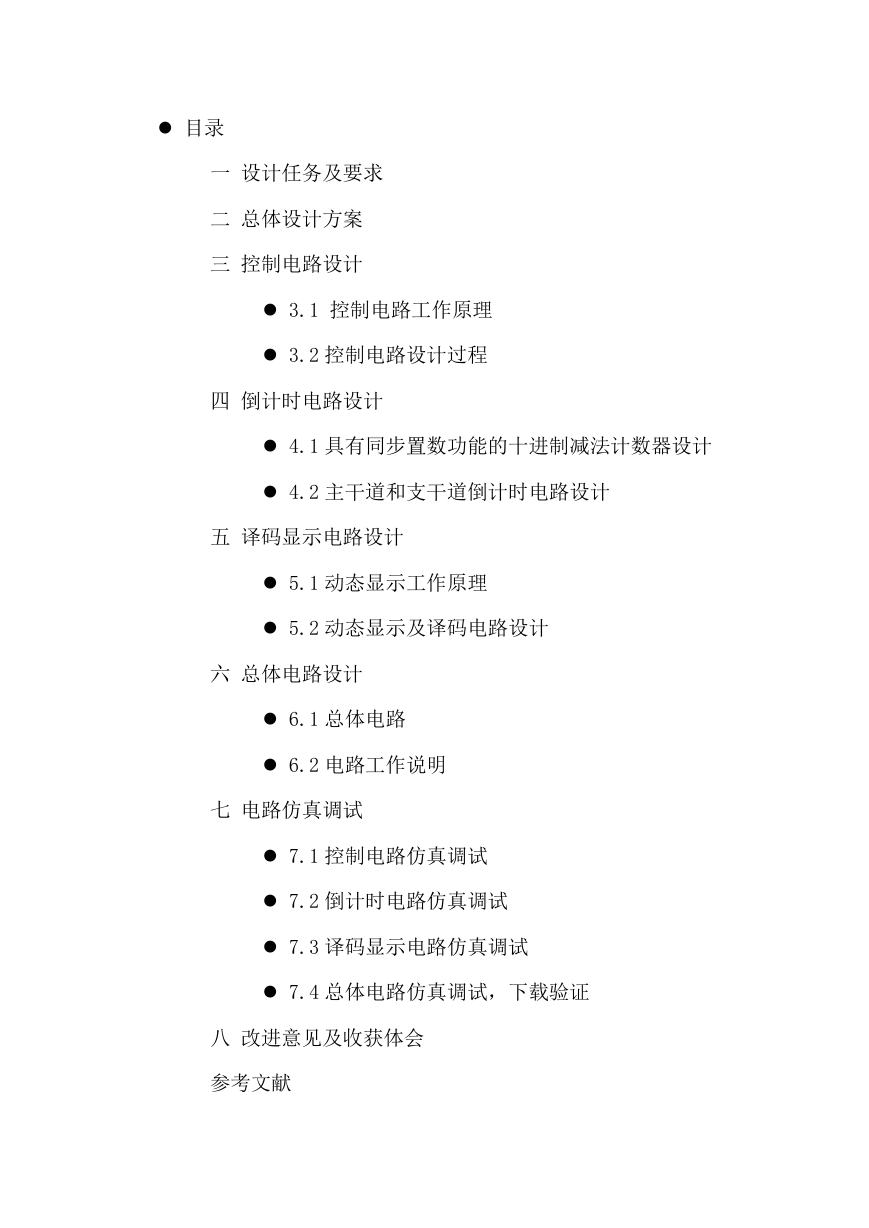

二、总体方案

时钟

控制器

倒计时

计数器

红绿灯

显示扫

描、译

数码管

交通灯控制器的功能框图

设主干道绿灯、黄灯、红灯分别为 G1、Y1、R1;支干道绿灯、黄灯、红灯分

别为 G2、Y2、R2,并且均用 0 表示灭,1 表示亮,则交通灯有如下四种输出

状态:

S0

S1

S2

S3

状态

G1Y1R1

G2Y2R2

00

01

10

11

1 0 0

0 1 0

0 0 1

0 0 1

0 0 1

0 0 1

1 0 0

0 1 0

�

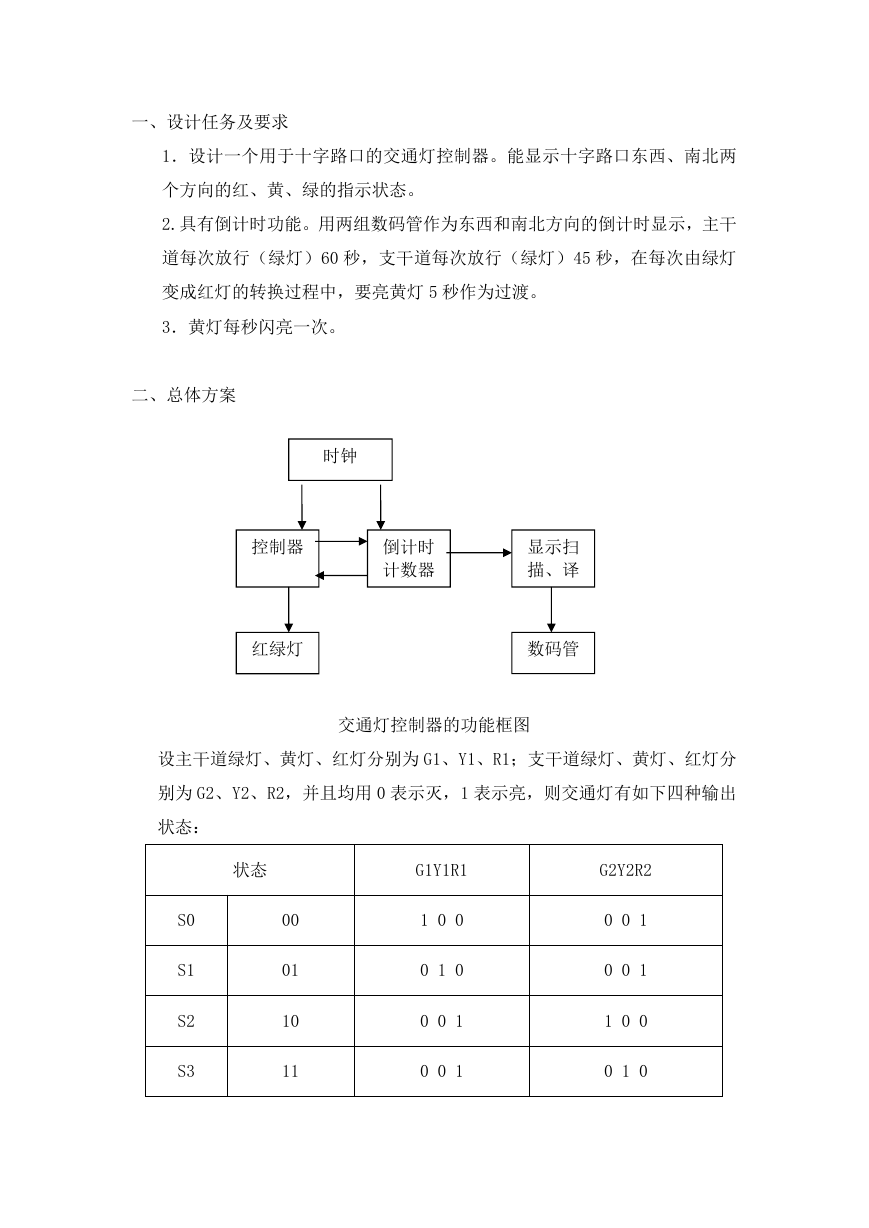

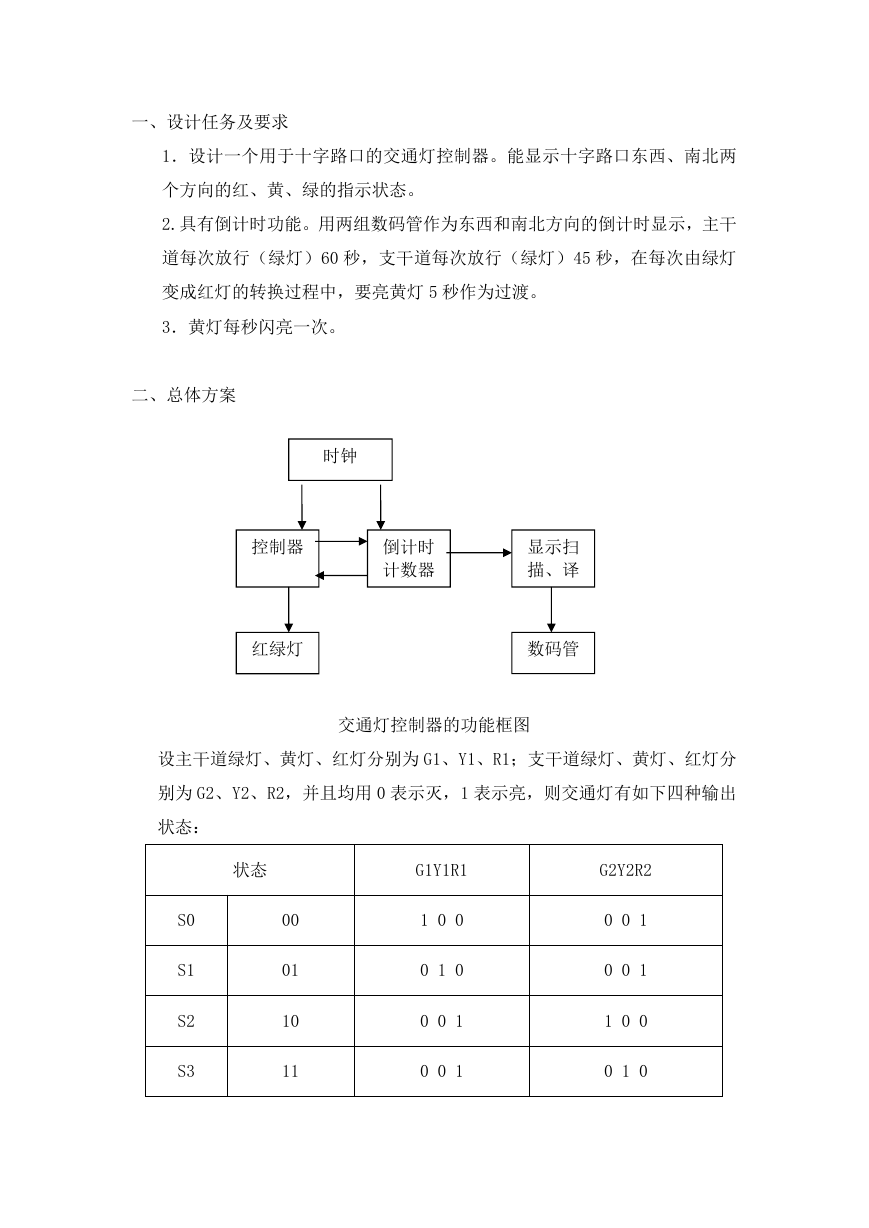

主干道倒计时显示:

60→……→01→05→……→01→50→……→06→ 05→……→01

支干道倒计时显示:

65→……→06→05→……→01→45→… …→01→05→……→01

S0

S1

S2

S3

通过以上观察可发现:

当主干道或者支干道的倒计时计数值为 01 时,控制器将从当前状态转入下

一个状态。因此,计数值 01 可作为控制器状态转换的条件,同时也可产生同步

置数信号,将下一状态的计数初值置入计数器。

三、控制电路设计

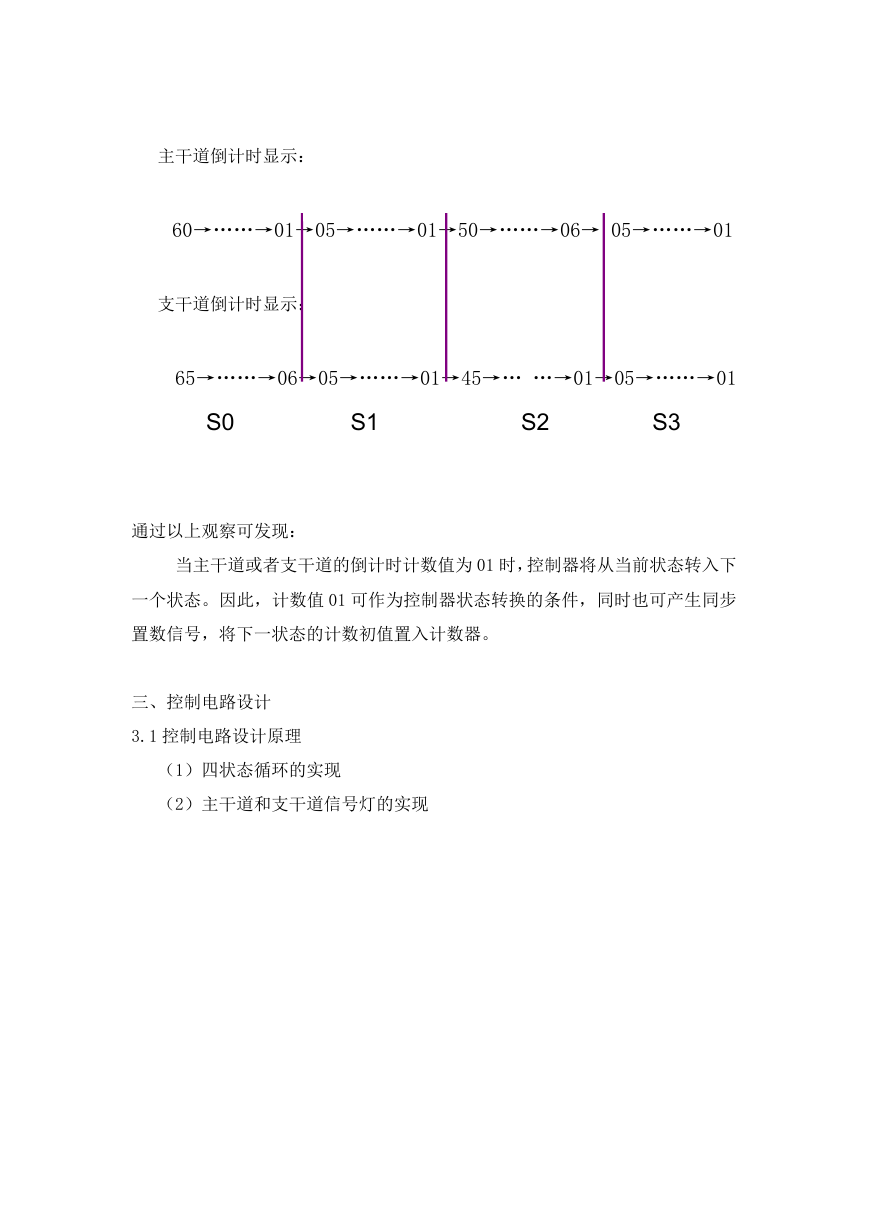

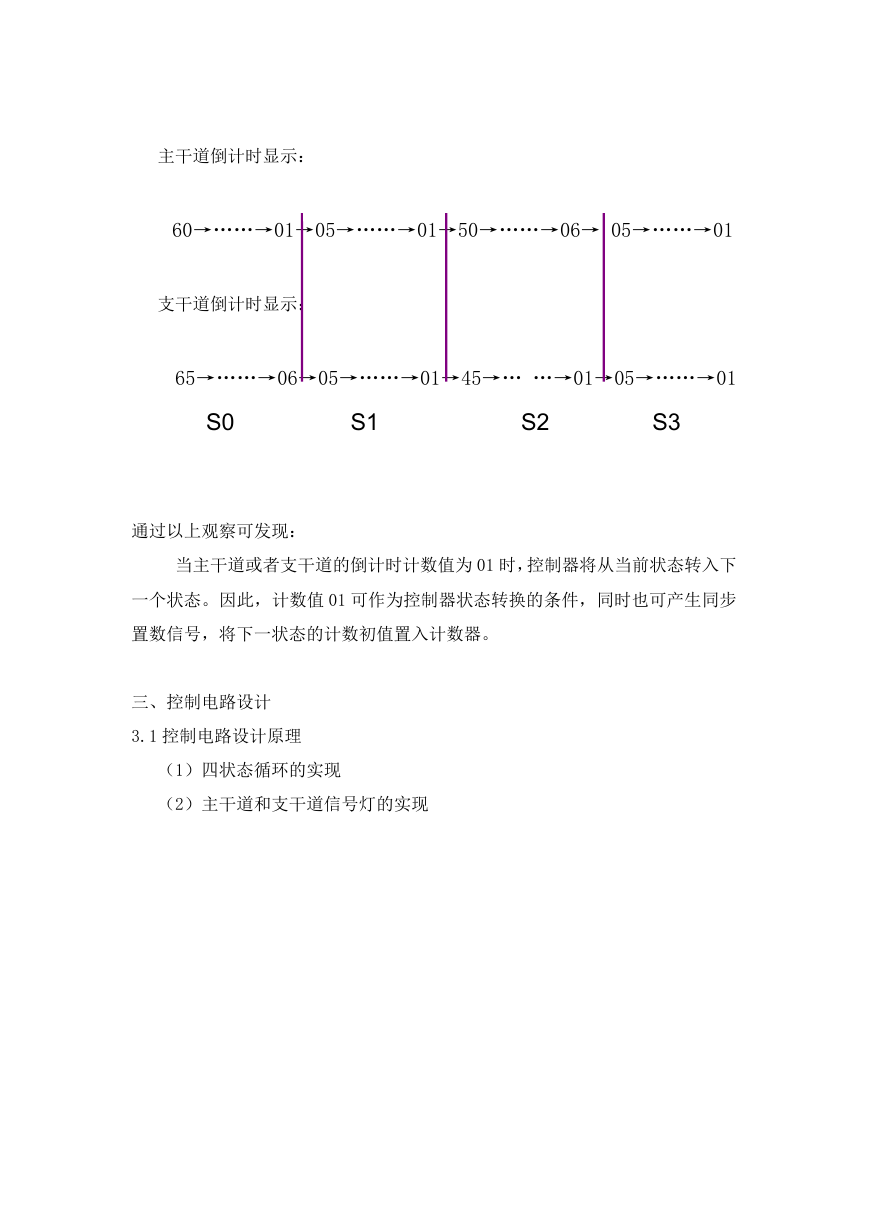

3.1 控制电路设计原理

(1)四状态循环的实现

(2)主干道和支干道信号灯的实现

�

T1=0

T1=1

S0

S1

T1=0

T1=1

T1=1

T1=1

S2

S3

T1=0

T1=0

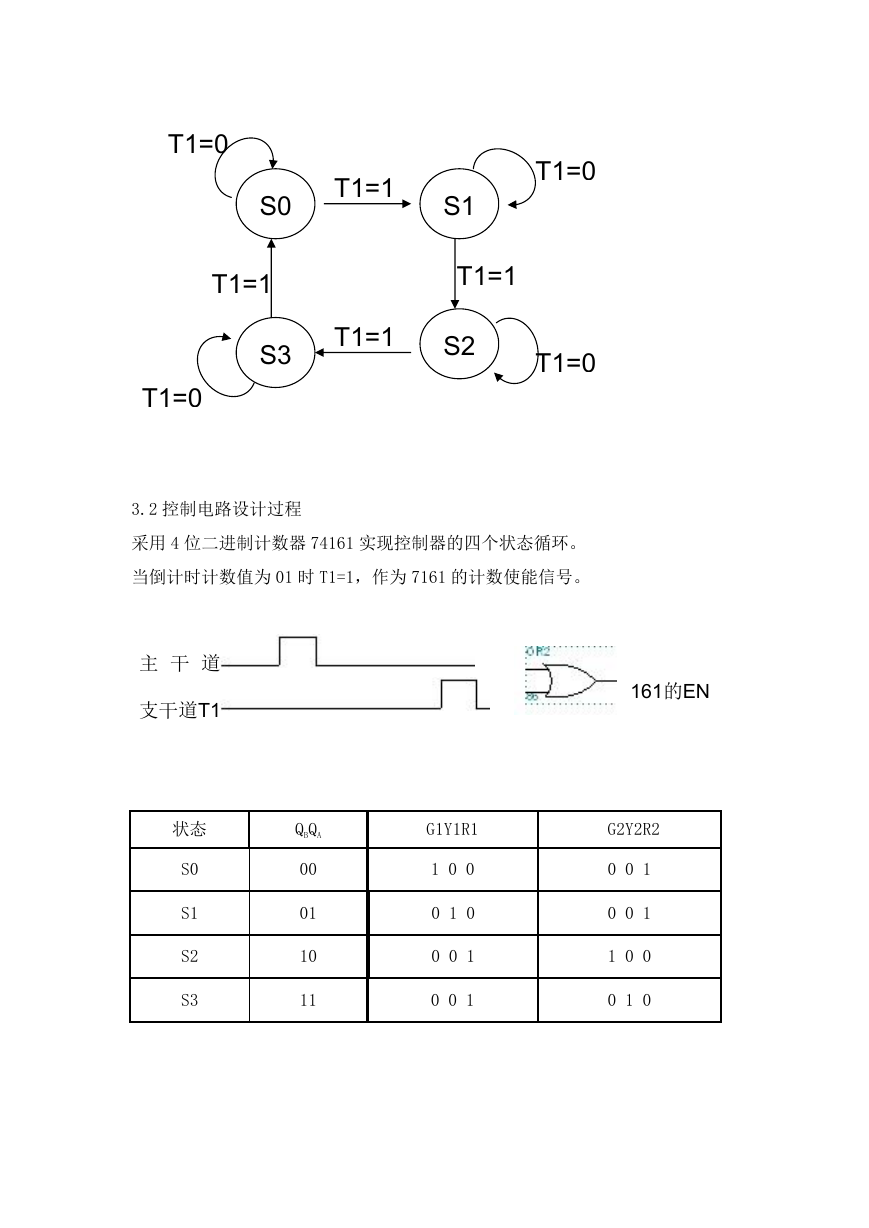

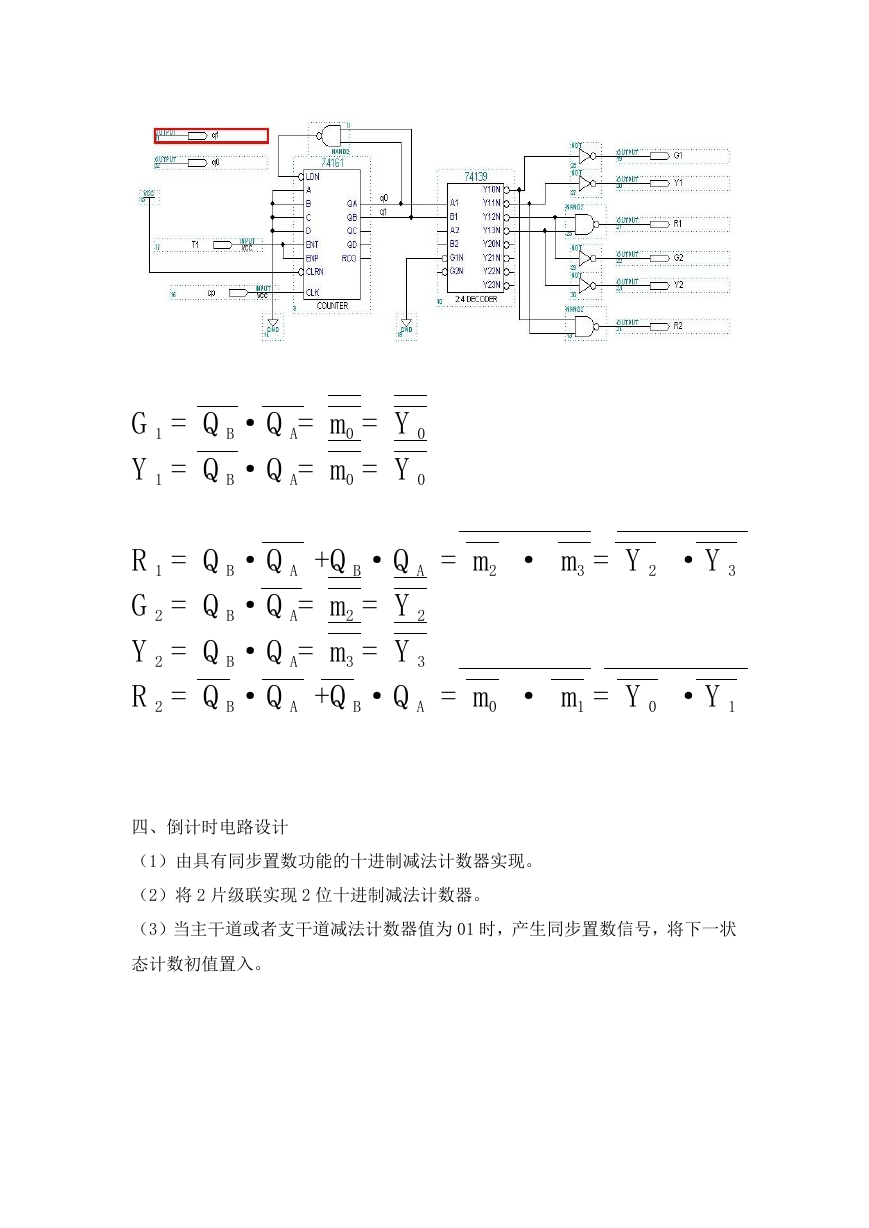

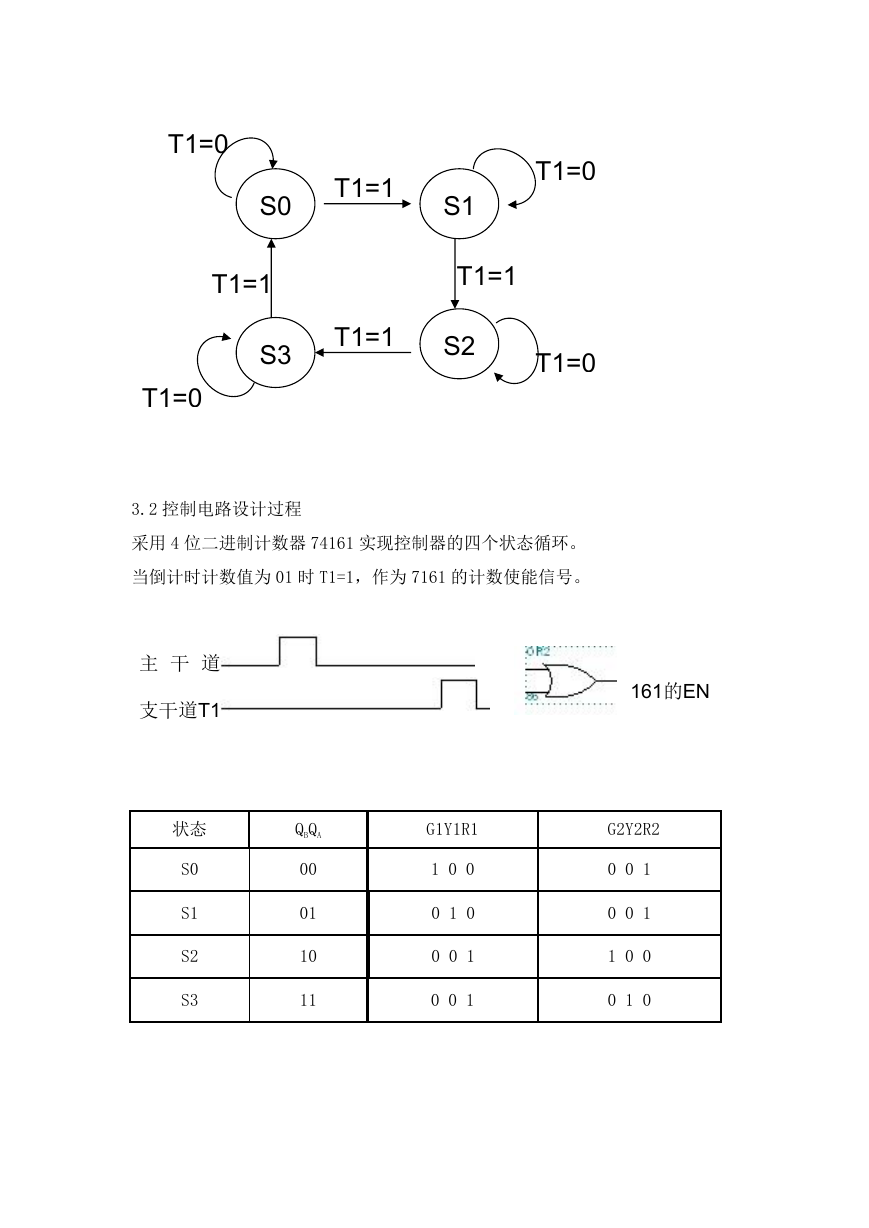

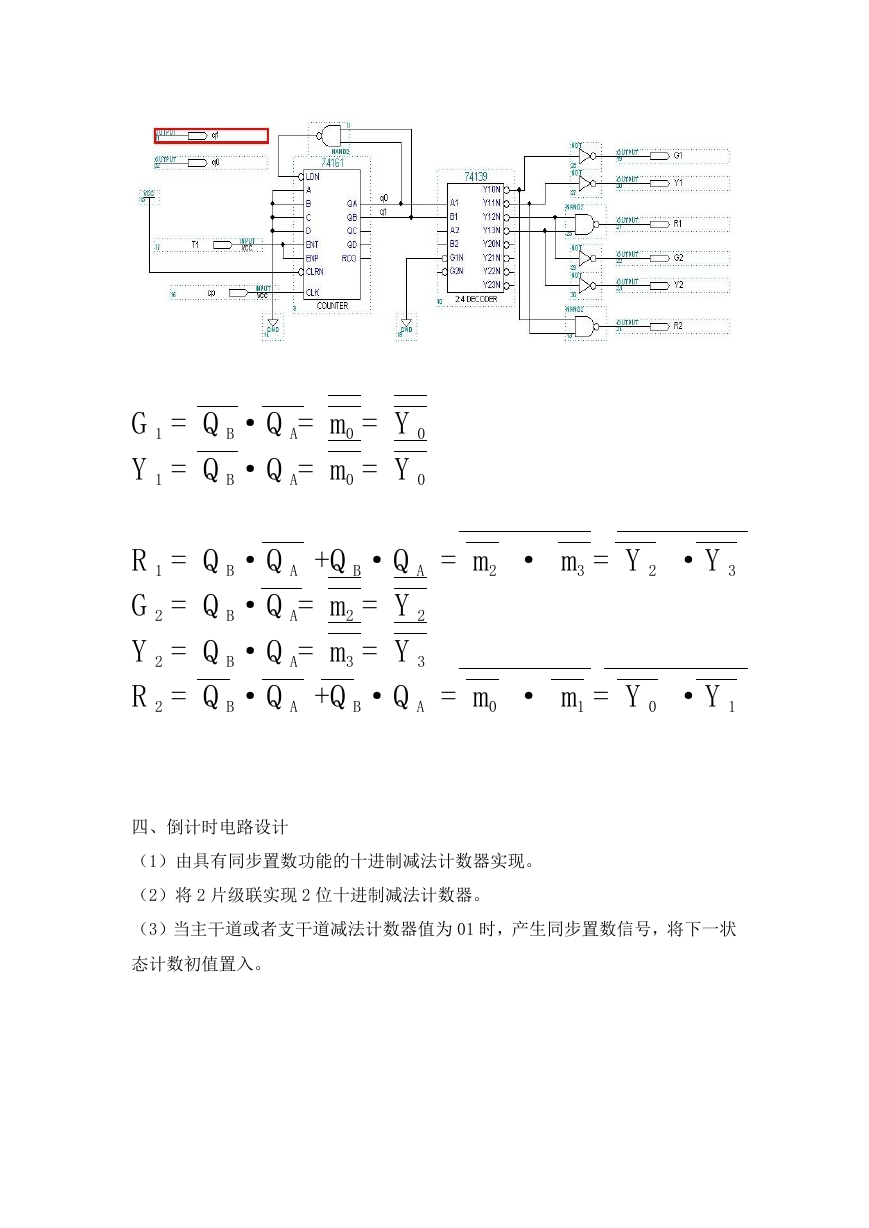

3.2 控制电路设计过程

采用 4 位二进制计数器 74161 实现控制器的四个状态循环。

当倒计时计数值为 01 时 T1=1,作为 7161 的计数使能信号。

主 干 道

支干道T1

161的EN

状态

QBQA

G1Y1R1

G2Y2R2

S0

S1

S2

S3

00

01

10

11

1 0 0

0 1 0

0 0 1

0 0 1

0 0 1

0 0 1

1 0 0

0 1 0

�

G 1 = Q B·Q A= m0 = Y 0

Y 1 = Q B·Q A= m0 = Y 0

R 1 = Q B·Q A +Q B·Q A = m2 · m3 = Y 2 ·Y 3

G 2 = Q B·Q A= m2 = Y 2

Y 2 = Q B·Q A= m3 = Y 3

R 2 = Q B·Q A +Q B·Q A = m0 · m1 = Y 0 ·Y 1

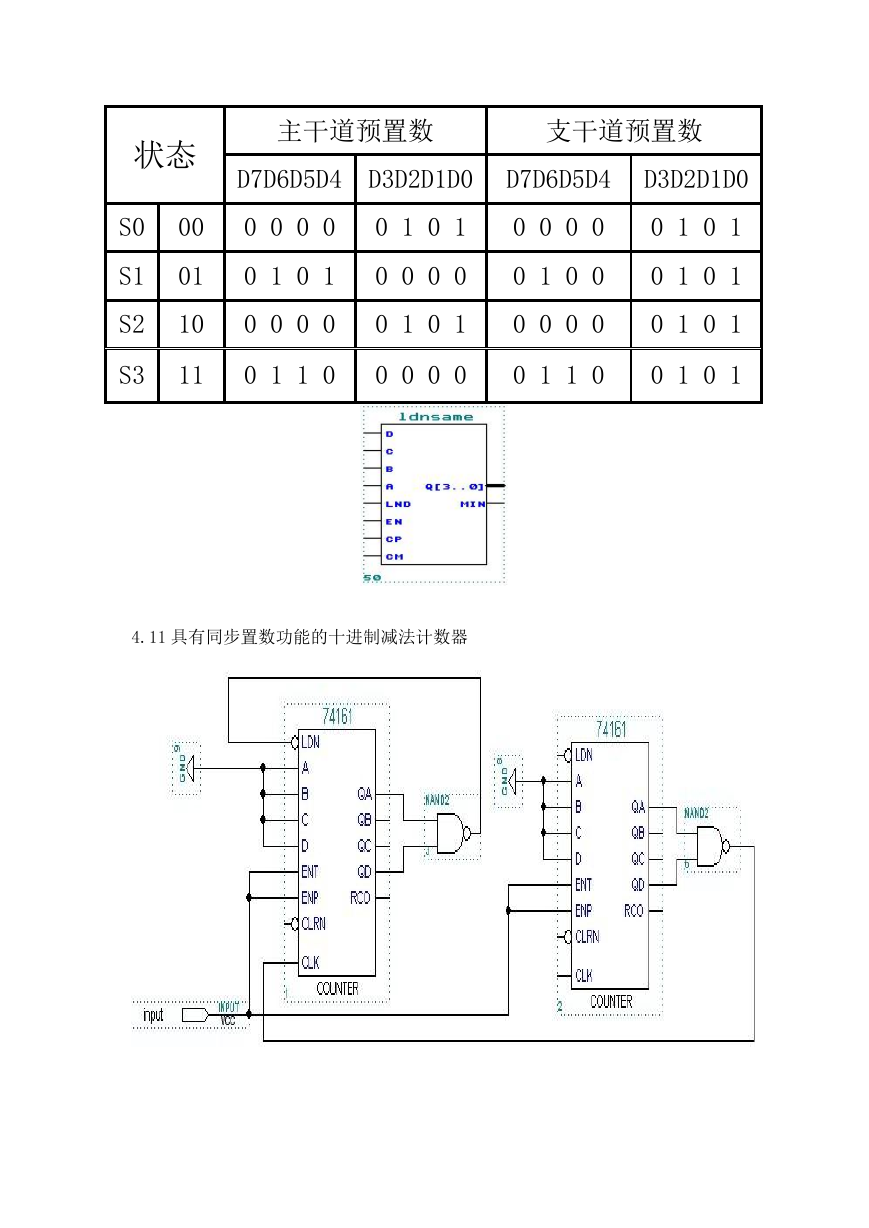

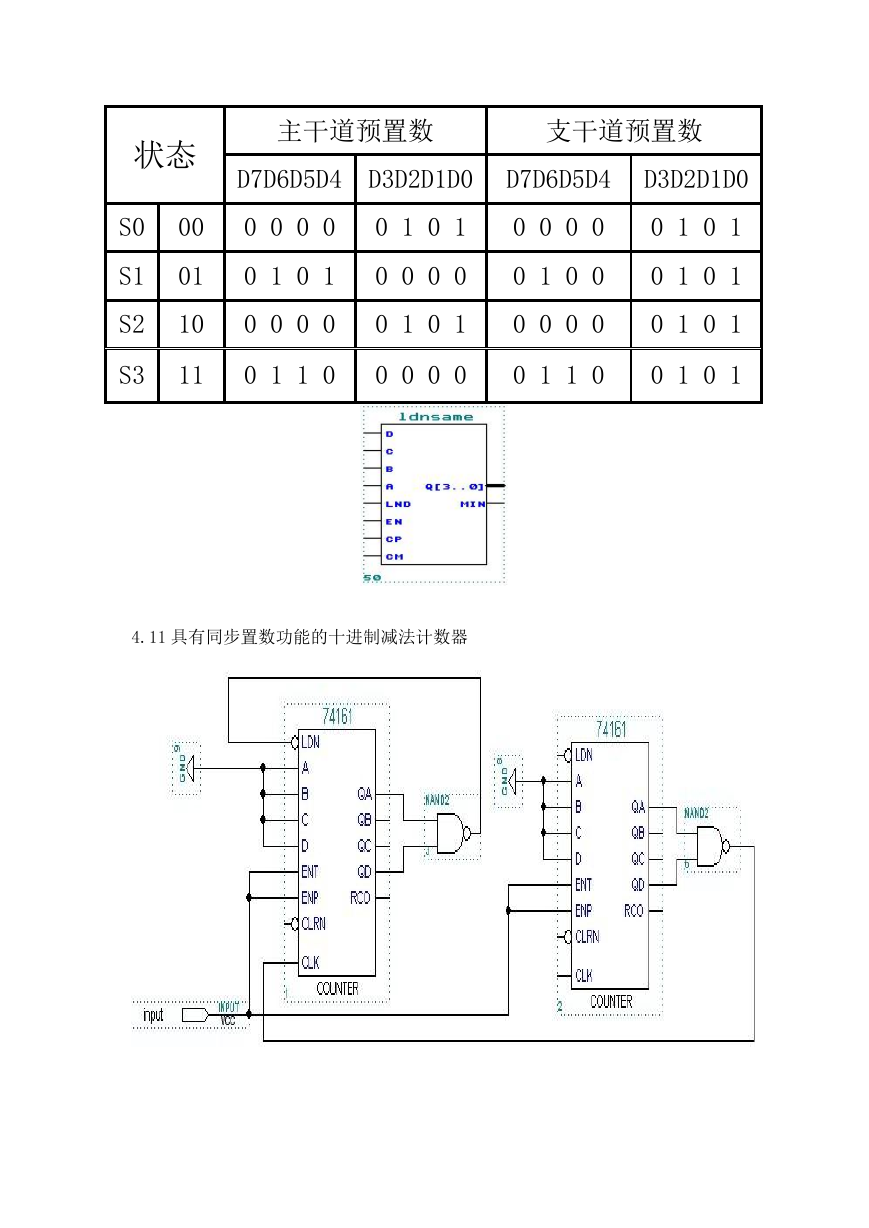

四、倒计时电路设计

(1)由具有同步置数功能的十进制减法计数器实现。

(2)将 2 片级联实现 2 位十进制减法计数器。

(3)当主干道或者支干道减法计数器值为 01 时,产生同步置数信号,将下一状

态计数初值置入。

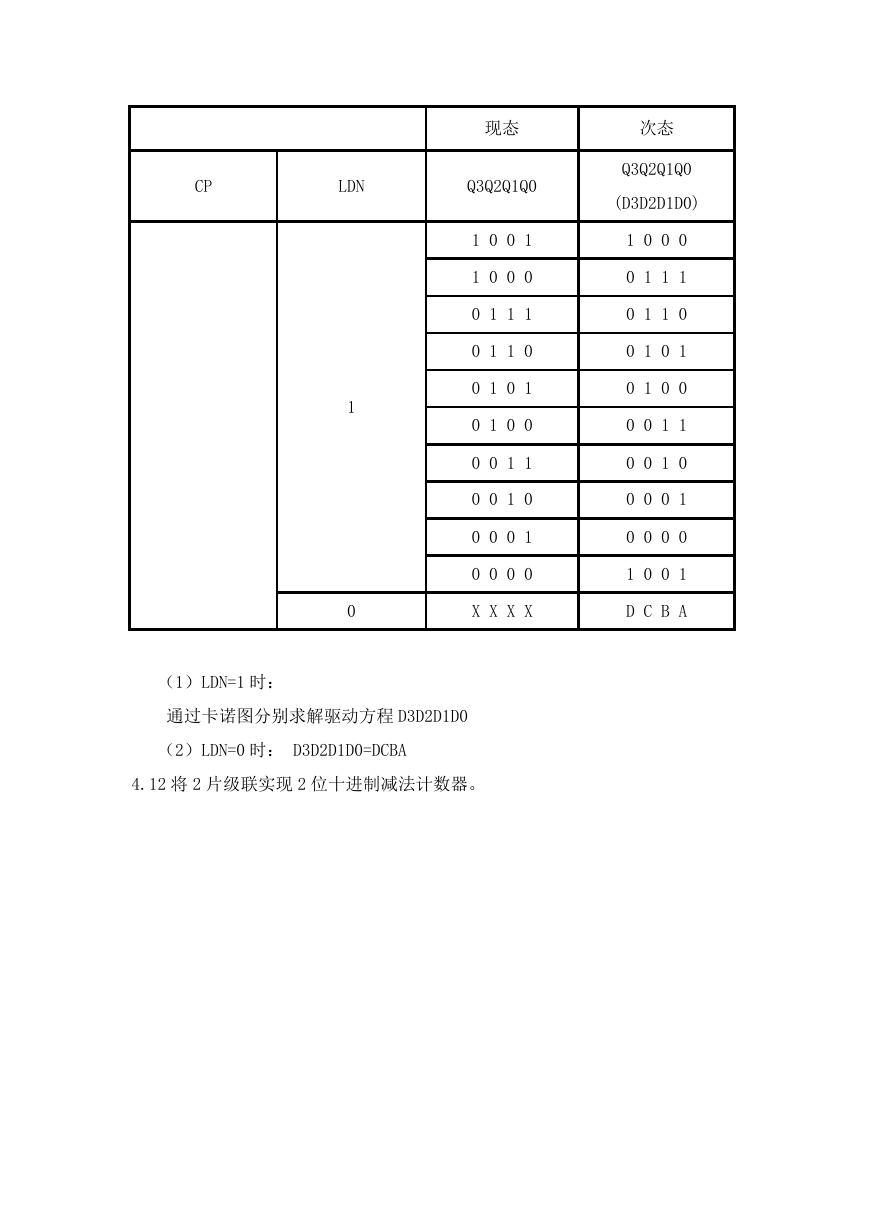

�

状态

S0

S1

S2

S3

00

01

10

11

主干道预置数

支干道预置数

D7D6D5D4 D3D2D1D0

D7D6D5D4

D3D2D1D0

0 0 0 0

0 1 0 1

0 0 0 0

0 1 0 1

0 1 0 1

0 0 0 0

0 1 0 0

0 1 0 1

0 0 0 0

0 1 0 1

0 0 0 0

0 1 0 1

0 1 1 0

0 0 0 0

0 1 1 0

0 1 0 1

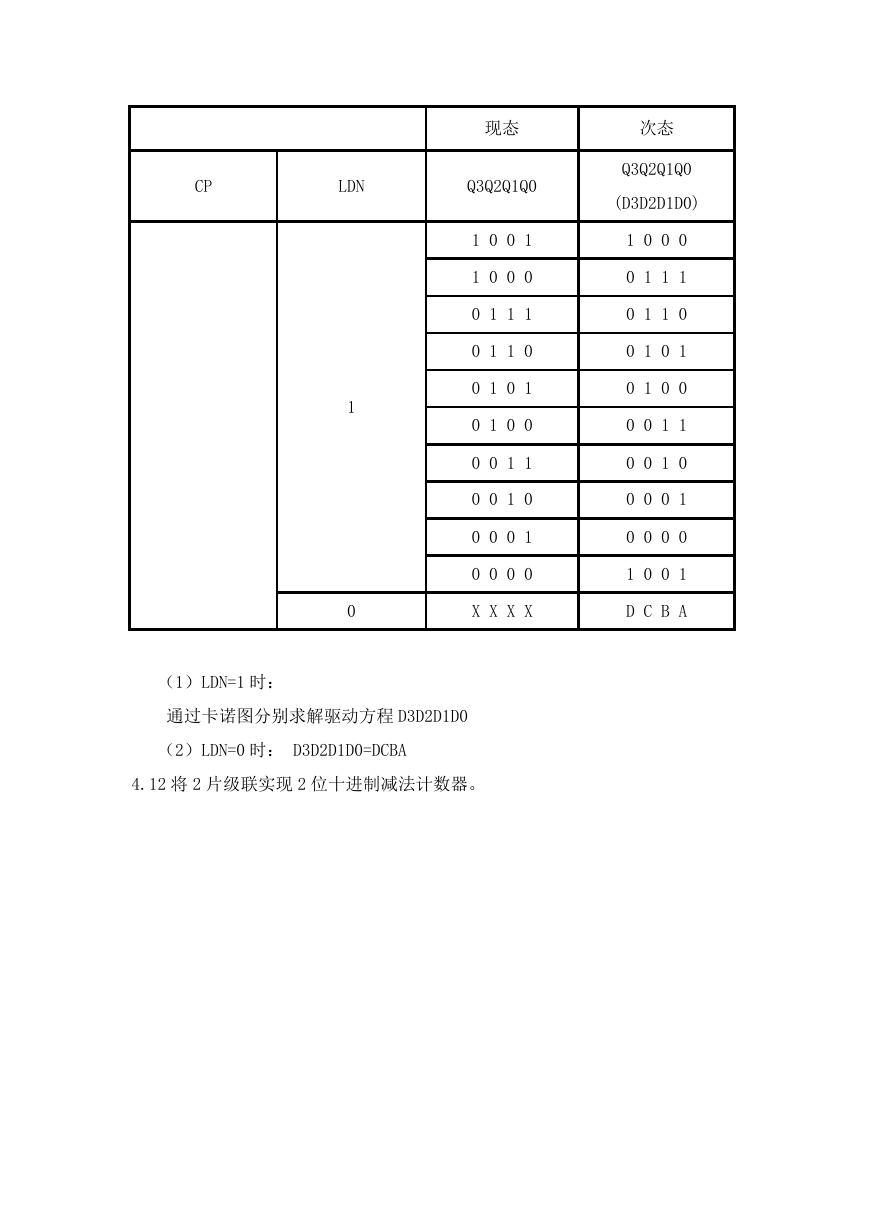

4.11 具有同步置数功能的十进制减法计数器

�

现态

次态

CP

LDN

Q3Q2Q1Q0

1 0 0 1

1 0 0 0

0 1 1 1

0 1 1 0

0 1 0 1

0 1 0 0

0 0 1 1

0 0 1 0

0 0 0 1

0 0 0 0

X X X X

1

0

Q3Q2Q1Q0

(D3D2D1D0)

1 0 0 0

0 1 1 1

0 1 1 0

0 1 0 1

0 1 0 0

0 0 1 1

0 0 1 0

0 0 0 1

0 0 0 0

1 0 0 1

D C B A

(1)LDN=1 时:

通过卡诺图分别求解驱动方程 D3D2D1D0

(2)LDN=0 时: D3D2D1D0=DCBA

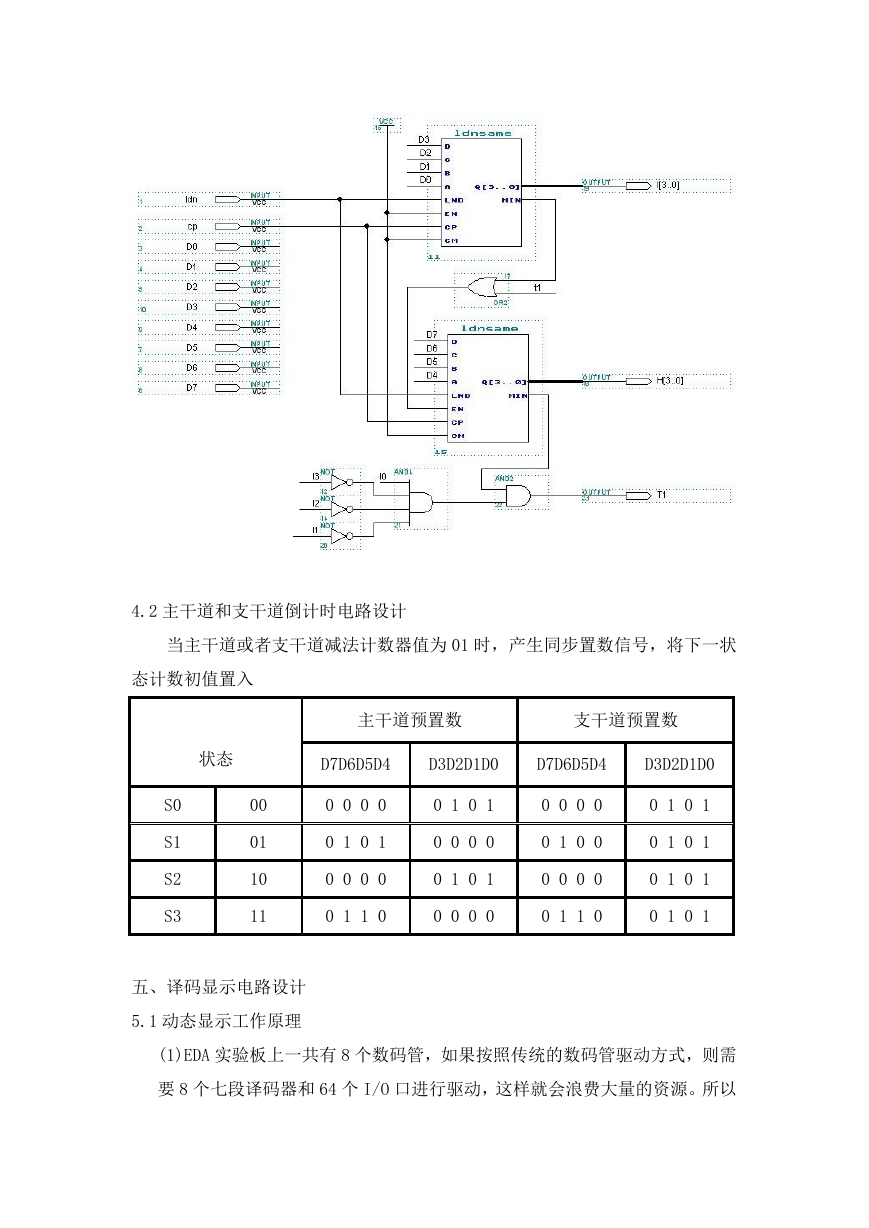

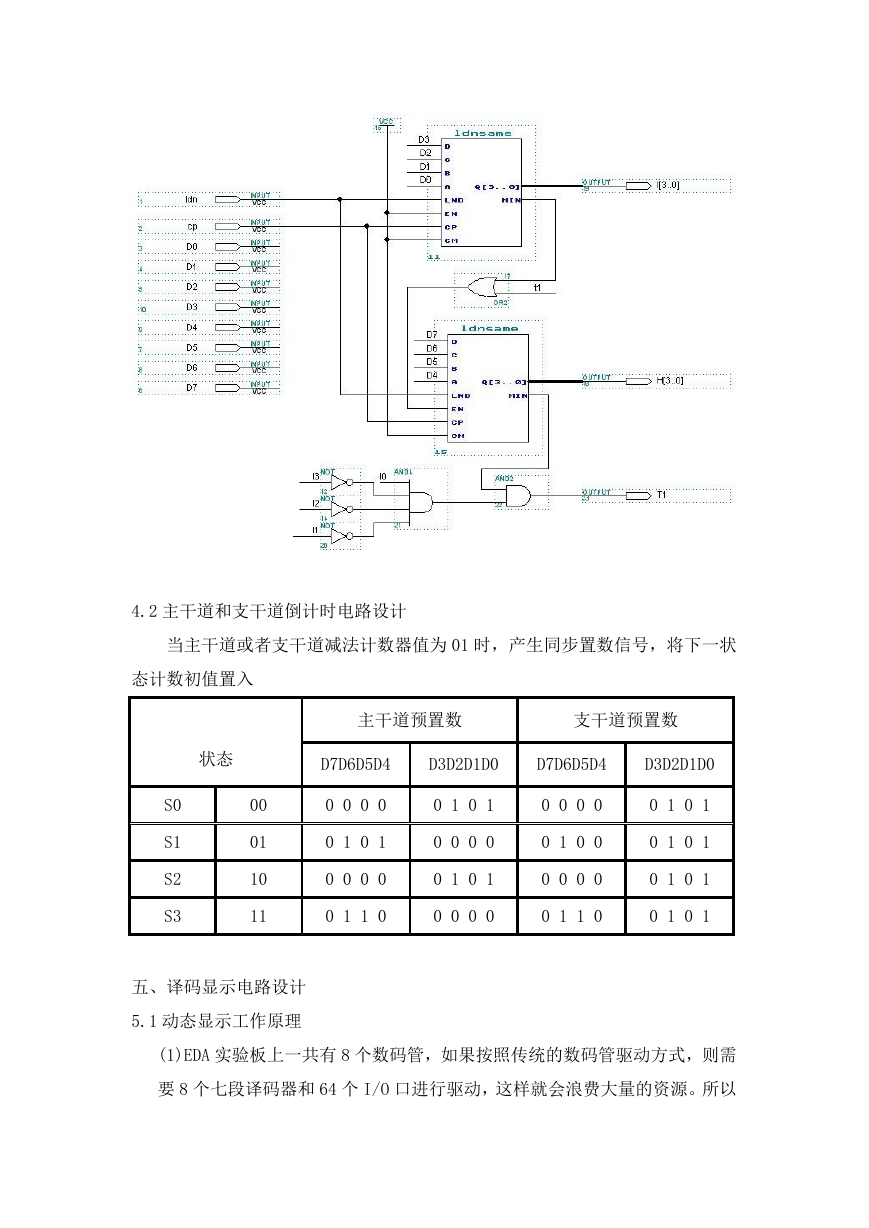

4.12 将 2 片级联实现 2 位十进制减法计数器。

�

4.2 主干道和支干道倒计时电路设计

当主干道或者支干道减法计数器值为 01 时,产生同步置数信号,将下一状

态计数初值置入

主干道预置数

支干道预置数

状态

D7D6D5D4

D3D2D1D0

D7D6D5D4

D3D2D1D0

S0

S1

S2

S3

00

01

10

11

0 0 0 0

0 1 0 1

0 0 0 0

0 1 0 1

0 1 0 1

0 0 0 0

0 1 0 0

0 1 0 1

0 0 0 0

0 1 0 1

0 0 0 0

0 1 0 1

0 1 1 0

0 0 0 0

0 1 1 0

0 1 0 1

五、译码显示电路设计

5.1 动态显示工作原理

(1)EDA 实验板上一共有 8 个数码管,如果按照传统的数码管驱动方式,则需

要 8 个七段译码器和 64 个 I/O 口进行驱动,这样就会浪费大量的资源。所以

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc