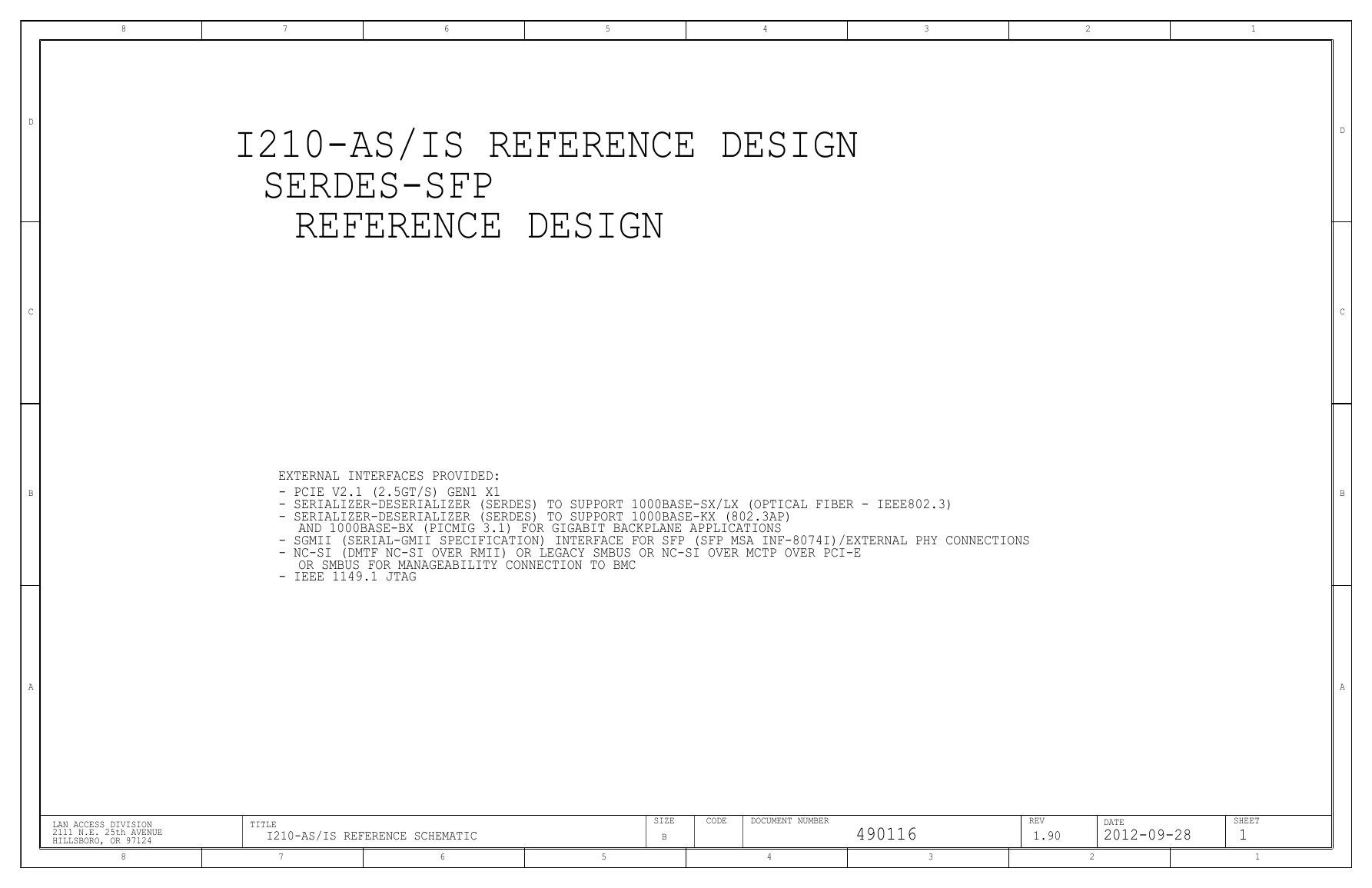

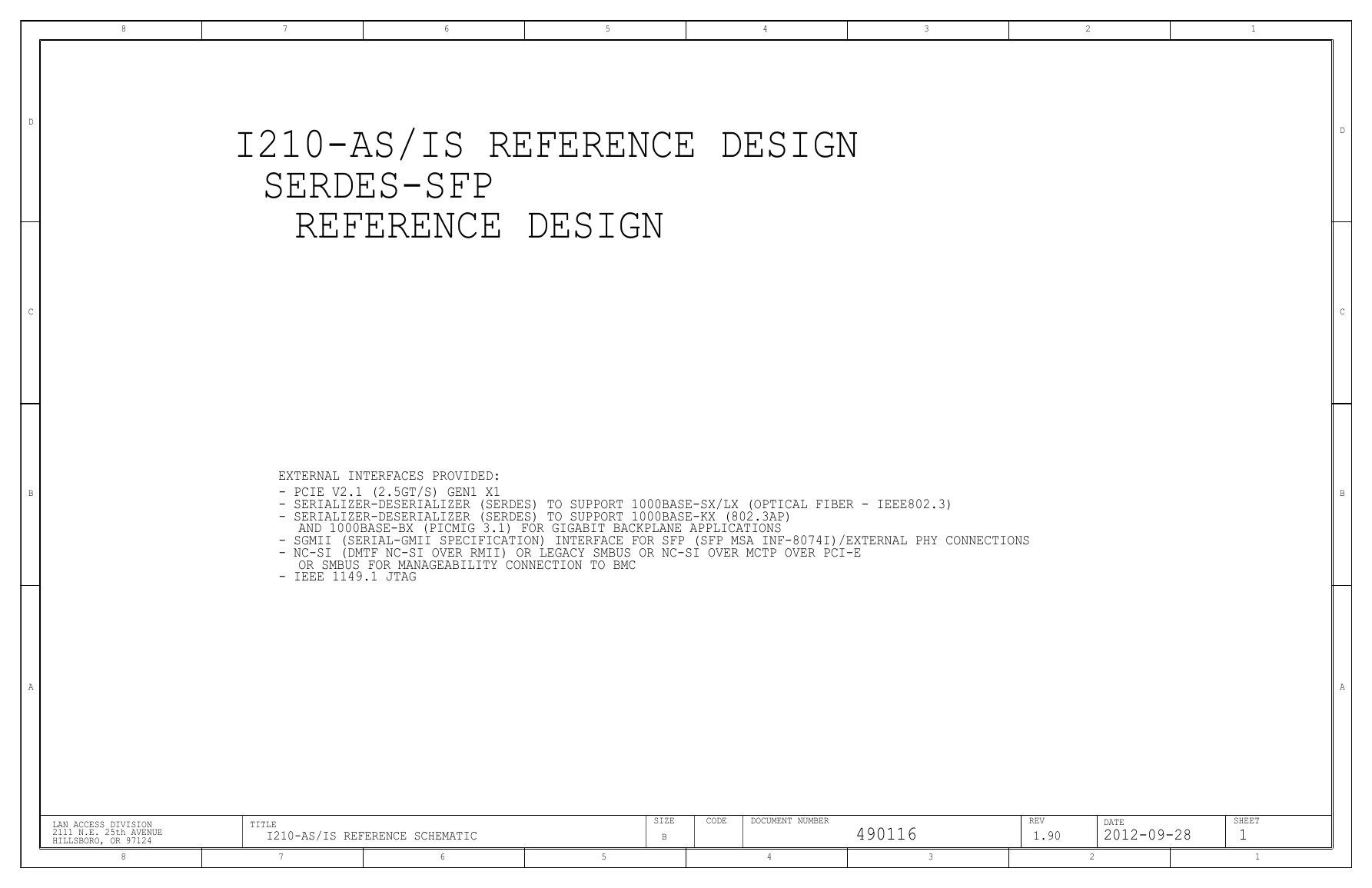

I210-AS/IS REFERENCE DESIGN

SERDES-SFP

REFERENCE DESIGN

EXTERNAL INTERFACES PROVIDED:

- PCIE V2.1 (2.5GT/S) GEN1 X1

- SERIALIZER-DESERIALIZER (SERDES) TO SUPPORT 1000BASE-SX/LX (OPTICAL FIBER - IEEE802.3)

- SERIALIZER-DESERIALIZER (SERDES) TO SUPPORT 1000BASE-KX (802.3AP)

AND 1000BASE-BX (PICMIG 3.1) FOR GIGABIT BACKPLANE APPLICATIONS

- SGMII (SERIAL-GMII SPECIFICATION) INTERFACE FOR SFP (SFP MSA INF-8074I)/EXTERNAL PHY CONNECTIONS

- NC-SI (DMTF NC-SI OVER RMII) OR LEGACY SMBUS OR NC-SI OVER MCTP OVER PCI-E

OR SMBUS FOR MANAGEABILITY CONNECTION TO BMC

- IEEE 1149.1 JTAG

I210-AS/IS REFERENCE SCHEMATIC

490116

1.90

2012-09-28

1

DOCUMENT NUMBERREVDATECODEBSIZETITLESHEET 54A12ABC78BCDD1345678263LAN ACCESS DIVISION2111 N.E. 25th AVENUEHILLSBORO, OR 97124�

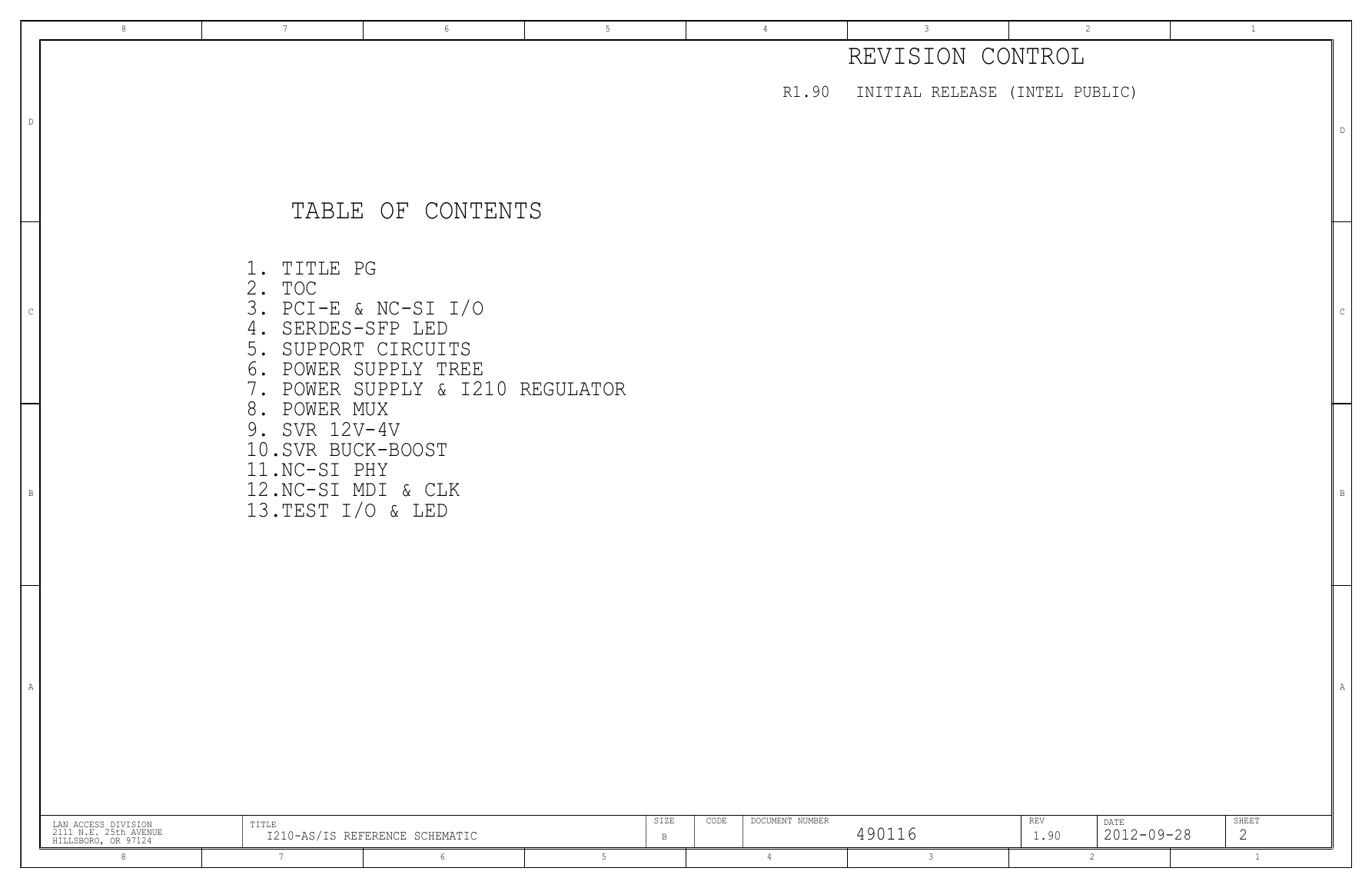

REVISION CONTROL

INITIAL RELEASE (INTEL PUBLIC)

R1.90

TABLE OF CONTENTS

1. TITLE PG

2. TOC

3. PCI-E & NC-SI I/O

4. SERDES-SFP LED

5. SUPPORT CIRCUITS

6. POWER SUPPLY TREE

7. POWER SUPPLY & I210 REGULATOR

8. POWER MUX

9. SVR 12V-4V

10.SVR BUCK-BOOST

11.NC-SI PHY

12.NC-SI MDI & CLK

13.TEST I/O & LED

I210-AS/IS REFERENCE SCHEMATIC

490116

1.90

2012-09-28

2

DOCUMENT NUMBERREVDATECODEBSIZETITLESHEET 54A12ABC78BCDD1345678263LAN ACCESS DIVISION2111 N.E. 25th AVENUEHILLSBORO, OR 97124�

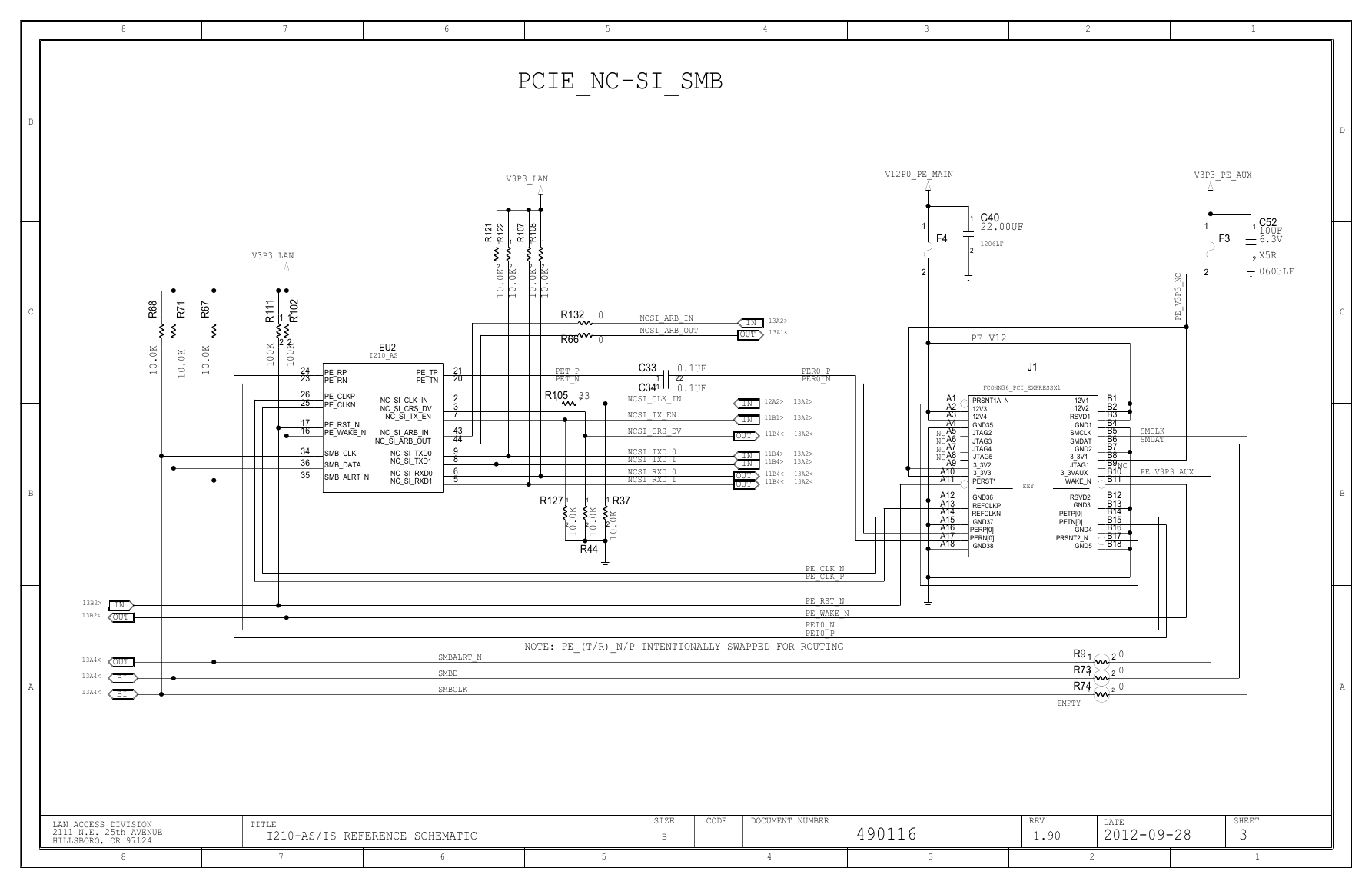

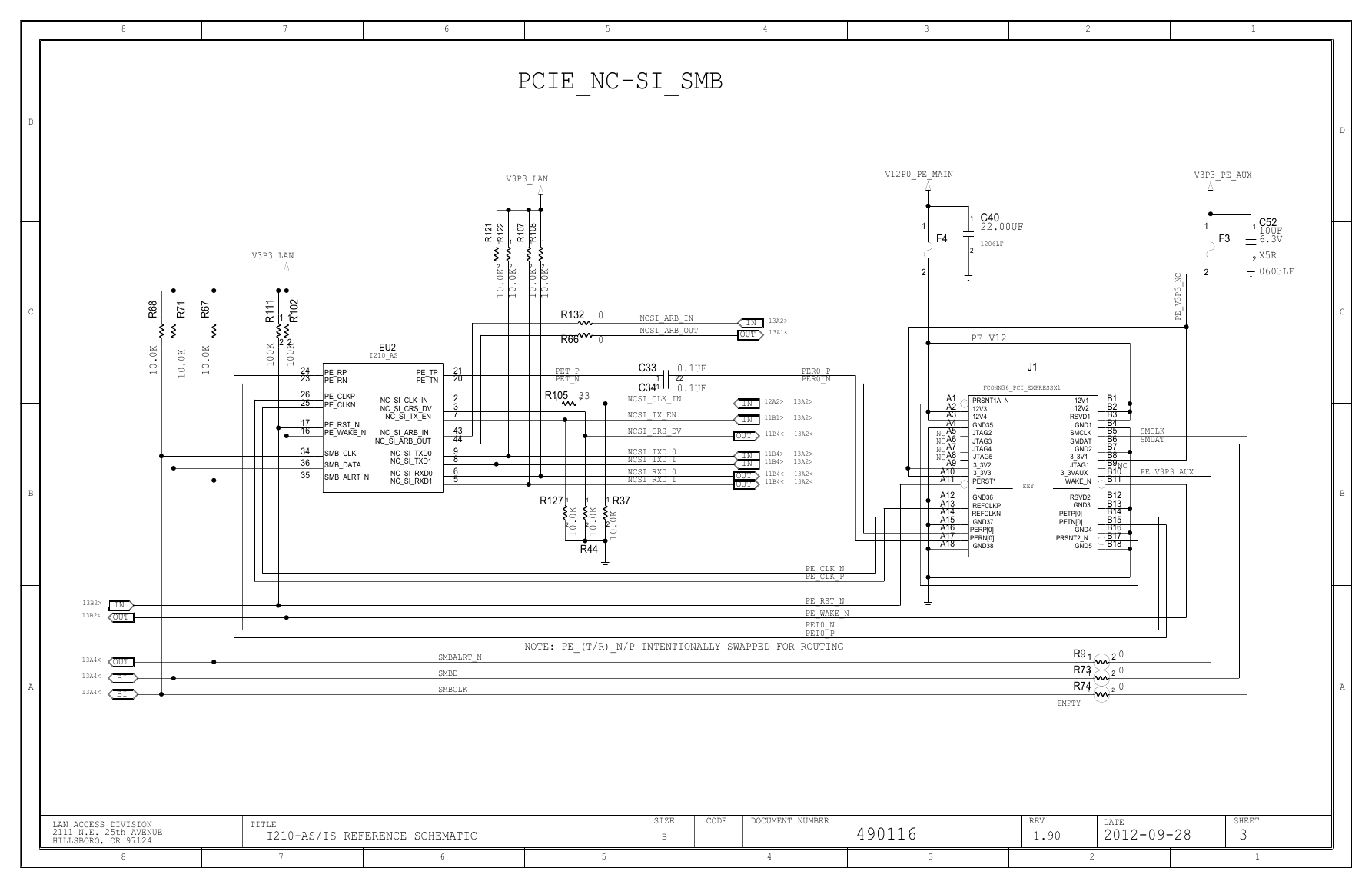

PCIE_NC-SI_SMB

V3P3_LAN

8

6

R

1

7

R

7

6

R

1

1

1

1R

2

0

1

1R

K

0

.

0

1

K

0

.

0

1

K

0

.

0

1

2

2

K

0

0

1

K

0

0

1

24

23

26

25

17

16

34

36

35

V3P3_LAN

1

2

1

2

2

1

7

0

1

8

0

1

1R

1R

1R

1R

2

2

K

0

.

0

1

K

0

.

0

1

2

2

K

0

.

0

1

K

0

.

0

1

R132

R66

0

0

PET_P

PET_N

1R105

33

2

EU2

21

20

2

3

7

43

44

9

8

6

5

C33

1

1C34

0.1UF

2

2

0.1UF

NCSI_CLK_IN

NCSI_TX_EN

NCSI_CRS_DV

NCSI_TXD_0

NCSI_TXD_1

NCSI_RXD_0

NCSI_RXD_1

R127

1

K

0

.

2

0

1

1

K

0

.

2

0

1

1 R37

K

0

2

.

0

1

R44

1

2

NCSI_ARB_IN

NCSI_ARB_OUT

13A2>

13A1<

V12P0_PE_MAIN

V3P3_PE_AUX

1 C40

22.00UF

1206LF

F4

2

F3

1

2

1 C52

10UF

6.3V

X5R

0603LF

2

C

N

_

3

P

3

V

_

E

P

PE_V12

J1

A1

A2

A3

A4

A5

NC

A6

NC

A7

NC

A8

NC

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

SMCLK

SMDAT

PE_V3P3_AUX

B1

B2

B3

B4

B5

B6

B7

B8

B9

NC

B10

B11

B12

B13

B14

B15

B16

B17

B18

PER0_P

PER0_N

12A2> 13A2>

11B1> 13A2>

11B4< 13A2<

11B4>

13A2>

11B4> 13A2>

11B4< 13A2<

11B4< 13A2<

PE_CLK_N

PE_CLK_P

13B2>

13B2<

13A4<

13A4<

13A4<

PE_RST_N

PE_WAKE_N

PET0_N

PET0_P

NOTE: PE_(T/R)_N/P INTENTIONALLY SWAPPED FOR ROUTING

SMBALRT_N

SMBD

SMBCLK

1R9

1R73

1R74

EMPTY

2

2

2

0

0

0

I210-AS/IS REFERENCE SCHEMATIC

490116

1.90

2012-09-28

3

DOCUMENT NUMBERREVDATECODEBSIZETITLESHEET 54A12ABC78BCDD1345678263LAN ACCESS DIVISION2111 N.E. 25th AVENUEHILLSBORO, OR 97124OUTINOUTBIBIINININOUTOUTOUTOUTININKEYFCONN36_PCI_EXPRESSX1PRSNT1A_N12V312V4GND35JTAG2JTAG3JTAG4JTAG53_3V23_3V3REFCLKNREFCLKPGND36PERST*GND37WAKE_NRSVD23_3VAUXJTAG13_3V1GND2SMDATSMCLKGND1RSVD112V212V1PETN[0]PETP[0]GND3PERN[0]PERP[0]GND38GND4PRSNT2_NGND5I210_ASNC_SI_RXD1NC_SI_RXD0NC_SI_TXD1NC_SI_TXD0NC_SI_ARB_OUTNC_SI_ARB_INNC_SI_TX_ENNC_SI_CRS_DVNC_SI_CLK_INPE_TNPE_TPSMB_ALRT_NSMB_DATASMB_CLKPE_WAKE_NPE_RST_NPE_CLKNPE_CLKPPE_RNPE_RP�

V3P3_LAN_SUPPORT

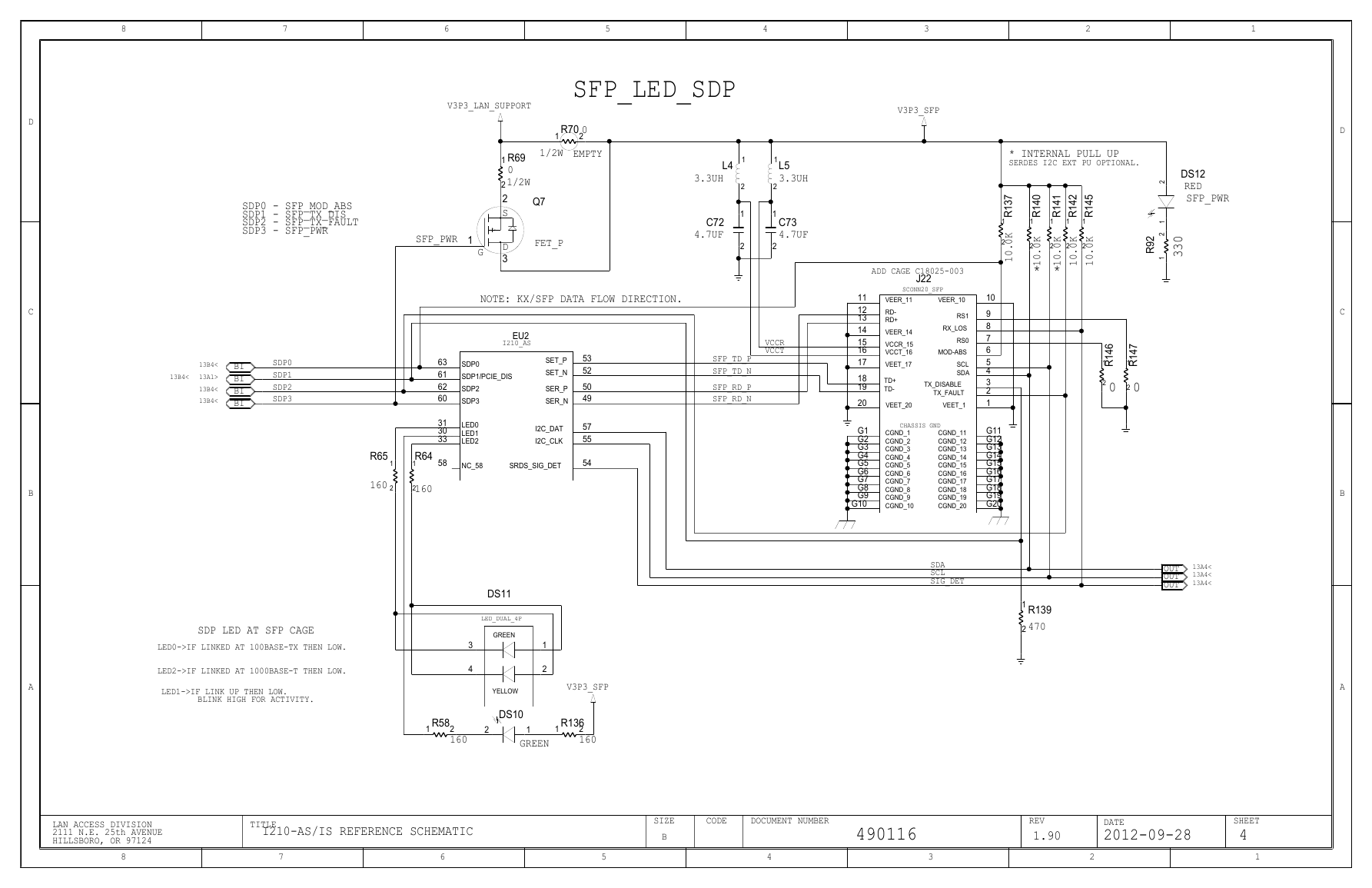

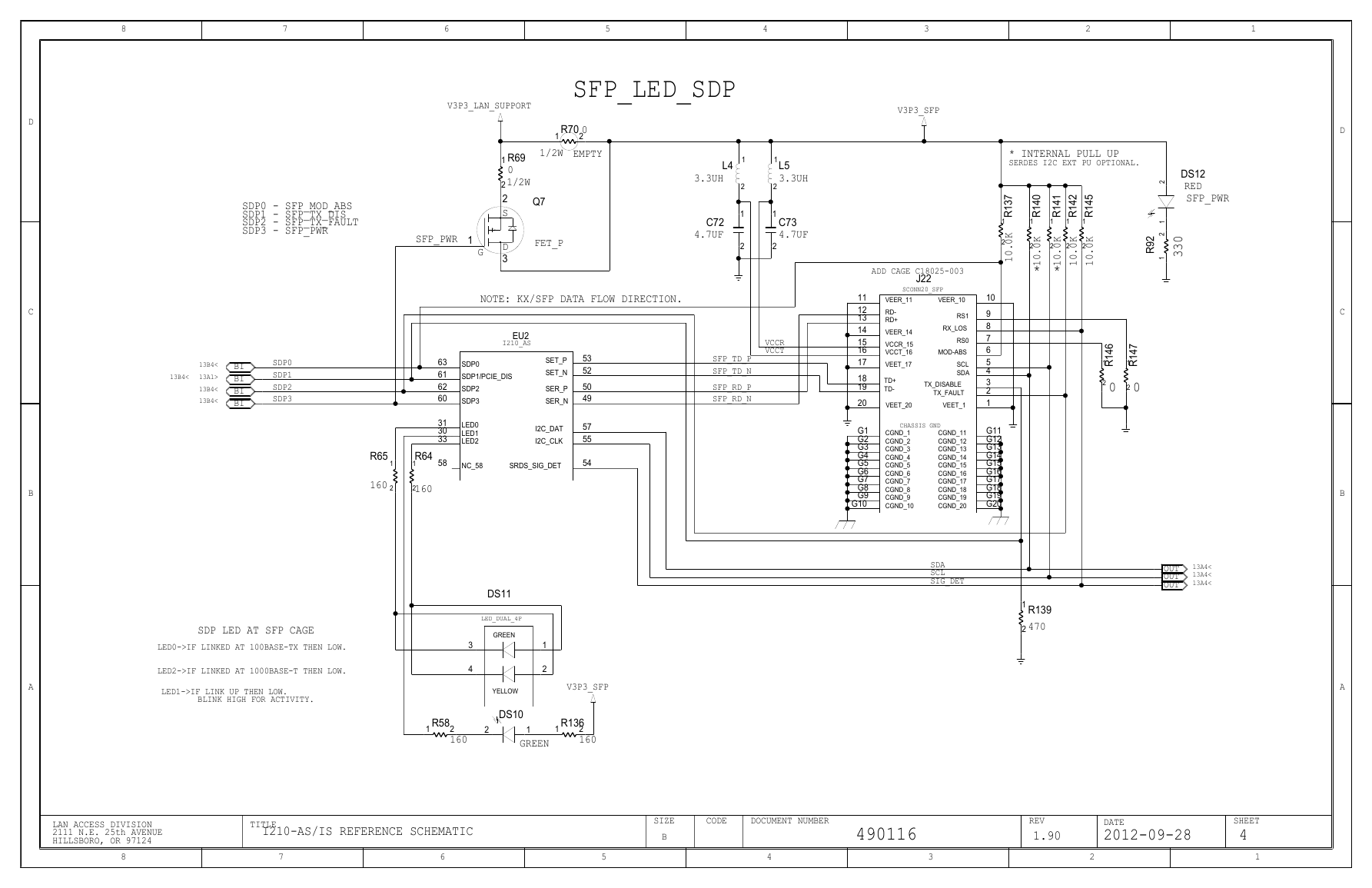

SFP_LED_SDP

V3P3_SFP

SDP0 - SFP_MOD_ABS

SDP1 - SFP_TX_DIS

SDP2 - SFP_TX_FAULT

SDP3 - SFP_PWR

SFP_PWR

1

1 R70

0

2

1/2W EMPTY

Q7

1 R69

0

1/2W

2

2

3

NOTE: KX/SFP DATA FLOW DIRECTION.

EU2

13B4<

13B4< 13A1>

13B4<

13B4<

SDP0

SDP1

SDP2

SDP3

63

61

62

60

31

30

33

58

R65

160

1

2

R64

1

160

2

53

52

50

49

57

55

54

L4

3.3UH

C72

4.7UF

1

2

1

2

1L5

3.3UH

2

1

2

C73

4.7UF

VCCR

VCCT

SFP_TD_P

SFP_TD_N

SFP_RD_P

SFP_RD_N

SDP LED AT SFP CAGE

LED0->IF LINKED AT 100BASE-TX THEN LOW.

LED2->IF LINKED AT 1000BASE-T THEN LOW.

LED1->IF LINK UP THEN LOW.

BLINK HIGH FOR ACTIVITY.

DS11

3

4

1

2

V3P3_SFP

1 R58

2

160

2

DS10

1

GREEN

1 R136

2

160

2

DS12

RED

SFP_PWR

1

2

2

9

R

1

0

3

3

* INTERNAL PULL UP

SERDES I2C EXT PU OPTIONAL.

0

4

1

R

1

1

4

1

R

1

2

4

1

R

1

5

4

1

R

1

K

2

0

.

0

1

K

K

K

2

2

2

0

0

0

.

.

.

0

0

0

1

1

1

**

6

4

1

1R

2

0

7

4

1

1R

2

0

7

3

1

R

1

K

2

0

.

0

1

10

9

8

7

6

5

4

3

2

1

G11

G12

G13

G14

G15

G16

G17

G18

G19

G20

ADD CAGE C18025-003

J22

11

12

13

14

15

16

17

18

19

20

G1

G2

G3

G4

G5

G6

G7

G8

G9

G10

SDA

SCL

SIG_DET

1

2

R139

470

13A4<

13A4<

13A4<

I210-AS/IS REFERENCE SCHEMATIC

490116

1.90

2012-09-28

4

DOCUMENT NUMBERREVDATECODEBSIZETITLESHEET 54A12ABC78BCDD1345678263LAN ACCESS DIVISION2111 N.E. 25th AVENUEHILLSBORO, OR 97124LED_DUAL_4PYELLOWGREENFET_PSGDCHASSIS GNDSCONN20_SFPVEER_11RX_LOSRS1VEER_10RS0MOD-ABSSCLSDATX_DISABLETX_FAULTVEET_1RD-RD+VEER_14VCCR_15VCCT_16VEET_17TD+TD-VEET_20CGND_20CGND_18CGND_19CGND_17CGND_16CGND_15CGND_13CGND_14CGND_12CGND_11CGND_9CGND_10CGND_8CGND_6CGND_7CGND_5CGND_4CGND_3CGND_1CGND_2I210_ASSER_PSER_NSET_NSET_PSRDS_SIG_DETI2C_CLKI2C_DATNC_58LED2LED1LED0SDP3SDP2SDP1/PCIE_DISSDP0BIBIBIBIOUTOUTOUT�

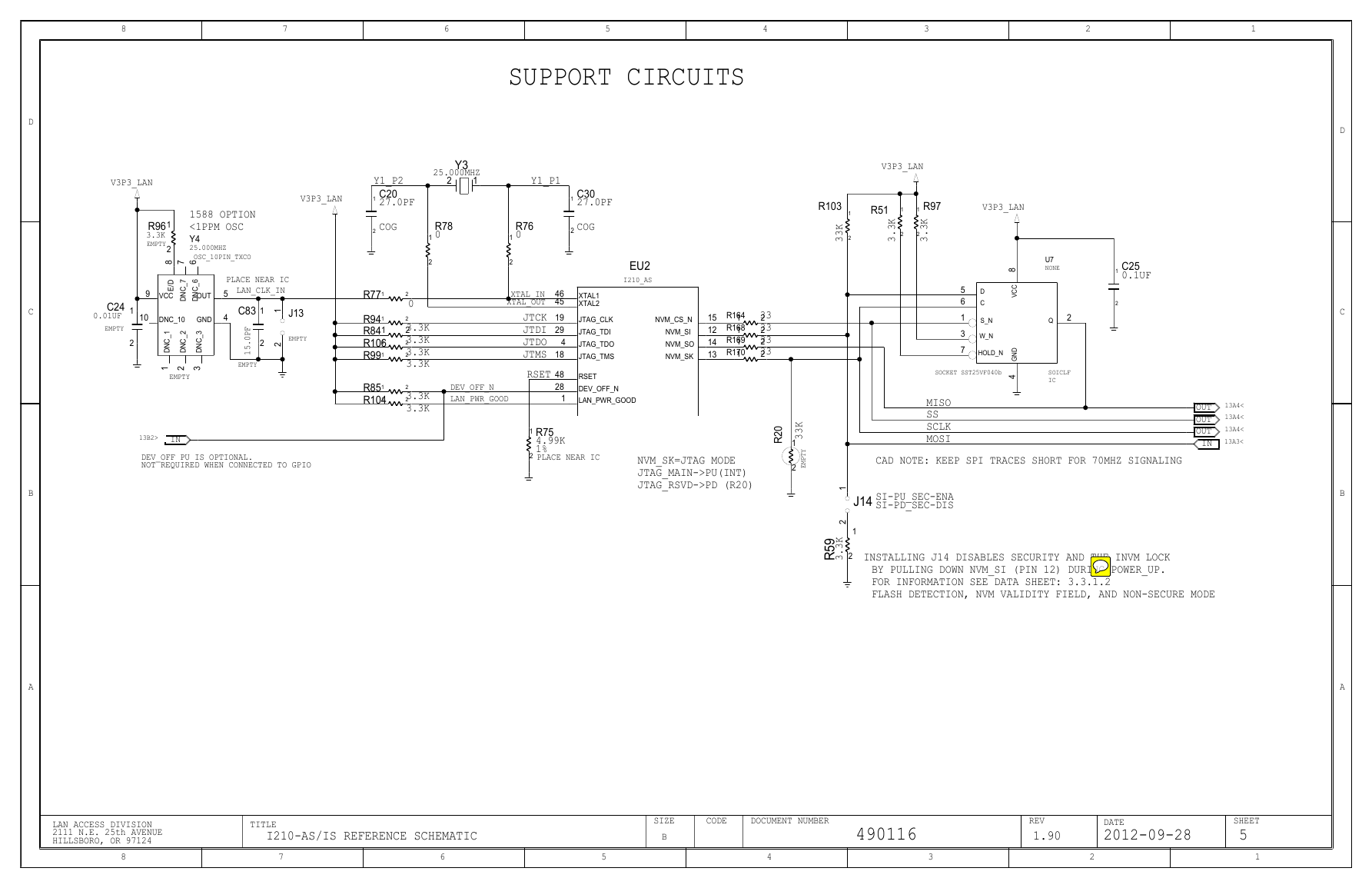

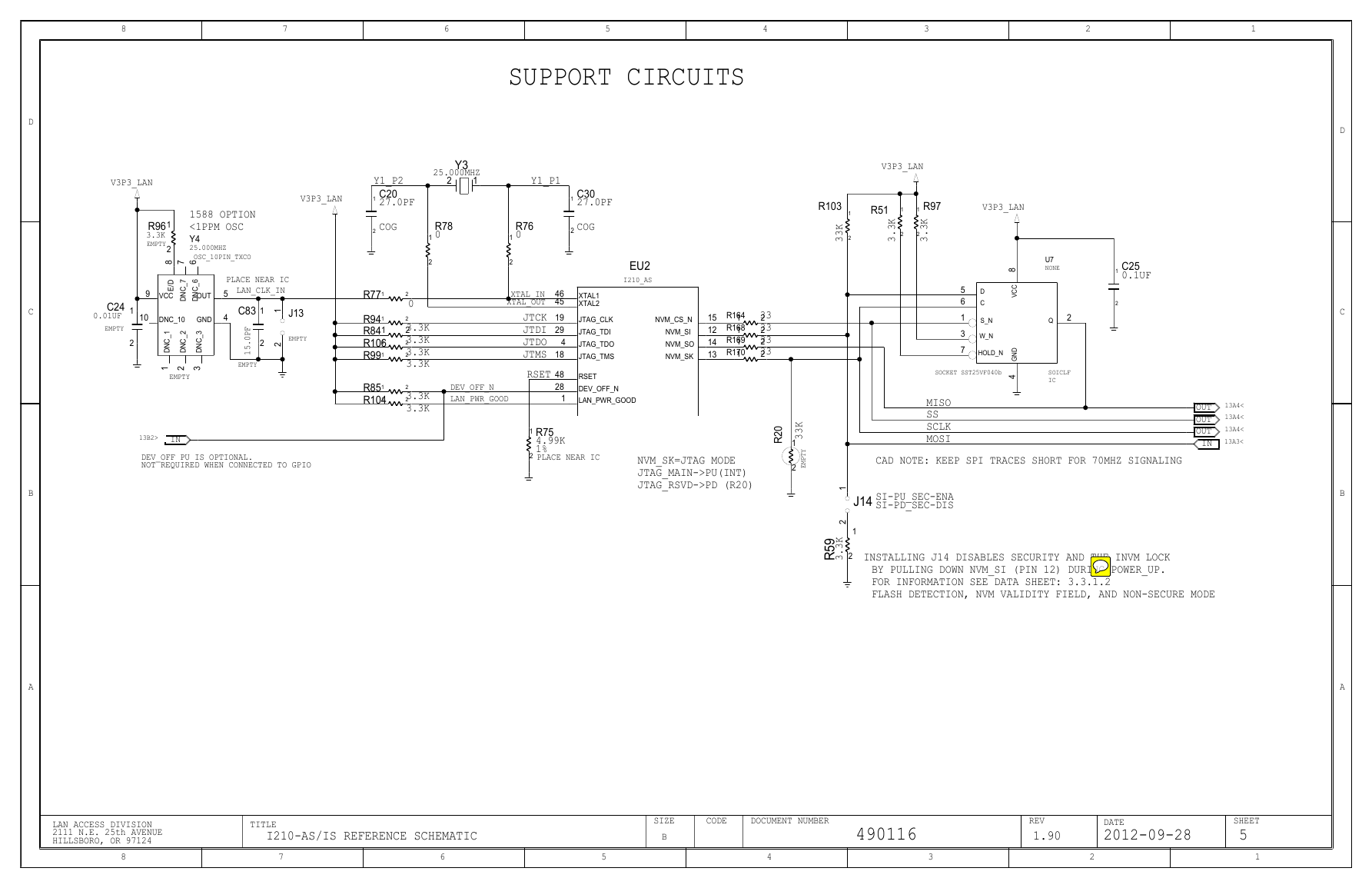

SUPPORT CIRCUITS

Y3

25.000MHZ

1

2

Y1_P1

R78

0

1

2

R76

0

1

2

1 C30

27.0PF

COG

2

EU2

1R77

1R94

1R84

1R106

1R99

1R85

1R104

2

0

2

3.3K

2

3.3K

2

3.3K

3.3K

2

2

2

3.3K

3.3K

XTAL_IN

XTAL_OUT

JTCK

JTDI

JTDO

JTMS

RSET

DEV_OFF_N

LAN_PWR_GOOD

46

45

19

29

4

18

48

28

1

1 R75

4.99K

1%

PLACE NEAR IC

2

15

12

14

13

1R164

1R168

1R169

1R170

33

2

33

2

33

2

33

2

0

2

K

3

3

1R

NVM_SK=JTAG MODE

JTAG_MAIN->PU(INT)

JTAG_RSVD->PD (R20)

Y

T

P

M

E

2

V3P3_LAN

1R96

3.3K

EMPTY

2

1588 OPTION

<1PPM OSC

Y4

25.000MHZ

876

V3P3_LAN

Y1_P2

1 C20

27.0PF

COG

2

C24

0.01UF

EMPTY

9

10

1

2

PLACE NEAR IC

LAN_CLK_IN

5

C83

1

4

1 J13

2

2

EMPTY

F

P

0

.

5

1

EMPTY

1

32

EMPTY

13B2>

DEV_OFF PU IS OPTIONAL.

NOT REQUIRED WHEN CONNECTED TO GPIO

V3P3_LAN

R103

1

K

3

2

3

R51

1

K

3

.

2

3

1 R97

K

3

.

2

3

V3P3_LAN

1 C25

0.1UF

2

8

U7

NONE

2

4

SOICLF

IC

5

6

1

3

7

MISO

SS

SCLK

MOSI

13A4<

13A4<

13A4<

13A3<

CAD NOTE: KEEP SPI TRACES SHORT FOR 70MHZ SIGNALING

1

2

J14

SI-PU_SEC-ENA

SI-PD_SEC-DIS

1

9

5

R

K

3

.

3

2

INSTALLING J14 DISABLES SECURITY AND THE INVM LOCK

BY PULLING DOWN NVM_SI (PIN 12) DURING POWER_UP.

FOR INFORMATION SEE DATA SHEET: 3.3.1.2

FLASH DETECTION, NVM VALIDITY FIELD, AND NON-SECURE MODE

I210-AS/IS REFERENCE SCHEMATIC

490116

1.90

2012-09-28

5

DOCUMENT NUMBERREVDATECODEBSIZETITLESHEET 54A12ABC78BCDD1345678263LAN ACCESS DIVISION2111 N.E. 25th AVENUEHILLSBORO, OR 97124INOUTOUTINOUT21OSC_10PIN_TXCODNC_10VCCE/DDNC_7DNC_6OUTGNDDNC_3DNC_2DNC_121SOCKET_SST25VF040bGNDVCCQHOLD_NW_NS_NCDI210_ASNVM_SKNVM_SONVM_SINVM_CS_NLAN_PWR_GOODDEV_OFF_NRSETJTAG_TMSJTAG_TDOJTAG_TDIJTAG_CLKXTAL2XTAL1�

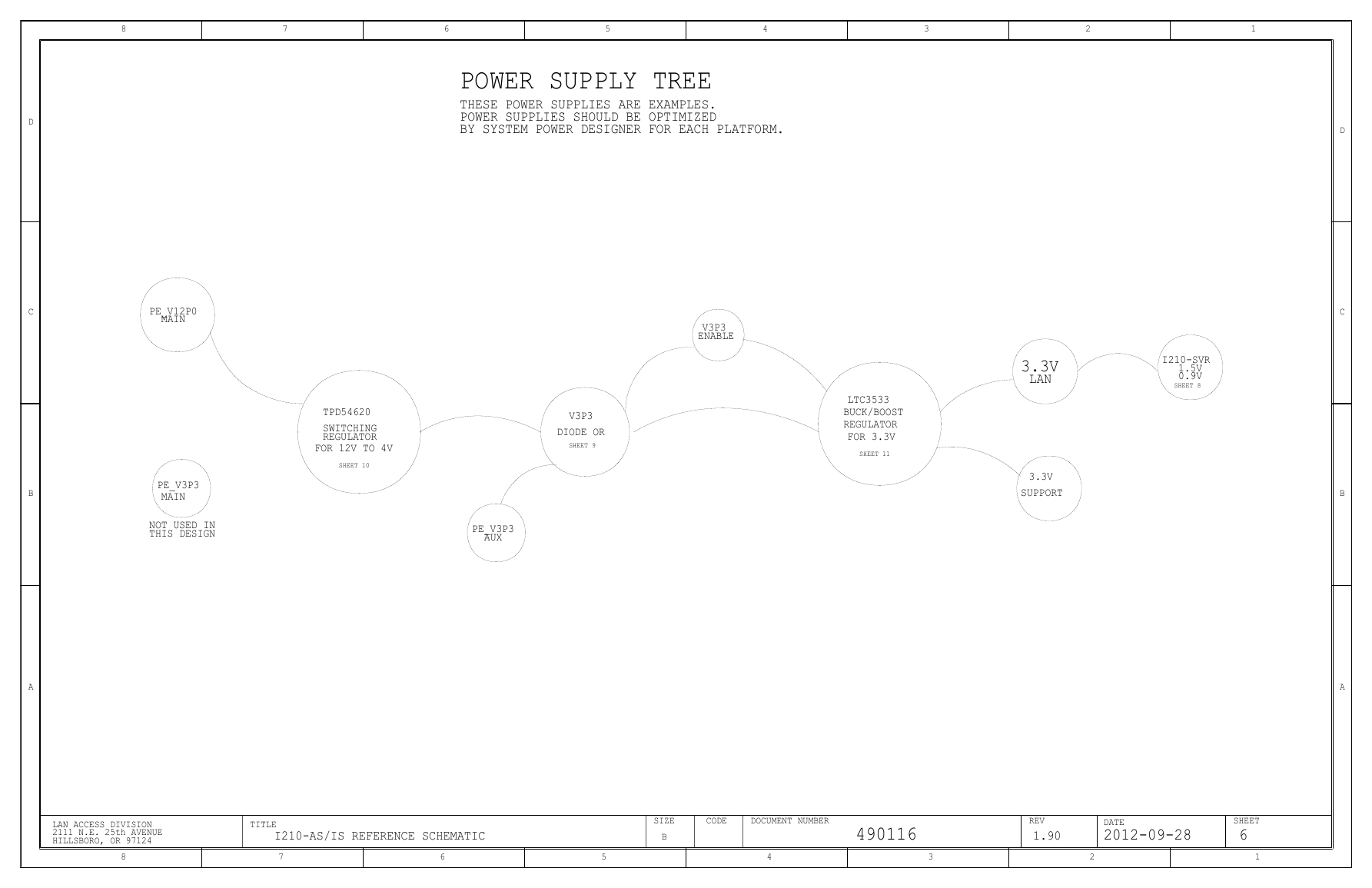

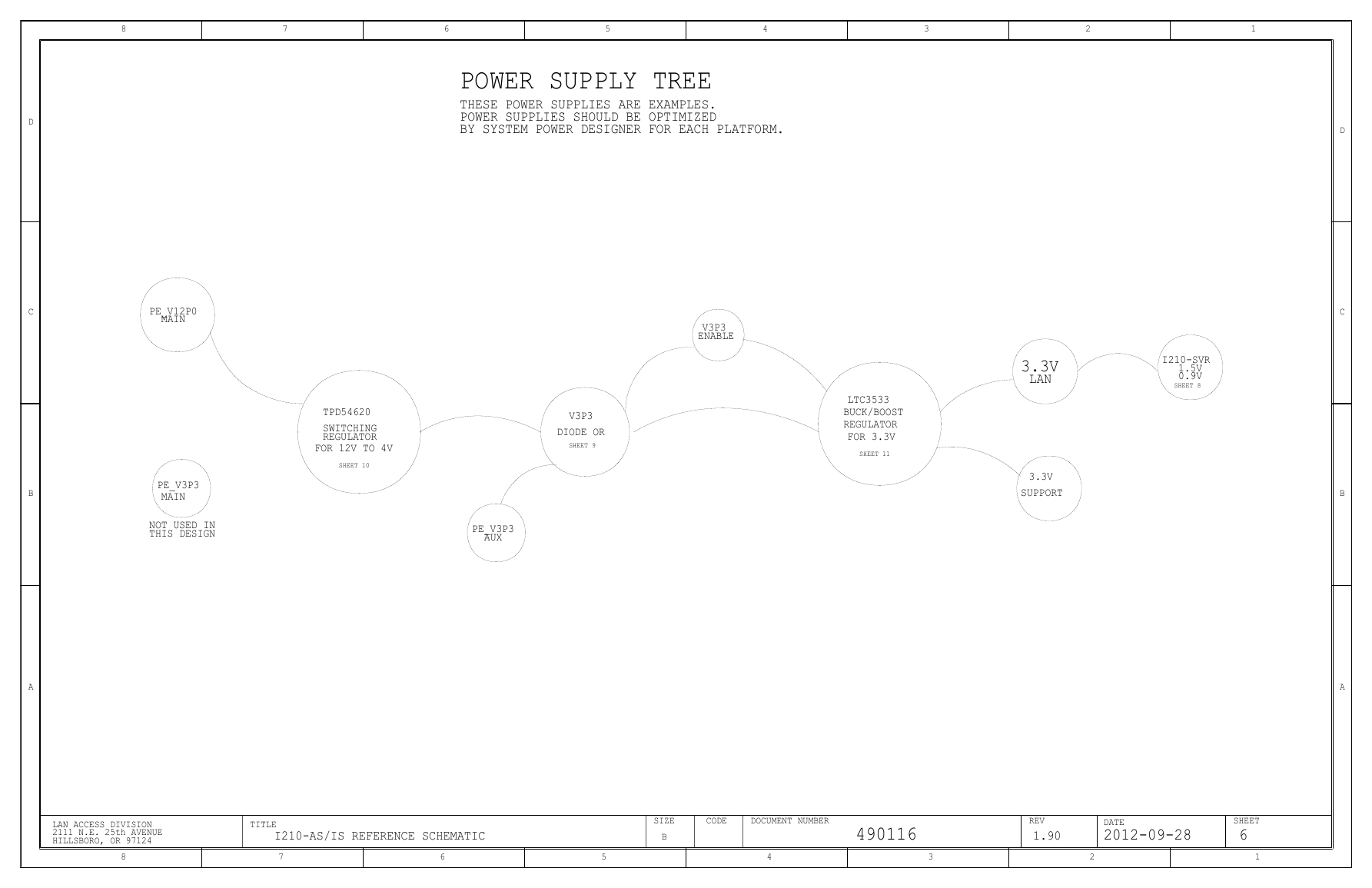

POWER SUPPLY TREE

THESE POWER SUPPLIES ARE EXAMPLES.

POWER SUPPLIES SHOULD BE OPTIMIZED

BY SYSTEM POWER DESIGNER FOR EACH PLATFORM.

PE_V12P0

MAIN

PE_V3P3

MAIN

NOT USED IN

THIS DESIGN

TPD54620

SWITCHING

REGULATOR

FOR 12V TO 4V

SHEET 10

V3P3

DIODE OR

SHEET 9

PE_V3P3

AUX

V3P3

ENABLE

LTC3533

BUCK/BOOST

REGULATOR

FOR 3.3V

SHEET 11

I210-SVR

1.5V

0.9V

SHEET 8

3.3VLAN

3.3V

SUPPORT

I210-AS/IS REFERENCE SCHEMATIC

490116

1.90

2012-09-28

6

DOCUMENT NUMBERREVDATECODEBSIZETITLESHEET 54A12ABC78BCDD1345678263LAN ACCESS DIVISION2111 N.E. 25th AVENUEHILLSBORO, OR 97124�

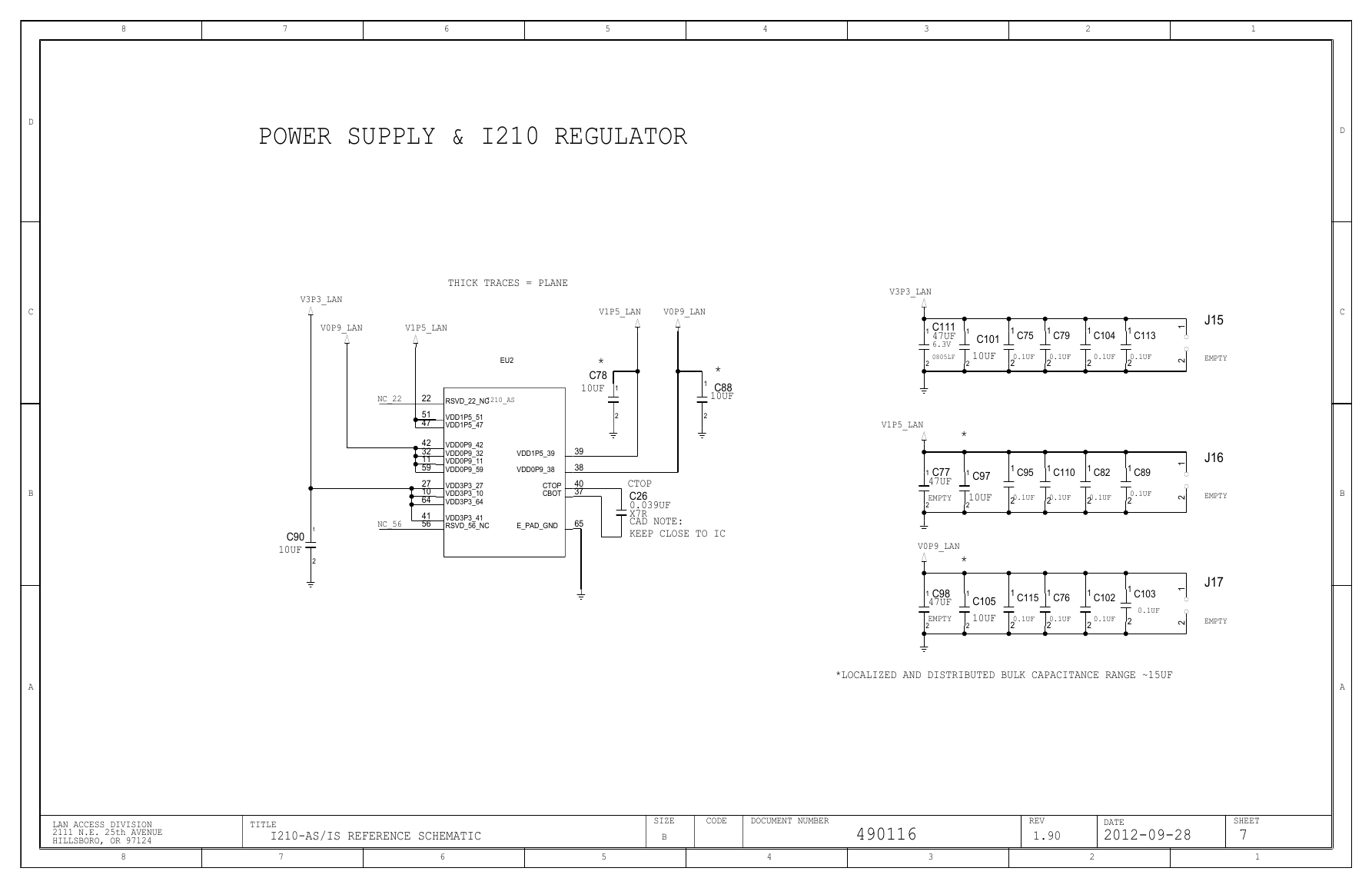

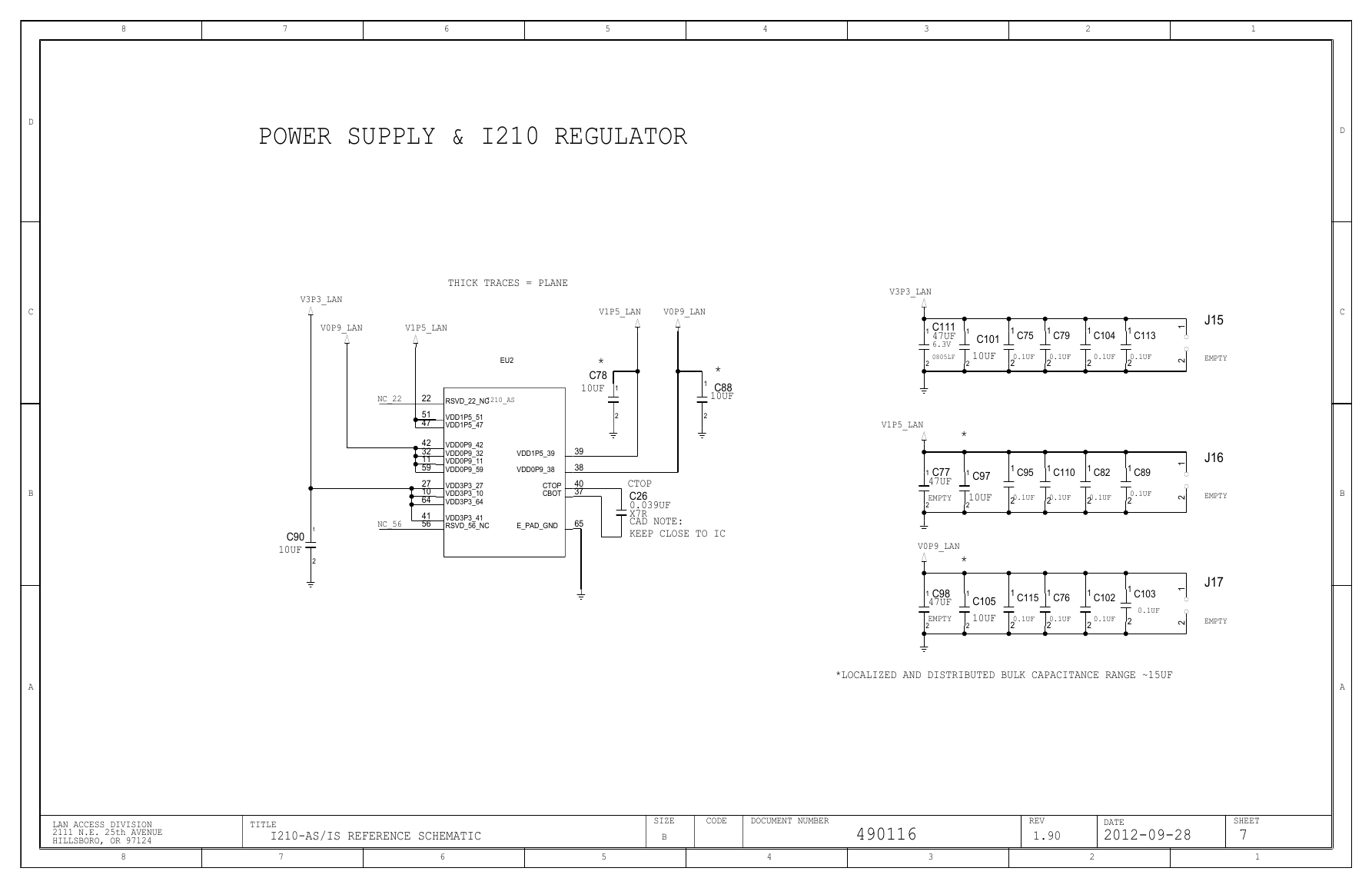

POWER SUPPLY & I210 REGULATOR

THICK TRACES = PLANE

V3P3_LAN

V0P9_LAN

V1P5_LAN

V1P5_LAN

V0P9_LAN

NC_22

NC_56

22

51

47

42

32

11

59

27

10

64

41

56

EU2

*

C78

10UF

1

2

39

38

40

37

65

*

1 C88

10UF

2

CTOP

C26

0.039UF

X7R

CAD NOTE:

KEEP CLOSE TO IC

C90

10UF

1

2

V3P3_LAN

1 C111

6.3V47UF

0805LF

2

1

2

C101

10UF

1 C75

0.1UF

2

1 C79

0.1UF

2

1 C104

1 C113

1 J15

0.1UF

2

0.1UF

2

2

EMPTY

V1P5_LAN

*

1 C77

47UF

EMPTY

2

1 C97

10UF

2

1 C95

1 C110

1 C82

0.1UF

2

0.1UF

2

0.1UF

2

1 C89

0.1UF

2

V0P9_LAN

*

1 C98

47UF

EMPTY

2

1

2

C105

10UF

1 C115

1 C76

0.1UF

2

0.1UF

2

1 C102

0.1UF

2

1 C103

0.1UF

2

1 J16

2

EMPTY

1 J17

2

EMPTY

*LOCALIZED AND DISTRIBUTED BULK CAPACITANCE RANGE ~15UF

I210-AS/IS REFERENCE SCHEMATIC

490116

1.90

2012-09-28

7

DOCUMENT NUMBERREVDATECODEBSIZETITLESHEET 54A12ABC78BCDD1345678263LAN ACCESS DIVISION2111 N.E. 25th AVENUEHILLSBORO, OR 97124212121I210_ASE_PAD_GNDCBOTCTOPVDD0P9_38VDD1P5_39VDD1P5_51VDD1P5_47RSVD_22_NCRSVD_56_NCVDD3P3_41VDD3P3_64VDD3P3_10VDD0P9_32VDD0P9_59VDD0P9_11VDD3P3_27VDD0P9_42�

POWER MUX (AUX / MAIN SWITCH)

INPUTS TO V3P3 DIODE OR

EXTERNAL SATA POWER

J10

V3P3_NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

V5P0_CONN_UNFUSED

V12P0_NC

5V_USB

1 J25

2

EMPTY

F1

IC

1

2

TPS54620_OUTPUT

~4.3V TYP

CR2

1 C3

10UF

2

V3P3_PE_AUX

CR4

2

CR3

2

MBRS540LT3

1

1

MBRS540LT3

MBRS540LT3

V3P3_OR

V3P3_OR

1 J12

2

EMPTY

1 C32

100UF

20%

1812LF

2

C80

180UF

20%

6.3V

EMPTY

7343LF

C99

180UF

20%

6.3V

EMPTY

7343LF

1 J11

EMPTY

2

1 C13

10UF

2

1 C14

10UF

2

1 R32

100K

2

1 R30

100K

EMPTY

2

1 R25

100K

EMPTY

2

1 R28

100K

2

2

3

4

7

9

13

1C10

0.1UF

2

U4

IDEAL DIODE

C62

0.1UF

2

1

1 R23

8.2K

2

1

10

12

11

8

5

6

4

U3

NTGS4141N

3

6521

I210-AS/IS REFERENCE SCHEMATIC

490116

1.90

2012-09-28

8

DOCUMENT NUMBERREVDATECODEBSIZETITLESHEET 54A12ABC78BCDD1345678263LAN ACCESS DIVISION2111 N.E. 25th AVENUEHILLSBORO, OR 97124212121CONN15_E33878_00112V_1512V_1412V_13GND_12GND_11GND_10VCC_9VCC_8VCC_7GND_6GND_5GND_4VCC3_3VCC3_2VCC3_1GS1D2D3D4D1GLTC4352FAULTSTATUSOUTGATESOURCECPOVINEPADGNDREV0VUVVCC�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc