Cover

Notice

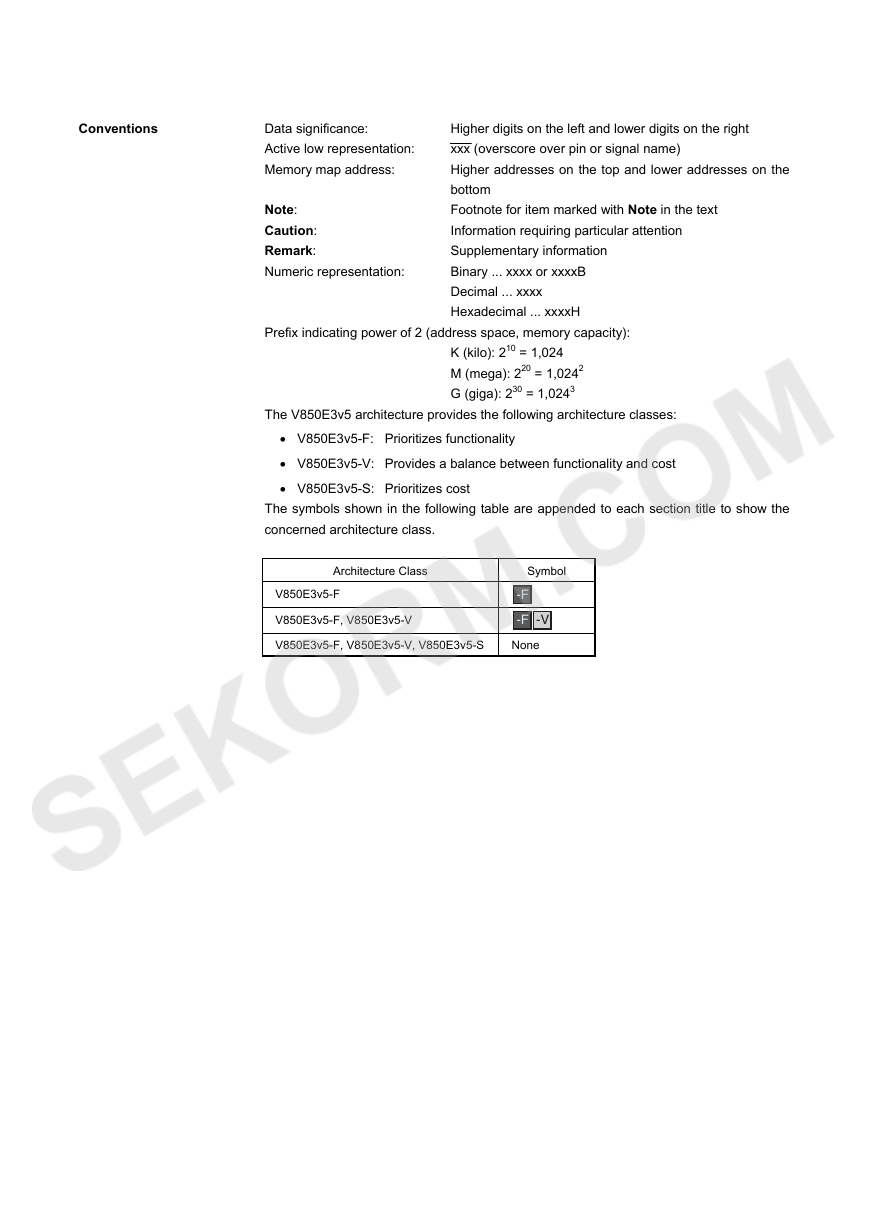

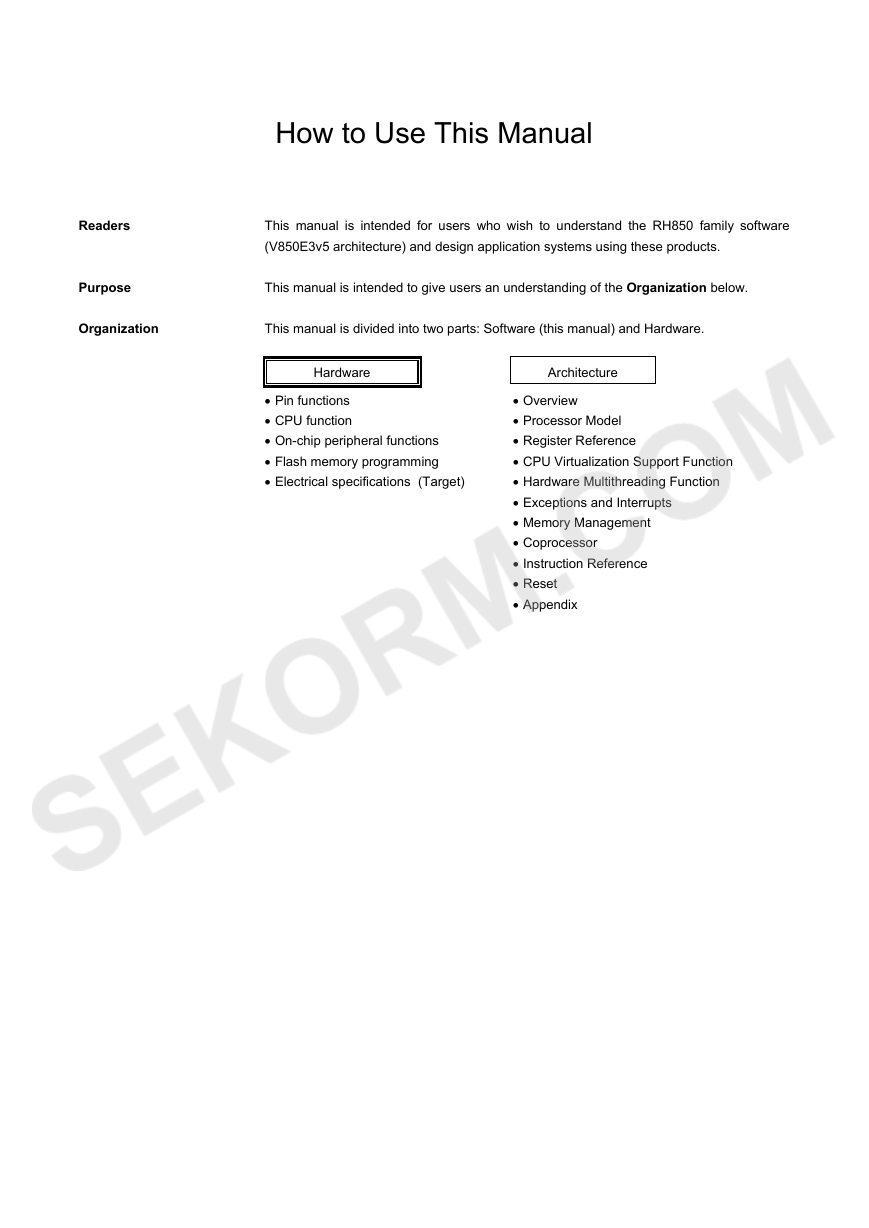

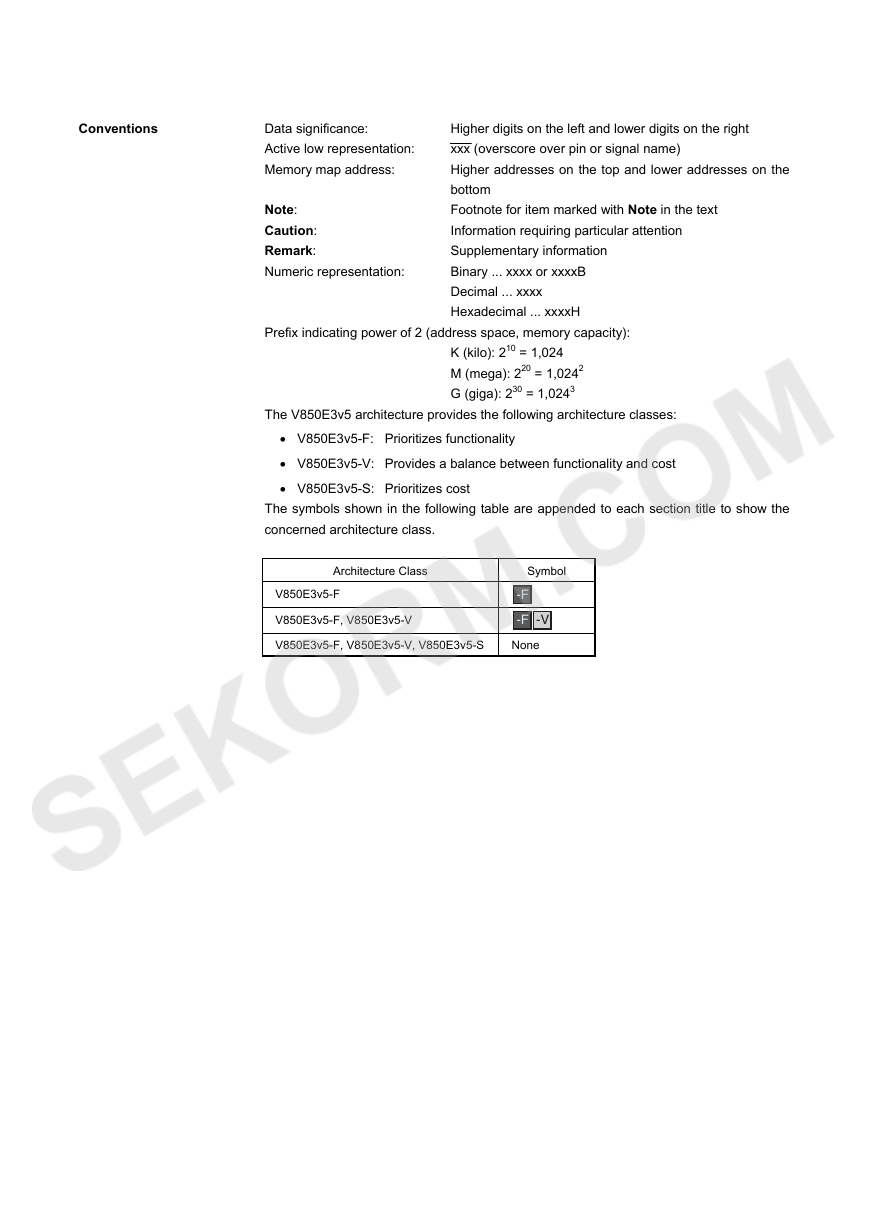

How to Use This Manual

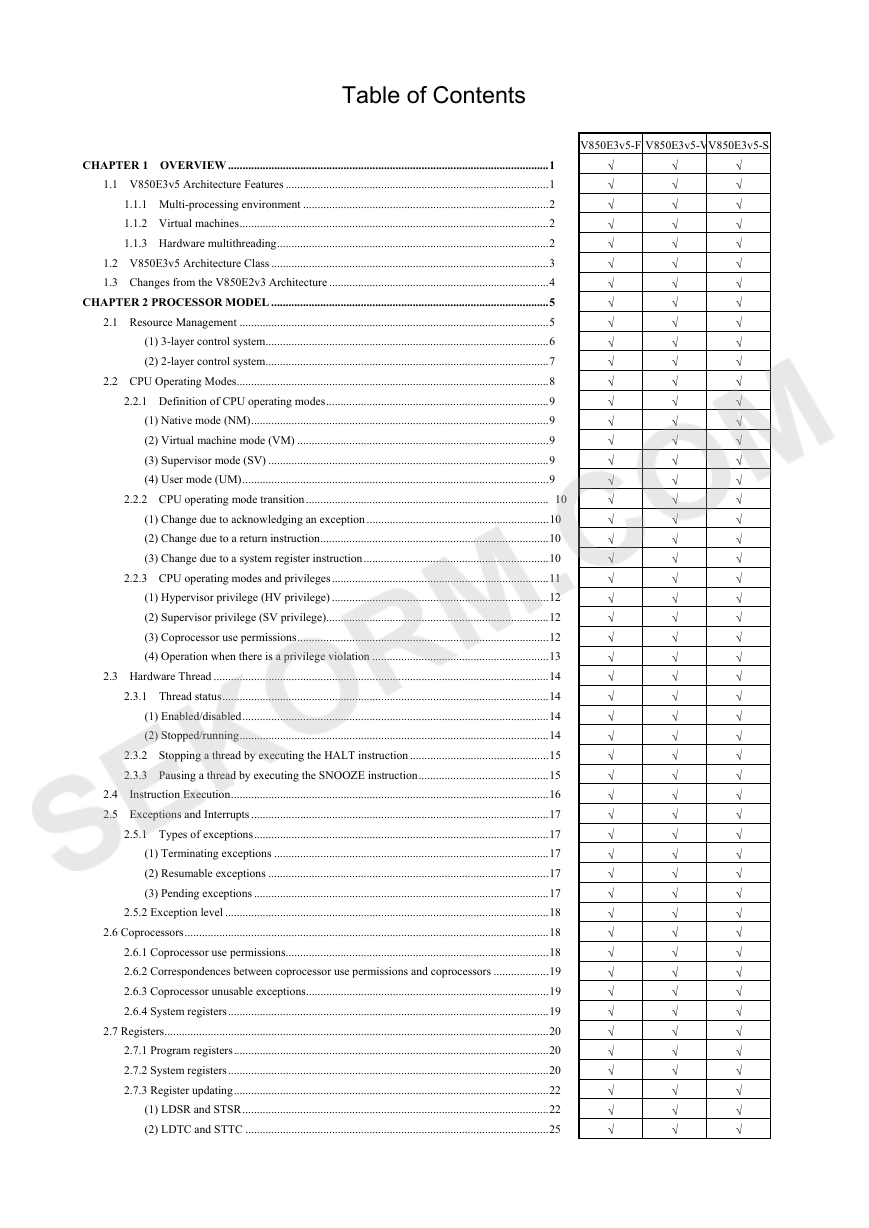

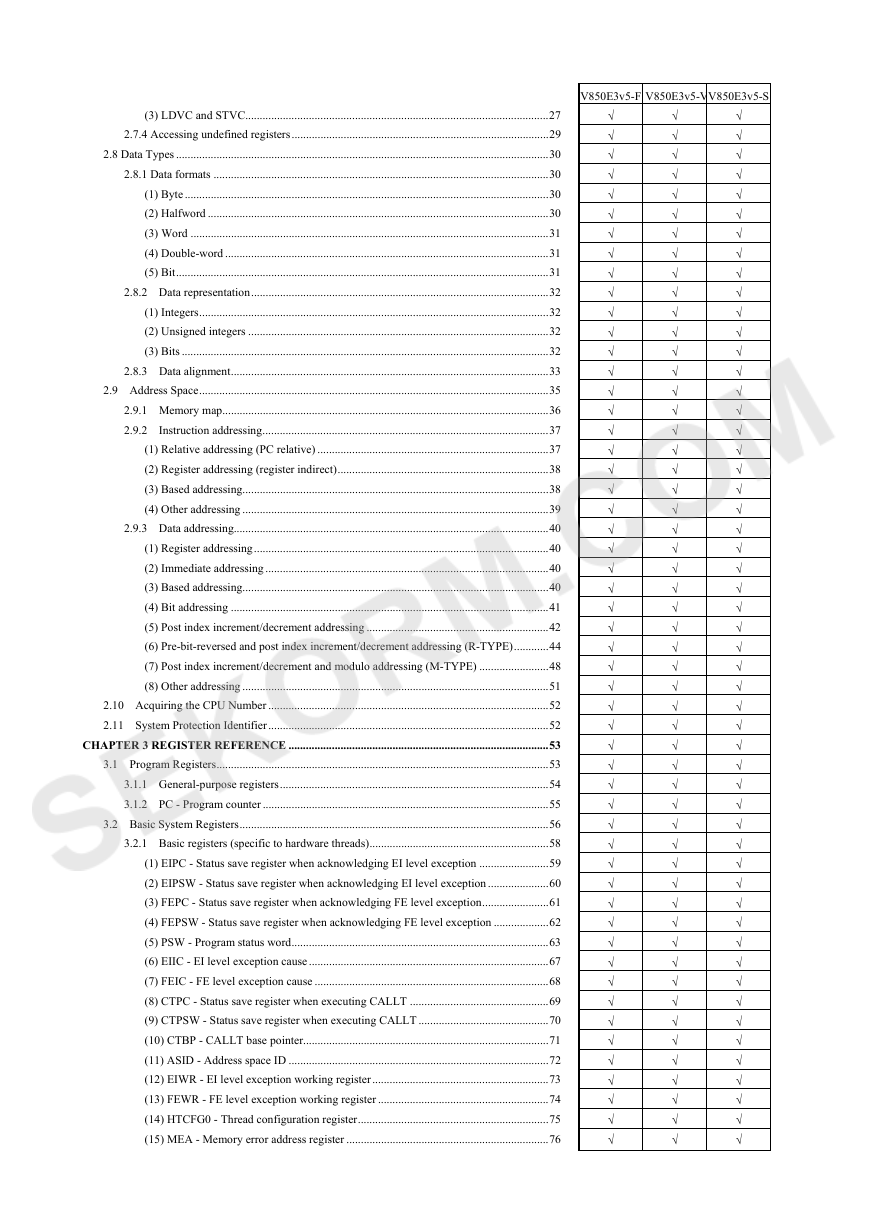

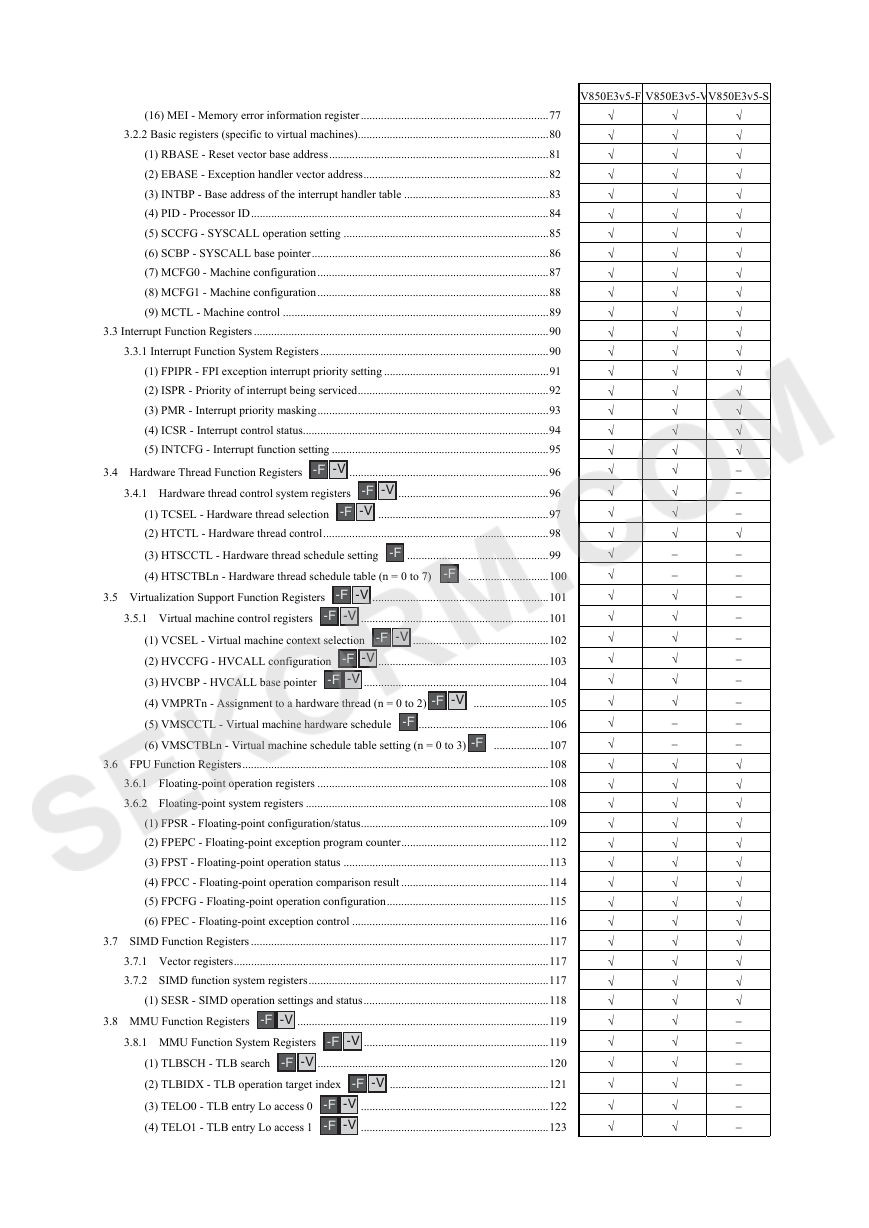

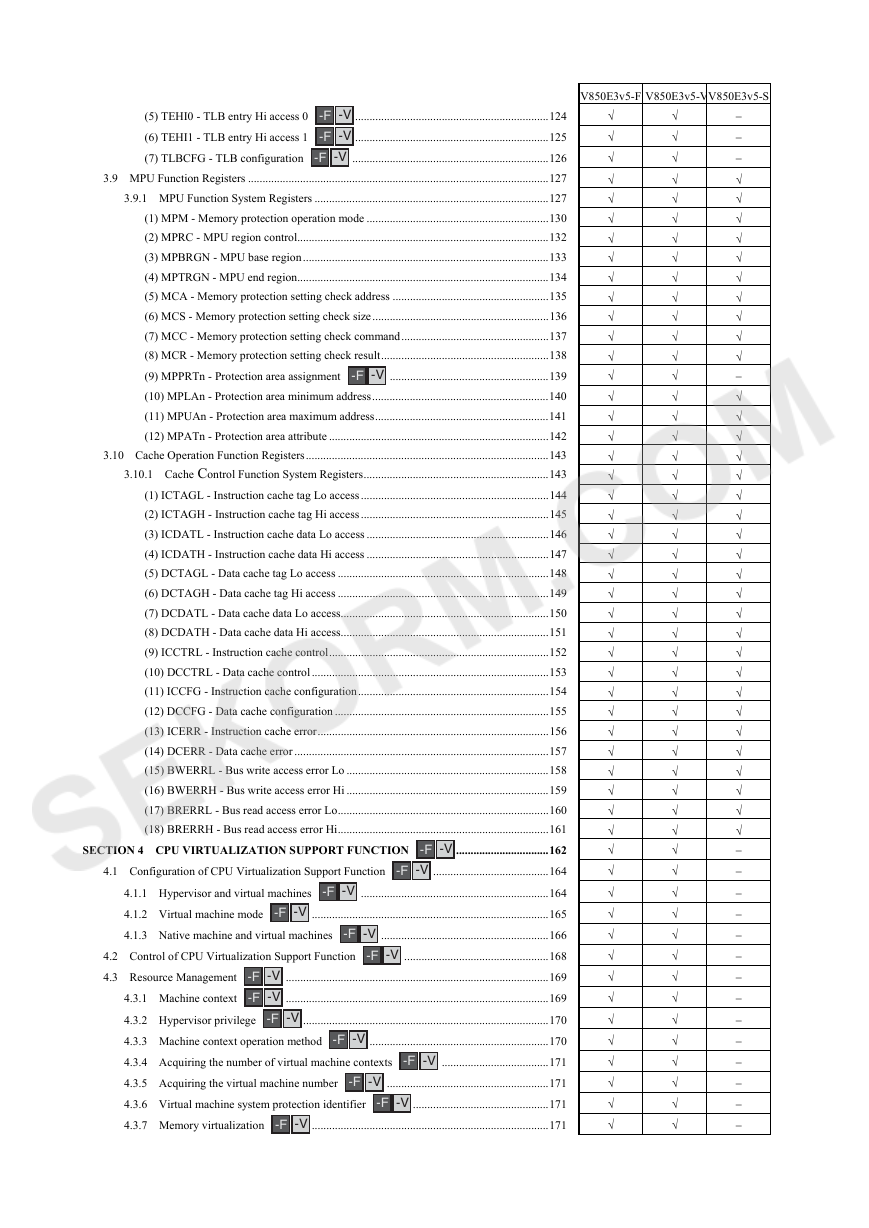

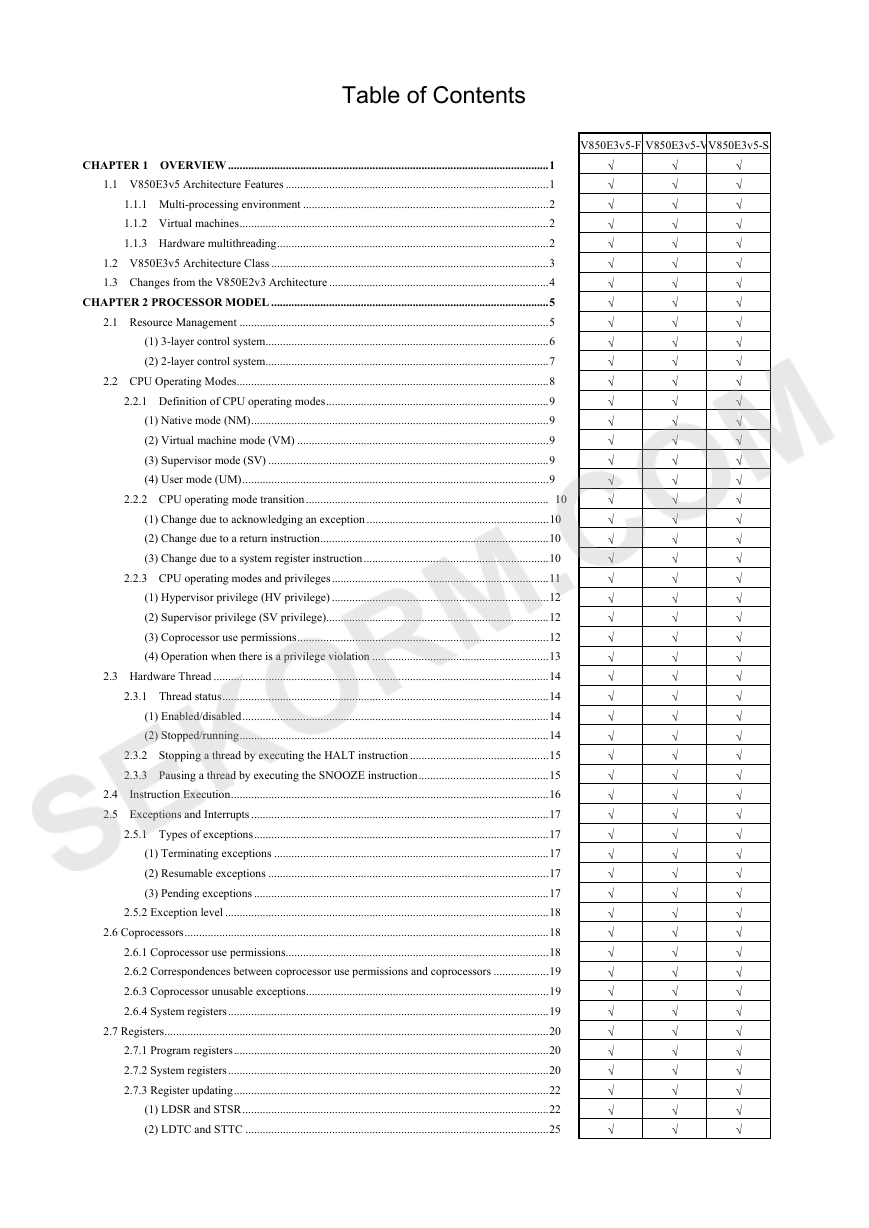

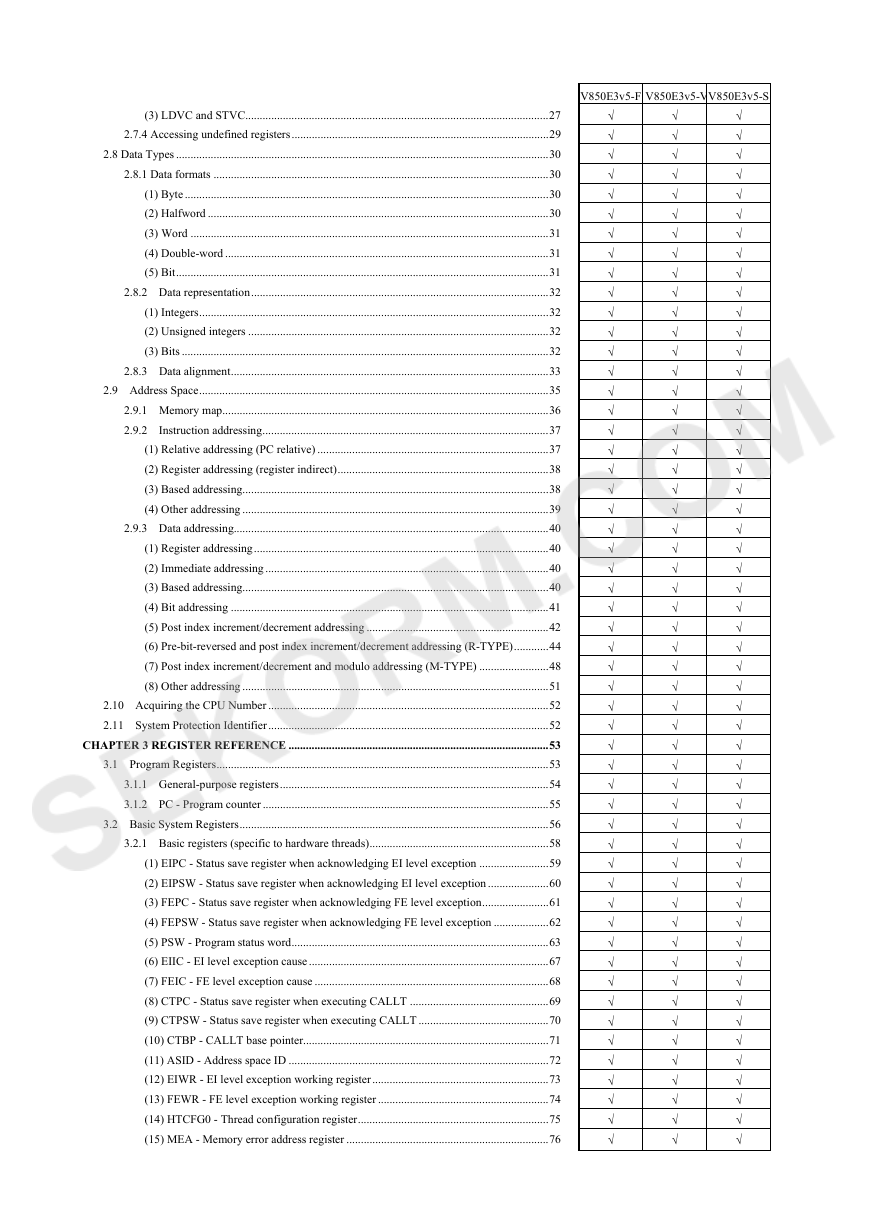

Table of Contents

CHAPTER 1 OVERVIEW

1.1 V850E3v5 Architecture Features

1.1.1 Multi-processing environment

1.1.2 Virtual machines

1.1.3 Hardware multithreading

1.2 V850E3v5 Architecture Class

(1) V850E3v5-F: Prioritizes functionality

(2) V850E3v5-V: Provides a balance between functionality and cost

(3) V850E3v5-S: Prioritizes cost

1.3 Changes from the V850E2v3 Architecture

CHAPTER 2 PROCESSOR MODEL

2.1 Resource Management

2.2 CPU Operating Modes

2.2.1 Definition of CPU operating modes

2.2.2 CPU operating mode transition

2.2.3 CPU operating modes and privileges

2.3 Hardware Thread

2.3.1 Thread status

2.3.2 Stopping a thread by executing the HALT instruction

2.3.3 Pausing a thread by executing the SNOOZE instruction

2.4 Instruction Execution

2.5 Exceptions and Interrupts

2.5.1 Types of exceptions

2.5.2 Exception level

2.6 Coprocessors

2.6.1 Coprocessor use permissions

2.6.2 Correspondences between coprocessor use permissions and coprocessors

2.6.3 Coprocessor unusable exceptions

2.6.4 System registers

2.7 Registers

2.7.1 Program registers

2.7.2 System registers

2.7.3 Register updating

2.7.4 Accessing undefined registers

2.8 Data Types

2.8.1 Data formats

2.8.2 Data representation

2.8.3 Data alignment

2.9 Address Space

2.9.1 Memory map

2.9.2 Instruction addressing

2.9.3 Data addressing

2.10 Acquiring the CPU Number

2.11 System Protection Identifier

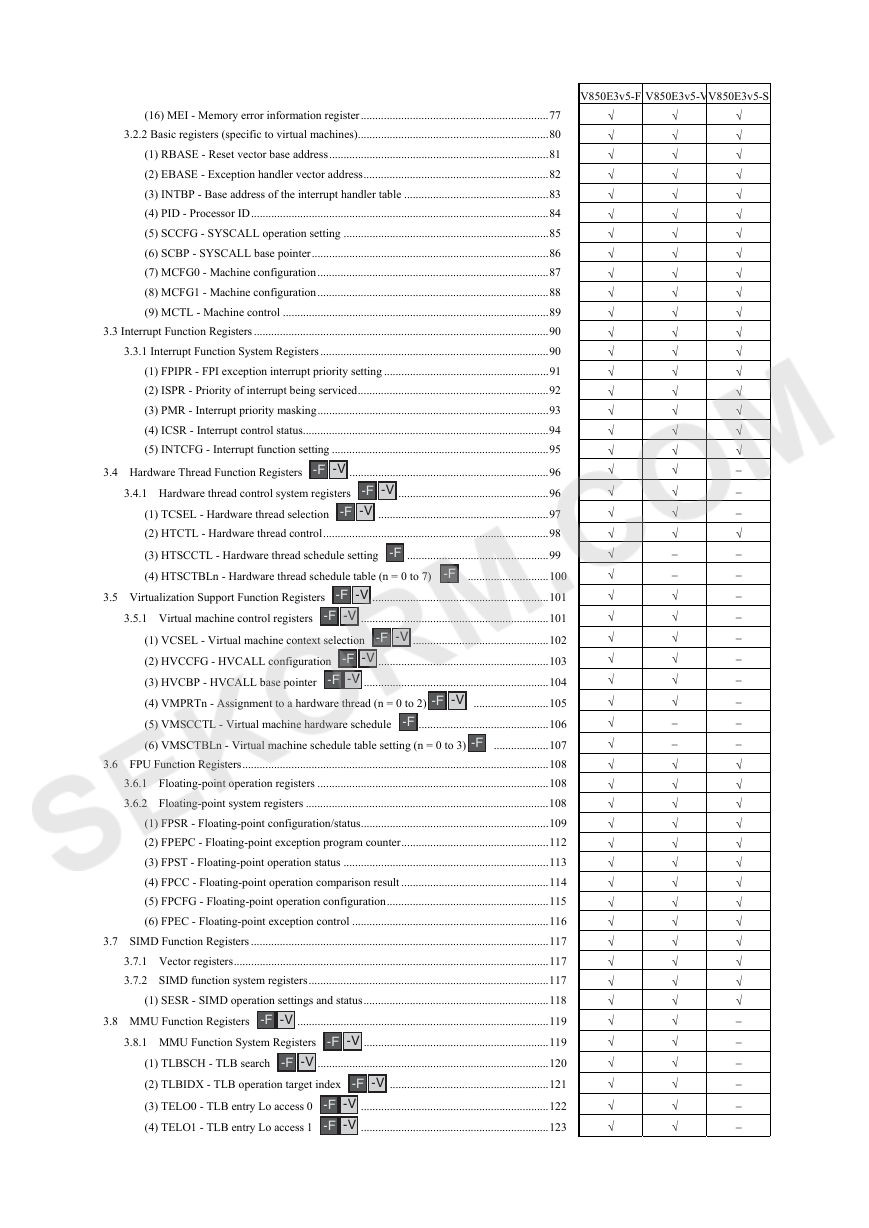

CHAPTER 3 REGISTER REFERENCE

3.1 Program Registers

3.1.1 General-purpose registers

3.1.2 PC - Program counter

3.2 Basic System Registers

3.2.1 Basic registers (specific to hardware threads)

(1) EIPC - Status save register when acknowledging EI level exception

(2) EIPSW - Status save register when acknowledging EI level exception

(3) FEPC - Status save register when acknowledging FE level exception

(4) FEPSW - Status save register when acknowledging FE level exception

(5) PSW - Program status word

(6) EIIC - EI level exception cause

(7) FEIC - FE level exception cause

(8) CTPC - Status save register when executing CALLT

(9) CTPSW - Status save register when executing CALLT

(10) CTBP - CALLT base pointer

(11) ASID - Address space ID

(12) EIWR - EI level exception working register

(13) FEWR - FE level exception working register

(14) HTCFG0 - Thread configuration register

(15) MEA - Memory error address register

(16) MEI - Memory error information register

3.2.2 Basic registers (specific to virtual machines)

(1) RBASE - Reset vector base address

(2) EBASE - Exception handler vector address

(3) INTBP - Base address of the interrupt handler table

(4) PID - Processor ID

(5) SCCFG - SYSCALL operation setting

(6) SCBP - SYSCALL base pointer

(7) MCFG0 - Machine configuration

(8) MCFG1 - Machine configuration

(9) MCTL - Machine control

3.3 Interrupt Function Registers

3.3.1 Interrupt Function System Registers

(1) FPIPR - FPI exception interrupt priority setting

(2) ISPR - Priority of interrupt being serviced

(3) PMR - Interrupt priority masking

(4) ICSR - Interrupt control status

(5) INTCFG - Interrupt function setting

3.4 Hardware Thread Function Registers

3.4.1 Hardware thread control system registers

(1) TCSEL - Hardware thread selection

(2) HTCTL - Hardware thread control

(3) HTSCCTL - Hardware thread schedule setting

(4) HTSCTBLn - Hardware thread schedule table (n = 0 to 7)

3.5 Virtualization Support Function Registers

3.5.1 Virtual machine control registers

(1) VCSEL - Virtual machine context selection

(2) HVCCFG - HVCALL configuration

(3) HVCBP - HVCALL base pointer

(4) VMPRTn - Assignment to a hardware thread (n = 0 to 2)

(5) VMSCCTL - Virtual machine hardware schedule

(6) VMSCTBLn - Virtual machine schedule table setting (n = 0 to 3)

3.6 FPU Function Registers

3.6.1 Floating-point operation registers

3.6.2 Floating-point system registers

(1) FPSR - Floating-point configuration/status

(2) FPEPC - Floating-point exception program counter

(3) FPST - Floating-point operation status

(4) FPCC - Floating-point operation comparison result

(5) FPCFG - Floating-point operation configuration

(6) FPEC - Floating-point exception control

3.7 SIMD Function Registers

3.7.1 Vector registers

3.7.2 SIMD function system registers

(1) SESR - SIMD operation settings and status

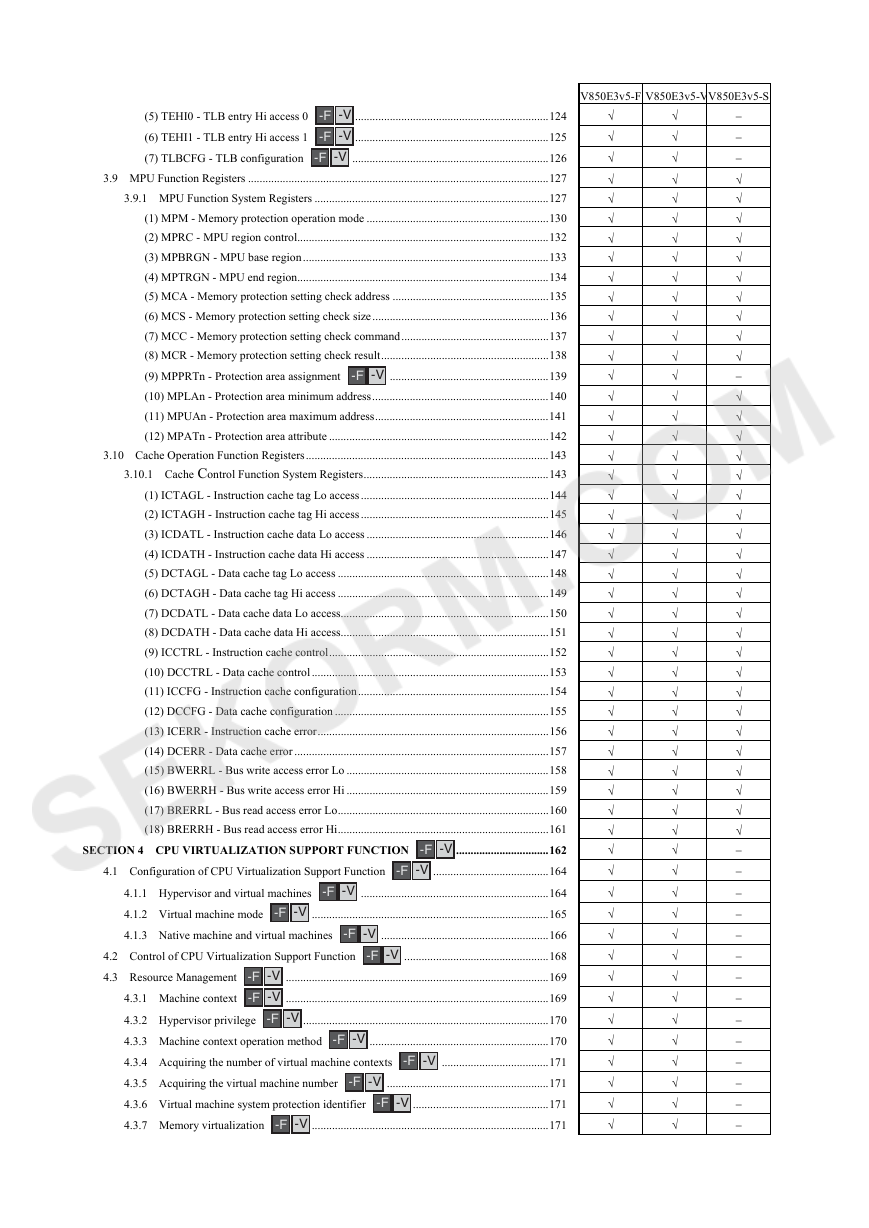

3.8 MMU Function Registers

3.8.1 MMU Function System Registers

(1) TLBSCH - TLB search

(2) TLBIDX - TLB operation target index

(3) TELO0 - TLB entry Lo access 0

(4) TELO1 - TLB entry Lo access 1

(5) TEHI0 - TLB entry Hi access 0

(6) TEHI1 - TLB entry Hi access 1

(7) TLBCFG - TLB configuration

3.9 MPU Function Registers

3.9.1 MPU Function System Registers

(1) MPM - Memory protection operation mode

(2) MPRC - MPU region control

(3) MPBRGN - MPU base region

(4) MPTRGN - MPU end region

(5) MCA - Memory protection setting check address

(6) MCS - Memory protection setting check size

(7) MCC - Memory protection setting check command

(8) MCR - Memory protection setting check result

(9) MPPRTn - Protection area assignment

(10) MPLAn - Protection area minimum address

(11) MPUAn - Protection area maximum address

(12) MPATn - Protection area attribute

3.10 Cache Operation Function Registers

3.10.1 Cache Control Function System Registers

(1) ICTAGL - Instruction cache tag Lo access

(2) ICTAGH - Instruction cache tag Hi access

(3) ICDATL - Instruction cache data Lo access

(4) ICDATH - Instruction cache data Hi access

(5) DCTAGL - Data cache tag Lo access

(6) DCTAGH - Data cache tag Hi access

(7) DCDATL - Data cache data Lo access

(8) DCDATH - Data cache data Hi access

(9) ICCTRL - Instruction cache control

(10) DCCTRL - Data cache control

(11) ICCFG - Instruction cache configuration

(12) DCCFG - Data cache configuration

(13) ICERR - Instruction cache error

(14) DCERR - Data cache error

(15) BWERRL - Bus write access error Lo

(16) BWERRH - Bus write access error Hi

(17) BRERRL - Bus read access error Lo

(18) BRERRH - Bus read access error Hi

SECTION 4 CPU VIRTUALIZATION SUPPORT FUNCTION

(1) CPU virtualization

(2) Memory virtualization

(3) Linkage to hardware multithreading

(4) Virtual machine schedule function

4.1 Configuration of CPU Virtualization Support Function

4.1.1 Hypervisor and virtual machines

4.1.2 Virtual machine mode

4.1.3 Native machine and virtual machines

4.2 Control of CPU Virtualization Support Function

4.3 Resource Management

4.3.1 Machine context

4.3.2 Hypervisor privilege

4.3.3 Machine context operation method

4.3.4 Acquiring the number of virtual machine contexts

4.3.5 Acquiring the virtual machine number

4.3.6 Virtual machine system protection identifier

4.3.7 Memory virtualization

(1) MMU supporting virtualization

(2) Memory resource address translation

4.4 Operation Model

4.4.1 Coordination with hardware multithreading

4.4.2 Structuring the virtual machines

4.4.3 Changing to native mode

4.4.4 Interrupts

4.4.5 Calling the hypervisor

(1) Hypervisor trap

(2) Hypervisor call

4.4.6 Interface with the hypervisor

(1) Utilization of the HVCALL instruction

(2) Stepwise use of the HVTRAP instruction

(3) Virtual machine for which hypervisor services are prohibited

4.5 Instructions

4.5.1 HVTRAP instruction

4.5.2 HVCALL instruction

4.5.3 LDVC/STVC instruction

4.6 Cautions on Using Virtual Machines

4.6.1 Logical partitioning-related differences between hardware threads and by virtual machines

(1) Protection of thread contexts among virtual machines

(2) CPU time schedule

(3) Logical partitioning by virtual machine context

4.6.2 Standalone use with CPU virtualization support function

4.6.3 Differences from physical multi-processor system

(1) CPU time schedule

(2) Sharing of the hardware functions of the CPU core

CHAPTER 5 HARDWARE MULTITHREADING FUNCTION

(1) Thread scheduler

(2) Thread interrupt response

(3) Thread control instructions

(4) CPU virtualization and affinity

5.1 Configuration of Hardware Multithreading Function

5.1.1 Scheduler and thread contexts

5.1.2 Virtualization support function and hardware threads

(1) Resource sharing between the native thread and thread #0

(2) Logical partitioning of thread contexts

5.2 Control of Hardware Thread Function

5.3 Resource Management

5.3.1 Thread contexts

5.3.2 Thread context operation method

5.3.3 Acquiring the number of built-in hardware threads

5.3.4 Acquiring the thread number

5.3.5 Multi-thread execution status and single-thread execution status

5.4 Operation Model

5.4.1 Starting thread execution

(1) Enabling hardware threads

(2) Setting up the thread execution schedule

(3) Setting up interrupts

(4) Transition to the multi-thread execution status

5.4.2 Stopping thread execution

(1) Transition to the single-thread execution status

(2) Disabling hardware threads

(3) Setting up the multi-thread execution schedule

(4) Releasing thread interrupts

(5) Transition to the multi-thread execution status

5.4.3 Exceptions and interrupts

(1) Exceptions related to instruction execution

(2) Exceptions for which the thread cannot be identified

(3) Interrupts

5.4.4 Exception and interrupt servicing thread independence

5.4.5 Parallel programming and inter-thread communication

5.5 Instructions

(1) Thread control instructions

(2) Thread context operation instructions

5.5.1 EST/DST instruction

5.5.2 HALT instruction

5.5.3 SNOOZE instruction

5.5.4 LDTC/STTC instruction

5.6 Scheduling

5.6.1 Multi-level scheduling

(1) Native mode

(2) Virtual machine mode

5.6.2 Schedule switching opportunities

(1) Transition to the native mode

(2) Transition to the single-thread execution status

5.6.3 Virtual machine schedule method

(1) Table schedule method

(2) Other schedule methods

5.6.4 Thread schedule method

(1) Table schedule method

(2) Other schedule methods

5.6.5 Relationship between virtual machine schedule and thread schedule

5.6.6 Operation when a scheduled thread cannot be executed

5.6.7 Exception acknowledgment

CHAPTER 6 EXCEPTIONS AND INTERRUPTS

6.1 Outline of Exceptions

6.1.1 Exception cause list

6.1.2 Overview of exception causes

(1) RESET and VMRESTART

(2) FENMI, FEINT, and EIINT

(3) SYSERR

(4) FPI and FPP

(5) MIP and MDP

(6) ITLBE and DTLBE

(7) RIE

(8) PIE

(9) UCPOP

(10) MAE

(11) TRAP, FETRAP, SYSCALL, HVCALL, and HVTRAP

6.1.3 Types of exceptions

(1) Terminating exceptions

(2) Resumable exceptions

(3) Pending exceptions

6.1.4 Exception acknowledgment conditions and priority order

6.1.5 Interrupt exception priority and priority masking

(1) Interrupt priority

(2) Interrupt priority mask

(3) Differences in operation between EIINTn and FPI

6.1.6 Return and restoration

6.1.7 Context saving

(1) Saving destination

(2) Context saving

6.2 Operation When Acknowledging an Exception

6.2.1 Special operations

(1) HVTRAP instruction

(2) Operational differences due to interrupt bind settings

(3) EP bit of PSW register

(4) Coprocessor unusable exception

(5) Reserved instruction exception

(6) Reset/virtual machine restart

6.3 Return from Exception Handling

6.4 Exception Management

6.4.1 Exception synchronization instruction

6.4.2 Checking and canceling pending exception

6.5 Exception Handler Address

6.5.1 Resets, exceptions, and interrupts

(1) Direct vector method

(2) Table reference method

6.5.2 System calls and hypervisor calls

(1) System calls

(2) Hypervisor calls

6.5.3 Base register restrictions

6.5.4 Models for application

CHAPTER 7 MEMORY MANAGEMENT

7.1 Memory Management Unit (MMU)

7.1.1 Features

(1) Virtual memory function

(2) Memory protection function

(3) Virtual machine support

7.1.2 Translation Lookaside Buffer (TLB)

(1) TLB entry format

7.1.3 Memory management registers

7.1.4 TLB instructions

(1) TLBR instruction

(2) TLBW instruction

(3) TLBS instruction

(4) TLBVI instruction

(5) TLBAI instruction

7.1.5 TLB exception

(1) Identification of TLB exception causes

(2) TLB exceptions in instructions in which memory access occurs several times during execution

(3) TLB exception in a cache operation instruction

7.1.6 Translation from virtual address to physical address

7.1.7 Address space

7.1.8 Use of MMU in virtual machine mode

(1) Address space for hypervisor call

7.1.9 Real addressing mode

(1) Real addressing mode for virtual machines

(2) Transition to read addressing mode

(3) When bit width differs between virtual address and physical address

7.1.10 Support of page sizes less than 4 KB

7.1.11 Avoidance of the synonym problem

7.2 Memory Protection Unit (MPU)

7.2.1 Features

(1) Memory access control

(2) Access management for each CPU operation mode

(3) Virtual machine support

7.2.2 Register set

7.2.3 MPU operation settings

(1) Settings for native mode

(2) Settings for virtual machine mode

7.2.4 Protection area settings

(1) Determination of protection area available for use by virtual machines

(2) Protection area settings

7.2.5 Caution points for protection area setup

(1) Crossing protection area boundaries

(2) Invalid protection area settings

(3) Invalidation of protection during HVCALL execution

7.2.6 Access control

7.2.7 Violations and exceptions

(1) Execution protection violation (MIP exception)

(2) Data protection violation (MDP exception)

(3) Exception cause code and exception address

7.2.8 Memory protection setting check function

(1) Procedure

(2) Sample code

7.3 Slave Address Translation Function

7.4 Cache

7.4.1 Cache operation registers

7.4.2 Change cache use mode

(1) Change use mode of instruction cache

(2) Change use mode of data cache

7.4.3 Cache operations using CACHE instruction

(1) Specification method for target of CACHE instruction

(2) Operations performed using the CACHE instruction

7.4.4 Cache operation when the PREF instruction is executed

7.4.5 Cache index specification method

7.4.6 Execution privilege of the CACHE/PREF instruction

7.4.7 Memory protection for CACHE and PREF instructions

7.4.8 Example of cache memory operation using CACHE instruction

7.4.9 Cache parity protection function

7.5 Mutual Exclusion

7.5.1 Shared data that does not require mutual exclusion processing

7.5.2 Performing mutual exclusion by using the LDL.W and STC.W instructions

(1) Link

(2) Sample code

7.5.3 Performing mutual exclusion by using the SET1 instruction

(1) Sample code

7.5.4 Performing mutual exclusion by using the CAXI instruction

(1) Sample code

CHAPTER 8 COPROCESSOR

8.1 Floating-Point Operation

8.1.1 Configuration of CPU floating -point operation function

(1) Not implemented

(2) Implementing only single precision

(3) Implementing single precision and double precision

8.1.2 FPU version

8.1.3 Data types

(1) Floating-point format

(2) Fixed-point formats

(3) Expanded floating-point format [FPU-3.0]

8.1.4 Register set

(1) Floating-point system registers

8.1.5 Floating-point instructions

8.1.6 Floating-point operation exceptions

(1) Types of exceptions

(2) Exception handling

8.1.7 Exception details

(1) Inexact exception (I)

(2) Invalid operation exception (V)

(3) Division by zero exception (Z)

(4) Overflow exception (O)

(5) Underflow exception (U)

(6) Unimplemented operation exception (E)

8.1.8 Precise exceptions and imprecise exceptions

(1) Precise exceptions

(2) Imprecise exceptions

8.1.9 Saving and returning status

8.1.10 Flushing subnormal numbers

(1) Normalize the subnormal numbers and continue executing arithmetic processing

(2) Generate an unimplemented operation exception (E) and execute exception handling

(3) Instructions that can handle subnormal numbers

(4) Instructions that are not affected by flushing subnormal numbers

8.1.11 Selection of floating-point operation model

(1) Do not generate exceptions model

(2) Imprecise exception model

(3) Precise exception model

8.1.12 Flush to nearest [FPU-3.0]

8.2 Fixed-Point SIMD

8.2.1 Features

(1) Parallel processing performance

(2) Memory access functions

(3) Instructions suitable for various application fields

8.2.2 Implementation of SIMD operation function

8.2.3 Data types

(1) 8-bit data format

(2) 16-bit data format

(3) 32-bit data format

(4) 64-bit data format

(5) Range and precision of fixed-point data types

8.2.4 Saturation

(1) 16-bit signed saturation

(2) 32-bit signed saturation

8.2.5 Rounding

(1) Normal rounding

8.2.6 Extension of significant digits for intermediate results

8.2.7 Register set

8.2.8 SIMD instructions

CHAPTER 9 INSTRUCTION REFERENCE

9.1 Opcodes and Instruction Formats

9.1.1 CPU instructions

(1) reg-reg instruction (Format I)

(2) imm-reg instruction (Format II)

(3) Conditional branch instruction (Format III)

(4) 16-bit load/store instruction (Format IV)

(5) Jump instruction (Format V)

(6) 3-operand instruction (Format VI)

(7) 32-bit load/store instruction (Format VII)

(8) Bit manipulation instruction (Format VIII)

(9) Extended instruction format 1 (Format IX)

(10) Extended instruction format 2 (Format X)

(11) Extended instruction format 3 (Format XI)

(12) Extended instruction format 4 (Format XII)

(13) Stack manipulation instruction format (Format XIII)

(14) Load/store instruction 48-bit format (Format XIV)

9.1.2 Coprocessor instructions

(1) Coprocessor unusable exception

9.1.3 Reserved instructions

9.2 Basic Instructions

9.2.1 Overview of basic instructions

(1) Load instructions

(2) Store instructions

(3) Multiply instructions

(4) Multiply-accumulate instructions

(5) Arithmetic instructions

(6) Conditional arithmetic instructions

(7) Saturated operation instructions

(8) Logical instructions

(9) Data manipulation instructions

(10) Bit search instructions

(11) Divide instructions

(12) High-speed divide instructions

(13) Branch instructions

(14) Loop instruction

(15) Bit manipulation instructions

(16) Special instructions

9.2.2 Basic instruction set

ADD

ADDI

ADF

AND

ANDI

Bcond

BINS

BSH

BSW

CALLT

CAXI

CLL

CLR1

CMOV

CMP

CTRET

DI

DISPOSE

DIV

DIVH

DIVHU

DIVQ

DIVQU

DIVU

EI

EIRET

FERET

FETRAP

HALT

HSH

HSW

JARL

JMP

JR

LD.B

LD.BU

LD.DW

LD.H

LD.HU

LD.W

LDL.W

LDSR

LOOP

MAC

MACU

MOV

MOVEA

MOVHI

MUL

MULH

MULHI

MULU

NOP

NOT

NOT1

OR

ORI

POPSP

PREPARE

PUSHSP

RIE

ROTL

SAR

SASF

SATADD

SATSUB

SATSUBI

SATSUBR

SBF

SCH0L

SCH0R

SCH1L

SCH1R

SET1

SETF

SHL

SHR

SLD.B

SLD.BU

SLD.H

SLD.HU

SLD.W

SNOOZE

SST.B

SST.H

SST.W

ST.B

ST.DW

ST.H

ST.W

STC.W

STSR

SUB

SUBR

SWITCH

SXB

SXH

SYNCE

SYNCI

SYNCM

SYNCP

SYSCALL

TRAP

TST

TST1

XOR

XORI

ZXB

ZXH

9.3 Virtualization Support Instructions

9.3.1 Overview of virtualization support instructions

9.3.2 Virtualization support instruction set

HVCALL

HVTRAP

LDVC.SR

STVC.SR

9.4 Hardware Multithreading Instructions

9.4.1 Overview of hardware multithreading instructions

9.4.2 Hardware multithreading instruction set

DST

EST

LDTC.{GR,VR,PC}

LDTC.SR

STTC.{GR,VR,PC}

STTC.SR

9.5 Cache Instructions

9.5.1 Overview of cache instructions

9.5.2 Cache instruction set

CACHE

PREF

9.6 MMU Control Instructions

9.6.1 Overview of MMU control instructions

9.6.2 MMU control instruction set

TLBAI

TLBR

TLBS

TLBVI

TLBW

9.7 Debug Instructions

9.7.1 Overview of debug instructions

9.7.2 Debug instruction set

DBCP

DBHVTRAP

DBPUSH

DBRET

DBTAG

DBTRAP

RMTRAP

9.8 Floating-Point Instructions

9.8.1 Instruction formats

(1) Format F:I

9.8.2 Overview of floating-point instructions

(1) Basic operation instructions

(2) Extended basic operation instructions

(3) Conversion instructions

(4) Comparison instructions

(5) Conditional move instructions

(6) Condition bit transfer instruction

9.8.3 Conditions for comparison instructions

9.8.4 Floating-point instruction set

ABSF.D

ABSF.S

ADDF.D

ADDF.S

CEILF.DL

CEILF.DUL

CEILF.DUW

CEILF.DW

CEILF.SL

CEILF.SUL

CEILF.SUW

CEILF.SW

CMOVF.D

CMOVF.S

CMPF.D

CMPF.S

CVTF.DL

CVTF.DS

CVTF.DUL

CVTF.DUW

CVTF.DW

CVTF.HS [FPU-3.0]

CVTF.LD

CVTF.LS

CVTF.SD

CVTF.SL

CVTF.SH [FPU-3.0]

CVTF.SUL

CVTF.SUW

CVTF.SW

CVTF.ULD

CVTF.ULS

CVTF.UWD

CVTF.UWS

CVTF.WD

CVTF.WS

DIVF.D

DIVF.S

FLOORF.DL

FLOORF.DUL

FLOORF.DUW

FLOORF.DW

FLOORF.SL

FLOORF.SUL

FLOORF.SUW

FLOORF.SW

FMAF.S [FPU-3.0]

FMSF.S [FPU-3.0]

FNMAF.S [FPU-3.0]

FNMSF.S [FPU-3.0]

MAXF.D

MAXF.S

MINF.D

MINF.S

MULF.D

MULF.S

NEGF.D

NEGF.S

RECIPF.D

RECIPF.S

ROUNDF.DL

ROUNDF.DUL

ROUNDF.DUW

ROUNDF.DW

ROUNDF.SL

ROUNDF.SUL

ROUNDF.SUW

ROUNDF.SW

RSQRTF.D

RSQRTF.S

SQRTF.D

SQRTF.S

SUBF.D

SUBF.S

TRFSR

TRNCF.DL

TRNCF.DUL

TRNCF.DUW

TRNCF.DW

TRNCF.SL

TRNCF.SUL

TRNCF.SUW

TRNCF.SW

9.9 SIMD Instructions

9.9.1 Instruction formats

(1) SIMD instruction format (Format C: 3OP)

9.9.2 Overview of SIMD instructions (vector manipulation instructions)

(1) Vector logical operation instructions

(2) Vector shift instructions

(3) Vector data movement instructions

(4) Vector data copying instructions

(5) Instructions for loading data to expansion registers

(6) Instructions for storing data from expansion registers

(7) Other instructions

9.9.3 Overview of SIMD instructions (fixed-point vector operation instructions)

(1) Fixed-point vector addition and subtraction instructions

(2) Fixed-point vector multiplication instructions

(3) Fixed-point vector complex multiplication instructions

(4) Fixed-point vector comparison instructions

(5) Fixed-point vector absolute value and sign reversing instructions

(6) Fixed-point vector maximum and minimum finding instructions

(7) Fixed-point vector multiply-add instructions

(8) Fixed-point vector multiplication and summation instructions

(9) Fixed-point vector multiplication, summation, and addition instructions

(10) Fixed-point data format conversion instructions

(11) Other instructions

9.9.4 SIMD instruction set

CNVQ15Q30

CNVQ30Q15

CNVQ31Q62

CNVQ62Q31

DUP.H

DUP.W

EXPQ31

MODADD

MOV.DW

MOV.H

MOV.W

PKI16I32

PKI16UI8

PKI32I16

PKI64I32

PKQ15Q31

PKQ30Q31

PKQ31Q15

PKUI8I16

VABS.H

VABS.W

VADD.DW

VADD.H

VADD.W

VADDS.H

VADDS.W

VADDSAT.H

VADDSAT.W

VAND

VBIQ.H

VBSWAP.DW

VBSWAP.H

VBSWAP.W

VCALC.H

VCALC.W

VCMOV

VCMPEQ.H

VCMPEQ.W

VCMPLE.H

VCMPLE.W

VCMPLT.H

VCMPLT.W

VCMPNE.H

VCMPNE.W

VCONCAT.B

VITLV.H

VITLV.W

VITLVHW.H

VITLVWH.H

VLD.B

VLD.DW

VLD.H

VLD.W

VMADRN.H

VMADRN.W

VMADSAT.H

VMADSAT.W

VMAXGE.H

VMAXGE.W

VMAXGT.H

VMAXGT.W

VMINLE.H

VMINLE.W

VMINLT.H

VMINLT.W

VMSUM.H

VMSUM.W

VMSUMAD.H

VMSUMAD.W

VMSUMADIM.H

VMSUMADIM.W

VMSUMADRE.H

VMSUMADRE.W

VMSUMADRN.H

VMUL.H

VMUL.W

VMULCX.H

VMULCX.W

VMULT.H

VMULT.W

VNEG.H

VNEG.W

VNOT

VOR

VSAR.DW

VSAR.H

VSAR.W

VSHL.DW

VSHL.H

VSHL.W

VSHR.DW

VSHR.H

VSHR.W

VSHUFL.B

VST.B

VST.DW

VST.H

VST.W

VSUB.DW

VSUB.H

VSUB.W

VSUBS.H

VSUBS.W

VSUBSAT.H

VSUBSAT.W

VXOR

SECTION 10 RESET

10.1 Status of Registers After Reset

10.2 Restarting a Virtual Machine

APPENDIX A SYSTEM REGISTERS

APPENDIX B MODES OF OPERATION

APPENDIX C V850E3v5-S SPECIFICATIONS

C.1 Functions Not Supported

(1) Hardware multithreading function

(2) CPU virtualization support function

(3) Memory management unit (MMU)

(4) Slave address translation

(5) Registers

(6) Instructions

C.2 System Register Configuration

APPENDIX D V850E3v5-V SPECIFICATIONS

D.1 Functions Not Supported

(1) Hardware multithreading function

(2) CPU virtualization support function

(3) Registers

(4) Instructions

D.2 System Register Configuration

APPENDIX E AVAILABILITY OF SYSTEM REGISTERS

APPENDIX F DIFFERENCES BETWEEN V850E3v5 AND OTHER ARCHITECTURES

APPENDIX G REGISTER INDEX

APPENDIX H INSTRUCTION INDEX

colophon

SALES OFFICES

backcover

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc