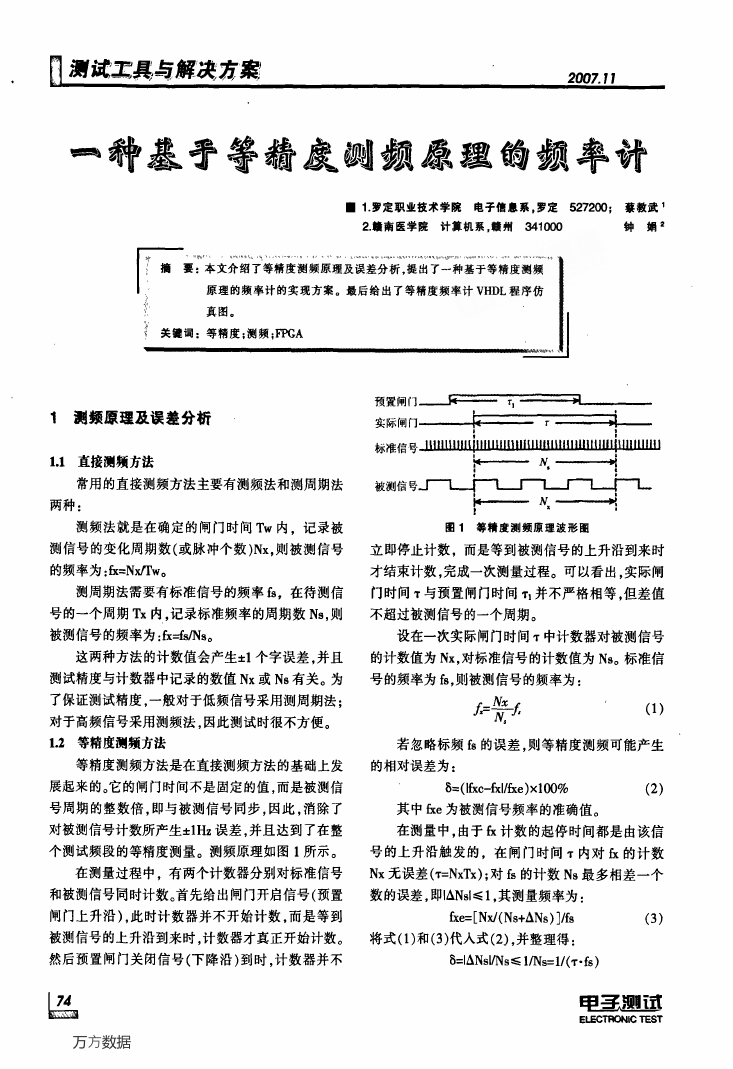

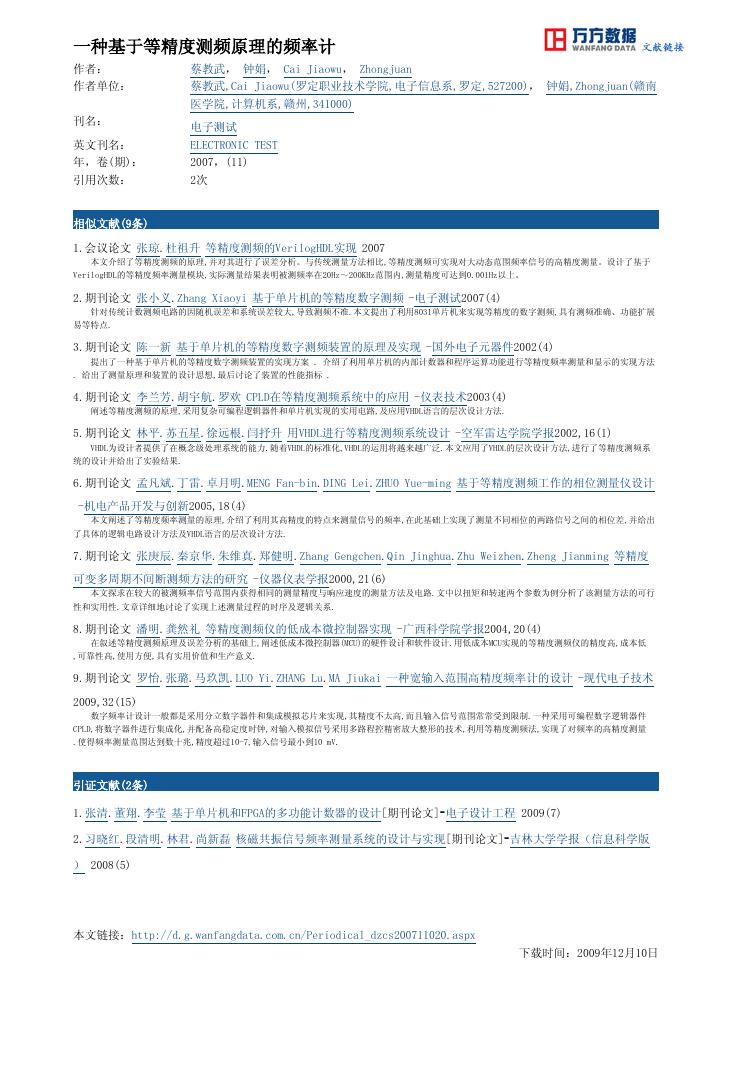

一神基矛等精虞测额原理鳓频枣谛●1.罗定职业技术学院电子信息系。罗定5272∞;蔡教武12.赣南医学院计算机系。赣州341000钟娟27;Ⅳ:1‰。’^。’÷{?一~一。11|1‘6+“。4。j?一…”……p、+M…%j’iij“二’jP4j。"4’~∥’#…………¨“。”j”。?……"。~q:本文介绍了等精度测频原理及误差分析,提出了一种基于等待度测频原理的频率计的实现方案。最后给出了等精度频率计VHDL程序仿1测频原理及误差分析1.1直接测频方法常用的直接测频方法主要有测频法和测周期法两种:测频法就是在确定的闸门时间Tw内。记录被测信号的变化周期数(或脉冲个数)Nx,则被测信号的频率为:&=N册w。测周期法需要有标准信号的频率fs,在待测信号的一个周期Tx内,记录标准频率的周期数Ns,则被测信号的频率为:fk≤洲s。这两种方法的计数值会产生±1个字误差,并且测试精度与计数器中记录的数值Nx或Ns有关。为了保证测试精度,一般对于低频信号采用测周期法;对于高频信号采用测频法,因此测试时很不方便。1.2等精度测频方法等精度测频方法是在直接测频方法的基础上发展起来的。它的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,因此,消除了对被测信号计数所产生±1Hz误差,并且达到了在整个测试频段的等精度测量。测频原理如图1所示。在测量过程中。有两个计数器分别对标准信号和被测信号同时计数。首先给出闸门开启信号(预置闸门上升沿)。此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才真正开始计数。然后预置闸门关闭信号(下降沿)到时,计数器并不预霞闸门岳=:=:.;■===司一.一一一实际闸门0;=====—■====:习一.t●::标准信号lu山llluⅢIll上lu工uItI山山山lu山上Lun凹l上山山卜——一M———叫●。I被测信号厂1广1广]门广1..卜一Ⅳx———一●‘●图1等精度测频原理波形图立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成一次测量过程。可以看出,实际闸门时间T与预置闸门时间下,并不严格相等,但差值不超过被测信号的一个周期。设在一次实际闸门时间下中计数器对被测信号的计数值为Nx,对标准信号的计数值为Ns。标准信号的频率为fs,则被测信号的频率为:仁等若忽略标频fs的误差,则等精度测频可能产生的相对误差为:8=(1fxc—&I,&e)×100%(2)其中&e为被测信号频率的准确值。在测量中,由于&计数的起停时间都是由该信号的上升沿触发的,在闸门时间T内对&的计数Nx无误差(T=NxTx);对fs的计数Ns最多相差一个数的误差,即I△Nsl≤l,其测量频率为:&e=[Nx/(Ns+△Ns)]/b(3)将式(1)和(3)代入式(2),并整理得:8=I△NsI,Ns≤l/Ns=1/(下·fs)单三泗i基日目朗删IcTEST 万方数据�

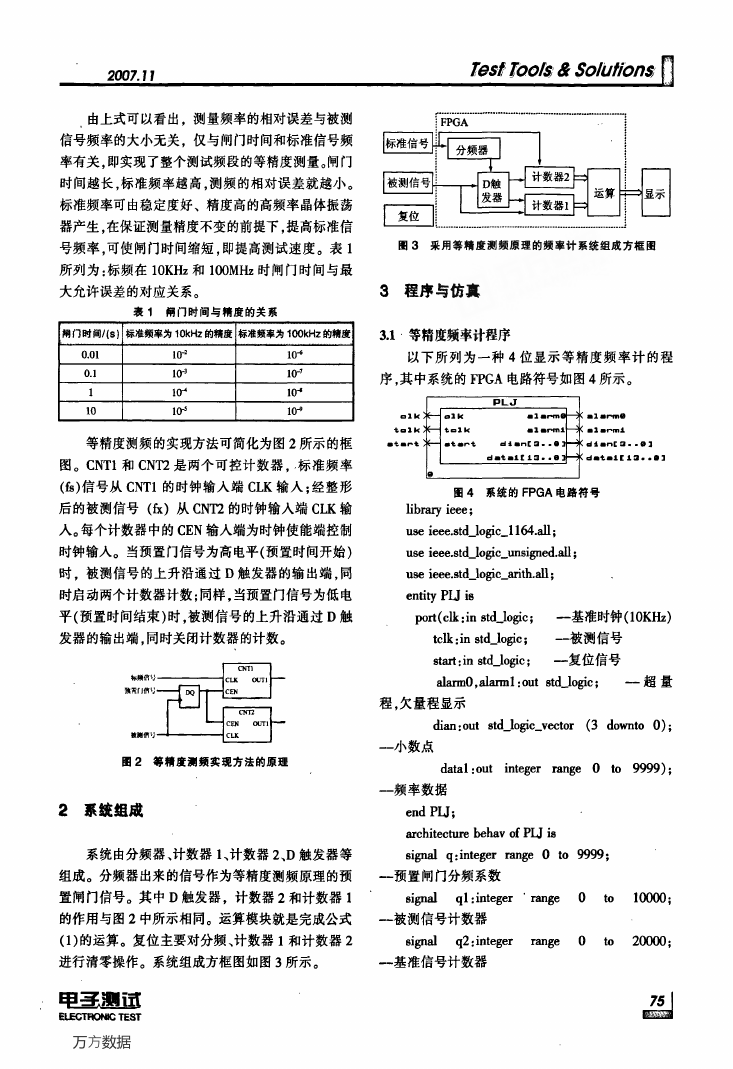

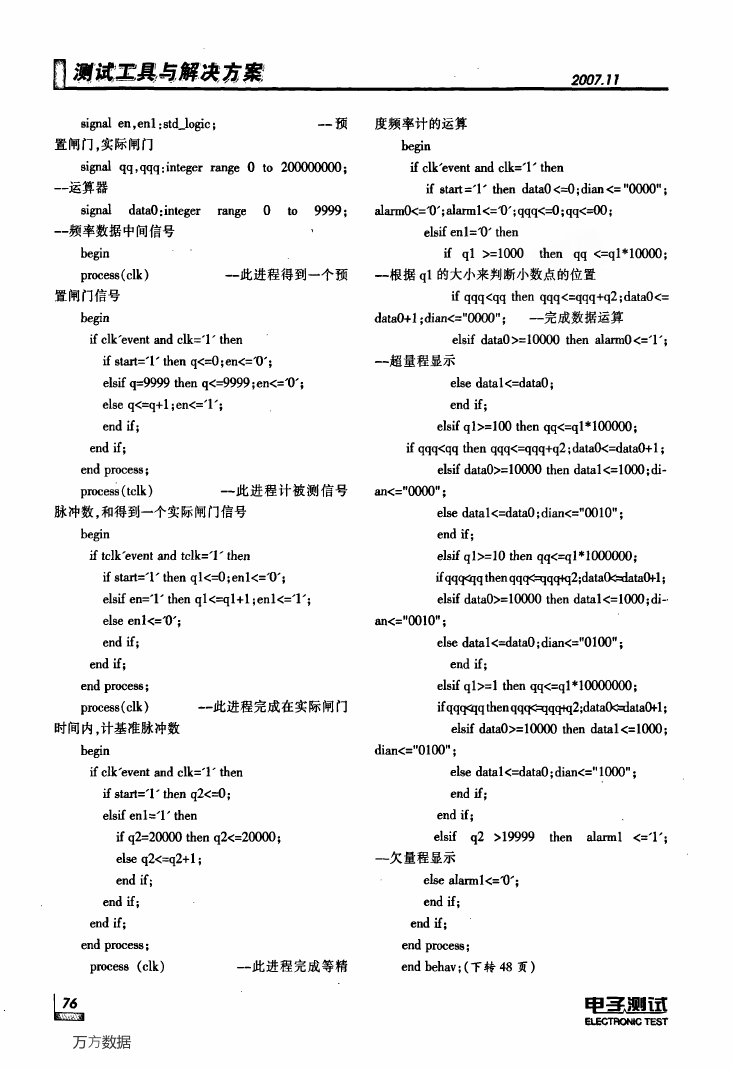

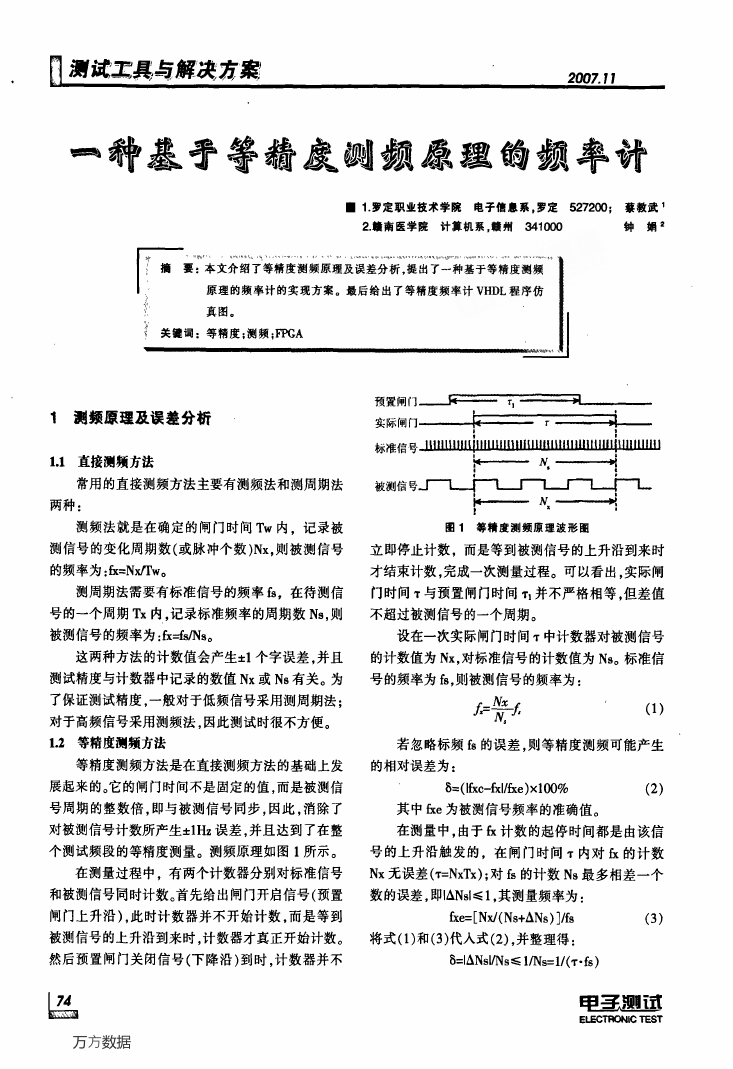

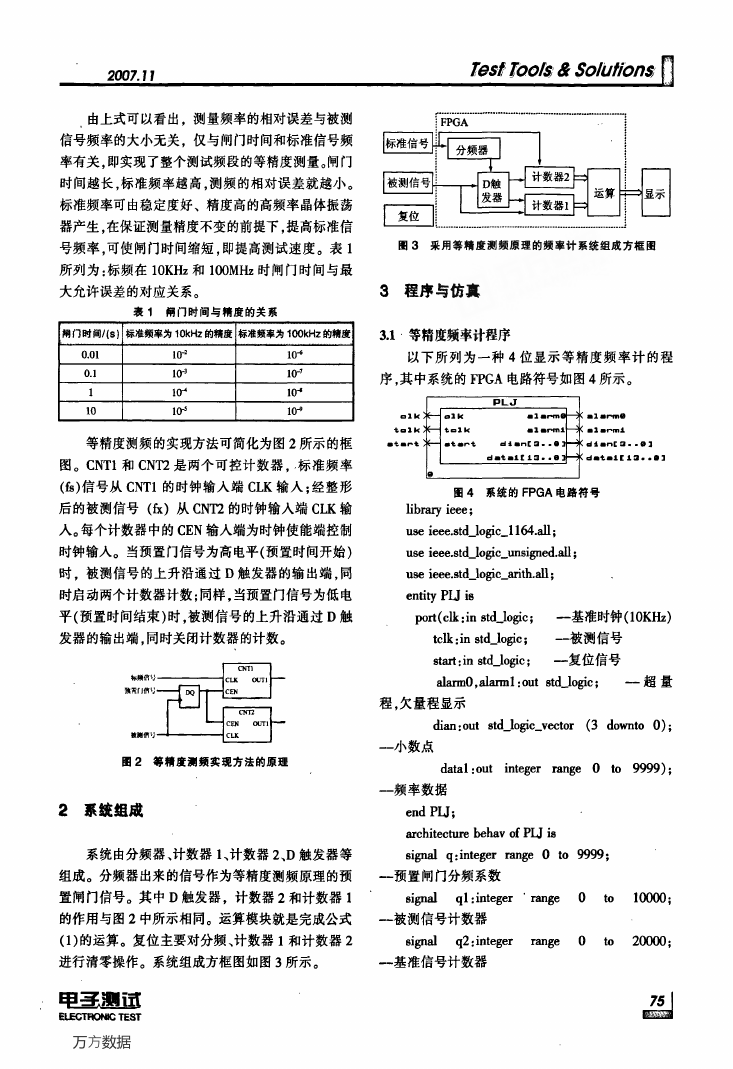

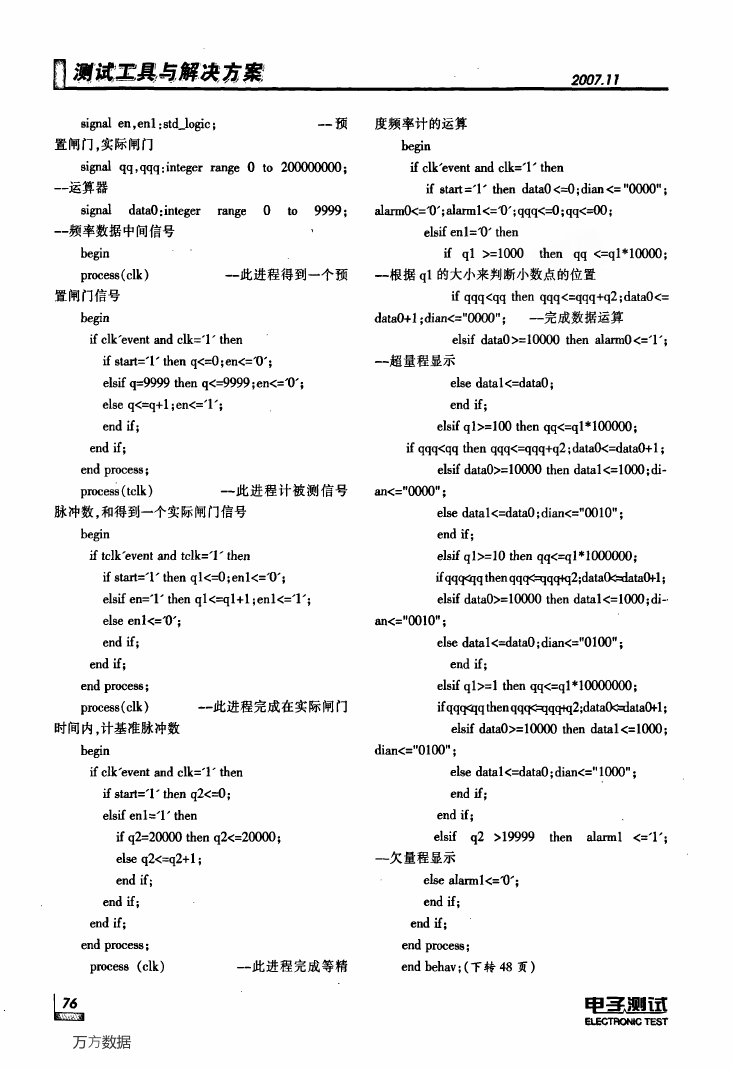

由上式可以看出。测量频率的相对误差与被测信号频率的大小无关,仅与闸门时间和标准信号频率有关。即实现了整个测试频段的等精度测量。闸门时间越长,标准频率越高,测频的相对误差就越小。标准频率可由稳定度好、精度高的高频率晶体振荡器产生,在保证测量精度不变的前提下,提高标准信号频率,可使闸门时间缩短,即提高测试速度。表1所列为:标频在10KHz和100MHz时闸门时间与最大允许误差的对应关系。表1闸门时间与精度的关系搠门时闻,fs}标准频率为10kH窿的精度标准频率为100kHz的精度O.0110-210-6O.1l扩l矿ll旷l酽10l沪1矿等精度测频的实现方法可简化为图2所示的框图。CN,I.1和CNT2是两个可控计数器。,标准频率(fs)信号从CNTl的时钟输入端CLK输入;经整形后的被测信号(&)从CN他的时钟输入端CLK输入。每个计数器中的CEN输入端为时钟使能端控制时钟输入。当预置门信号为高电平(预置时间开始)时.被测信号的上升沿通过D触发器的输出端,同时启动两个计数器计数;同样,当预置门信号为低电平(预置时间结束)时,被测信号的上升沿通过D触发器的输出端。同时关闭计数器的计数。图2等精度测频实现方法的原理2系统组成系统由分频器、计数器l、计数器2、D触发器等组成。分频器出来的信号作为等精度测频原理的预置闸门信号。其中D触发器,计数器2和计数器1的作用与图2中所示相同。运算模块就是完成公式(1)的运算。复位主要对分频、计数器1和计数器2进行清零操作。系统组成方框图如图3所示。单蚤塾i亘日日疆ROⅫCW;FPGA巫叵瞩l鲨型堡兰}一囡}……l复位li‘------------_____Jt……..图3采用等精度测频原理的频率计系统组成方框图3程序与仿真3.1‘等精度频率计程序以下所列为一种4位显示等精度频率计的程序,其中系统的FPGA电路符号如图4所示。-1■r·mo■1■r’midi-n【a·-口】d■t-1【ia··●】图4系统的FPGA电路符号libraryieee;u∞ieee.stdjogic-1l“.au;useieee.stiUogic_-unsi印ed.all;u鸵ieee.stdjo百c赫th.all;ent姆PLJi8port(cll【:instdjogic;一基准时钟(10KHz)tclk:instdjo百c;一被测信号staIt:instdjogic;一复位信号ak姗0,al锄1:outstdJogic;一超量程.欠量程显示di肌:outstdjogic—vector(3do、忸to0);一一/J、数点datal:outinteger珊lge0to9999);一频率数据endP【J:architecnlrebehavofPLJissi印alq:integermnge0to9999;~预置闸门分频系数si驴alql:integer。瑚geOto10000;一被测信号计数器si印alq2:integermge0to20000;一基准信号计数器吁U吁倩佛竹鞭¨潮杯霄键R 万方数据�

si印alen,enl:stdjo舀c;一预置闸门,实际闸门sigrIalqq,qqq:integer砌geOto200000000;一运算器8igIlaldata0:integermnge0to9999;一频率数据中间信号、beginpmcess(clk)~此进程得到一个预置闸门信号be西nifclk’eventandclk=’l7thenifstan=’17tIIenq<=0;en<=,0’;elsifq29999dIenq<=9999;en<=,0’;elseq<=q+1;en<=7r;endif:endif:endpmcess;procesi(tclk)一此进程计被测信号脉冲数,和得到一个实际闸门信号be百niftclk,eventandtclk=71’£henifstan=717thenq1<=0;enl<=,07;elsifen=’1,tllenq1<2ql+1;enl<=’1’;elseenl<=勺’:endif:endif:endprocess;process(clk)一此进程完成在实际闸门时间内。计基准脉冲数beginifclk,eventandclk=’l7thenifstan=71,thenq2<=0;elsifenl=7l,thenifq2=20000thenq2<=20000;el∞q2<=q2+l;endif;endif:endif:endprocess;proces8(clk)度频率计的运算be舀nifclk7eventandclk=7l7thenifstan=7l’tlIendata0<=0:di舳<=”0000II;alarm0<=勺7;al姗l<=,0’;qqq<=0;qq<=00;elsifenl=勺’thenifq1>=1000thenqq<=q1爿‘10000;一根据q1的大小来判断小数点的位置ifqqq=10000thenalann0<=7l’;~超量程显示elsedatal<=datalo:endif:elsifql>=100thenqq<=ql幸100000;ifqqq=10000thendatal<=1000:di·锄<=”0000”;elsedatal<=data0;dian<=”0010”;endif:elsifq1>=10tllenqq<=q1水1000000;ifqqqqqthenqqq《qqq+q2;data0《耐atackl;elsifdata0>=10000thendatal<=1000:di一,an<=”0010”:elsedatal<=datao;di肌<=”0100”;endif:elsifq1>=1thenqq<=q1枣10000000;ifqqqqqthenqqq《=qqq+q2;data0《酣atao+1;elsifdataO>=10000山endatal<=1000:di卸<=”0100”;eIsedatal<=data0;dian<=¨1000”;endif:endif;,elsifq2>19999thenal锄1<=7r;~欠量程显示elseaJ姗1<=勺’:endif:endif:endprocess;一此进程完成等精endbehav;(下转48页)屯毫迦i基目氐~T∞NIc耐 万方数据�

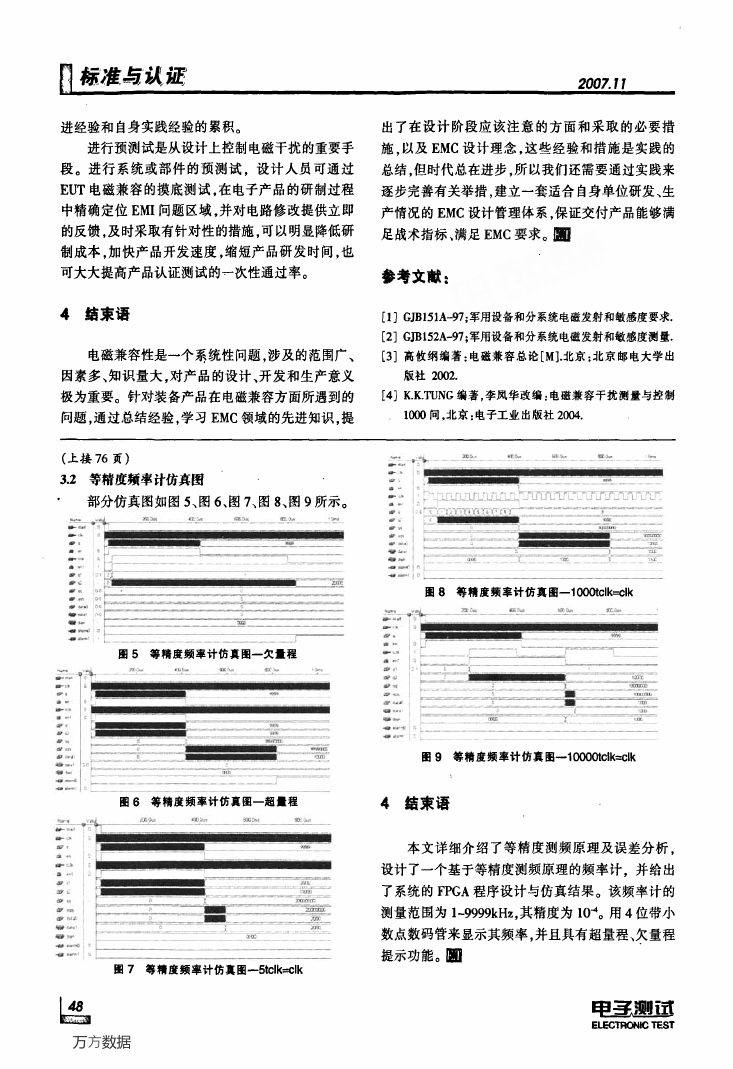

进经验和自身实践经验的累积。进行预测试是从设计上控制电磁干扰的重要手段。进行系统或部件的预测试,设计人员可通过EUT电磁兼容的摸底测试,在电子产品的研制过程中精确定位EMI问题区域,并对电路修改提供立即的反馈,及时采取有针对性的措施,可以明显降低研制成本,加快产品开发速度,缩短产品研发时间,也可大大提高产品认证测试的一次性通过率。4结束语电磁兼容性是一个系统性问题,涉及的范围广、因素多、知识量大,对产品的设计、开发和生产意义极为重要。针对装备产品在电磁兼容方面所遇到的问题,通过总结经验,学习EMC领域的先进知识,提出了在设计阶段应该注意的方面和采取的必要措施。以及EMC设计理念,这些经验和措施是实践的总结,但时代总在进步,所以我们还需要通过实践来逐步完善有关举措,建立一套适合自身单位研发、生产情况的EMC设计管理体系。保证交付产品能够满足战术指标、满足EMc要求。圃参考文献:[1]GJBl51A—97;军用设备和分系统电磁发射和敏感度要求.[2]GJBl52A-97;军用设备和分系统电磁发射和敏感度测量.[3]高攸纲编著:电磁兼容总论[M].北京:北京邮电大学出版社2002.[4]K.K.’rUNG编著,李风华改编:电磁兼容干扰测量与控制.1000问,北京:电子工业出版社2004.(上接76页)3.2等精度频率计仿真图’’部分仿真图如图5、图6、图7、图8、图9所示。图5等精度频率计仿真图一欠量程图6等精度频率计仿真图一超量程图7等精度频率计仿真图一5tcIk=cIk图8等精度频率计仿真图一1000ccIk=cIk图9等精度频率计仿真图一10000Iclk.屺Ik4结柬语本文详细介绍了等精度测频原理及误差分析。设计了一个基于等精度测频原理的频率计。并给出了系统的FPGA程序设计与仿真结果。该频率计的测量范围为1~9999kHz,其精度为lO一。用4位带小数点数码管来显示其频率,并且具有超量程、欠量程提示功能。圃屯量迦i基日日日rFIdH岭TEST 万方数据�

一种基于等精度测频原理的频率计

作者:

蔡教武, 钟娟, Cai Jiaowu, Zhongjuan

作者单位:

蔡教武,Cai Jiaowu(罗定职业技术学院,电子信息系,罗定,527200), 钟娟,Zhongjuan(赣南

医学院,计算机系,赣州,341000)

刊名:

电子测试

英文刊名:

ELECTRONIC TEST

年,卷(期):

2007,(11)

2次

引用次数:

相似文献(9条)

1.会议论文 张琼.杜祖升 等精度测频的VerilogHDL实现 2007

本文介绍了等精度测频的原理,并对其进行了误差分析。与传统测量方法相比,等精度测频可实现对大动态范围频率信号的高精度测量。设计了基于

VerilogHDL的等精度频率测量模块,实际测量结果表明被测频率在20Hz~200KHz范围内,测量精度可达到0.001Hz以上。

2.期刊论文 张小义.Zhang Xiaoyi 基于单片机的等精度数字测频 -电子测试2007(4)

针对传统计数测频电路的因随机误差和系统误差较大,导致测频不准.本文提出了利用8031单片机来实现等精度的数字测频,具有测频准确、功能扩展

易等特点.

3.期刊论文 陈一新 基于单片机的等精度数字测频装置的原理及实现 -国外电子元器件2002(4)

提出了一种基于单片机的等精度数字测频装置的实现方案 . 介绍了利用单片机的内部计数器和程序运算功能进行等精度频率测量和显示的实现方法

. 给出了测量原理和装置的设计思想,最后讨论了装置的性能指标 .

4.期刊论文 李兰芳.胡宇航.罗欢 CPLD在等精度测频系统中的应用 -仪表技术2003(4)

阐述等精度测频的原理,采用复杂可编程逻辑器件和单片机实现的实用电路,及应用VHDL语言的层次设计方法.

5.期刊论文 林平.苏五星.徐远根.闫抒升 用VHDL进行等精度测频系统设计 -空军雷达学院学报2002,16(1)

VHDL为设计者提供了在概念级处理系统的能力.随着VHDL的标准化,VHDL的运用将越来越广泛.本文应用了VHDL的层次设计方法,进行了等精度测频系

统的设计并给出了实验结果.

6.期刊论文 孟凡斌.丁雷.卓月明.MENG Fan-bin.DING Lei.ZHUO Yue-ming 基于等精度测频工作的相位测量仪设计

-机电产品开发与创新2005,18(4)

本文阐述了等精度频率测量的原理,介绍了利用其高精度的特点来测量信号的频率,在此基础上实现了测量不同相位的两路信号之间的相位差,并给出

了具体的逻辑电路设计方法及VHDL语言的层次设计方法.

7.期刊论文 张庚辰.秦京华.朱维真.郑健明.Zhang Gengchen.Qin Jinghua.Zhu Weizhen.Zheng Jianming 等精度

可变多周期不间断测频方法的研究 -仪器仪表学报2000,21(6)

本文探求在较大的被测频率信号范围内获得相同的测量精度与响应速度的测量方法及电路.文中以扭矩和转速两个参数为例分析了该测量方法的可行

性和实用性.文章详细地讨论了实现上述测量过程的时序及逻辑关系.

8.期刊论文 潘明.龚然礼 等精度测频仪的低成本微控制器实现 -广西科学院学报2004,20(4)

在叙述等精度测频原理及误差分析的基础上,阐述低成本微控制器(MCU)的硬件设计和软件设计.用低成本MCU实现的等精度测频仪的精度高,成本低

,可靠性高,使用方便,具有实用价值和生产意义.

9.期刊论文 罗怡.张璐.马玖凯.LUO Yi.ZHANG Lu.MA Jiukai 一种宽输入范围高精度频率计的设计 -现代电子技术

2009,32(15)

数字频率计设计一般都是采用分立数字器件和集成模拟芯片来实现,其精度不太高,而且输入信号范围常常受到限制.一种采用可编程数字逻辑器件

CPLD,将数字器件进行集成化,并配备高稳定度时钟,对输入模拟信号采用多路程控精密放大整形的技术,利用等精度测频法,实现了对频率的高精度测量

.使得频率测量范围达到数十兆,精度超过10-7,输入信号最小到10 mV.

引证文献(2条)

1.张清.董翔.李莹 基于单片机和FPGA的多功能计数器的设计[期刊论文]-电子设计工程 2009(7)

2.习晓红.段清明.林君.尚新磊 核磁共振信号频率测量系统的设计与实现[期刊论文]-吉林大学学报(信息科学版

) 2008(5)

本文链接:http://d.g.wanfangdata.com.cn/Periodical_dzcs200711020.aspx

下载时间:2009年12月10日

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc