碳化硅电力电子器件研发进展与存在问题

作者:陈治明

关键词:碳化硅,电力电子,器件

1 引 言

借助于微电子技术的长足发展,以硅器件为基础的电力电子技术因大功率场效应晶

体管(功率 MOS)和绝缘栅双极晶体管(IGBT)等新型电力电子器件的全面应用而臻于成

熟。目前,这些器件的开关性能已随其结构设计和制造工艺的相当完善而接近其由材料特性

决定的理论极限,依靠硅器件继续完善和提高电力电子装置与系统性能的潜力已十分有限。

于是,依靠新材料满足新一代电力电子装置与系统对器件性能的更高要求,早在世纪交替之

前就在电力电子学界与技术界形成共识,对碳化硅电力电子器件的研究与开发也随之形成热

点。

作为一种宽禁带半导体材料,碳化硅不但击穿电场强度高、热稳定性好,还具有载

流子饱和漂移速度高、热导率高等特点,可以用来制造各种耐高温的高频大功率器件,应用

于硅器件难以胜任的场合,或在一般应用中产生硅器件难以产生的效果。使用宽禁带材料可

以提高器件的工作温度。6H- SiC 和 4H-SiC 的禁带宽度分别高达 3.0 eV 和 3.25 eV,相应的

本征温度可高达 800 °C 以上;即就是禁带最窄的 3C-SiC,其禁带宽度也在 2.3eV 左右。因

此,用碳化硅做成的器件,其最高工作温度有可能超过 600°C。功率开关器件的反向电压

承受力与其漂移区(单极器件)或基区(双极器件)的长度和电阻率有关,而单极功率开关

器件的通态比电阻又直接决定于漂移区的长度和电阻率,因而与其制造材料击穿电场强度的

立方成反比[[i]]。使用击穿电场强度高的材料制作高压功率开关,其电阻率不必选择太高,

器件的漂移区或基区也不必太长。这样,不但其通态比电阻会大大降低,工作频率也会大大

提高。碳化硅的击穿电场强度是硅的 8 倍,其电子饱和漂移速度也是硅的 2 倍,更有利于提

高器件的工作频率,因而碳化硅单极功率开关不单是通态比电阻很低,其工作频率一般也要

比硅器件高 10 倍以上。热导率高则使碳化硅器件可以在高温下长时间稳定工作。此外,碳

化硅还是目前唯一可以用热氧化法生成高品质本体氧化物的化合物半导体。这使其也可以象

硅一样用来制造 MOSFET 和 IGBT 这样的含有 MOS 结构的器件。除了电力电子技术,碳化硅

的主要应用领域还包括高频电子学、高温电子学、以及传感器技术等[[ii]], [[iii]]。因此,包

含微波电源在内的电力电子技术有可能从碳化硅材料的实用化得到的好处,就不仅仅是使用

碳化硅功率开关器件对整机性能的改善,也包括材料的耐高温能力和化学稳定性通过集成信

号采集与处理系统和智能控制系统对整机性能的改善,从而可以在恶劣环境中保持良好工作

状态。], []。因此,包含微波电源在内的电力电子技术有可能从碳化硅材料的实用化得到的

好处,就不仅仅是使用碳化硅功率开关器件对整机性能的改善,也包括材料的耐高温能力和

化学稳定性通过集成信号采集与处理系统和智能控制系统对整机性能的改善,从而可以在恶

劣环境中保持良好工作状态。]。使用击穿电场强度高的材料制作高压功率开关,其电阻率

不必选择太高,器件的漂移区或基区也不必太长。这样,不但其通态比电阻会大大降低,工

作频率也会大大提高。碳化硅的击穿电场强度是硅的 8 倍,其电子饱和漂移速度也是硅的 2

倍,更有利于提高器件的工作频率,因而碳化硅单极功率开关不单是通态比电阻很低,其工

作频率一般也要比硅器件高 10 倍以上。热导率高则使碳化硅器件可以在高温下长时间稳定

工作。此外,碳化硅还是目前唯一可以用热氧化法生成高品质本体氧化物的化合物半导体。

�

这使其也可以象硅一样用来制造 MOSFET 和 IGBT 这样的含有 MOS 结构的器件。除了电力电

子技术,碳化硅的主要应用领域还包括高频电子学、高温电子学、以及传感器技术等。因此,

包含微波电源在内的电力电子技术有可能从碳化硅材料的实用化得到的好处,就不仅仅是使

用碳化硅功率开关器件对整机性能的改善,也包括材料的耐高温能力和化学稳定性通过集成

信号采集与处理系统和智能控制系统对整机性能的改善,从而可以在恶劣环境中保持良好工

作状态。

随着直径 30mm 左右的碳化硅片在 1990 年前后上市,以及高品质 6H-SiC 和 4H-SiC

外延层生长技术紧随其后的成功应用,各种碳化硅功率器件的研究和开发即蓬勃开展起来。

目前,各种功率器件都已证实可改用碳化硅来制造。尽管产量、成本、以及可靠性等问题仍

对其商品化有所限制,但碳化硅器件替代硅器件的过程已经开始。美国的 Cree 公司和德国

的 Infineon 公司(西门子集团)都已有耐压 600V、电流 10A 或 12A 以下的碳化硅肖特基势

垒二极管系列产品出售[[iv]],一支 4A 器件目前售价仅 4 美圆。碳化硅肖特基势垒二极管投

入市场,一下子将肖特基势垒二极管的应用范围从 250V(砷化镓器件)提高到 600V。同时,

其高温特性特好,从室温到由管壳限定的 175℃,反向漏电流几乎没有什么增加。若采用适

当的管壳,这种新器件的工作温度可超过 300℃。目前,许多公司已在其 IGBT 变频或逆变

装置中用这种器件取代硅快恢复二极管[[v]],取得提高工作频率、大幅度降低开关损耗的明

显效果,其总体效益远远超过碳化硅器件与硅器件的价差。要不了多少年,电力电子装置和

系统的性能就会因为碳化硅器件的广泛应用而得到极大改善。],取得提高工作频率、大幅

度降低开关损耗的明显效果,其总体效益远远超过碳化硅器件与硅器件的价差。要不了多少

年,电力电子装置和系统的性能就会因为碳化硅器件的广泛应用而得到极大改善。],一支

4A 器件目前售价仅 4 美圆。碳化硅肖特基势垒二极管投入市场,一下子将肖特基势垒二极

管的应用范围从 250V(砷化镓器件)提高到 600V。同时,其高温特性特好,从室温到由管

壳限定的 175℃,反向漏电流几乎没有什么增加。若采用适当的管壳,这种新器件的工作温

度可超过 300℃。目前,许多公司已在其 IGBT 变频或逆变装置中用这种器件取代硅快恢复

二极管,取得提高工作频率、大幅度降低开关损耗的明显效果,其总体效益远远超过碳化硅

器件与硅器件的价差。要不了多少年,电力电子装置和系统的性能就会因为碳化硅器件的广

泛应用而得到极大改善。

下面,就几种主要的碳化硅电力电子器件,从器件、材料和制造工艺的当前水平到存在的主

要问题作一评述。

2 碳化硅电力电子器件

就应用要求而言,电力电子器件除了要尽可能降低静态和动态损耗而外,还要有尽可能高的

承受浪涌电流(电流在数十毫秒的瞬间数倍于稳态值)的能力。由于浪涌电流会引起器件结

温的骤然升高,通态比电阻偏高的器件,其浪涌电流承受力注定非常低。由于单极功率器件

的通态比电阻随其阻断电压的提高而迅速增大,硅功率 MOS 只在电压等级不超过 100V 时

才具有较好的性能价格比。尽管硅 IGBT 在这方面有很大改进,但其开关速度比功率 MOS

低,不能满足高频应用的需要。 理论分析表明,用 6H-SiC 和 4H-SiC 制造功率 MOS,其通态

比电阻可以比同等级的硅功率 MOS 分别低 100 倍和 2000 倍[[vi]]。这就是说,如果用碳化硅

制造单极器件,在阻断电压高达 10 000 V 的情况下,其通态压降还会比硅的双极器件低。而

单极器件在工作频率等方面要优于双极器件,因而对碳化硅电力电子器件的研究开发比较集

中于肖特基势垒二极管和 MOSFET,并取得较大进展;但双极晶体管和晶闸管之类的双极器

件,特别是]。这就是说,如果用碳化硅制造单极器件,在阻断电压高达 10 000 V 的情况下,

其通态压降还会比硅的双极器件低。而单极器件在工作频率等方面要优于双极器件,因而对

碳化硅电力电子器件的研究开发比较集中于肖特基势垒二极管和 MOSFET,并取得较大进展;

但双极晶体管和晶闸管之类的双极器件,特别是 PIN 二极管也相当受重视,进展也很快。

�

2.1 碳化硅肖特基势垒二极管(SBD)

许多金属,例如镍(Ni)金 (Au)、铂 (Pt)、钯(Pd)、钛 (Ti)、钴 (Co) 等,都可与碳化硅形

成肖特基势垒接触,其势垒高度一般在 1eV 以上。据报道,Au/4H-SiC 接触的势垒高度可达

1.73 eV ,Ti/4H-SiC 接触的高度也有 1.1 eV[[vii]]]。6H-SiC 的肖特基势垒高度变化范围较宽,

最低只有 0.5 eV,最高可达 1.7 eV[[viii]]]。

美国北卡州立大学功率半导体研究中心(PSRC)于 1992 年最先报道了全世界首次研制成功

的 6H-SiC 肖特基势垒二极管,其阻断电压为 400V[[ix]]]。在他们 1994 年的报道中,阻断电

压提高到 1000V,接近其理论设计值[[x]]]。随后,对碳化硅肖特基势垒二极管的研发活动扩

展到欧洲和亚洲,使用材料扩大到 4H-SiC,阻断电压也有很大提高[[xi]],[[xii]]]],[]。

由于高电压下碳化硅的肖特基势垒比硅薄,进一步提高碳化硅肖特基势垒二极管的阻断电压

就会受到隧穿势垒的反向漏电流的限制。计算表明,对一个高度为 1eV 的典型碳化硅肖特

基势垒,与碳化硅临界击穿电场 3MVcm-1 相对应的最高击穿电压下的势垒宽度只有 3 nm 左

右。这正好是发生电子隧穿的典型宽度。为了充分发挥碳化硅临界击穿电场强度高的优势,

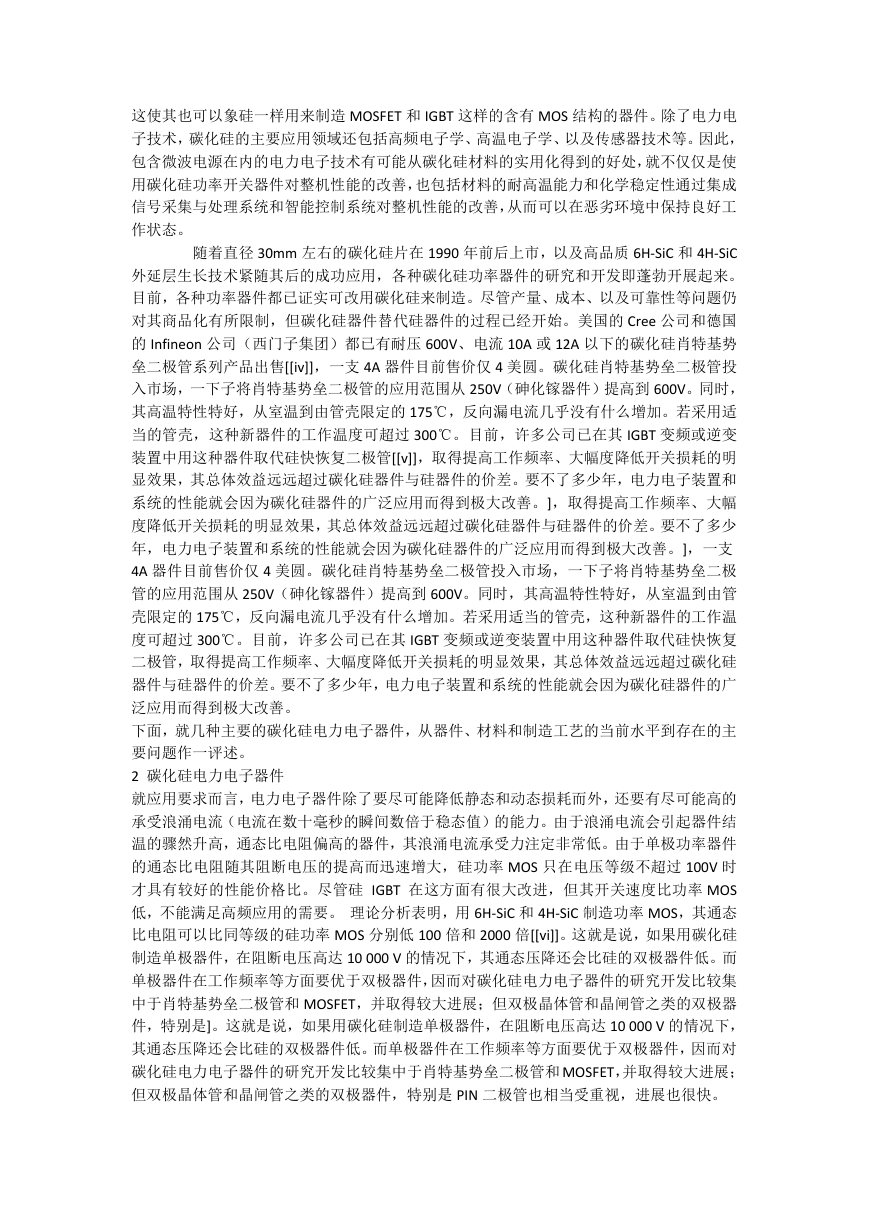

可采用如图 1 所示的 pn 结肖特基势垒复合结构(简称 JBS 或 MPS)来排除隧穿电流对实现

最高阻断电压的限制。这种结构原本是对硅器件提出来的[[xiii]]]。由于 pn 结的势垒高度与

半导体的禁带宽度有关,而肖特基势垒高度只决定于金属与半导体的功函数差,因而这两种

势垒的高度之差对宽禁带半导体来说可以很大。这样,当 JBS 器件正偏置时,肖特基势垒区

可因势垒低而首先进入导通状态,成为器件的主导,而 pn 结则因开启电压较高而基本不起

作用;但在反偏状态,pn 结正好可以发挥其高势垒的作用,在高反压下以迅速扩展的耗尽

区为肖特基势垒屏蔽强电场,从而使反向漏电流大幅度下降[[xiv]],[[xv]]]],[]。JBS 与单纯肖特

基势垒二极管一样,仍然是一种多数载流子器件,其反向恢复时间可降低到几个纳秒,只有

硅快速二极管和碳化硅高压 pn 结二极管的十分之一。

JBS 目前的困难在于 p 型碳化硅的欧姆接触较难形成,因为用离子注入法对碳化硅进行 p 型

掺杂需要很高的退火温度,在碳化硅中很难形成 p+区。采用 Baliga 提出的凹槽肖特基势垒

二极管 (TSBS) 结构可以获得与 JBS 类似的效果,却可避免 p 型掺杂[[xvi]]]。如图 2 所示,在

碳化硅外延层的表面和表层凹槽的表面分别用功函数不同的两种金属形成高低不同的肖特

基势垒。低势垒接触在表面,高势垒接触在凹槽表面,后者为前者起削弱反向电场的作用。

实验表明,如果这两种接触的势垒高度以及台面宽度和凹槽深度搭配得当,器件的反向漏电

流可以大大降低[[xvii]]]。

目前,对大功率碳化硅肖特基势垒二极管的研究开发已达到小面积(直径 0.5 mm 以下)器

件的反向阻断电压超过 4000 V,大面积(直径超过 1 mm)器件也能达到 1000 V 左右的水平。

例如,在 2001 年中已有 140A/800V 4H-SiC JBS 的报导[[xviii]]]。在同年的另一报导中,反向

电压高达 1200V 的 4H-SiC 肖特基势垒二极管已做到直径 3mm,其正向电流密度高达 300

Acm-2,而相应的正向压降只有 2V[[xix]]]。

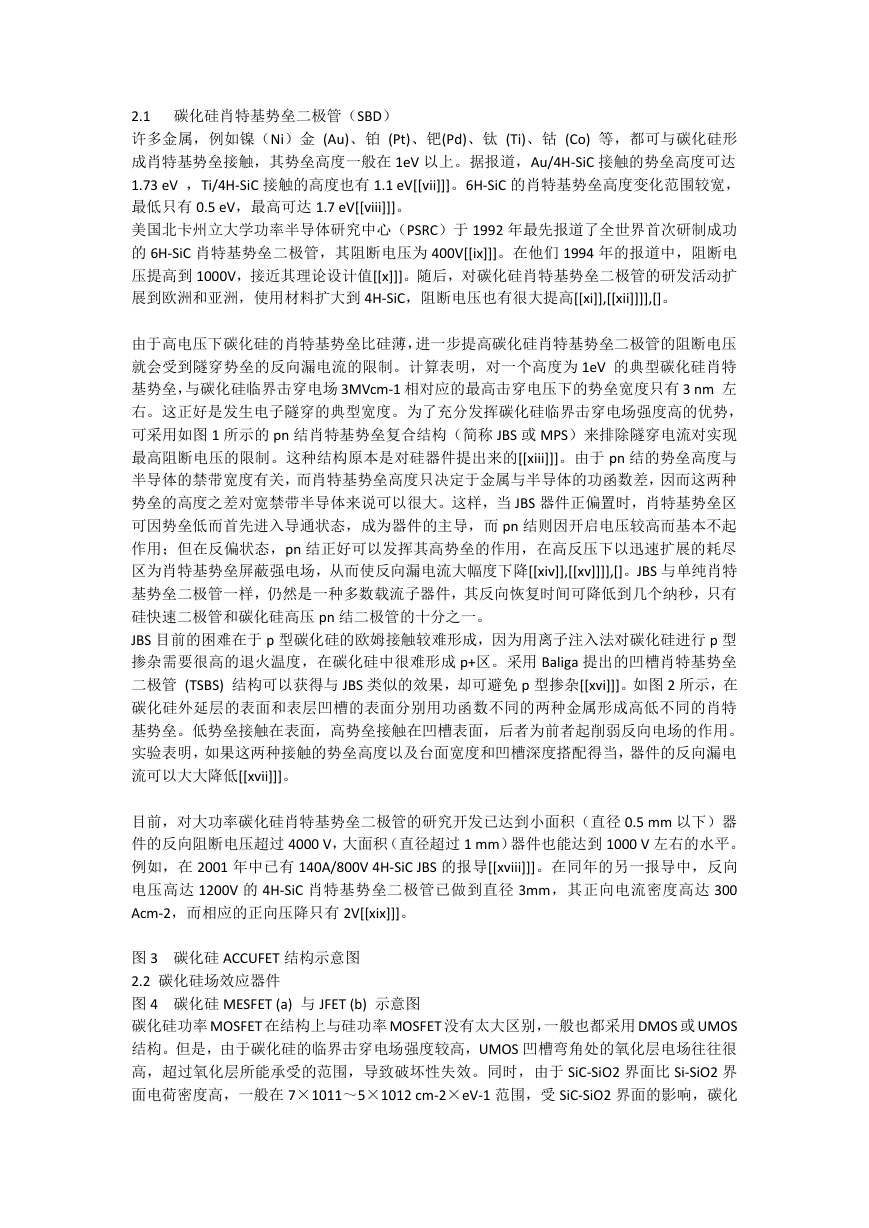

图 3 碳化硅 ACCUFET 结构示意图

2.2 碳化硅场效应器件

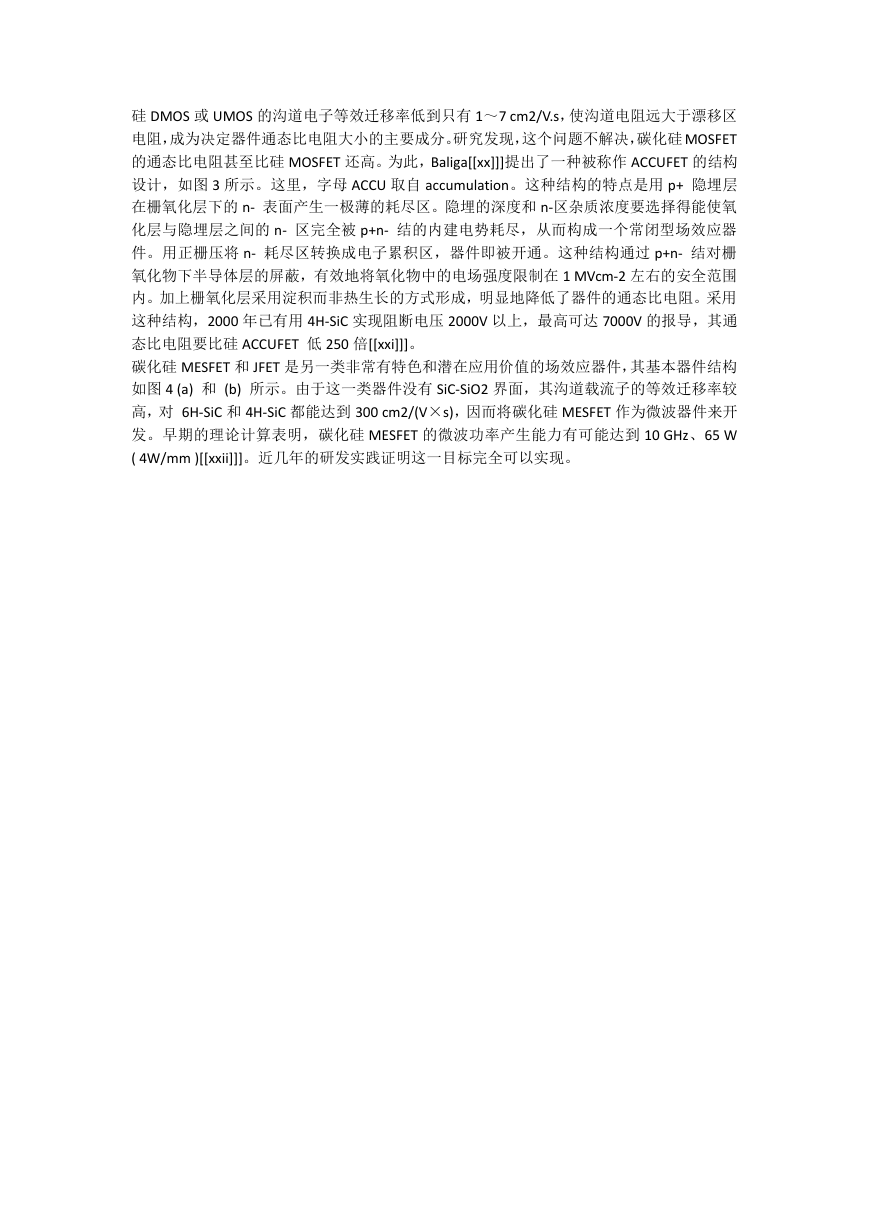

图 4 碳化硅 MESFET (a) 与 JFET (b) 示意图

碳化硅功率 MOSFET 在结构上与硅功率 MOSFET 没有太大区别,一般也都采用 DMOS 或 UMOS

结构。但是,由于碳化硅的临界击穿电场强度较高,UMOS 凹槽弯角处的氧化层电场往往很

高,超过氧化层所能承受的范围,导致破坏性失效。同时,由于 SiC-SiO2 界面比 Si-SiO2 界

面电荷密度高,一般在 7×1011~5×1012 cm-2×eV-1 范围,受 SiC-SiO2 界面的影响,碳化

�

硅 DMOS 或 UMOS 的沟道电子等效迁移率低到只有 1~7 cm2/V.s,使沟道电阻远大于漂移区

电阻,成为决定器件通态比电阻大小的主要成分。研究发现,这个问题不解决,碳化硅 MOSFET

的通态比电阻甚至比硅 MOSFET 还高。为此,Baliga[[xx]]]提出了一种被称作 ACCUFET 的结构

设计,如图 3 所示。这里,字母 ACCU 取自 accumulation。这种结构的特点是用 p+ 隐埋层

在栅氧化层下的 n- 表面产生一极薄的耗尽区。隐埋的深度和 n-区杂质浓度要选择得能使氧

化层与隐埋层之间的 n- 区完全被 p+n- 结的内建电势耗尽,从而构成一个常闭型场效应器

件。用正栅压将 n- 耗尽区转换成电子累积区,器件即被开通。这种结构通过 p+n- 结对栅

氧化物下半导体层的屏蔽,有效地将氧化物中的电场强度限制在 1 MVcm-2 左右的安全范围

内。加上栅氧化层采用淀积而非热生长的方式形成,明显地降低了器件的通态比电阻。采用

这种结构,2000 年已有用 4H-SiC 实现阻断电压 2000V 以上,最高可达 7000V 的报导,其通

态比电阻要比硅 ACCUFET 低 250 倍[[xxi]]]。

碳化硅 MESFET 和 JFET 是另一类非常有特色和潜在应用价值的场效应器件,其基本器件结构

如图 4 (a) 和 (b) 所示。由于这一类器件没有 SiC-SiO2 界面,其沟道载流子的等效迁移率较

高,对 6H-SiC 和 4H-SiC 都能达到 300 cm2/(V×s),因而将碳化硅 MESFET 作为微波器件来开

发。早期的理论计算表明,碳化硅 MESFET 的微波功率产生能力有可能达到 10 GHz、65 W

( 4W/mm )[[xxii]]]。近几年的研发实践证明这一目标完全可以实现。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc