实验三、电子表电路设计

一、实验目的:

通过对电子表例程的分析、改进,掌握复杂电路的调试方法,元件例化语

句的使用方法,熟悉大规模复杂时序电路的设计方法,掌握层次化的设计思路,

通过此实验能够熟练的应用 VHDL 语言和 EDA 设计工具独立的完成复杂设计。

二、实验原理:

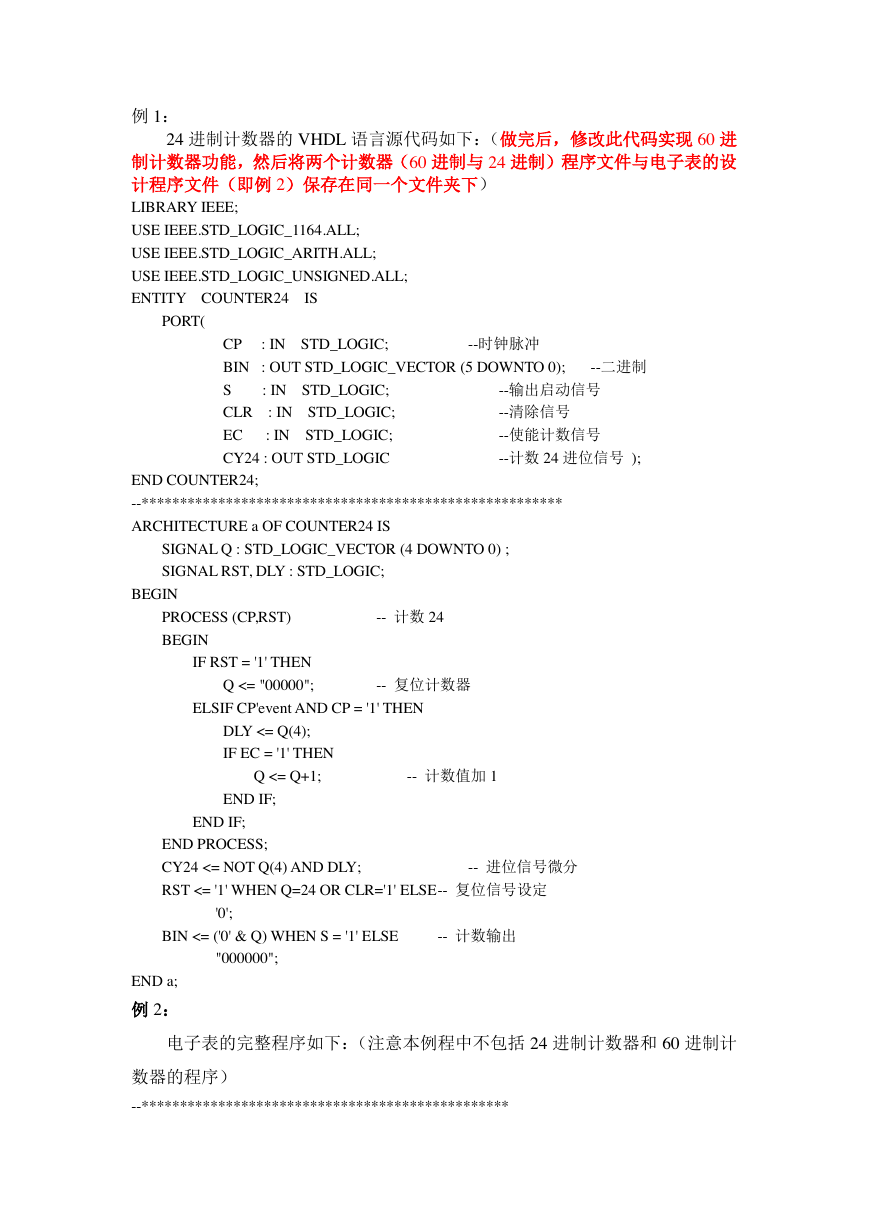

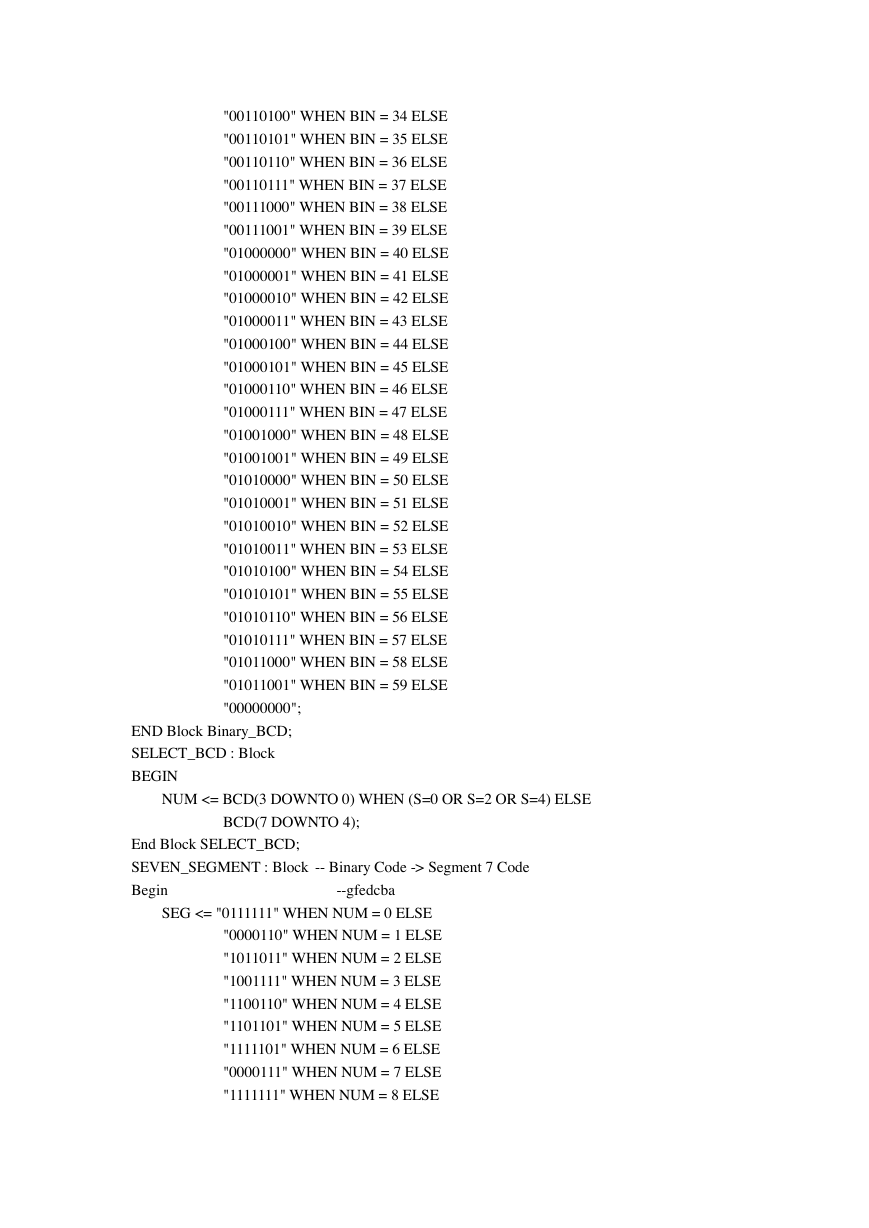

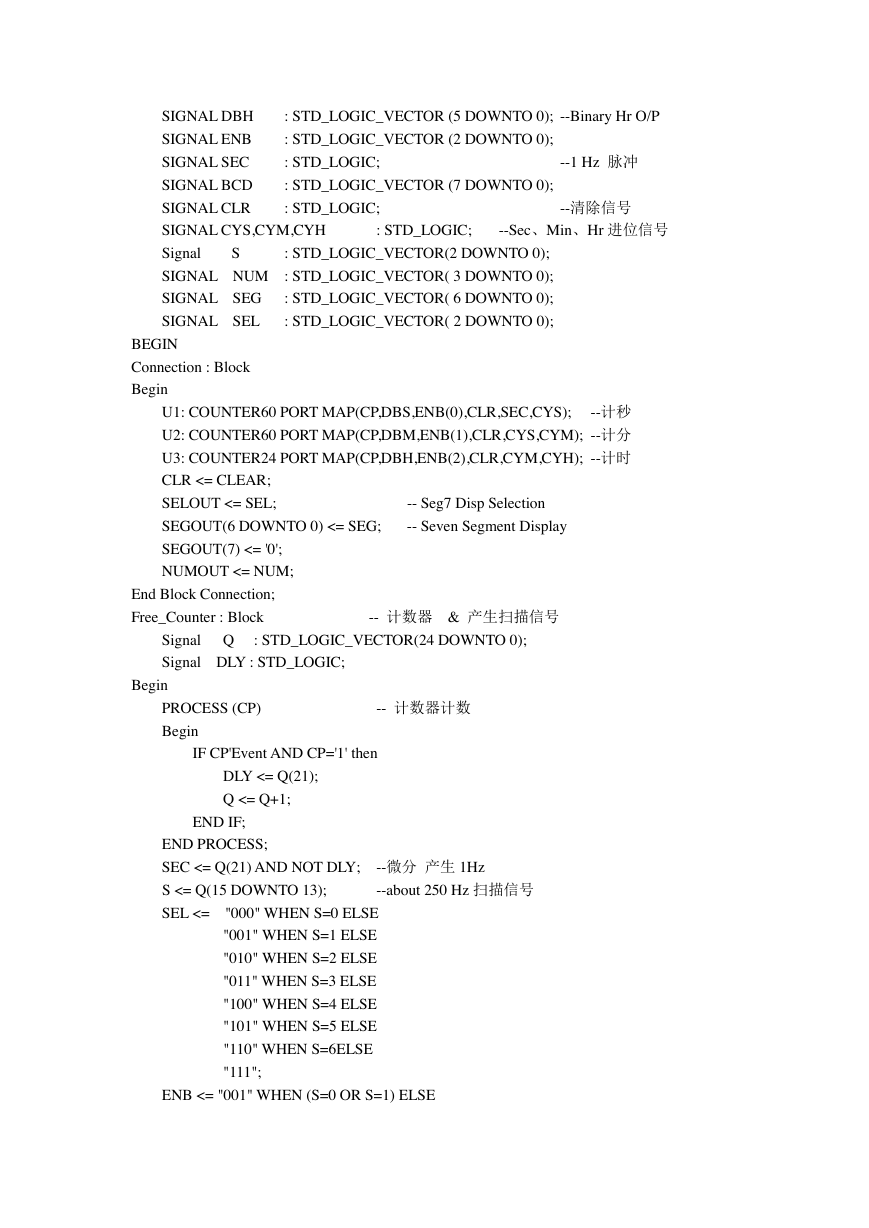

下图为数字电子表的原理图。

6 个七段数码管

38

译

码

SEG (8)

时钟显示

电路方框图

CP

分频器Q

SEC

BCD

七段译码电路

NUM(4)

BCD 选择

扫描电路 S(3)

ENB

(2)

CYH

24

进

制

ENB (1)

60

进

制

CY

ENB

(0)

CYS

60

进

制

计数器

计数器

计数器

BCD (7-4)

BCD (3-0)

DBH

DBM

DBS

BCD(8)BIN(6)

BIN ( 6 )

CLR

三、实验设备:

1、用实验箱上的八个七段数码管做电子表的显示器,用拨码开关做为输入。

(注意:要把 20 进制和 60 进制计数器的元件例化程序与电子表工程文件放在

同一工程文件夹下),取实验箱上晶振的 5M 频率做为基频。

四、实验步骤:

�

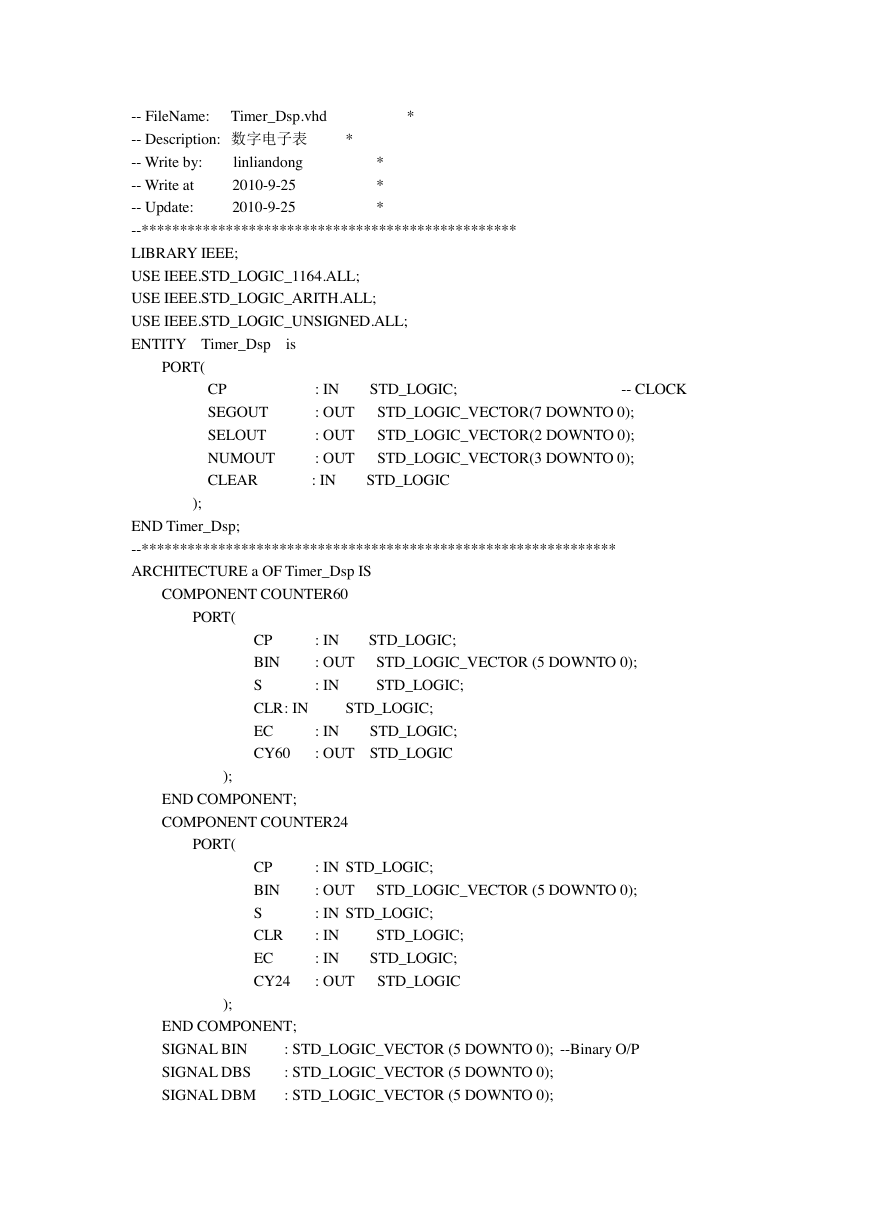

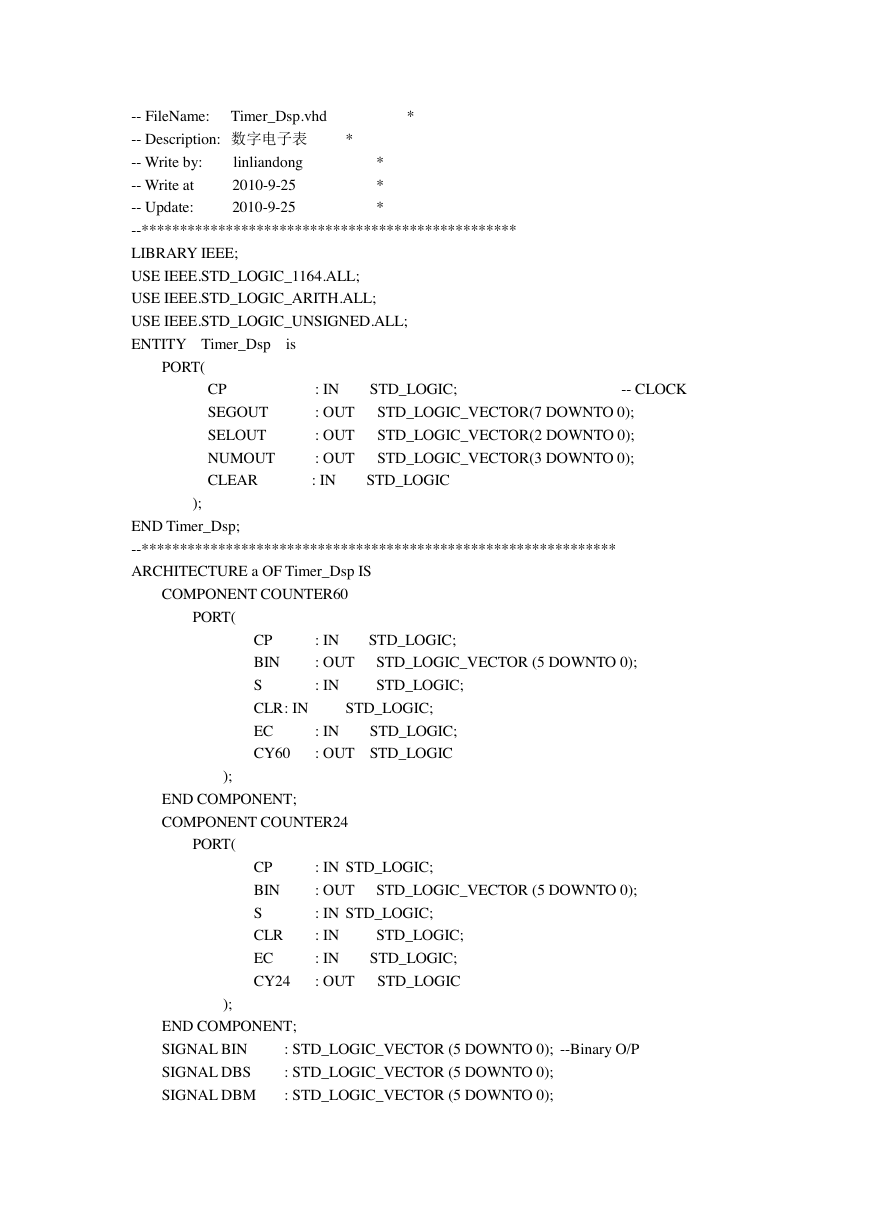

例 1:

24 进制计数器的 VHDL 语言源代码如下:(做完后,修改此代码实现 60 进

制计数器功能,然后将两个计数器(60 进制与 24 进制)程序文件与电子表的设

计程序文件(即例 2)保存在同一个文件夹下)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNTER24 IS

PORT(

CP : IN STD_LOGIC;

--时钟脉冲

BIN : OUT STD_LOGIC_VECTOR (5 DOWNTO 0);

S : IN STD_LOGIC;

CLR : IN STD_LOGIC;

EC : IN STD_LOGIC;

CY24 : OUT STD_LOGIC

--二进制

--输出启动信号

--清除信号

--使能计数信号

--计数 24 进位信号 );

END COUNTER24;

--*******************************************************

ARCHITECTURE a OF COUNTER24 IS

SIGNAL Q : STD_LOGIC_VECTOR (4 DOWNTO 0) ;

SIGNAL RST, DLY : STD_LOGIC;

BEGIN

PROCESS (CP,RST)

BEGIN

IF RST = '1' THEN

Q <= "00000";

-- 计数 24

-- 复位计数器

ELSIF CP'event AND CP = '1' THEN

DLY <= Q(4);

IF EC = '1' THEN

Q <= Q+1;

END IF;

END IF;

-- 计数值加 1

END PROCESS;

CY24 <= NOT Q(4) AND DLY;

RST <= '1' WHEN Q=24 OR CLR='1' ELSE -- 复位信号设定

-- 进位信号微分

'0';

BIN <= ('0' & Q) WHEN S = '1' ELSE

-- 计数输出

"000000";

END a;

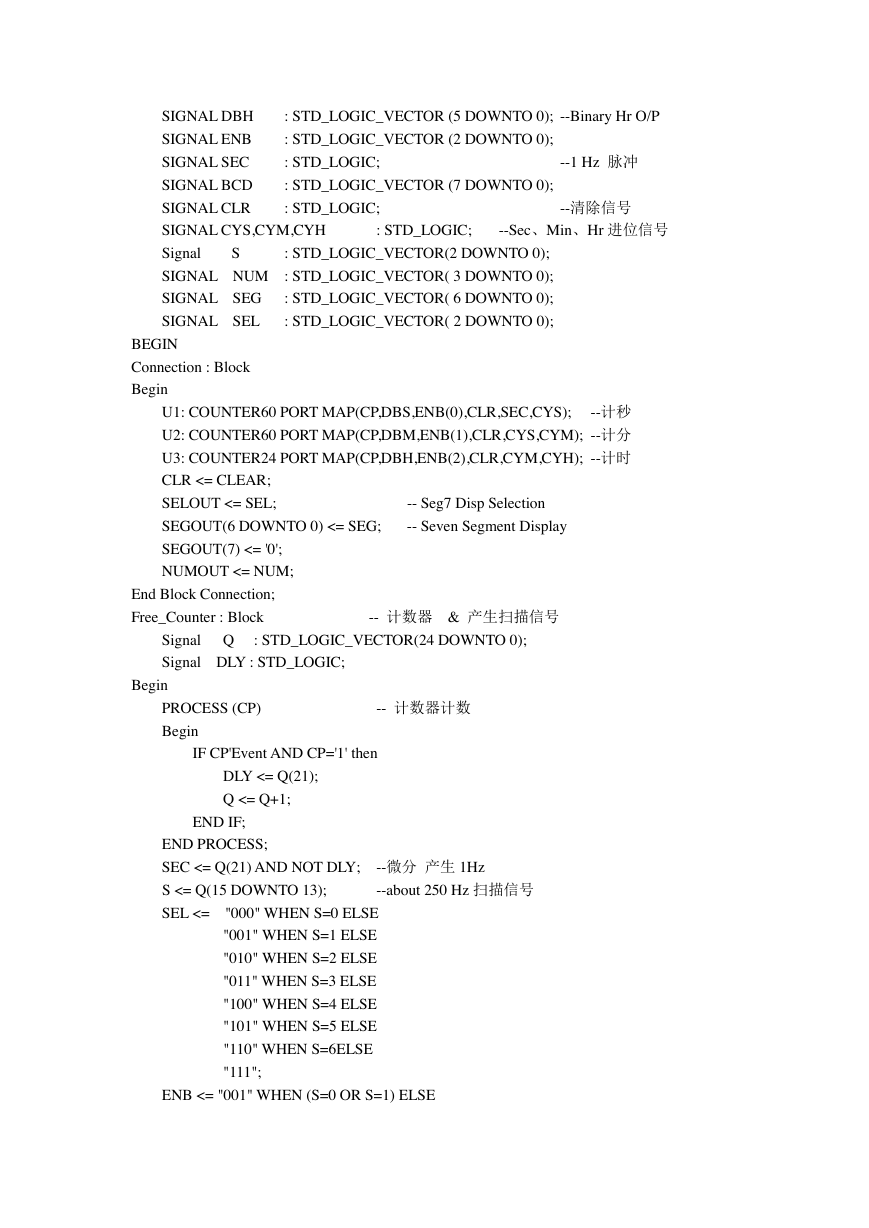

例 2:

电子表的完整程序如下:(注意本例程中不包括 24 进制计数器和 60 进制计

数器的程序)

--************************************************

�

-- FileName:

-- Description: 数字电子表

Timer_Dsp.vhd

*

*

-- Write by: linliandong

-- Write at 2010-9-25

-- Update: 2010-9-25

*

*

*

--*************************************************

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY Timer_Dsp is

PORT(

CP

SEGOUT

SELOUT

: IN STD_LOGIC;

-- CLOCK

: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

: OUT STD_LOGIC_VECTOR(2 DOWNTO 0);

NUMOUT

: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CLEAR : IN STD_LOGIC

);

END Timer_Dsp;

--**************************************************************

ARCHITECTURE a OF Timer_Dsp IS

COMPONENT COUNTER60

PORT(

CP

: IN STD_LOGIC;

BIN

: OUT

STD_LOGIC_VECTOR (5 DOWNTO 0);

S

: IN

STD_LOGIC;

CLR : IN

STD_LOGIC;

EC

: IN STD_LOGIC;

CY60

: OUT STD_LOGIC

);

END COMPONENT;

COMPONENT COUNTER24

PORT(

CP

: IN STD_LOGIC;

BIN

: OUT

STD_LOGIC_VECTOR (5 DOWNTO 0);

S

: IN STD_LOGIC;

CLR

EC

: IN

STD_LOGIC;

: IN STD_LOGIC;

CY24

: OUT STD_LOGIC

);

END COMPONENT;

SIGNAL BIN

: STD_LOGIC_VECTOR (5 DOWNTO 0); --Binary O/P

SIGNAL DBS

: STD_LOGIC_VECTOR (5 DOWNTO 0);

SIGNAL DBM

: STD_LOGIC_VECTOR (5 DOWNTO 0);

�

SIGNAL DBH

: STD_LOGIC_VECTOR (5 DOWNTO 0); --Binary Hr O/P

SIGNAL ENB

: STD_LOGIC_VECTOR (2 DOWNTO 0);

SIGNAL SEC

: STD_LOGIC;

--1 Hz 脉冲

SIGNAL BCD

: STD_LOGIC_VECTOR (7 DOWNTO 0);

SIGNAL CLR

: STD_LOGIC;

SIGNAL CYS,CYM,CYH

: STD_LOGIC;

--清除信号

--Sec、Min、Hr 进位信号

Signal S

: STD_LOGIC_VECTOR(2 DOWNTO 0);

SIGNAL NUM : STD_LOGIC_VECTOR( 3 DOWNTO 0);

SIGNAL SEG

: STD_LOGIC_VECTOR( 6 DOWNTO 0);

SIGNAL SEL

: STD_LOGIC_VECTOR( 2 DOWNTO 0);

BEGIN

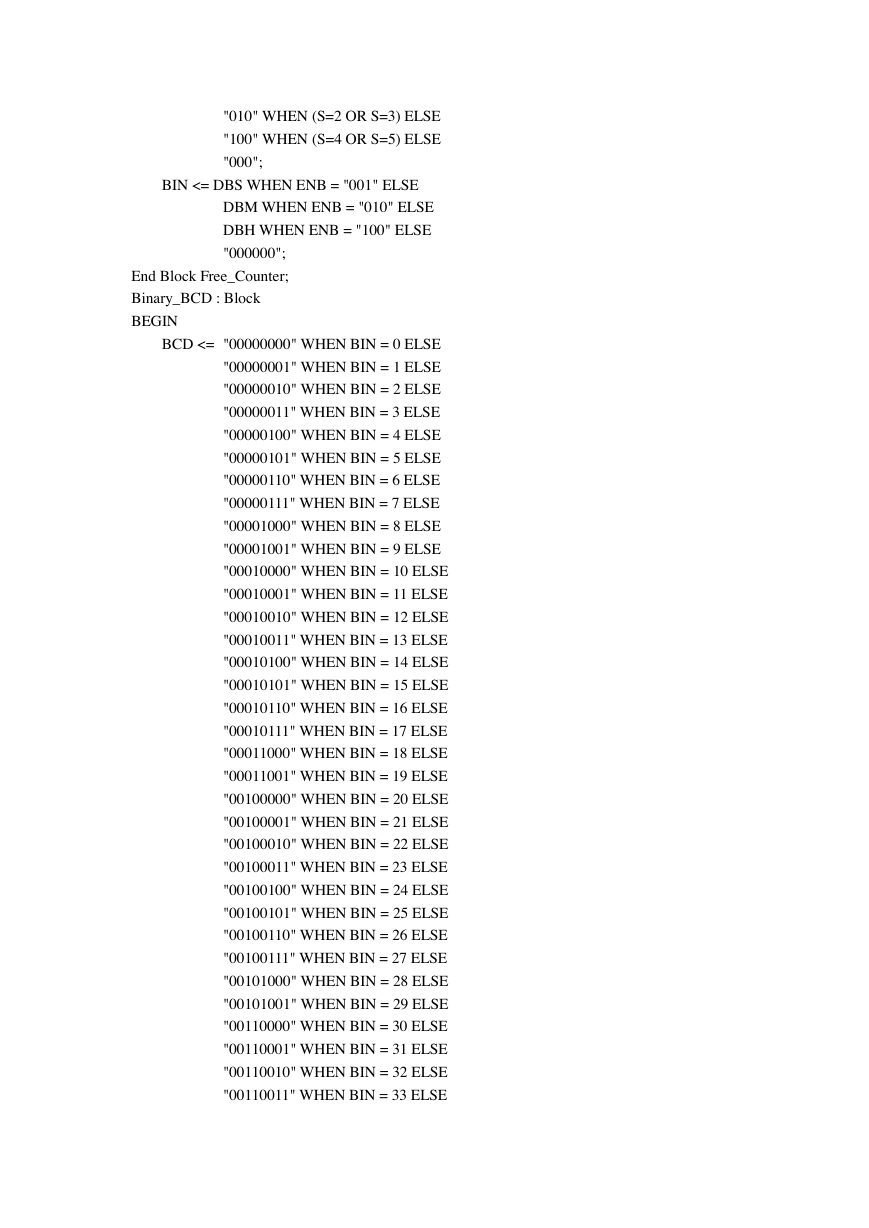

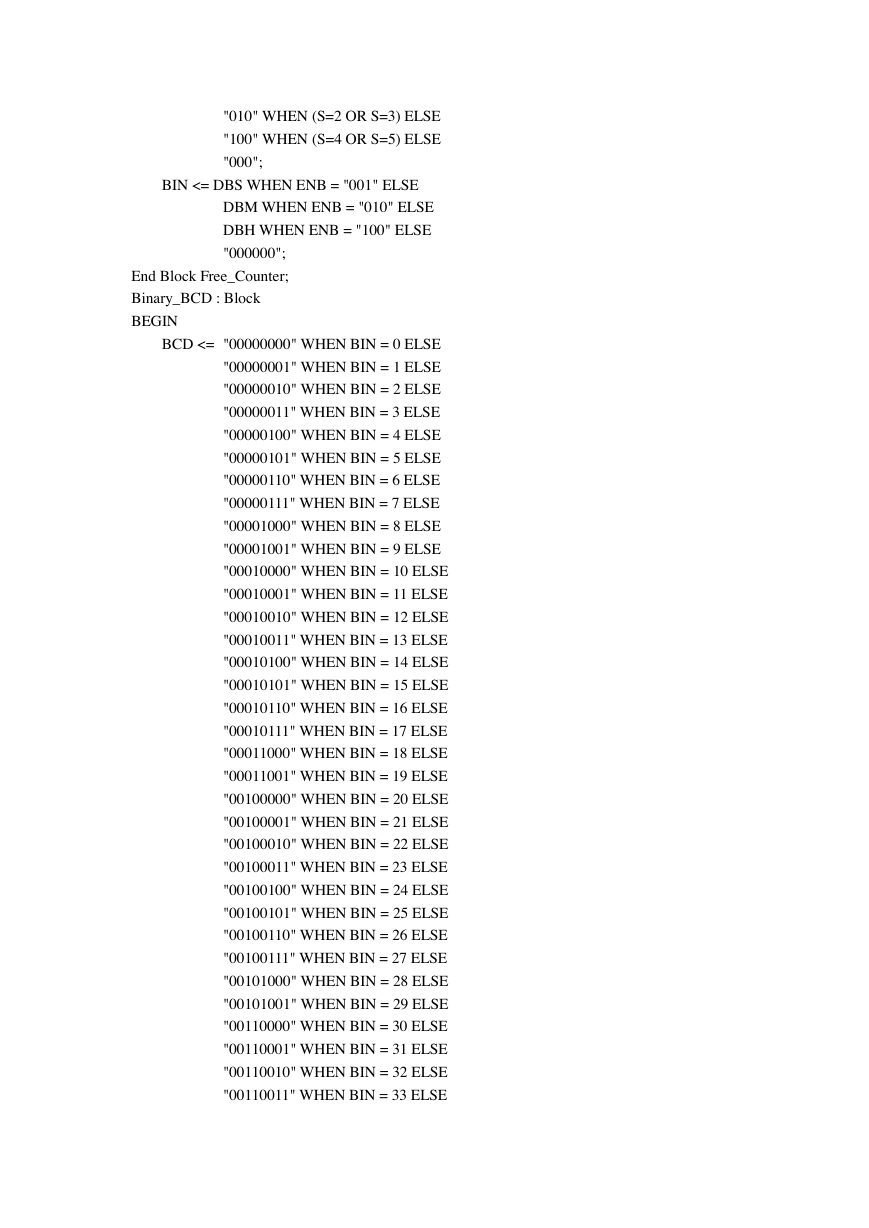

Connection : Block

Begin

--计秒

U1: COUNTER60 PORT MAP(CP,DBS,ENB(0),CLR,SEC,CYS);

U2: COUNTER60 PORT MAP(CP,DBM,ENB(1),CLR,CYS,CYM); --计分

U3: COUNTER24 PORT MAP(CP,DBH,ENB(2),CLR,CYM,CYH); --计时

CLR <= CLEAR;

SELOUT <= SEL;

-- Seg7 Disp Selection

SEGOUT(6 DOWNTO 0) <= SEG;

-- Seven Segment Display

SEGOUT(7) <= '0';

NUMOUT <= NUM;

End Block Connection;

Free_Counter : Block

-- 计数器 & 产生扫描信号

Signal Q

: STD_LOGIC_VECTOR(24 DOWNTO 0);

Signal DLY : STD_LOGIC;

Begin

PROCESS (CP)

-- 计数器计数

Begin

IF CP'Event AND CP='1' then

DLY <= Q(21);

Q <= Q+1;

END IF;

--微分 产生 1Hz

--about 250 Hz 扫描信号

END PROCESS;

SEC <= Q(21) AND NOT DLY;

S <= Q(15 DOWNTO 13);

SEL <= "000" WHEN S=0 ELSE

"001" WHEN S=1 ELSE

"010" WHEN S=2 ELSE

"011" WHEN S=3 ELSE

"100" WHEN S=4 ELSE

"101" WHEN S=5 ELSE

"110" WHEN S=6ELSE

"111";

ENB <= "001" WHEN (S=0 OR S=1) ELSE

�

"010" WHEN (S=2 OR S=3) ELSE

"100" WHEN (S=4 OR S=5) ELSE

"000";

BIN <= DBS WHEN ENB = "001" ELSE

DBM WHEN ENB = "010" ELSE

DBH WHEN ENB = "100" ELSE

"000000";

End Block Free_Counter;

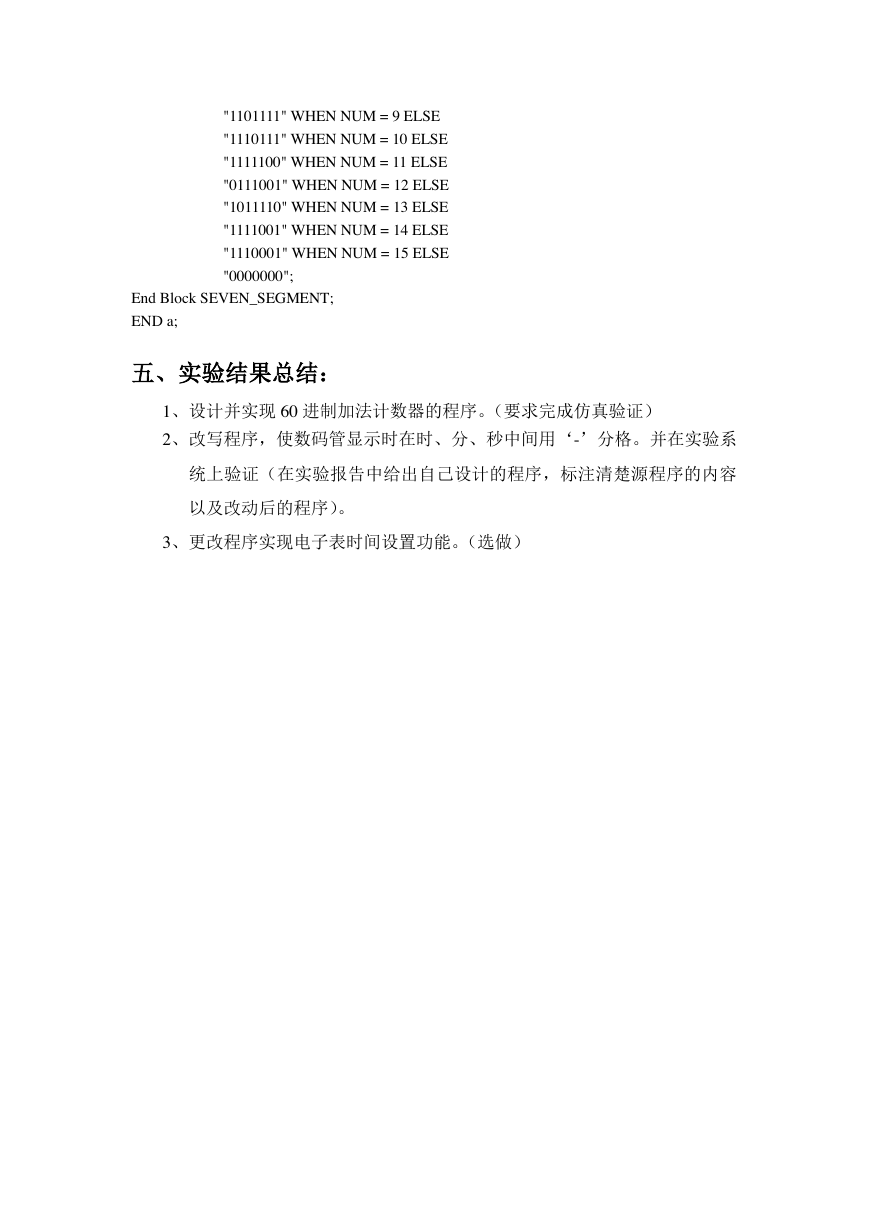

Binary_BCD : Block

BEGIN

BCD <= "00000000" WHEN BIN = 0 ELSE

"00000001" WHEN BIN = 1 ELSE

"00000010" WHEN BIN = 2 ELSE

"00000011" WHEN BIN = 3 ELSE

"00000100" WHEN BIN = 4 ELSE

"00000101" WHEN BIN = 5 ELSE

"00000110" WHEN BIN = 6 ELSE

"00000111" WHEN BIN = 7 ELSE

"00001000" WHEN BIN = 8 ELSE

"00001001" WHEN BIN = 9 ELSE

"00010000" WHEN BIN = 10 ELSE

"00010001" WHEN BIN = 11 ELSE

"00010010" WHEN BIN = 12 ELSE

"00010011" WHEN BIN = 13 ELSE

"00010100" WHEN BIN = 14 ELSE

"00010101" WHEN BIN = 15 ELSE

"00010110" WHEN BIN = 16 ELSE

"00010111" WHEN BIN = 17 ELSE

"00011000" WHEN BIN = 18 ELSE

"00011001" WHEN BIN = 19 ELSE

"00100000" WHEN BIN = 20 ELSE

"00100001" WHEN BIN = 21 ELSE

"00100010" WHEN BIN = 22 ELSE

"00100011" WHEN BIN = 23 ELSE

"00100100" WHEN BIN = 24 ELSE

"00100101" WHEN BIN = 25 ELSE

"00100110" WHEN BIN = 26 ELSE

"00100111" WHEN BIN = 27 ELSE

"00101000" WHEN BIN = 28 ELSE

"00101001" WHEN BIN = 29 ELSE

"00110000" WHEN BIN = 30 ELSE

"00110001" WHEN BIN = 31 ELSE

"00110010" WHEN BIN = 32 ELSE

"00110011" WHEN BIN = 33 ELSE

�

"00110100" WHEN BIN = 34 ELSE

"00110101" WHEN BIN = 35 ELSE

"00110110" WHEN BIN = 36 ELSE

"00110111" WHEN BIN = 37 ELSE

"00111000" WHEN BIN = 38 ELSE

"00111001" WHEN BIN = 39 ELSE

"01000000" WHEN BIN = 40 ELSE

"01000001" WHEN BIN = 41 ELSE

"01000010" WHEN BIN = 42 ELSE

"01000011" WHEN BIN = 43 ELSE

"01000100" WHEN BIN = 44 ELSE

"01000101" WHEN BIN = 45 ELSE

"01000110" WHEN BIN = 46 ELSE

"01000111" WHEN BIN = 47 ELSE

"01001000" WHEN BIN = 48 ELSE

"01001001" WHEN BIN = 49 ELSE

"01010000" WHEN BIN = 50 ELSE

"01010001" WHEN BIN = 51 ELSE

"01010010" WHEN BIN = 52 ELSE

"01010011" WHEN BIN = 53 ELSE

"01010100" WHEN BIN = 54 ELSE

"01010101" WHEN BIN = 55 ELSE

"01010110" WHEN BIN = 56 ELSE

"01010111" WHEN BIN = 57 ELSE

"01011000" WHEN BIN = 58 ELSE

"01011001" WHEN BIN = 59 ELSE

"00000000";

END Block Binary_BCD;

SELECT_BCD : Block

BEGIN

NUM <= BCD(3 DOWNTO 0) WHEN (S=0 OR S=2 OR S=4) ELSE

BCD(7 DOWNTO 4);

End Block SELECT_BCD;

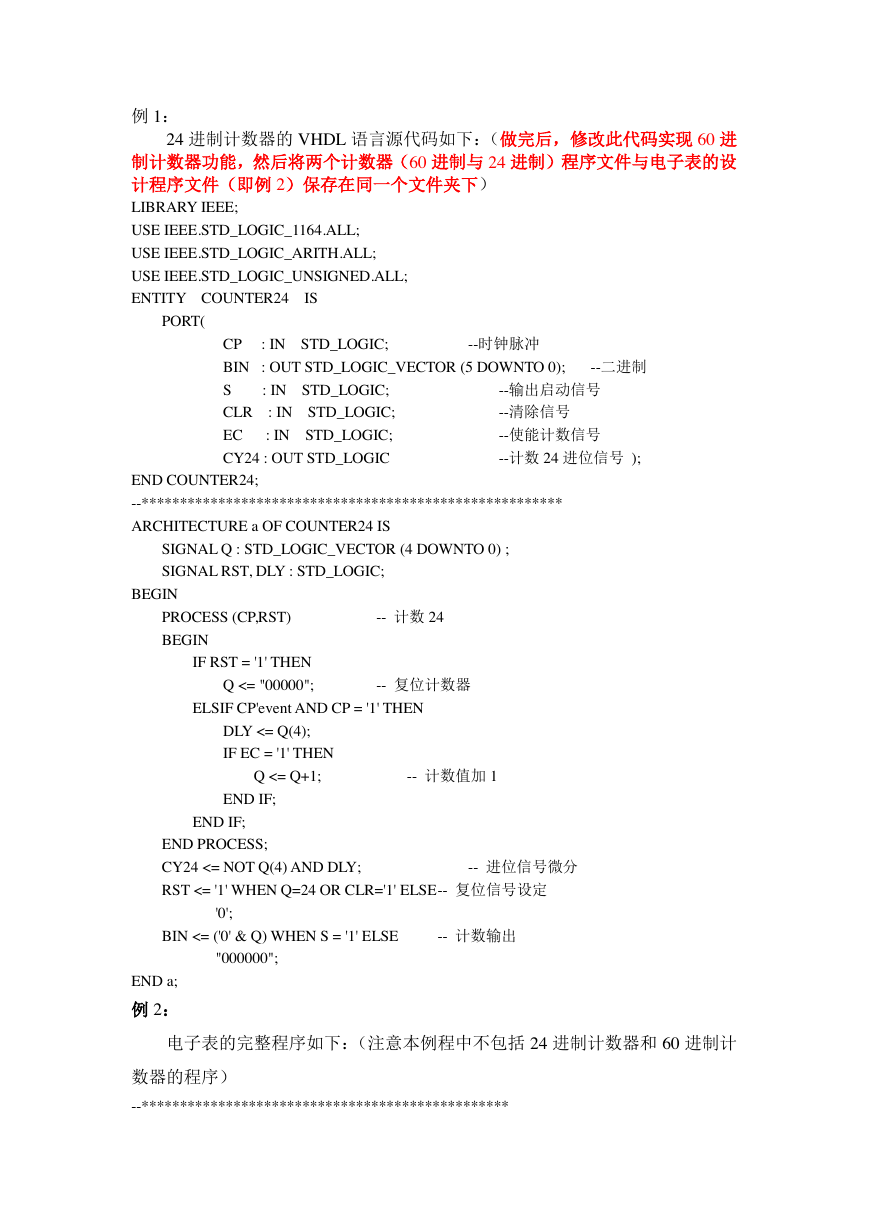

SEVEN_SEGMENT : Block -- Binary Code -> Segment 7 Code

Begin --gfedcba

SEG <= "0111111" WHEN NUM = 0 ELSE

"0000110" WHEN NUM = 1 ELSE

"1011011" WHEN NUM = 2 ELSE

"1001111" WHEN NUM = 3 ELSE

"1100110" WHEN NUM = 4 ELSE

"1101101" WHEN NUM = 5 ELSE

"1111101" WHEN NUM = 6 ELSE

"0000111" WHEN NUM = 7 ELSE

"1111111" WHEN NUM = 8 ELSE

�

"1101111" WHEN NUM = 9 ELSE

"1110111" WHEN NUM = 10 ELSE

"1111100" WHEN NUM = 11 ELSE

"0111001" WHEN NUM = 12 ELSE

"1011110" WHEN NUM = 13 ELSE

"1111001" WHEN NUM = 14 ELSE

"1110001" WHEN NUM = 15 ELSE

"0000000";

End Block SEVEN_SEGMENT;

END a;

五、实验结果总结:

1、设计并实现 60 进制加法计数器的程序。(要求完成仿真验证)

2、改写程序,使数码管显示时在时、分、秒中间用‘-’分格。并在实验系

统上验证(在实验报告中给出自己设计的程序,标注清楚源程序的内容

以及改动后的程序)。

3、更改程序实现电子表时间设置功能。(选做)

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc