5

4

3

2

1

D

C

B

A

D

C

B

A

ALINX Confidential

5

4

3

2

Http://www.heijin.org

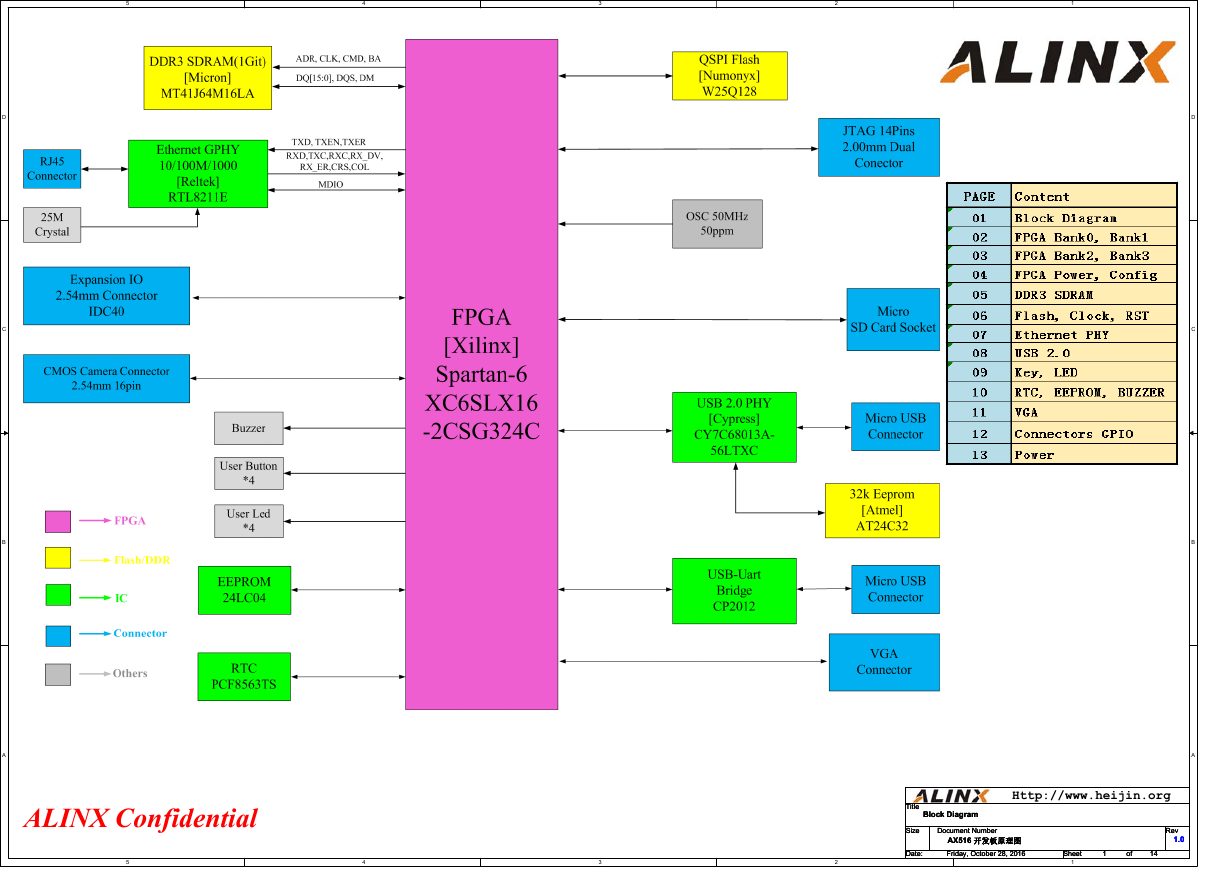

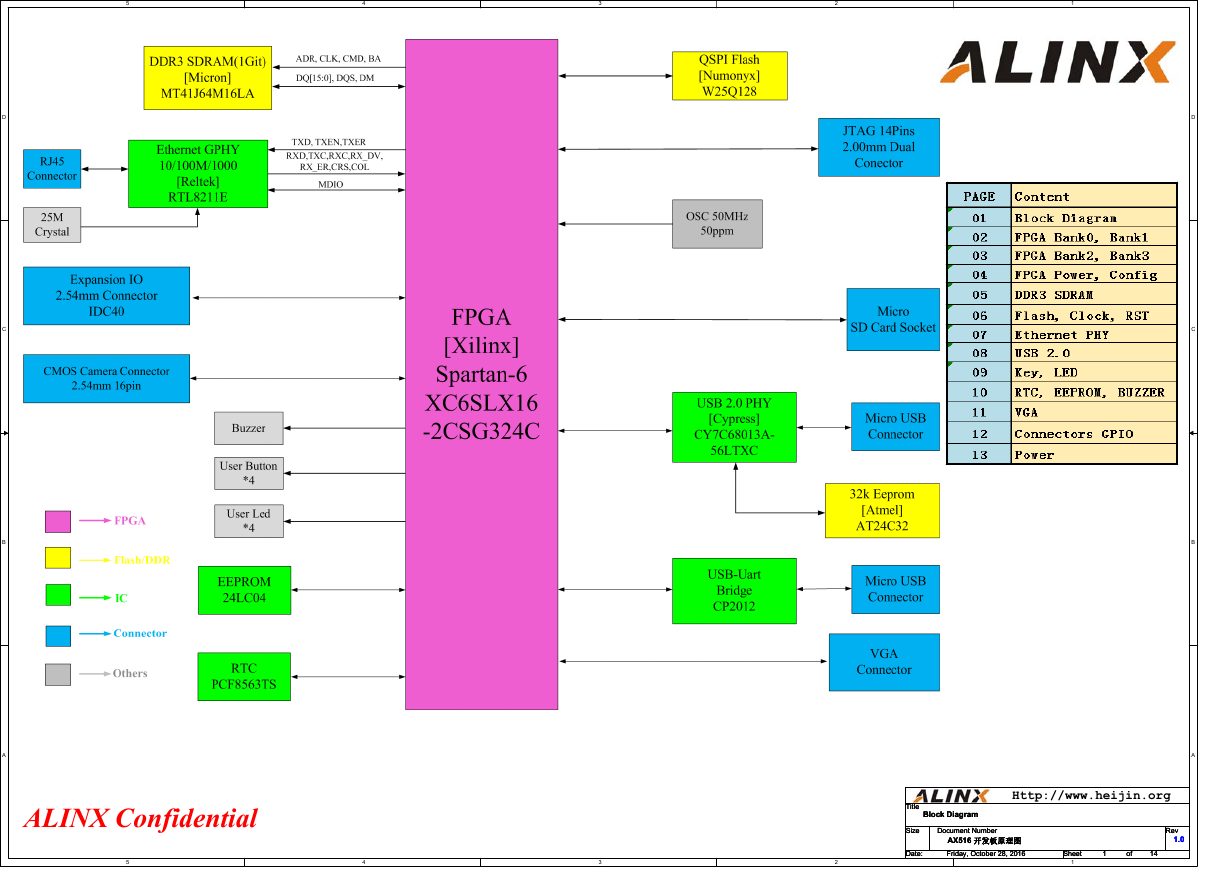

Block Diagram

Block Diagram

Block Diagram

Document Number

Document Number

Document Number

AX516 开发板原理图

AX516 开发板原理图

AX516 开发板原理图

Friday, October 28, 2016

Friday, October 28, 2016

Friday, October 28, 2016

Rev

Rev

Rev

1.0

1.0

1.0

Sheet

Sheet

Sheet

1

1

1

1

of

of

of

14

14

14

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

�

3

2

U1B

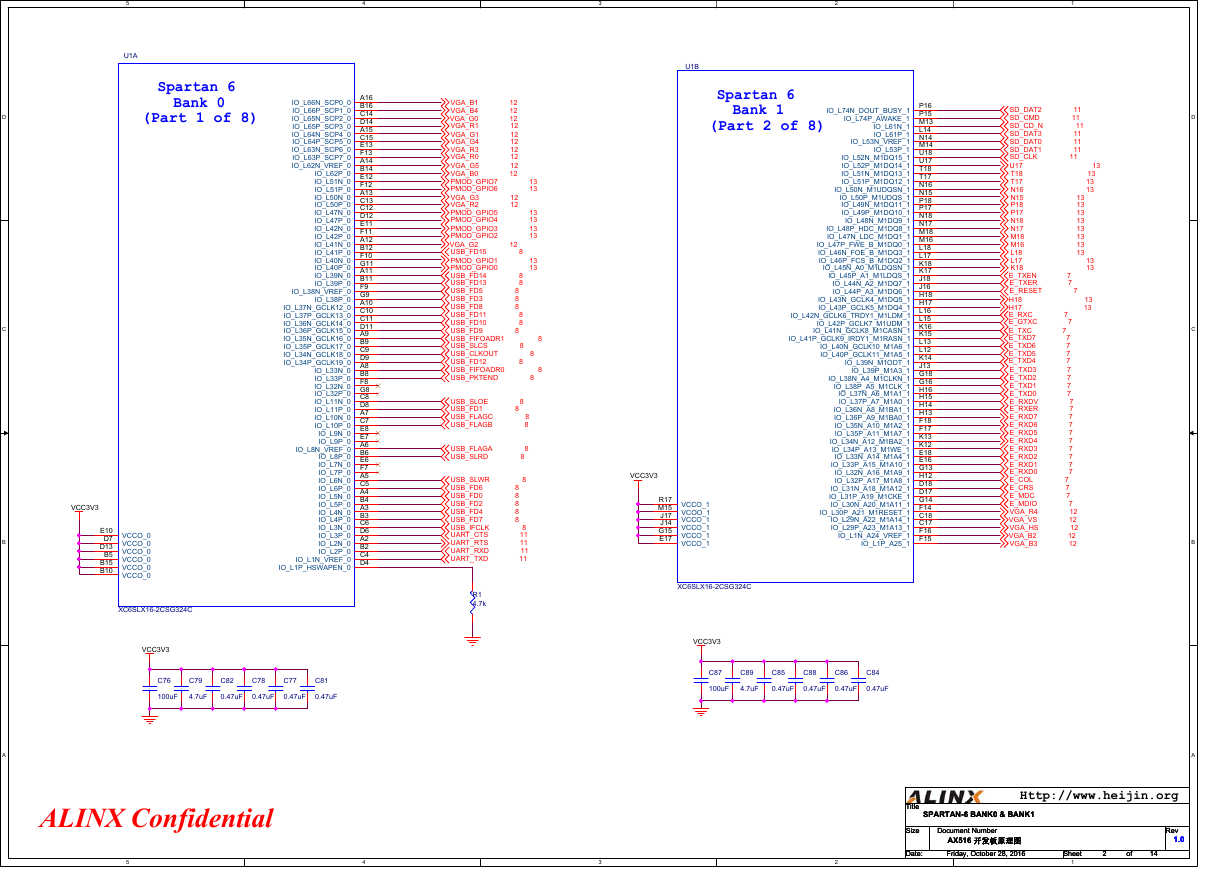

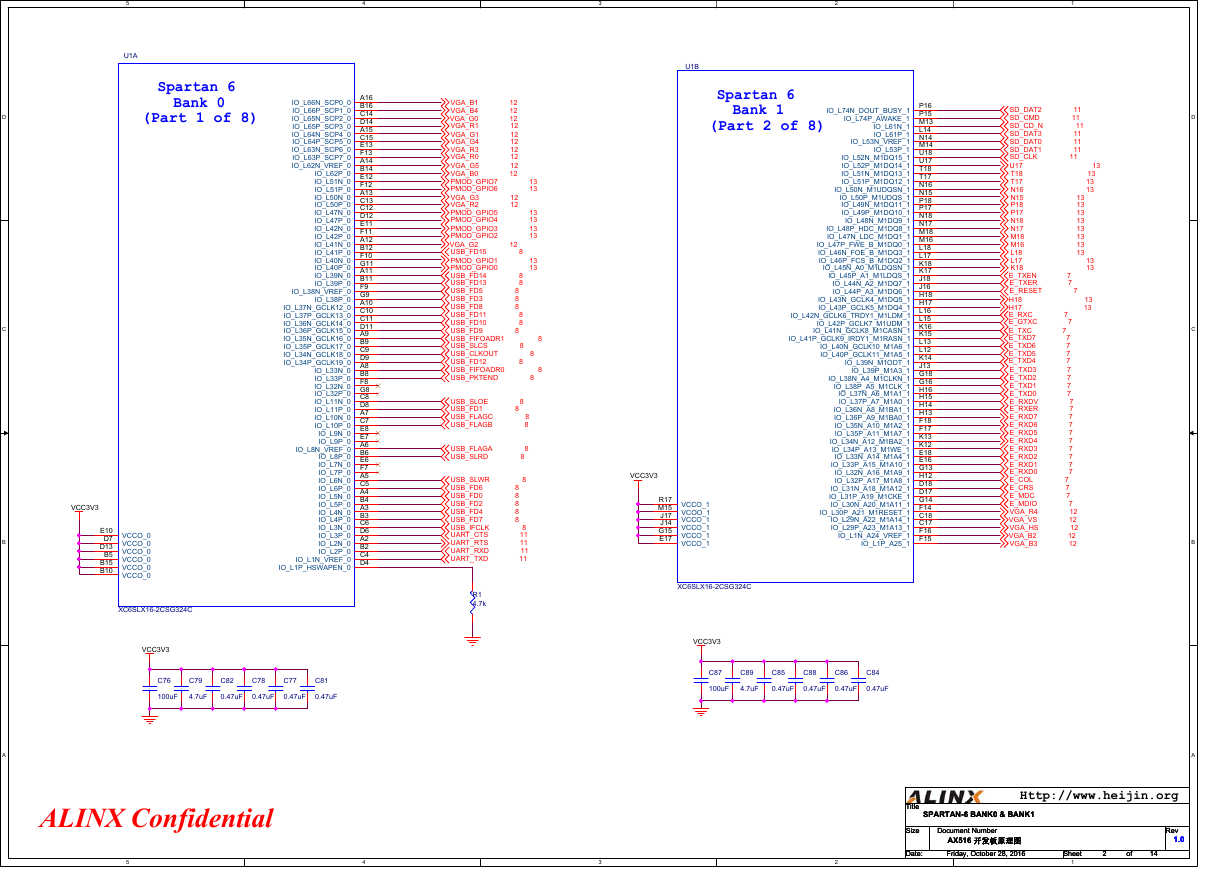

Spartan 6

(Part 2 of 8)

Bank 1

13

13

13

13

13

13

13

13

1

11

11

11

11

11

11

11

13

13

13

13

13

13

13

13

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

12

12

12

12

12

P16

P15

M13

L14

N14

M14

U18

U17

T18

T17

N16

N15

P18

P17

N18

N17

M18

M16

L18

L17

K18

K17

J18

J16

H18

H17

L16

L15

K16

K15

L13

L12

K14

J13

G18

G16

H16

H15

H14

H13

F18

F17

K13

K12

E18

E16

G13

H12

D18

D17

G14

F14

C18

C17

F16

F15

SD_DAT2

SD_CMD

SD_CD_N

SD_DAT3

SD_DAT0

SD_DAT1

SD_CLK

U17

T18

T17

N16

N15

P18

P17

N18

N17

M18

M16

L18

L17

K18

E_TXEN

E_TXER

E_RESET

H18

H17

E_RXC

E_GTXC

E_TXC

E_TXD7

E_TXD6

E_TXD5

E_TXD4

E_TXD3

E_TXD2

E_TXD1

E_TXD0

E_RXDV

E_RXER

E_RXD7

E_RXD6

E_RXD5

E_RXD4

E_RXD3

E_RXD2

E_RXD1

E_RXD0

E_COL

E_CRS

E_MDC

E_MDIO

VGA_R4

VGA_VS

VGA_HS

VGA_B2

VGA_B3

IO_L74N_DOUT_BUSY_1

IO_L74P_AWAKE_1

IO_L61N_1

IO_L61P_1

IO_L53N_VREF_1

IO_L53P_1

IO_L52N_M1DQ15_1

IO_L52P_M1DQ14_1

IO_L51N_M1DQ13_1

IO_L51P_M1DQ12_1

IO_L50N_M1UDQSN_1

IO_L50P_M1UDQS_1

IO_L49N_M1DQ11_1

IO_L49P_M1DQ10_1

IO_L48N_M1DQ9_1

IO_L48P_HDC_M1DQ8_1

IO_L47N_LDC_M1DQ1_1

IO_L47P_FWE_B_M1DQ0_1

IO_L46N_FOE_B_M1DQ3_1

IO_L46P_FCS_B_M1DQ2_1

IO_L45N_A0_M1LDQSN_1

IO_L45P_A1_M1LDQS_1

IO_L44N_A2_M1DQ7_1

IO_L44P_A3_M1DQ6_1

IO_L43N_GCLK4_M1DQ5_1

IO_L43P_GCLK5_M1DQ4_1

IO_L42N_GCLK6_TRDY1_M1LDM_1

IO_L42P_GCLK7_M1UDM_1

IO_L41N_GCLK8_M1CASN_1

IO_L41P_GCLK9_IRDY1_M1RASN_1

IO_L40N_GCLK10_M1A6_1

IO_L40P_GCLK11_M1A5_1

IO_L39N_M1ODT_1

IO_L39P_M1A3_1

IO_L38N_A4_M1CLKN_1

IO_L38P_A5_M1CLK_1

IO_L37N_A6_M1A1_1

IO_L37P_A7_M1A0_1

IO_L36N_A8_M1BA1_1

IO_L36P_A9_M1BA0_1

IO_L35N_A10_M1A2_1

IO_L35P_A11_M1A7_1

IO_L34N_A12_M1BA2_1

IO_L34P_A13_M1WE_1

IO_L33N_A14_M1A4_1

IO_L33P_A15_M1A10_1

IO_L32N_A16_M1A9_1

IO_L32P_A17_M1A8_1

IO_L31N_A18_M1A12_1

IO_L31P_A19_M1CKE_1

IO_L30N_A20_M1A11_1

IO_L30P_A21_M1RESET_1

IO_L29N_A22_M1A14_1

IO_L29P_A23_M1A13_1

IO_L1N_A24_VREF_1

IO_L1P_A25_1

VCC3V3

R17

VCCO_1

M15

VCOO_1

J17

VCCO_1

J14

VCCO_1

G15

E17 VCCO_1

VCCO_1

XC6SLX16-2CSG324C

VCC3V3

4

A16

B16

C14

D14

A15

C15

E13

F13

A14

B14

E12

F12

A13

C13

C12

D12

E11

F11

A12

B12

F10

G11

A11

B11

F9

G9

A10

C10

C11

D11

A9

B9

C9

D9

A8

B8

F8

G8

C8

D8

A7

C7

E8

E7

A6

B6

E6

F7

A5

C5

A4

B4

A3

B3

C6

D6

A2

B2

C4

D4

IO_L66N_SCP0_0

IO_L66P_SCP1_0

IO_L65N_SCP2_0

IO_L65P_SCP3_0

IO_L64N_SCP4_0

IO_L64P_SCP5_0

IO_L63N_SCP6_0

IO_L63P_SCP7_0

IO_L62N_VREF_0

IO_L62P_0

IO_L51N_0

IO_L51P_0

IO_L50N_0

IO_L50P_0

IO_L47N_0

IO_L47P_0

IO_L42N_0

IO_L42P_0

IO_L41N_0

IO_L41P_0

IO_L40N_0

IO_L40P_0

IO_L39N_0

IO_L39P_0

IO_L38N_VREF_0

IO_L38P_0

IO_L37N_GCLK12_0

IO_L37P_GCLK13_0

IO_L36N_GCLK14_0

IO_L36P_GCLK15_0

IO_L35N_GCLK16_0

IO_L35P_GCLK17_0

IO_L34N_GCLK18_0

IO_L34P_GCLK19_0

IO_L33N_0

IO_L33P_0

IO_L32N_0

IO_L32P_0

IO_L11N_0

IO_L11P_0

IO_L10N_0

IO_L10P_0

IO_L9N_0

IO_L9P_0

IO_L8N_VREF_0

IO_L8P_0

IO_L7N_0

IO_L7P_0

IO_L6N_0

IO_L6P_0

IO_L5N_0

IO_L5P_0

IO_L4N_0

IO_L4P_0

IO_L3N_0

IO_L3P_0

IO_L2N_0

IO_L2P_0

IO_L1N_VREF_0

IO_L1P_HSWAPEN_0

5

U1A

Spartan 6

(Part 1 of 8)

Bank 0

VCC3V3

E10

D7 VCCO_0

D13 VCCO_0

B5 VCCO_0

B15 VCCO_0

B10 VCCO_0

VCCO_0

XC6SLX16-2CSG324C

VCC3V3

VGA_B1

VGA_B4

VGA_G0

VGA_R1

VGA_G1

VGA_G4

VGA_R3

VGA_R0

VGA_G5

VGA_B0

PMOD_GPIO7

PMOD_GPIO6

VGA_G3

VGA_R2

PMOD_GPIO5

PMOD_GPIO4

PMOD_GPIO3

PMOD_GPIO2

VGA_G2

USB_FD15

PMOD_GPIO1

PMOD_GPIO0

USB_FD14

USB_FD13

USB_FD5

USB_FD3

USB_FD8

USB_FD11

USB_FD10

USB_FD9

USB_FIFOADR1

USB_SLCS

USB_CLKOUT

USB_FD12

USB_FIFOADR0

USB_PKTEND

12

12

12

12

12

12

12

12

12

12

12

12

12

8

8

8

8

8

8

8

8

8

8

8

13

13

13

13

13

13

13

13

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

11

11

11

11

USB_SLOE

USB_FD1

USB_FLAGC

USB_FLAGB

USB_FLAGA

USB_SLRD

USB_SLWR

USB_FD6

USB_FD0

USB_FD2

USB_FD4

USB_FD7

USB_IFCLK

UART_CTS

UART_RTS

UART_RXD

UART_TXD

R1

4.7k

D

C

B

A

C76

C79

C82

C78

C77

C81

100uF

4.7uF

0.47uF

0.47uF

0.47uF

0.47uF

C87

C89

C85

C88

C86

C84

100uF

4.7uF

0.47uF

0.47uF

0.47uF

0.47uF

ALINX Confidential

5

4

3

2

Http://www.heijin.org

SPARTAN-6 BANK0 & BANK1

SPARTAN-6 BANK0 & BANK1

SPARTAN-6 BANK0 & BANK1

Document Number

Document Number

Document Number

AX516 开发板原理图

AX516 开发板原理图

AX516 开发板原理图

Friday, October 28, 2016

Friday, October 28, 2016

Friday, October 28, 2016

Rev

Rev

Rev

1.0

1.0

1.0

Sheet

Sheet

Sheet

1

2

2

2

of

of

of

14

14

14

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

D

C

B

A

�

4

V2

V3

U3

P6

N5

V4

T4

T3

R3

V5

U5

T5

R5

P7

N6

T7

R7

V6

T6

P8

N7

V7

U7

V8

U8

N8

M8

V9

T9

T8

R8

V10

U10

T10

R10

V11

U11

N9

M10

P11

N10

V12

T12

T11

R11

N11

M11

V13

U13

P12

N12

V14

T14

V15

U15

T13

R13

V16

U16

T15

R15

V17

P13

FPGA_PROG_B

QSPI_CS

FPGA_INT_B

EEPROM_I2C_SCL

EEPROM_I2C_SDA

6

9

9

10

10

9

9

9

9

9

9

9

9

LED4

LED3

LED2

LED1

KEY4

KEY3

KEY2

KEY1

RTC_I2C_SCL

RTC_RESET

RTC_I2C_SDA

IO2_L45N

IO2_L45P

IO2_L44N

IO2_L44P

IO2_L43N

IO2_L43P

IO2_L41N

IO2_L41P

IO2_40N

IO2_40P

IO2_32N_GCLK

IO2_32P_GCLK

IO2_31N_GCLK

IO2_31P_GCLK

FPGA_GCLK1

SMA_CLK

IO2_29N_GCLK

IO2_29P_GCLK

IO2_23N

IO2_23P

IO2_22N

IO2_22P

IO2_20N

IO2_20P

IO2_19N

IO2_19P

IO2_16N

IO2_16P

IO2_15N

IO2_15P

IO2_14N

IO2_14P

10

10

10

13

13

13

13

13

13

6

13

13

13

13

13

13

13

13

13

13

6

13

13

13

13

13

13

13

13

13

13

13

13

13

13

FPGA_M1

FPGA_M0

FPGA_CMPCS_B

QSPI_MISO3

QSPI_MISO2

IO2_5N

IO2_5P

QSPI_MISO0

QSPI_MISO1

IO2_2N

IO2_2P

QSPI_CLK

FPGA_DONE

13

13

13

13

6

6

6

6

6

9

VCCO_2

R7

10k

PROGRAM_B_2

IO_L65N_CSO_B_2

IO_L65P_INIT_B_2

IO_L64N_D9_2

IO_L64P_D8_2

IO_L63N_2

IO_L63P_2

IO_L62N_D6_2

IO_L62P_D5_2

IO_L49N_D4_2

IO_L49P_D3_2

IO_L48N_RDWR_B_VREF_2

IO_L48P_D7_2

IO_L47N_2

IO_L47P_2

IO_L46N_2

IO_L46P_2

IO_L45N_2

IO_L45P_2

IO_L44N_2

IO_L44P_2

IO_L43N_2

IO_L43P_2

IO_L41N_VREF_2

IO_L41P_2

IO_L40N_2

IO_L40P_2

IO_L32N_GCLK28_2

IO_L32P_GCLK29_2

IO_L31N_GCLK30_D15_2

IO_L31P_GCLK31_D14_2

IO_L30N_GCLK0_USERCCLK_2

IO_L30P_GCLK1_D13_2

IO_L29N_GCLK2_2

IO_L29P_GCLK3_2

IO_L23N_2

IO_L23P_2

IO_L22N_2

IO_L22P_2

IO_L20N_2

IO_L20P_2

IO_L19N_2

IO_L19P_2

IO_L16N_VREF_2

IO_L16P_2

IO_L15N_2

IO_L15P_2

IO_L14N_D12_2

IO_L14P_D11_2

IO_L13N_D10_2

IO_L13P_M1_2

IO_L12N_D2_MISO3_2

IO_L12P_D1_MISO2_2

IO_L5N_2

IO_L5P_2

IO_L3N_MOSI_CSI_B_MISO0_2

IO_L3P_D0_DIN_MISO_MISO1_2

IO_L2N_CMPMOSI_2

IO_L2P_CMPCLK_2

IO_L1N_M0_CMPMISO_2

IO_L1P_CCLK_2

DONE_2

CMPCS_B_2

D

C

B

A

IO_L83N_VREF_3

IO_L83P_3

IO_L55N_M3A14_3

IO_L55P_M3A13_3

IO_L54N_M3A11_3

IO_L54P_M3RESET_3

IO_L53N_M3A12_3

IO_L53P_M3CKE_3

IO_L52N_M3A9_3

IO_L52P_M3A8_3

IO_L51N_M3A4_3

IO_L51P_M3A10_3

IO_L50N_M3BA2_3

IO_L50P_M3WE_3

IO_L49N_M3A2_3

IO_L49P_M3A7_3

IO_L48N_M3BA1_3

IO_L48P_M3BA0_3

IO_L47N_M3A1_3

IO_L47P_M3A0_3

IO_L46N_M3CLKN_3

IO_L46P_M3CLK_3

IO_L45N_M3ODT_3

IO_L45P_M3A3_3

IO_L44N_GCLK20_M3A6_3

IO_L44P_GCLK21_M3A5_3

IO_L43N_GCLK22_IRDY2_M3CASN_3

IO_L43P_GCLK23_M3RASN_3

IO_L42N_GCLK24_M3LDM_3

IO_L42P_GCLK25_TRDY2_M3UDM_3

IO_L41N_GCLK26_M3DQ5_3

IO_L41P_GCLK27_M3DQ4_3

IO_L40N_M3DQ7_3

IO_L40P_M3DQ6_3

IO_L39N_M3LDQSN_3

IO_L39P_M3LDQS_3

IO_L38N_M3DQ3_3

IO_L38P_M3DQ2_3

IO_L37N_M3DQ1_3

IO_L37P_M3DQ0_3

IO_L36N_M3DQ9_3

IO_L36P_M3DQ8_3

IO_L35N_M3DQ11_3

IO_L35P_M3DQ10_3

IO_L34N_M3UDQSN_3

IO_L34P_M3UDQS_3

IO_L33N_M3DQ13_3

IO_L33P_M3DQ12_3

IO_L32N_M3DQ15_3

IO_L32P_M3DQ14_3

IO_L31N_VREF_3

IO_L31P_3

IO_L2N_3

IO_L2P_3

IO_L1N_VREF_3

IO_L1P_3

C1

C2

F5

F6

D3

E4

G6

H7

D1

D2

F3

F4

E1

E3

H5

H6

F1

F2

J6

J7

G1

G3

K6

L7

H3

H4

K5

L5

K3

K4

H1

H2

J1

J3

L3

L4

K1

K2

L1

L2

M1

M3

N1

N2

P1

P2

T1

T2

U1

U2

M5

L6

P3

P4

N3

N4

FPGA_ONCHIP_TERM2

DDR3_A14

DDR3_A13

DDR3_A11

DDR3_RESET_N

DDR3_A12

DDR3_CKE

DDR3_A9

DDR3_A8

DDR3_A4

DDR3_A10

DDR3_BA2

DDR3_WE_N

DDR3_A2

DDR3_A7

DDR3_BA1

DDR3_BA0

DDR3_A1

DDR3_A0

DDR3_CLK_N

DDR3_CLK_P

DDR3_ODT

DDR3_A3

DDR3_A6

DDR3_A5

DDR3_CAS_N

DDR3_RAS_N

DDR3_LDM

DDR3_UDM

DDR3_DQ5

DDR3_DQ4

DDR3_DQ7

DDR3_DQ6

DDR3_LDQS_N

DDR3_LDQS_P

DDR3_DQ3

DDR3_DQ2

DDR3_DQ1

DDR3_DQ0

DDR3_DQ9

DDR3_DQ8

DDR3_DQ11

DDR3_DQ10

DDR3_UDQS_N

DDR3_UDQS_P

DDR3_DQ13

DDR3_DQ12

DDR3_DQ15

DDR3_DQ14

FPGA_ONCHIP_TERM1

CPU_RESET

5

5

5

5

5

5

5

5

5

5

D

R3

5

100R

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

9

R8

OTM

VCC1V5

C

R4

OTM_10k

DDR3_VREF

C1

0.1uF

R5

OTM_10k

1%

VCC1V5

R145

100R

B

A

5

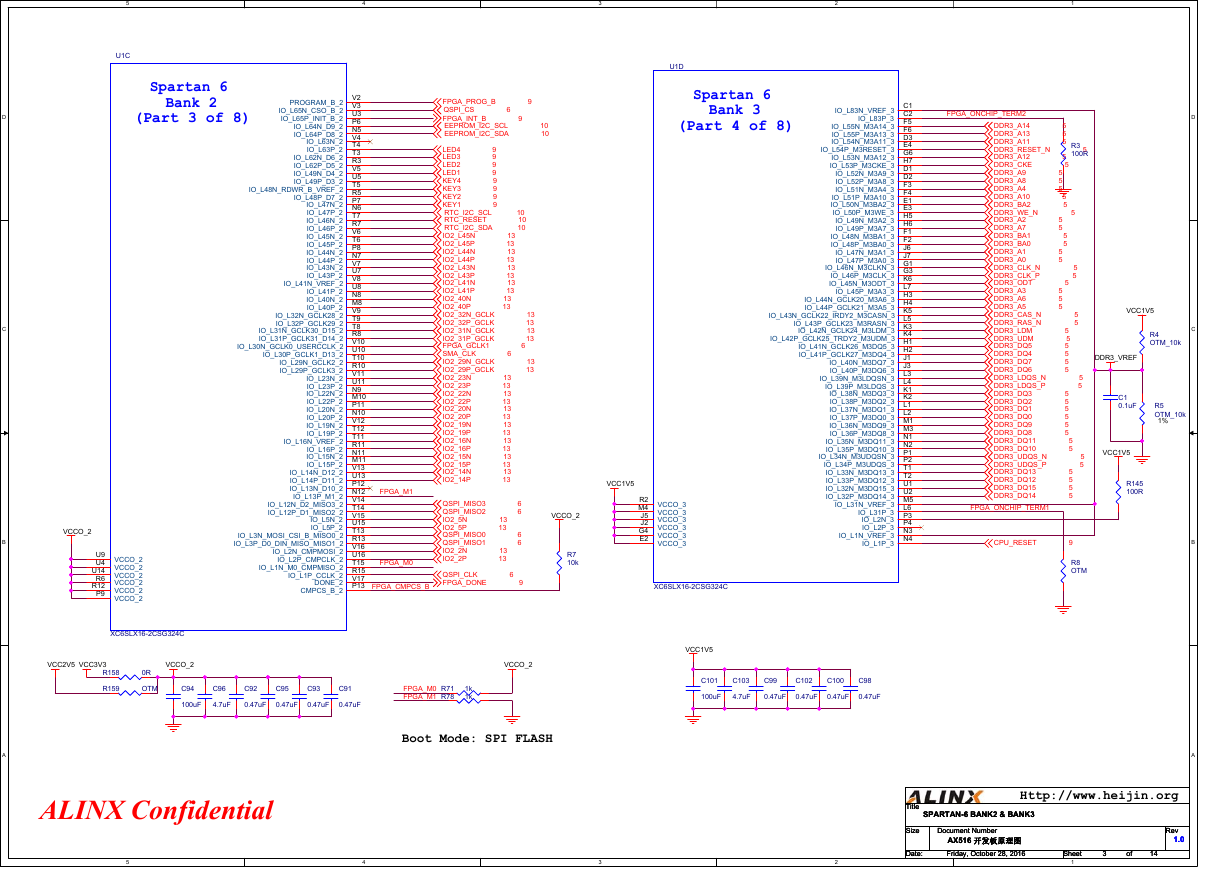

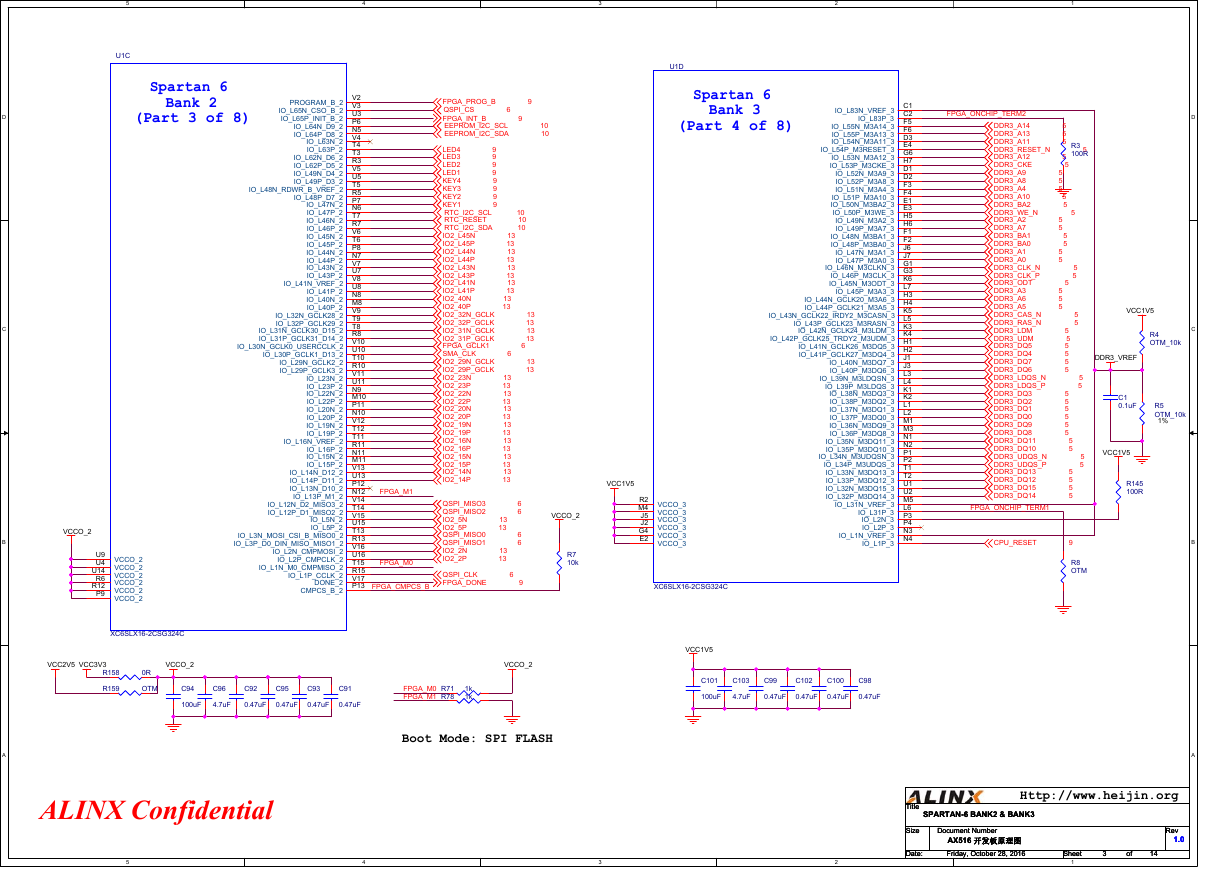

U1C

Spartan 6

(Part 3 of 8)

Bank 2

3

2

1

U1D

Spartan 6

(Part 4 of 8)

Bank 3

VCCO_2

U9

VCCO_2

U4

VCCO_2

U14

VCCO_2

R6

VCCO_2

R12

P9 VCCO_2

VCCO_2

XC6SLX16-2CSG324C

VCC1V5

R2

VCCO_3

M4

VCCO_3

J5

VCCO_3

J2

G4 VCCO_3

E2 VCCO_3

VCCO_3

XC6SLX16-2CSG324C

VCC1V5

VCC2V5

VCC3V3

R158

R159

0R

OTM

VCCO_2

VCCO_2

C94

C96

C92

C95

C93

C91

100uF

4.7uF

0.47uF

0.47uF

0.47uF

0.47uF

FPGA_M0

FPGA_M1

R71

R78

1k

1k

C101

C103

C99

C102

C100

C98

100uF

4.7uF

0.47uF

0.47uF

0.47uF

0.47uF

Boot Mode: SPI FLASH

ALINX Confidential

5

4

3

2

Http://www.heijin.org

SPARTAN-6 BANK2 & BANK3

SPARTAN-6 BANK2 & BANK3

SPARTAN-6 BANK2 & BANK3

Document Number

Document Number

Document Number

AX516 开发板原理图

AX516 开发板原理图

AX516 开发板原理图

Friday, October 28, 2016

Friday, October 28, 2016

Friday, October 28, 2016

Rev

Rev

Rev

1.0

1.0

1.0

Sheet

Sheet

Sheet

1

3

3

3

of

of

of

14

14

14

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

�

D

C

B

A

5

4

3

2

1

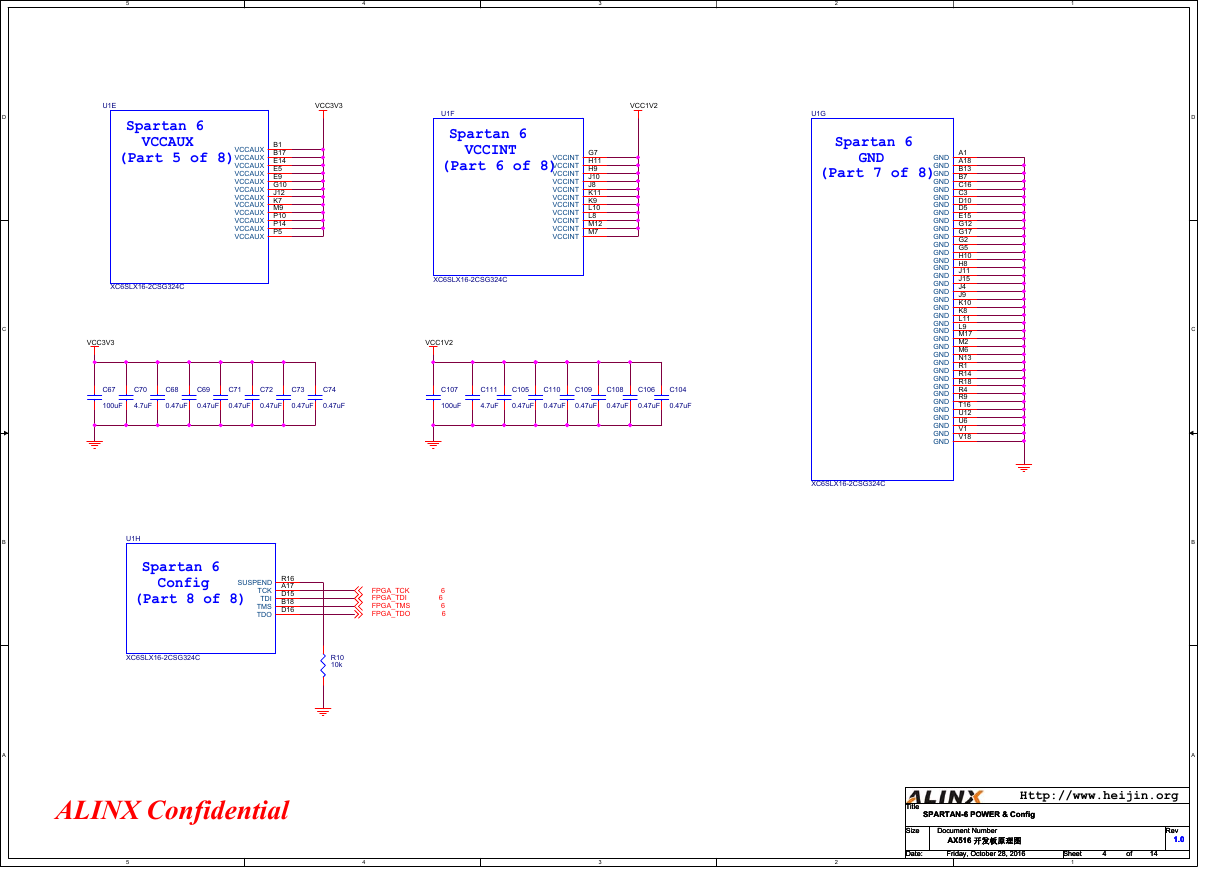

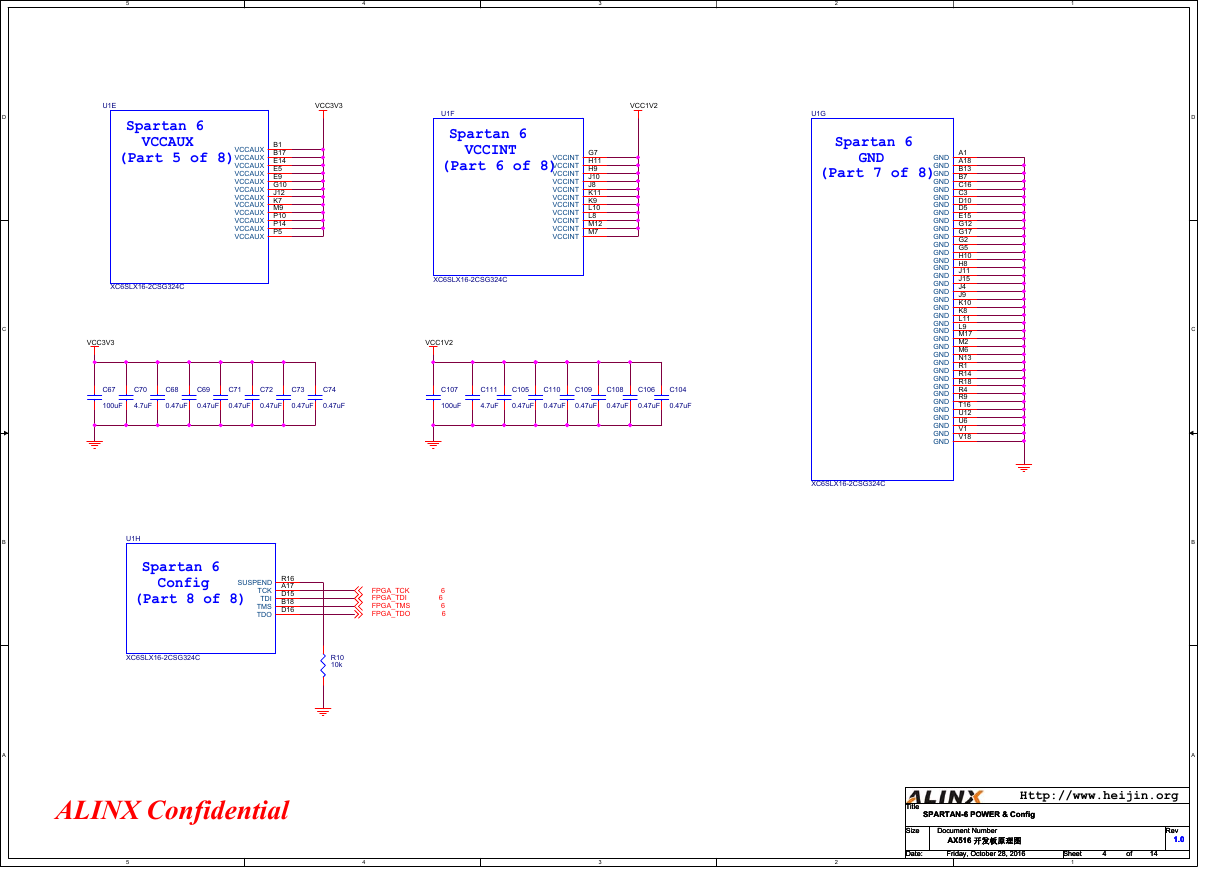

U1E

Spartan 6

(Part 5 of 8)

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCC3V3

B1

B17

E14

E5

E9

G10

J12

K7

M9

P10

P14

P5

U1F

Spartan 6

(Part 6 of 8)

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

G7

H11

H9

J10

J8

K11

K9

L10

L8

M12

M7

XC6SLX16-2CSG324C

XC6SLX16-2CSG324C

VCC3V3

VCC1V2

C67

C70

C68

C69

C71

C72

C73

C74

100uF

4.7uF

0.47uF

0.47uF

0.47uF

0.47uF

0.47uF

0.47uF

C107

100uF

C111

C105

C110

C109

C108

C106

C104

4.7uF

0.47uF

0.47uF

0.47uF

0.47uF

0.47uF

0.47uF

U1H

XC6SLX16-2CSG324C

Spartan 6

(Part 8 of 8)

Config

SUSPEND

TCK

TDI

TMS

TDO

R16

A17

D15

B18

D16

FPGA_TCK

FPGA_TDI

FPGA_TMS

FPGA_TDO

6

6

6

6

VCC1V2

U1G

Spartan 6

(Part 7 of 8)

GND

A1

A18

B13

B7

C16

C3

D10

D5

E15

G12

G17

G2

G5

H10

H8

J11

J15

J4

J9

K10

K8

L11

L9

M17

M2

M6

N13

R1

R14

R18

R4

R9

T16

U12

U6

V1

V18

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

XC6SLX16-2CSG324C

R10

10k

ALINX Confidential

5

4

3

2

Http://www.heijin.org

SPARTAN-6 POWER & Config

SPARTAN-6 POWER & Config

SPARTAN-6 POWER & Config

Document Number

Document Number

Document Number

AX516 开发板原理图

AX516 开发板原理图

AX516 开发板原理图

Friday, October 28, 2016

Friday, October 28, 2016

Friday, October 28, 2016

Rev

Rev

Rev

1.0

1.0

1.0

Sheet

Sheet

Sheet

1

4

4

4

of

of

of

14

14

14

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

D

C

B

A

�

D

C

B

A

5

4

3

2

1

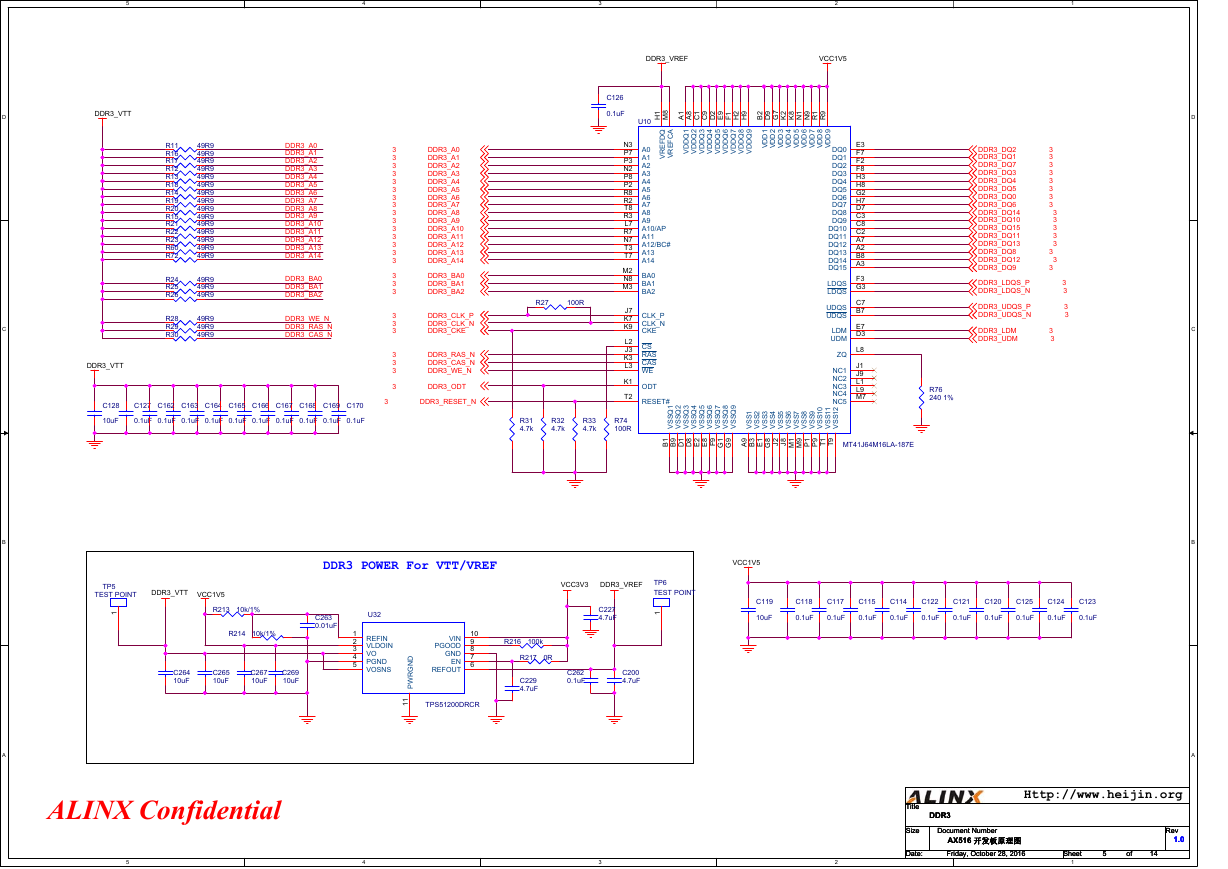

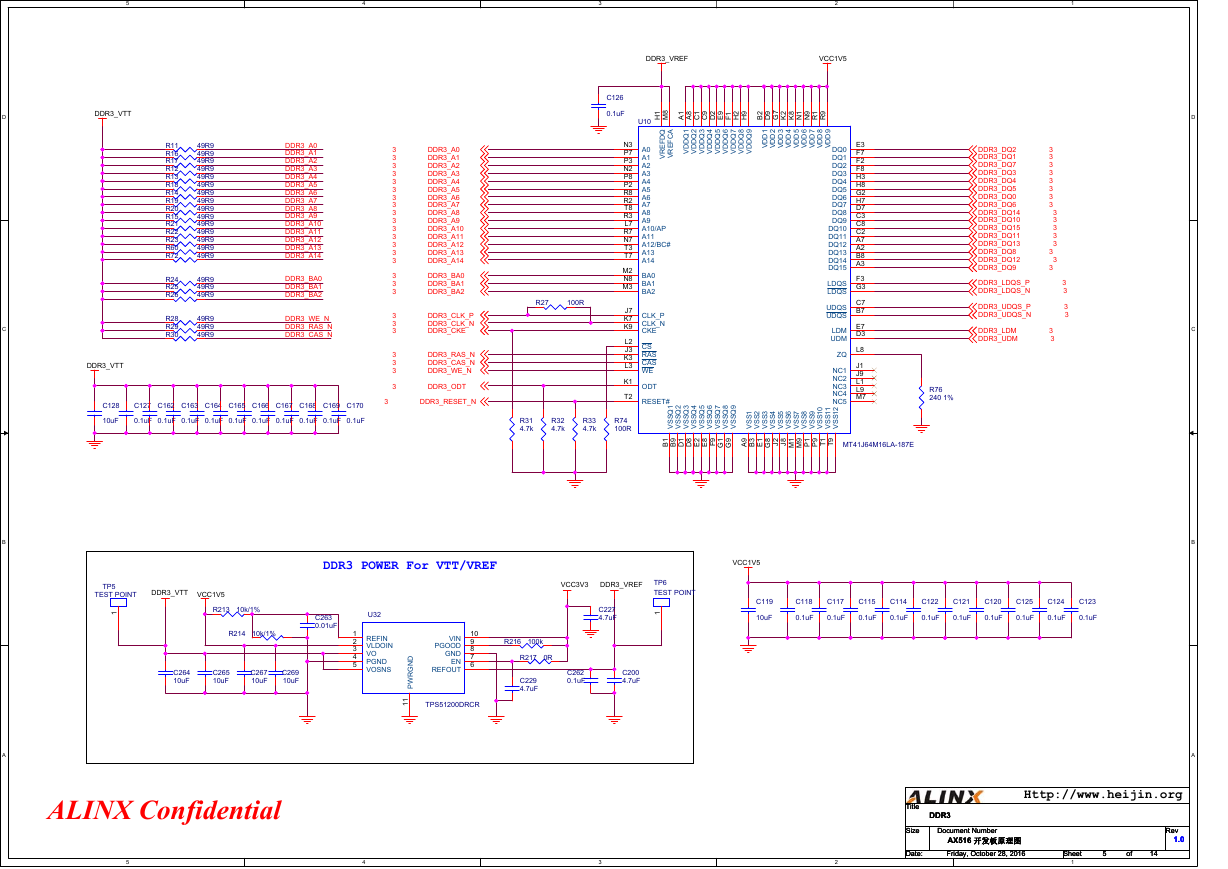

DDR3_VREF

VCC1V5

DDR3_VTT

DDR3_VTT

C128

10uF

R11

R16

R17

R12

R13

R18

R14

R19

R20

R15

R21

R22

R23

R60

R72

R24

R25

R26

R28

R29

R30

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

49R9

DDR3_A0

DDR3_A1

DDR3_A2

DDR3_A3

DDR3_A4

DDR3_A5

DDR3_A6

DDR3_A7

DDR3_A8

DDR3_A9

DDR3_A10

DDR3_A11

DDR3_A12

DDR3_A13

DDR3_A14

DDR3_BA0

DDR3_BA1

DDR3_BA2

DDR3_WE_N

DDR3_RAS_N

DDR3_CAS_N

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

DDR3_A0

DDR3_A1

DDR3_A2

DDR3_A3

DDR3_A4

DDR3_A5

DDR3_A6

DDR3_A7

DDR3_A8

DDR3_A9

DDR3_A10

DDR3_A11

DDR3_A12

DDR3_A13

DDR3_A14

DDR3_BA0

DDR3_BA1

DDR3_BA2

DDR3_CLK_P

DDR3_CLK_N

DDR3_CKE

DDR3_RAS_N

DDR3_CAS_N

DDR3_WE_N

DDR3_ODT

C127

C162

C163

C164

C165

C166

C167

C168

C169

C170

3

DDR3_RESET_N

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

C126

0.1uF

1

H

8

M

U10

1

A

8

A

1

C

9

C

2

D

9

E

1

F

2

H

9

H

2

B

9

D

7

G

2

K

8

K

1

N

9

N

1

R

9

R

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

M2

N8

M3

J7

K7

K9

L2

J3

K3

L3

K1

T2

R27

100R

R31

4.7k

R32

4.7k

R33

4.7k

R74

100R

1

Q

D

D

V

2

Q

D

D

V

3

Q

D

D

V

4

Q

D

D

V

5

Q

D

D

V

6

Q

D

D

V

7

Q

D

D

V

8

Q

D

D

V

9

Q

D

D

V

Q

D

F

E

R

V

A

C

F

E

R

V

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

A14

BA0

BA1

BA2

CLK_P

CLK_N

CKE

CS

RAS

CAS

WE

ODT

RESET#

1

Q

S

S

V

2

Q

S

S

V

3

Q

S

S

V

4

Q

S

S

V

5

Q

S

S

V

6

Q

S

S

V

7

Q

S

S

V

8

Q

S

S

V

9

Q

S

S

V

1

B

9

B

1

D

8

D

2

E

8

E

9

F

1

G

9

G

1

D

D

V

2

D

D

V

3

D

D

V

4

D

D

V

5

D

D

V

6

D

D

V

7

D

D

V

8

D

D

V

9

D

D

V

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

LDQS

LDQS

UDQS

UDQS

LDM

UDM

ZQ

NC1

NC2

NC3

NC4

NC5

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

F3

G3

C7

B7

E7

D3

L8

J1

J9

L1

L9

M7

DDR3_DQ2

DDR3_DQ1

DDR3_DQ7

DDR3_DQ3

DDR3_DQ4

DDR3_DQ5

DDR3_DQ0

DDR3_DQ6

DDR3_DQ14

DDR3_DQ10

DDR3_DQ15

DDR3_DQ11

DDR3_DQ13

DDR3_DQ8

DDR3_DQ12

DDR3_DQ9

DDR3_LDQS_P

DDR3_LDQS_N

DDR3_UDQS_P

DDR3_UDQS_N

DDR3_LDM

DDR3_UDM

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

R76

240 1%

1

S

S

V

2

S

S

V

3

S

S

V

4

S

S

V

5

S

S

V

6

S

S

V

7

S

S

V

8

S

S

V

9

S

S

V

0

1

S

S

V

1

1

S

S

V

2

1

S

S

V

9

A

3

B

1

E

8

G

2

J

8

J

1

M

9

M

1

P

9

P

1

T

9

T

MT41J64M16LA-187E

DDR3 POWER For VTT/VREF

VCC1V5

TP5

TEST POINT

1

DDR3_VTT

VCC1V5

R213 10k/1%

R214 10k/1%

C263

0.01uF

C264

10uF

C265

10uF

C267

10uF

C269

10uF

U32

REFIN

VLDOIN

VO

PGND

VOSNS

1

2

3

4

5

D

N

G

R

W

P

VIN

PGOOD

GND

EN

REFOUT

10

9

8

7

6

1

1

TPS51200DRCR

VCC3V3

DDR3_VREF

TP6

TEST POINT

C227

4.7uF

1

R216 100k

R217 0R

C229

4.7uF

C262

0.1uF

C200

4.7uF

C119

10uF

C118

C117

C115

C114

C122

C121

C120

C125

C124

C123

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

ALINX Confidential

5

4

3

2

Http://www.heijin.org

DDR3

DDR3

DDR3

Document Number

Document Number

Document Number

AX516 开发板原理图

AX516 开发板原理图

AX516 开发板原理图

Friday, October 28, 2016

Friday, October 28, 2016

Friday, October 28, 2016

Rev

Rev

Rev

1.0

1.0

1.0

Sheet

Sheet

Sheet

1

5

5

5

of

of

of

14

14

14

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

D

C

B

A

�

5

4

3

2

1

VCC3V3

VCC3V3

R66

1k

R63

1k

R89

OTM

R64

1k

C15

0.1uF

U4

VCC3V3

R92

1k

3

3

3

QSPI_MISO3

QSPI_CS

QSPI_MISO1

R62

33R

1

2

3

4

5

6

7

8

IO3_HOLD_B

VCC

/RESET

NC1

NC2

NC3

CS_B

IO1_DOUT

CLK

IO0_DIN

NC7

NC6

NC5

NC4

GND

/WP_IO2

16

15

14

13

12

11

10

9

W25Q128FVFIG

QSPI FLASH

QSPI_CLK

QSPI_MISO0

3

3

R90 33R

QSPI_MISO2

3

VCC3V3

J5

1

3

5

7

9

11

13

2

4

6

8

10

12

14

HEADER 7x2/SM

R118

R119

R120

R121

33R

33R

33R

33R

FPGA_TMS

FPGA_TCK

FPGA_TDO

FPGA_TDI

4

4

4

4

JTAG Connector

VCC3V3

L6

BEAD

R75

10k

C16

0.1uF

C17

4.7uF

4

3

J27

4

1

X1

VDD

OUT

OE

GND

OSC 50Mhz

3

2

R73

33R

FPGA_GCLK1

3

1

R108

33R

SMA_CLK

3

5

2

MSA Connector

CLOCK

D

C

B

A

D

C

B

A

ALINX Confidential

5

4

3

2

Http://www.heijin.org

Flash, Clock, JTAG

Flash, Clock, JTAG

Flash, Clock, JTAG

Document Number

Document Number

Document Number

AX516 开发板原理图

AX516 开发板原理图

AX516 开发板原理图

Friday, October 28, 2016

Friday, October 28, 2016

Friday, October 28, 2016

Rev

Rev

Rev

1.0

1.0

1.0

Sheet

Sheet

Sheet

1

6

6

6

of

of

of

14

14

14

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

�

D

C

B

A

5

4

3

2

1

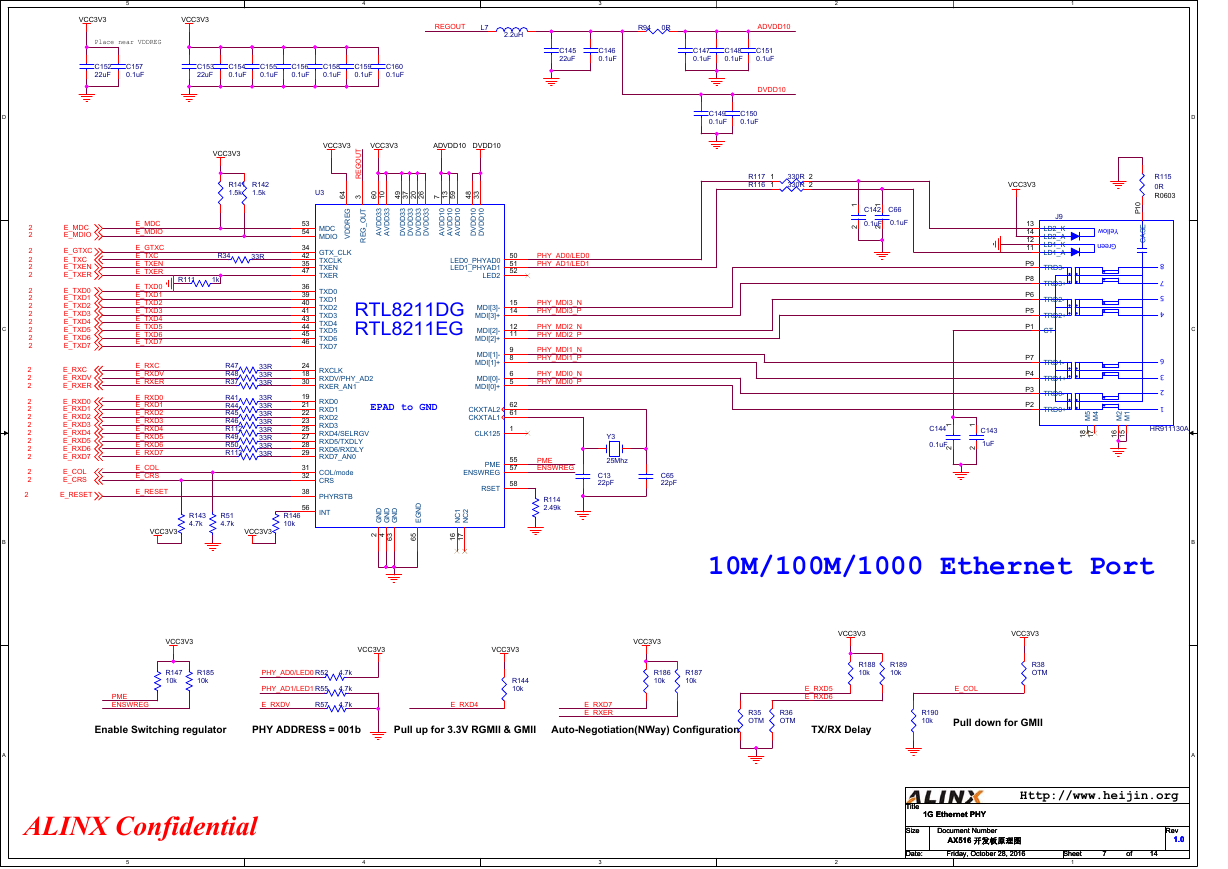

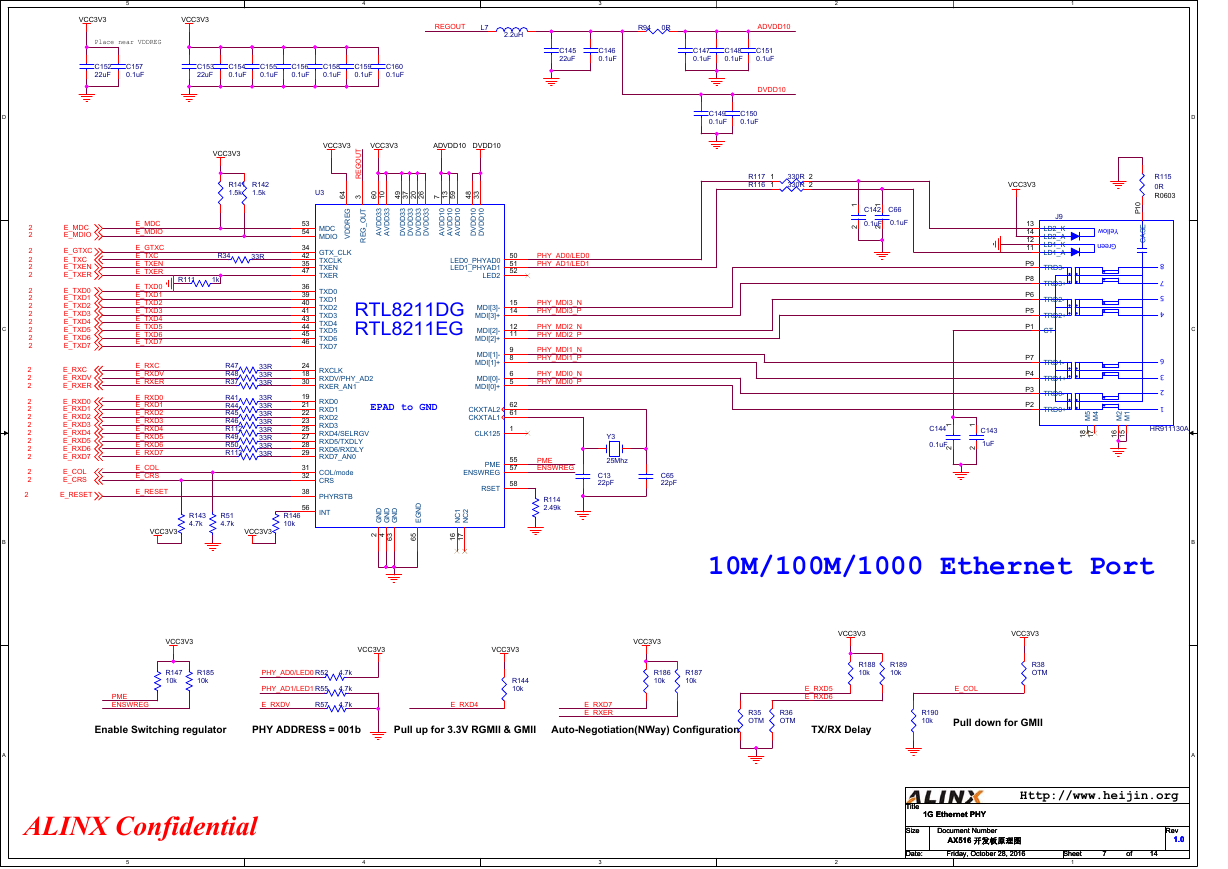

VCC3V3

VCC3V3

Place near VDDREG

C152

22uF

C157

0.1uF

C153

22uF

C154

0.1uF

C155

0.1uF

C156

0.1uF

C158

0.1uF

C159

0.1uF

C160

0.1uF

REGOUT

L7

2.2uH

R94

0R

ADVDD10

C145

22uF

C146

0.1uF

C147

0.1uF

C148

0.1uF

C151

0.1uF

VCC3V3

ADVDD10 DVDD10

VCC3V3

T

U

O

G

E

R

U3

4

6

3

0

6

0

1

G

E

R

D

D

V

T

U

O

_

G

E

R

3

3

D

D

V

A

3

3

D

D

V

A

MDC

MDIO

9

4

7

3

0

2

6

2

3

1

9

5

7

3

3

D

D

V

D

3

3

D

D

V

D

3

3

D

D

V

D

3

3

D

D

V

D

0

1

D

D

V

A

0

1

D

D

V

A

0

1

D

D

V

A

8

4

3

3

0

1

D

D

V

D

0

1

D

D

V

D

1

2

1

C142

0.1uF

2

DVDD10

C149

0.1uF

C150

0.1uF

R117

R116

1

1

330R 2

330R 2

VCC3V3

VCC3V3

R141

1.5k

R142

1.5k

R34

33R

R111

1k

R47

R48

R37

R41

R44

R45

R46

R112

R49

R50

R113

33R

33R

33R

33R

33R

33R

33R

33R

33R

33R

33R

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

E_MDC

E_MDIO

E_GTXC

E_TXC

E_TXEN

E_TXER

E_TXD0

E_TXD1

E_TXD2

E_TXD3

E_TXD4

E_TXD5

E_TXD6

E_TXD7

E_RXC

E_RXDV

E_RXER

E_RXD0

E_RXD1

E_RXD2

E_RXD3

E_RXD4

E_RXD5

E_RXD6

E_RXD7

E_COL

E_CRS

E_MDC

E_MDIO

E_GTXC

E_TXC

E_TXEN

E_TXER

E_TXD0

E_TXD1

E_TXD2

E_TXD3

E_TXD4

E_TXD5

E_TXD6

E_TXD7

E_RXC

E_RXDV

E_RXER

E_RXD0

E_RXD1

E_RXD2

E_RXD3

E_RXD4

E_RXD5

E_RXD6

E_RXD7

E_COL

E_CRS

2

E_RESET

E_RESET

R143

4.7k

R51

4.7k

R146

10k

VCC3V3

VCC3V3

53

54

34

42

35

47

36

39

40

41

43

44

45

46

24

18

30

19

21

22

23

25

27

28

29

31

32

38

56

GTX_CLK

TXCLK

TXEN

TXER

TXD0

TXD1

TXD2

TXD3

TXD4

TXD5

TXD6

TXD7

RXCLK

RXDV/PHY_AD2

RXER_AN1

RXD0

RXD1

RXD2

RXD3

RXD4/SELRGV

RXD5/TXDLY

RXD6/RXDLY

RXD7_AN0

COL/mode

CRS

PHYRSTB

INT

RTL8211DG

RTL8211EG

LED0_PHYAD0

LED1_PHYAD1

LED2

MDI[3]-

MDI[3]+

MDI[2]-

MDI[2]+

MDI[1]-

MDI[1]+

MDI[0]-

MDI[0]+

EPAD to GND

CKXTAL2

CKXTAL1

CLK125

PME

ENSWREG

RSET

D

N

G

D

N

G

D

N

G

2

4

3

6

D

N

G

E

1

C

N

2

C

N

5

6

6

1

7

1

50

51

52

15

14

12

11

9

8

6

5

62

61

1

55

57

58

PHY_AD0/LED0

PHY_AD1/LED1

PHY_MDI3_N

PHY_MDI3_P

PHY_MDI2_N

PHY_MDI2_P

PHY_MDI1_N

PHY_MDI1_P

PHY_MDI0_N

PHY_MDI0_P

PME

ENSWREG

R114

2.49k

Y3

25Mhz

C13

22pF

C65

22pF

C66

0.1uF

13

14

12

11

P9

P8

P6

P5

P1

P7

P4

P3

P2

J9

LD2_K

LD2_A

LD1_K

LD1_A

TRD3-

TRD3+

TRD2-

TRD2+

CT

TRD1-

TRD1+

TRD0-

TRD0+

1

C144

0.1uF

2

1

2

C143

1uF

R115

0R

R0603

0

1

P

E

S

A

C

Yellow

Green

8

7

5

4

6

3

2

1

HR911130A

5

M

4

M

2

M

1

M

8

1

7

1

6

1

5

1

10M/100M/1000 Ethernet Port

VCC3V3

R147

10k

R185

10k

PME

ENSWREG

PHY_AD0/LED0

R52

PHY_AD1/LED1

R55

E_RXDV

R57

4.7k

4.7k

4.7k

VCC3V3

VCC3V3

R144

10k

E_RXD4

E_RXD7

E_RXER

VCC3V3

R186

10k

R187

10k

Enable Switching regulator

PHY ADDRESS = 001b

Pull up for 3.3V RGMII & GMII

Auto-Negotiation(NWay) Configuration

VCC3V3

R188

10k

R189

10k

VCC3V3

R38

OTM

E_RXD5

E_RXD6

E_COL

R35

OTM

R36

OTM

TX/RX Delay

R190

10k

Pull down for GMII

ALINX Confidential

5

4

3

2

Http://www.heijin.org

1G Ethernet PHY

1G Ethernet PHY

1G Ethernet PHY

Document Number

Document Number

Document Number

AX516 开发板原理图

AX516 开发板原理图

AX516 开发板原理图

Friday, October 28, 2016

Friday, October 28, 2016

Friday, October 28, 2016

Rev

Rev

Rev

1.0

1.0

1.0

Sheet

Sheet

Sheet

1

7

7

7

of

of

of

14

14

14

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

D

C

B

A

�

D

C

B

A

5

4

3

2

1

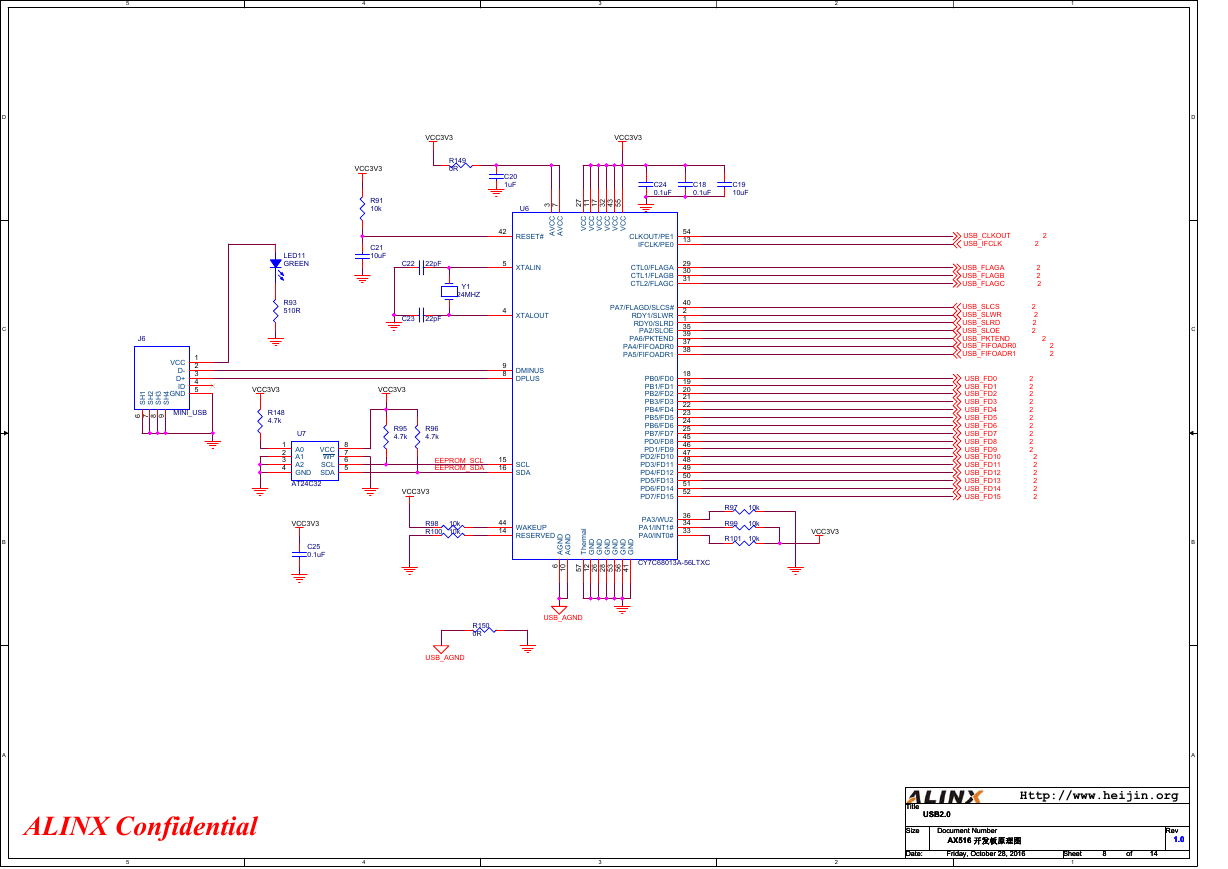

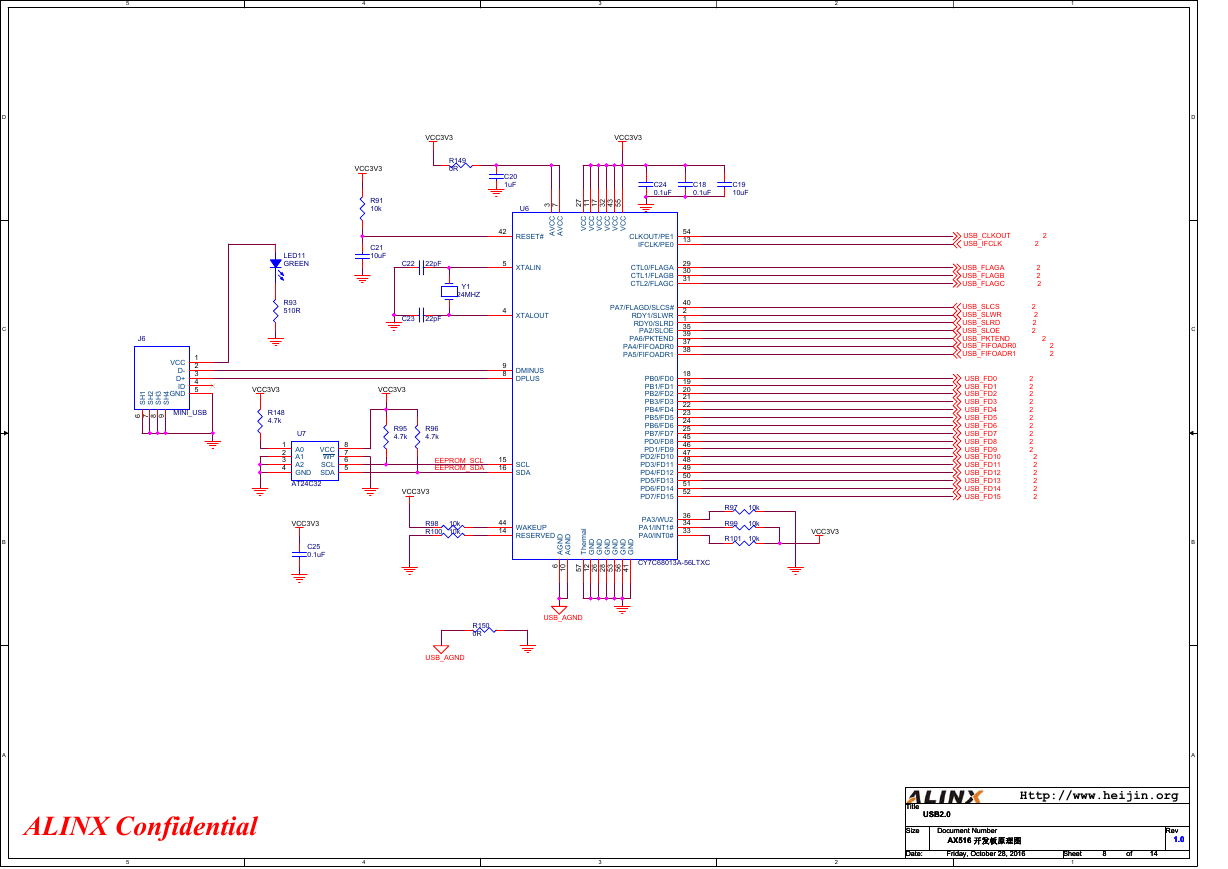

VCC3V3

R91

10k

C21

10uF

VCC3V3

R149

0R

C22

22pF

C23

22pF

Y1

24MHZ

C20

1uF

U6

3

7

42

RESET#

C

C

V

A

C

C

V

A

5

4

XTALIN

XTALOUT

9

8 DMINUS

DPLUS

VCC3V3

R95

4.7k

R96

4.7k

EEPROM_SCL

EEPROM_SDA

15

16

SCL

SDA

VCC3V3

R98

10k

R100 10k

44

14

WAKEUP

RESERVED

D

N

G

A

D

N

G

A

6

0

1

LED11

GREEN

R93

510R

VCC3V3

R148

4.7k

U7

1

2

3

4

VCC

WP

SCL

SDA

A0

A1

A2

GND

AT24C32

8

7

6

5

VCC3V3

C25

0.1uF

J6

VCC

D-

D+

ID

GND

1

H

S

2

H

S

3

H

S

4

H

S

1

2

3

4

5

6

7

8

9

MINI_USB

VCC3V3

C24

0.1uF

C18

0.1uF

C19

10uF

7

2

1

1

7

1

2

3

3

4

5

5

C

C

V

C

C

V

C

C

V

C

C

V

C

C

V

C

C

V

CLKOUT/PE1

IFCLK/PE0

CTL0/FLAGA

CTL1/FLAGB

CTL2/FLAGC

PA7/FLAGD/SLCS#

RDY1/SLWR

RDY0/SLRD

PA2/SLOE

PA6/PKTEND

PA4/FIFOADR0

PA5/FIFOADR1

PB0/FD0

PB1/FD1

PB2/FD2

PB3/FD3

PB4/FD4

PB5/FD5

PB6/FD6

PB7/FD7

PD0/FD8

PD1/FD9

PD2/FD10

PD3/FD11

PD4/FD12

PD5/FD13

PD6/FD14

PD7/FD15

PA3/WU2

PA1/INT1#

PA0/INT0#

l

a

m

r

e

h

T

D

N

G

D

N

G

D

N

G

D

N

G

D

N

G

D

N

G

54

13

29

30

31

40

2

1

35

39

37

38

18

19

20

21

22

23

24

25

45

46

47

48

49

50

51

52

36

34

33

R97

R99

10k

10k

R101 10k

VCC3V3

USB_CLKOUT

USB_IFCLK

2

2

USB_FLAGA

USB_FLAGB

USB_FLAGC

USB_SLCS

USB_SLWR

USB_SLRD

USB_SLOE

USB_PKTEND

USB_FIFOADR0

USB_FIFOADR1

2

2

2

2

2

2

2

2

2

2

USB_FD0

USB_FD1

USB_FD2

USB_FD3

USB_FD4

USB_FD5

USB_FD6

USB_FD7

USB_FD8

USB_FD9

USB_FD10

USB_FD11

USB_FD12

USB_FD13

USB_FD14

USB_FD15

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

7

5

2

1

6

2

8

2

3

5

6

5

1

4

CY7C68013A-56LTXC

USB_AGND

R150

0R

USB_AGND

ALINX Confidential

5

4

3

2

Http://www.heijin.org

USB2.0

USB2.0

USB2.0

Document Number

Document Number

Document Number

AX516 开发板原理图

AX516 开发板原理图

AX516 开发板原理图

Friday, October 28, 2016

Friday, October 28, 2016

Friday, October 28, 2016

Rev

Rev

Rev

1.0

1.0

1.0

Sheet

Sheet

Sheet

1

8

8

8

of

of

of

14

14

14

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

D

C

B

A

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc