FPGA学习之Cyclone器件资源结构知识介绍

因为下周将进行RAM核调用及系统设计学习,这周结束我就先参考Cyclone IV器件手册,来学习FP

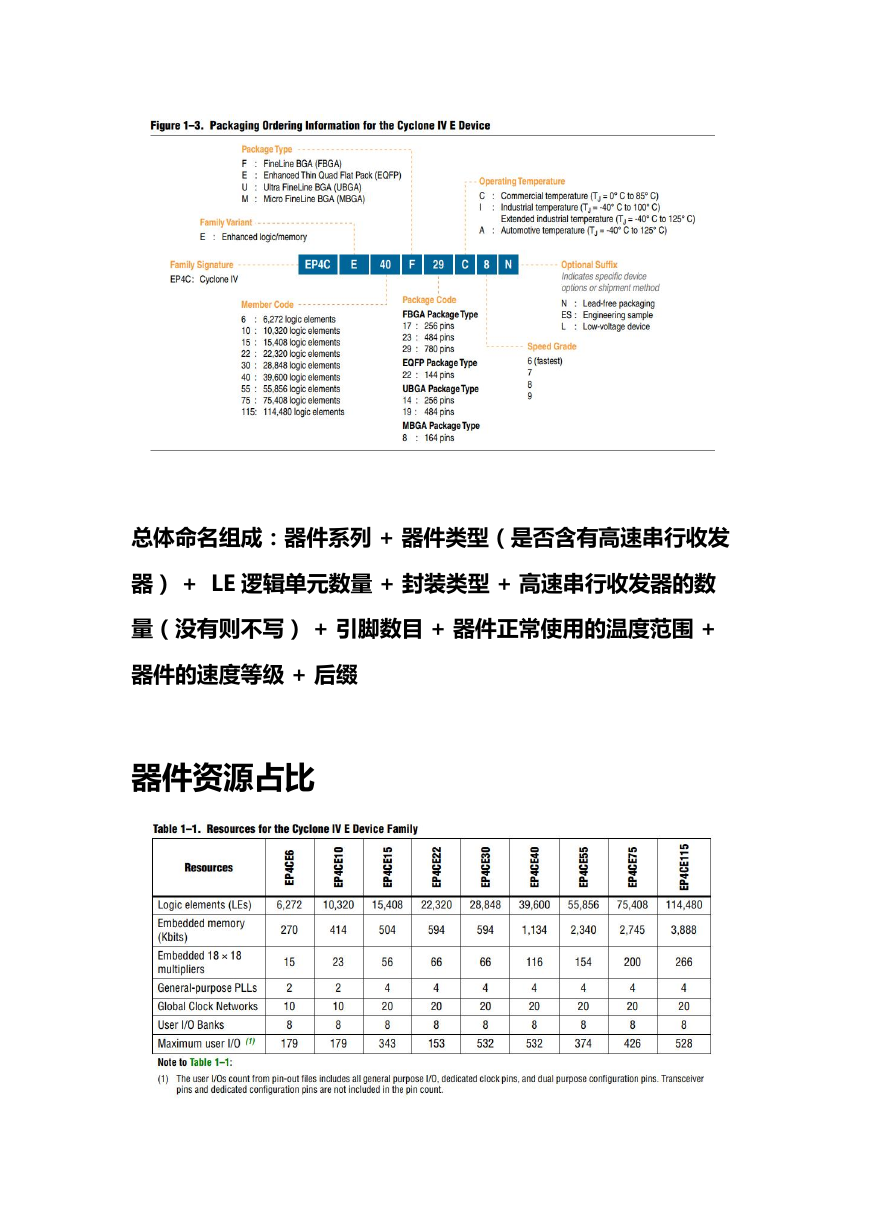

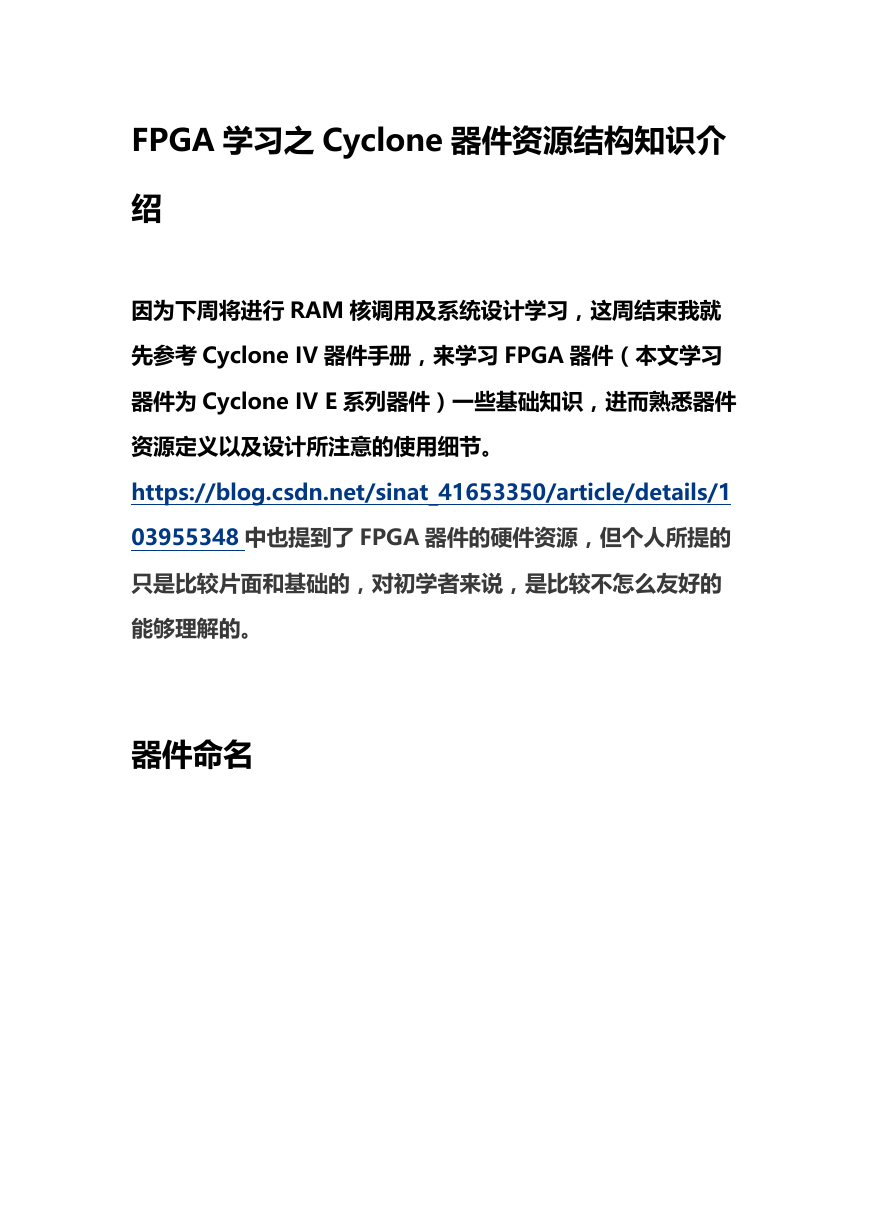

器件命名

总体命名组成:器件系列 + 器件类型(是否含有高速串行收发器) + LE逻辑单元数量 + 封装类型

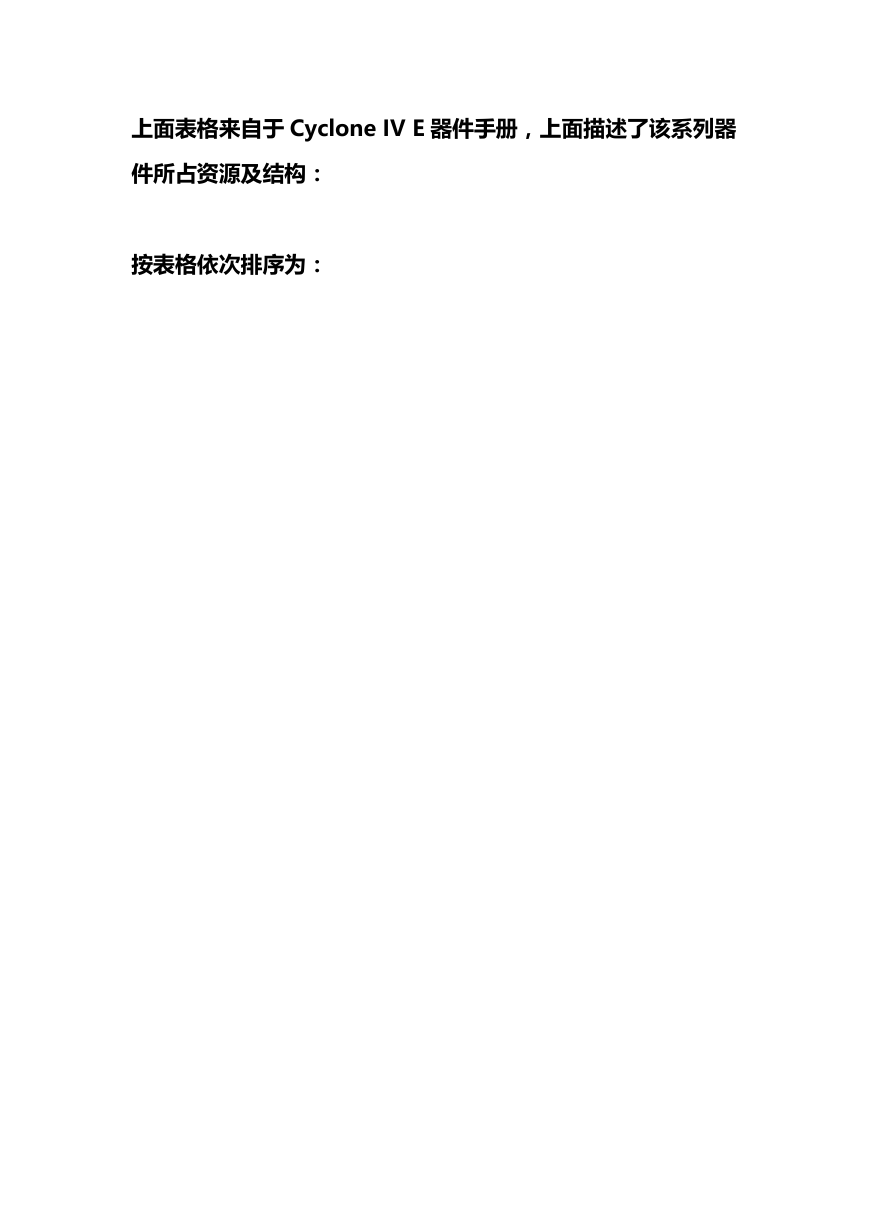

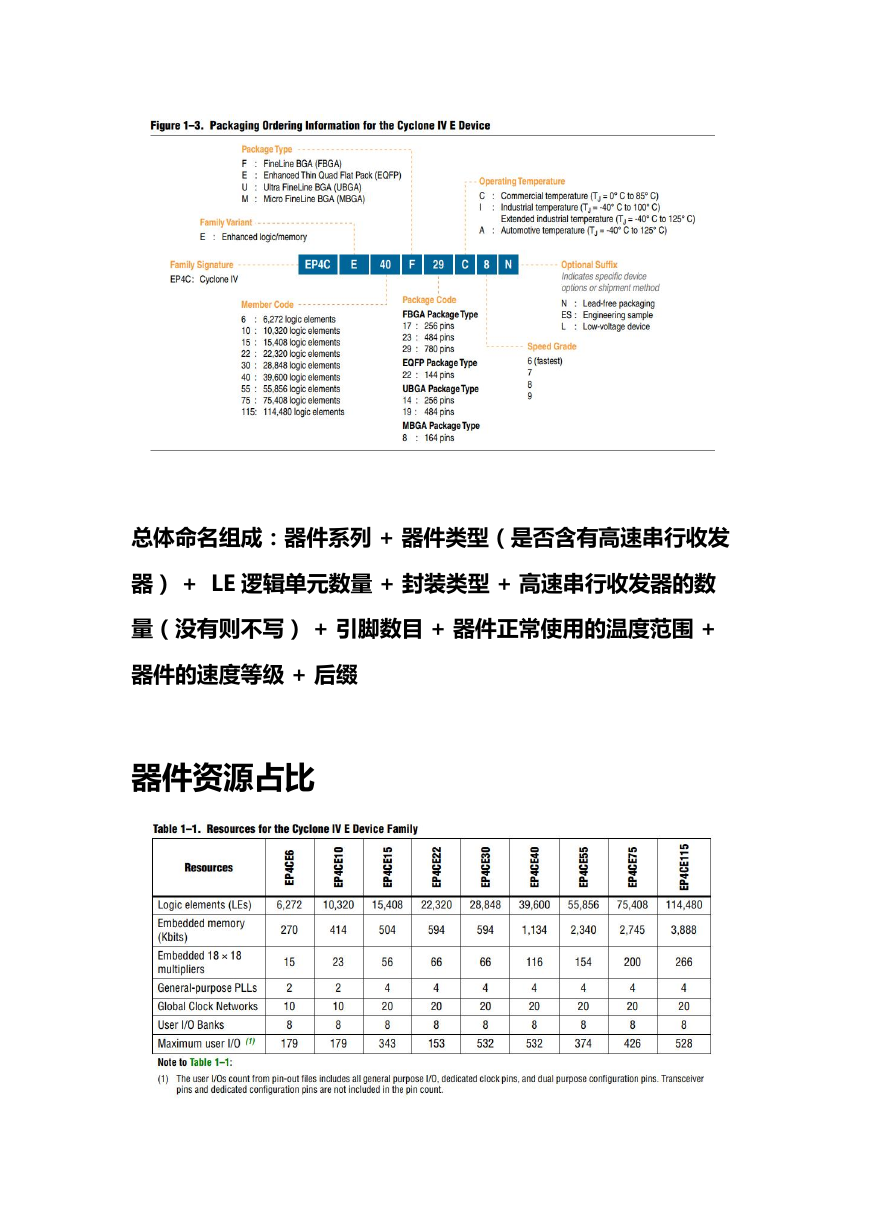

器件资源占比

上面表格来自于Cyclone IV E器件手册,上面描述了该系列器件所占资源及结构:

按表格依次排序为:

1.逻辑单元(LE)

2.嵌入式存储器(Kbits)

3.嵌入式18x18乘法器

4.通用PLL

5.全局时钟网络

6.用户I/O块

7.最大用户I/O块:注释:列表6中的用户 I/O 管脚包括所有的通用 I/O 管脚、专用时钟管脚以

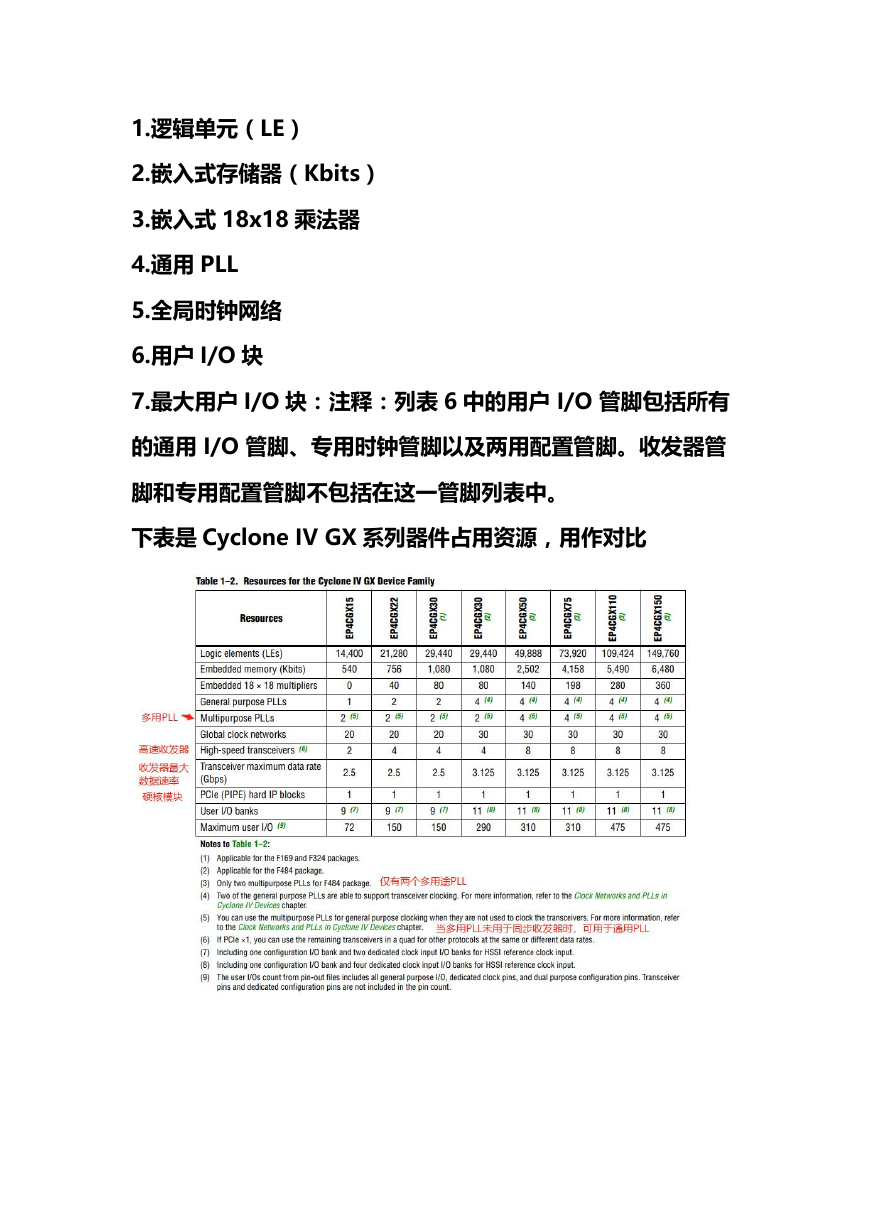

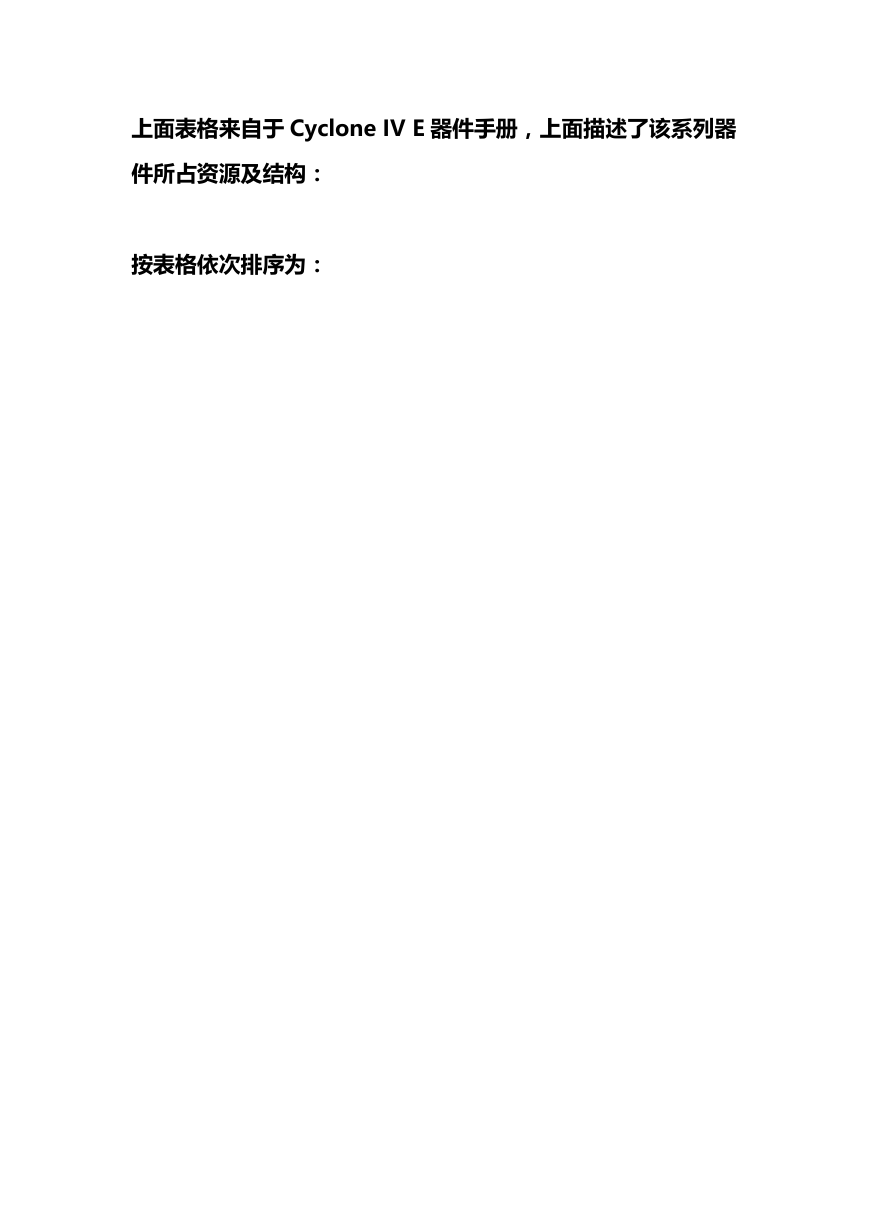

下表是Cyclone IV GX系列器件占用资源,用作对比

FPGA架构

我们要入门FPGA设计以及后续的时序分析学习,那么必须了解FPGA器件内部的工作方式。

为什么说FPGA是一门硬件描述语言,因为FPGA的内部结构其实就好比一块PCB板,FPGA的逻辑阵列

首先介绍一下这几种资源所代表的的含义与电路是咋样的吧?

1.逻辑单元(LE)

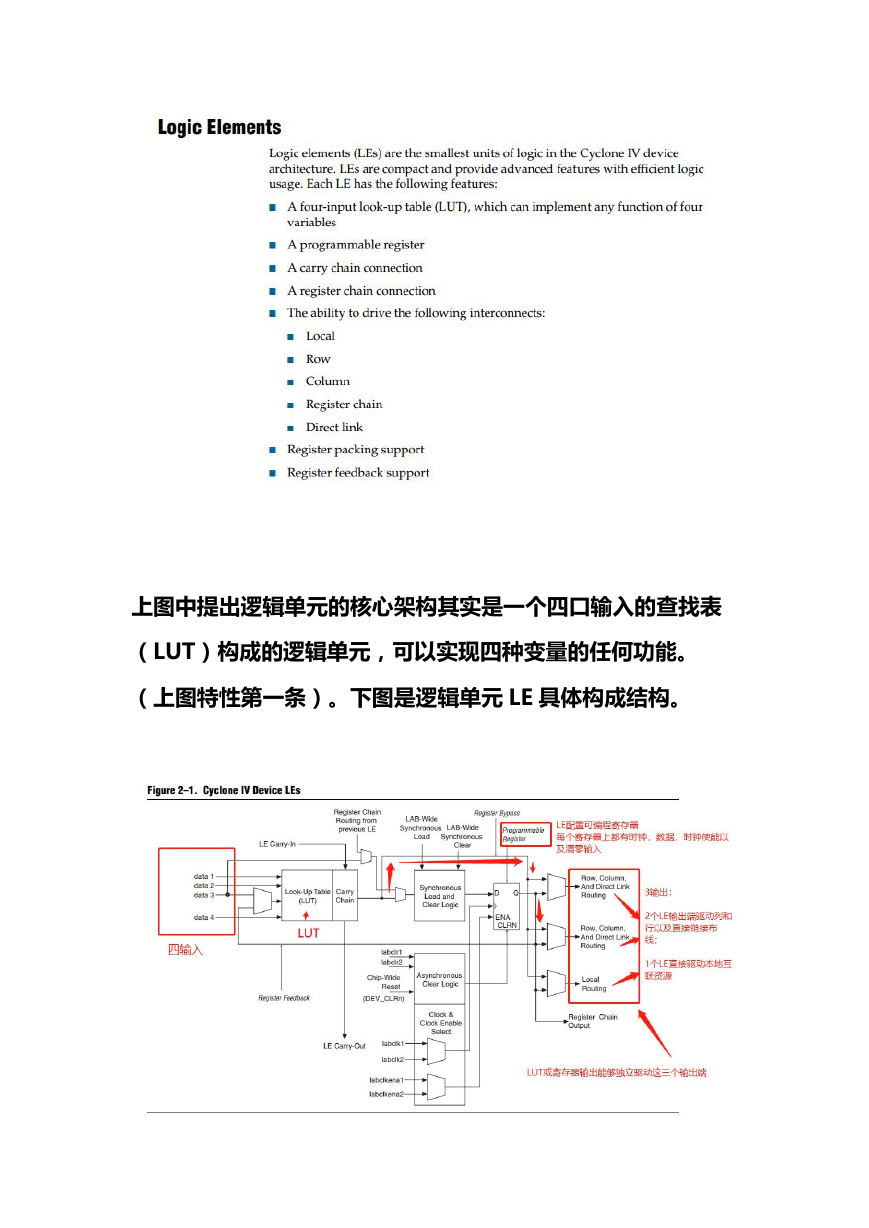

逻辑单元(LE)在Cyclone IV器件中是最小的逻辑单元,逻辑单元特性如下图所示:

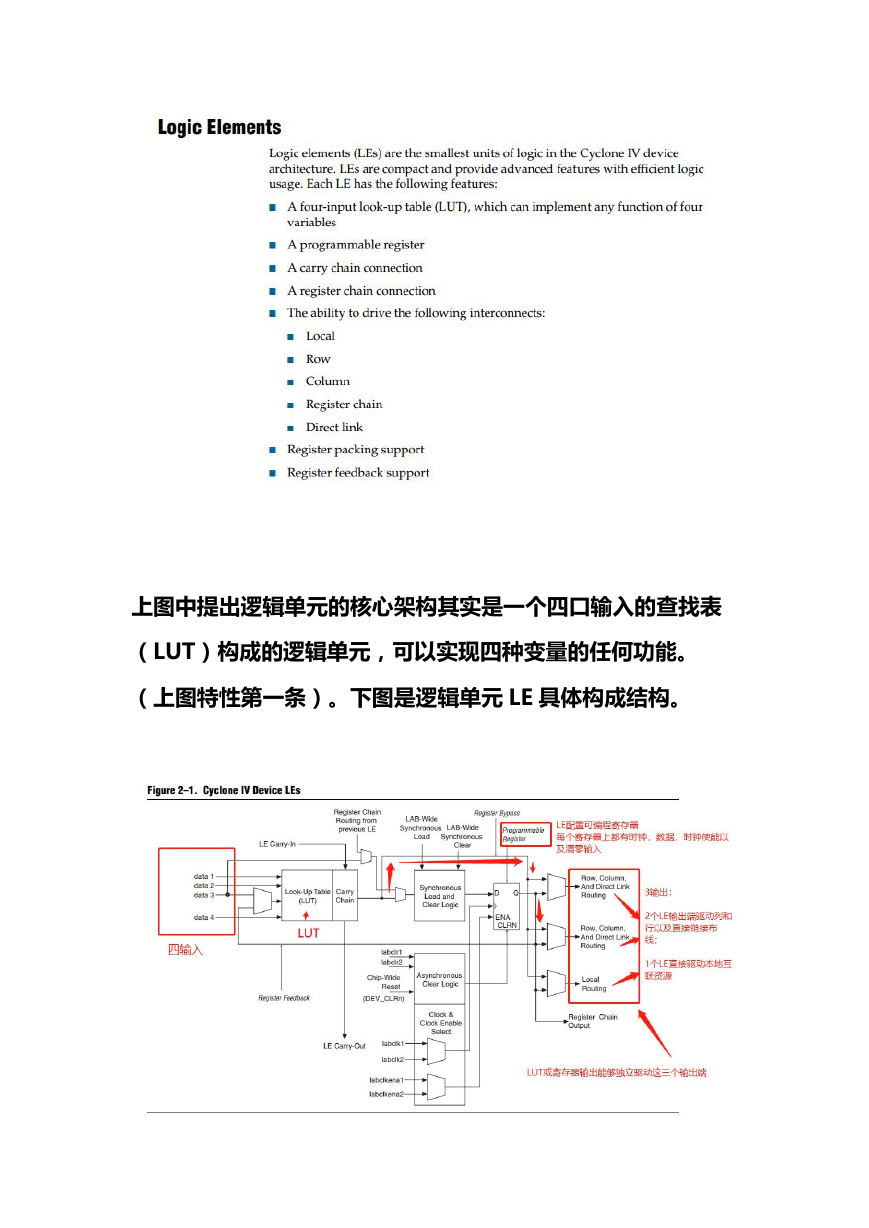

上图中提出逻辑单元的核心架构其实是一个四口输入的查找表(LUT)构成的逻辑单元,可以实现四种变量的任

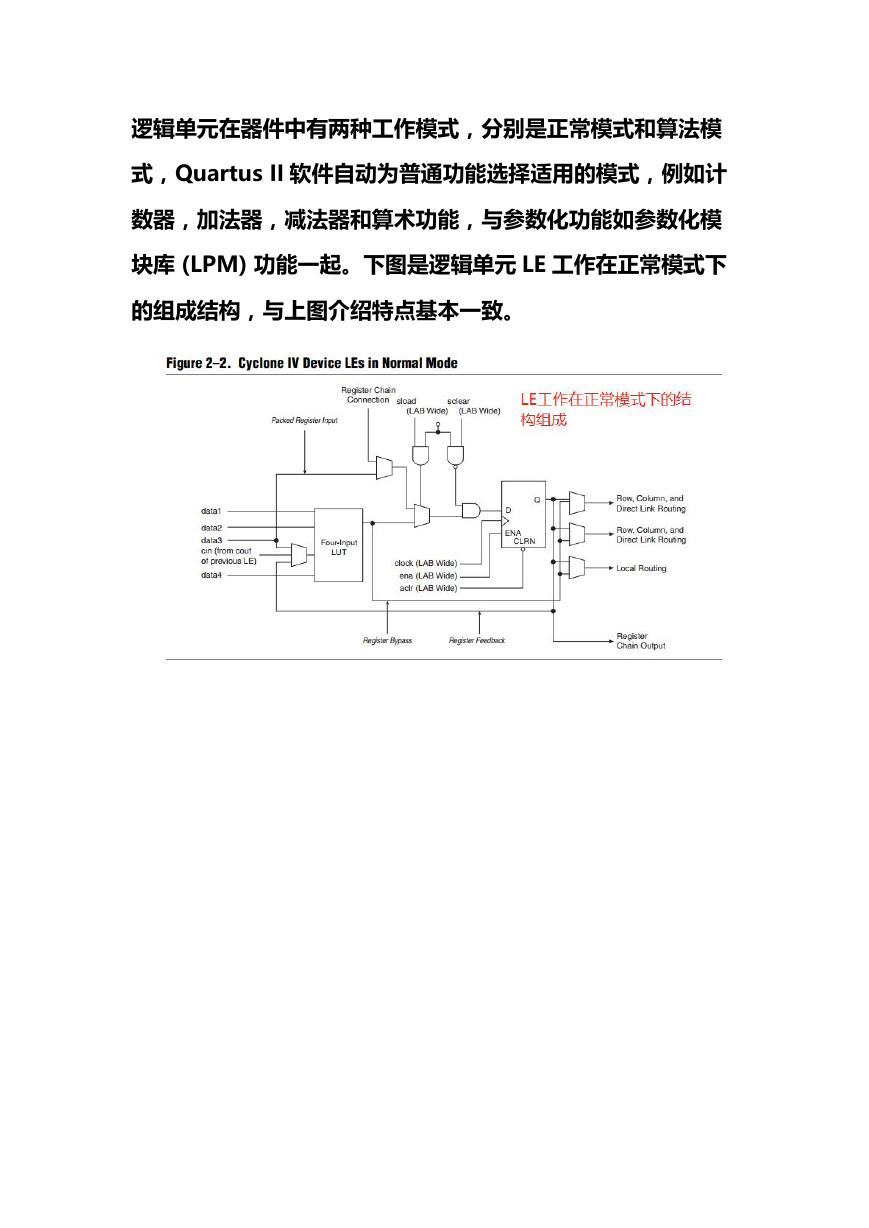

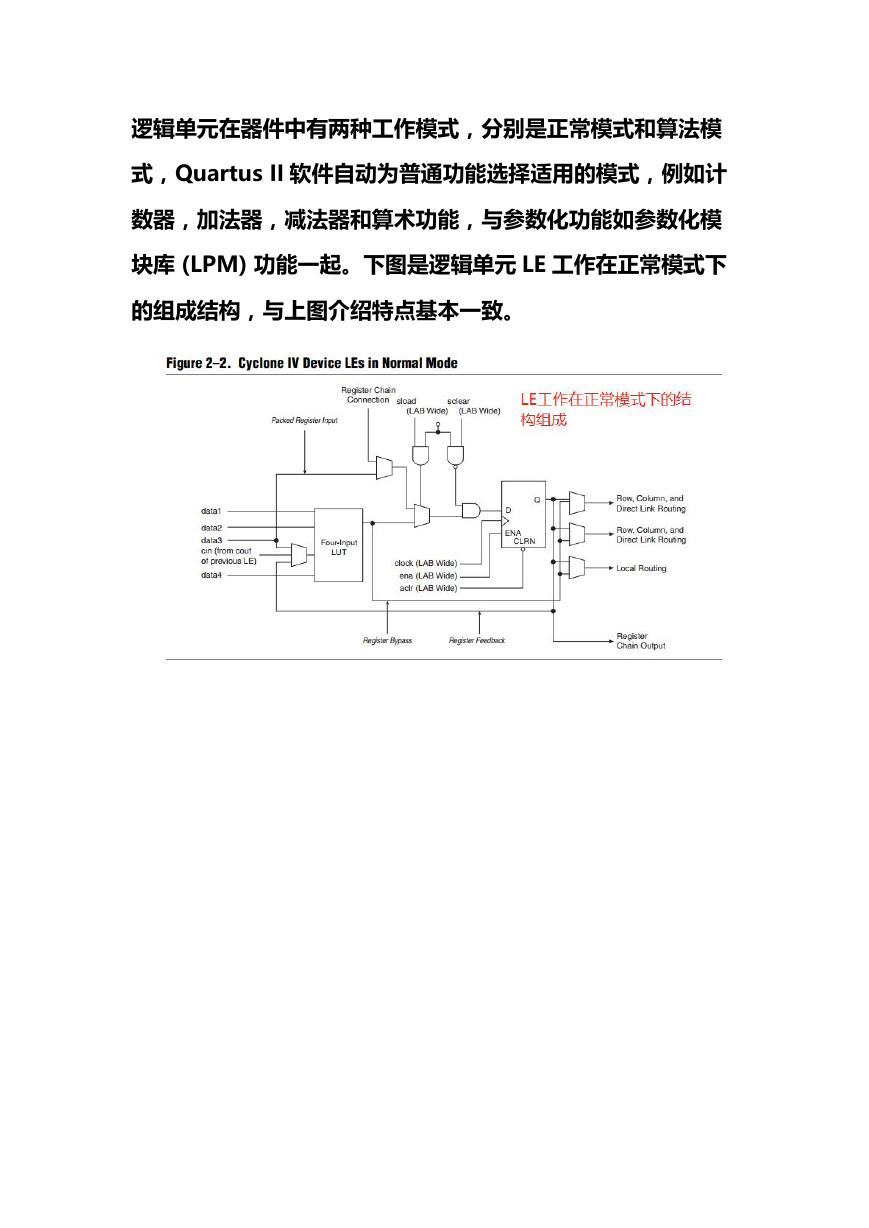

逻辑单元在器件中有两种工作模式,分别是正常模式和算法模式,Quartus II软件自动为普通功能选择

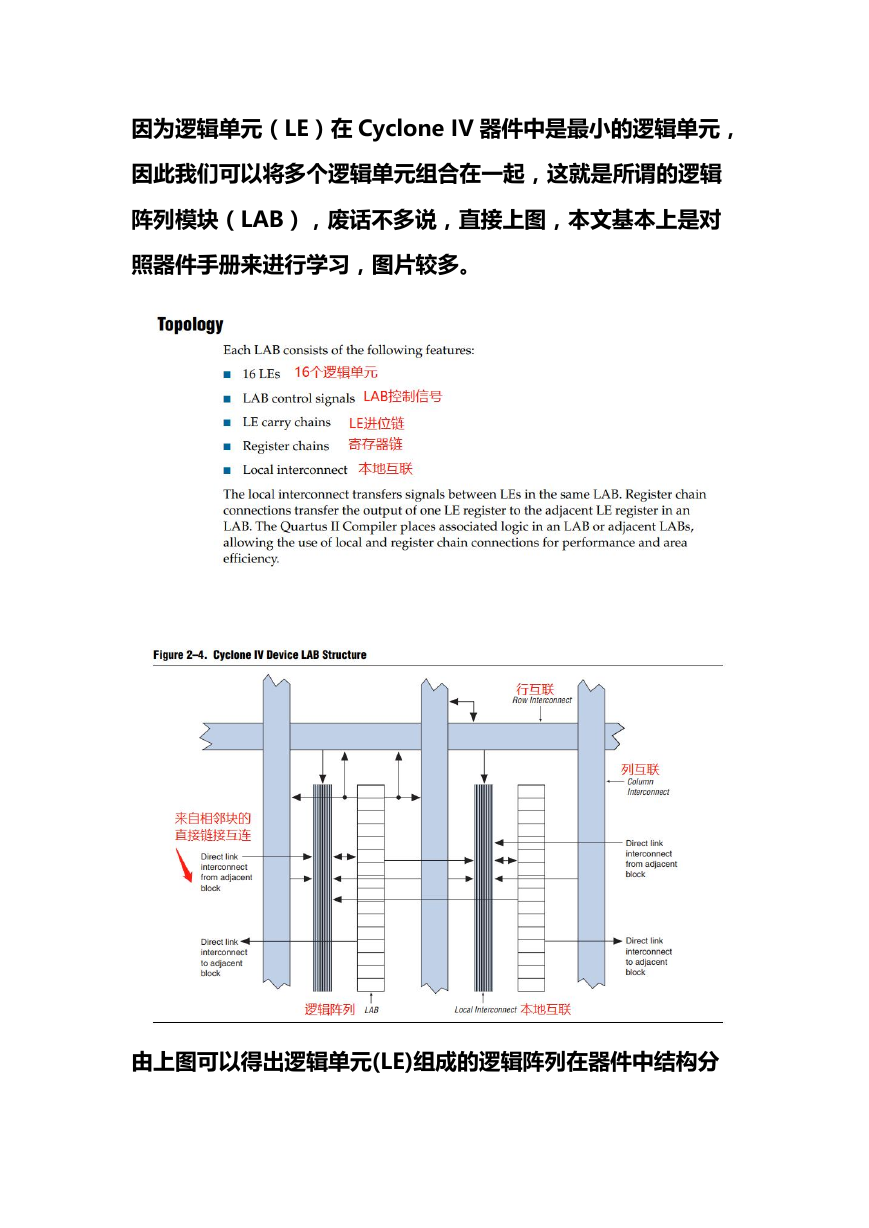

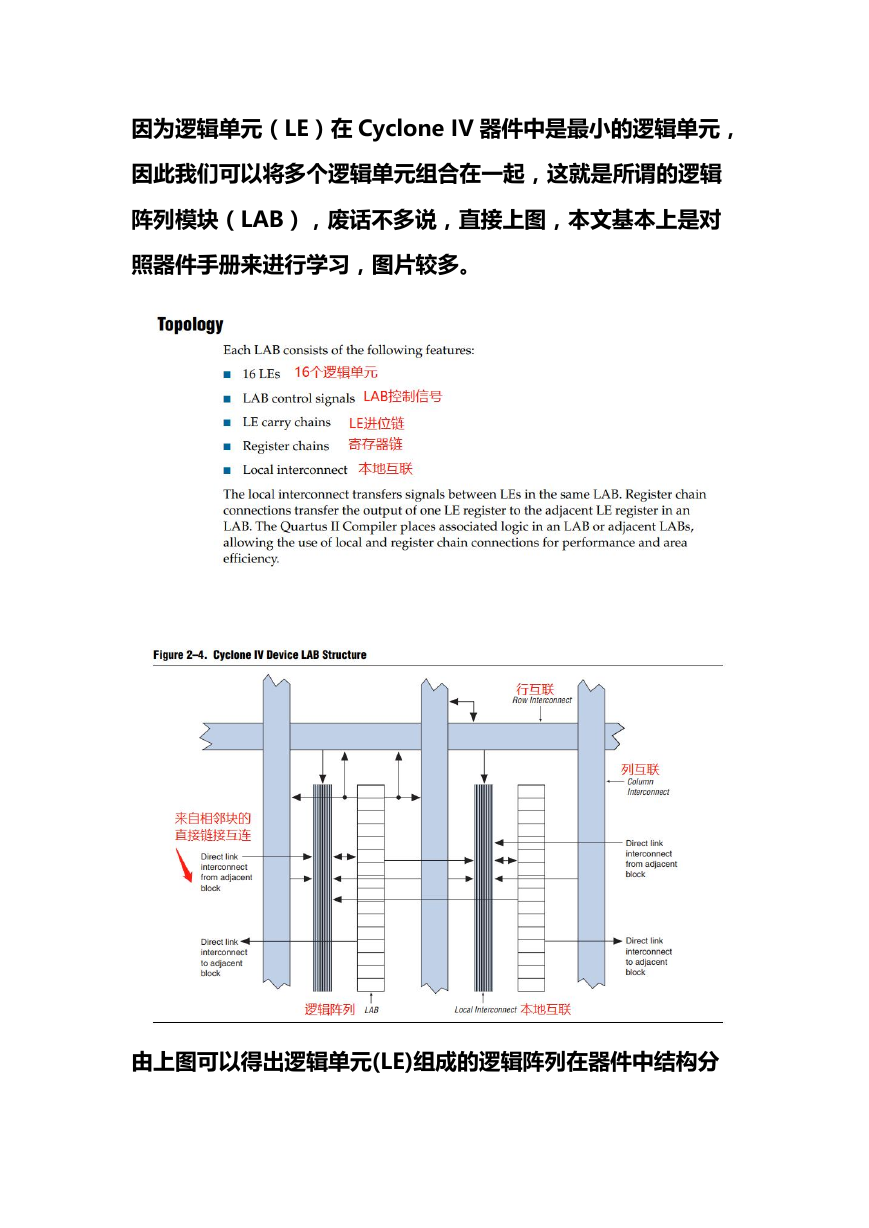

因为逻辑单元(LE)在Cyclone IV器件中是最小的逻辑单元,因此我们可以将多个逻辑单元组合在一

2.嵌入式存储器(Kbits)

嵌入式存储器结构由一列列 M9K 存储器模块组成,通过对这些 M9K 存储器模块进行配置,可以实现各

3.嵌入式乘法器

4.通用PLL

5.用户I/O块

在View-->Pin Legend中打开可得下图对器件的每个符号进行的解释,三角向上的是VCC,三

资源分布图

经过上面对器件资源的介绍,那么这些资源如何分布在器件内部呢?下图不同器件资源分布图

这三个资源分布图一对比就清晰看出(三个不属于同一系列器件),逻辑阵列LAB与M9K存储器以及乘法器交

案列分析

下面以一个典型的数据采集实例,来分析这种资源分布的优势。

对照上图来分析数据流向:

1.数据先由外部高速ADC采集,通过I/O口进入到FPGA内部。

2.接着经过一定的逻辑电路预处理后写入到由M9K存储器组成的缓存,如FIFO或双口RAM中。

3.然后,再由逻辑电路从M9K存储器中读出,进行相应的处理,在处理的过程中,可能会需要高速的乘法运算

4.运算结束后,再由逻辑电路处理后送入由M9K存储器组成的缓存,如FIFO或双口RAM中。

5.等待其他电路如数据发送电路将数据从缓存中读取出来并最终通过I/O口连接的通信电路传输出去。

如果我们将整个数据流从左向右分析,就会发现数据流中每一级所需要的资源都刚好和 Cyclone IV

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc