Title Page

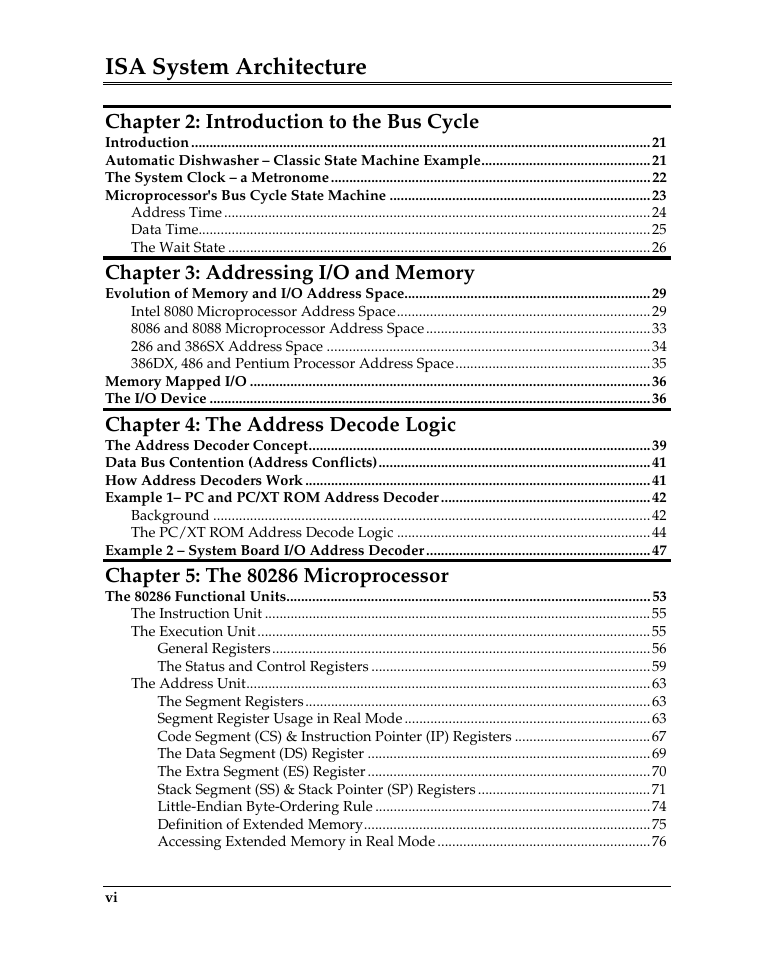

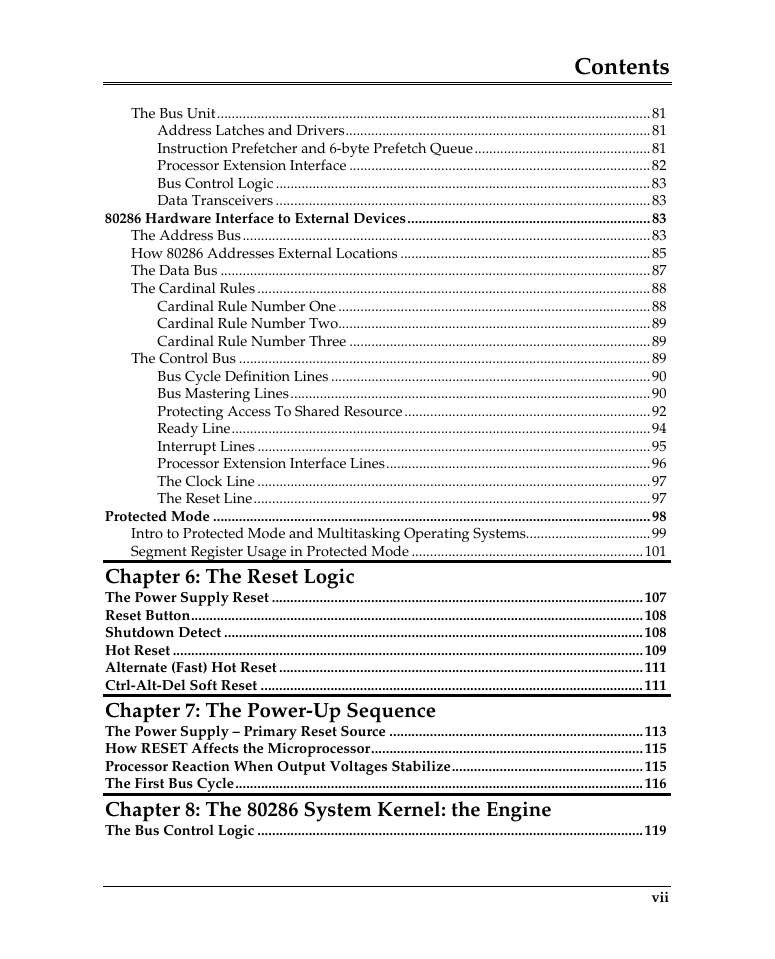

Table of Contents

Chapter 1: Intro to Microprocessor Communication

Instruction Fetch and Execution

General

In-Line Code Fetching

Reading and Writing

Chapter 2: Introduction to the Bus Cycle

Introduction

Automatic Dishwasher – Classic State Machine Example

The System Clock – a Metronome

Microprocessor's Bus Cycle State Machine

Address Time

Data Time

Chapter 3: Addressing I/O and Memory

Evolution of Memory and I/O Address Space

Intel 8080 Microprocessor Address Space

8086 and 8088 Microprocessor Address Space

Chapter 4: The Address Decode Logic

The Address Decoder Concept

Data Bus Contention (Address Conflicts)

How Address Decoders Work

Example 1– PC and PC/XT ROM Address Decoder

Background

Chapter 5: The 286 Microprocessor

The 80286 Functional Units

The Instruction Unit

The Execution Unit

General Registers

Chapter 6: The Reset Logic

The Power Supply Reset

Reset Button

Shutdown Detect

Hot Reset

Alternate (Fast) Hot Reset

Ctrl-Alt-Del Soft Reset

Chapter 7: The Power-Up Sequence

The Power Supply – Primary Reset Source

How RESET Affects the Microprocessor

Processor Reaction When Output Voltages Stabilize

The First Bus Cycle

Chapter 8: The 80286 System Kernel: The Engine

The Bus Control Logic

The Address Latch

Address Pipelining

Chapter 9: Detailed View of the 80286 Bus Cycle

Address and Data Time Revisited

The Read Bus Cycle

Chapter 10: The 80386DX and SX Microprocessors

Introduction

The 80386 Functional Units

General

Code Prefetch Unit

Instruction Decode Unit

Execution Unit

General

The Registers

General Registers

Status, MSW and Instruction Registers

Appendix B: Glossary

Glossary

Index

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc