摘 要

数字时钟是一种集计时、显示、报时于一体的数字系统,随着电子技术的发展,在原

有计时基础上又拓展出了工业过程控制、定时控制、显示气候温度等多种功能,目前普遍

运用在人们的日常生活中。

本文以 Altera 公司 9.0 版本的 Quartus Ⅱ软件编译硬件描述语言 Verilog 代码,采用自

顶而下的设计方法对代码进行综合、适配、功能仿真,最后下载入 Cyclone EP2C5T144 的

FPGA 核心板,实现了数字时钟的设计要求。通过顶层文件调用子模块函数由按键的输入

来完成数字钟校对功能,不仅能分别显示时分秒和年月日,还具有闹钟音乐、跑表、整点

报时等多项功能。较为详细地说明了时钟设计各模块的流程,突出显示了 Verilog 语言的可

读性及 FPGA 设计数字电路的灵活性。

关键词:Verilog HDL;数字时钟;功能仿真;Cyclone EP2C5T144

I

�

Abstract

Digital clock is a digital systems in the integration of timing, displaying time and reporting

time. With the development of electronic technology, it extends out of various functions. Such as

the industrial process controlling, timing controlling, climate temperature displaying on the basis

of the original timing. Digital clock is being widely used in the people's daily life.

This article mainly introduced the design of digital clock based on Verilog design method by

the top-down to version 9.0 of Altera company Quartus Ⅱ software, compiling Verilog

hardware description language code and making a comprehensive, adaptation,

function

simulation. Finally the code was downloaded into the Cyclone EP2C5T144 FPGA core board.

Realizing the design requirements of electronic clock. Completing the function of correcting

time through the top documents call a module functions are done by key inputting. Digital clock

can not only display the time and date respectively, but also has many functions such as alarm

clock, stopwatch, announcing the hour. The detailed description about the design of clock

module process is given, highlighting the readability of the Verilog language, giving prominence

to FPGA design of digital circuit flexibility.

Key Words: Verilog HDL; digital electronic clock; functional simulation; Cyclone EP2C5T144

II

�

目 录

摘 要................................................................................................................I

Abstract...........................................................................................................II

1. 引言..............................................................................................................1

1.1 背景及选题意义...........................................................................................1

1.2 国内研究现状...............................................................................................1

1.3 主要内容安排...............................................................................................2

2. 设计语言及软件的介绍............................................................................. 2

2.1 硬件描述语言 Verilog HDL 简介...............................................................2

2.1.1 Verilog 语言的特点........................................................................... 3

2.2 Quartus II 软件简介...................................................................................... 3

2.2.1 Quartus II 的设计流程......................................................................... 4

2.2.2 Quartus II 的界面介绍......................................................................... 4

2.2.3 Quartus II 的使用步骤......................................................................... 4

3. 硬件电路介绍.............................................................................................4

3.1 系统芯片的简介..........................................................................................4

3.2 系统主板电路分析......................................................................................5

4. 数字钟总体及各模块的设计..................................................................... 7

4.1 数字时钟总体设计方案...............................................................................7

4.2 分频模块.......................................................................................................8

4.3 控制模块.....................................................................................................10

4.4 时间及调整模块.........................................................................................10

4.4.1 时间正常显示模块......................................................................... 10

4.4.2 时间调整模块..................................................................................12

4.5 时间位选模块.............................................................................................13

4.6 秒表模块.....................................................................................................14

4.7 闹钟模块.....................................................................................................16

4.8 闹铃与定时报时音乐模块........................................................................ 16

4.9 日期模块.....................................................................................................18

4.10 日期调整模块...........................................................................................20

4.11 显示模块...................................................................................................20

4.12 数字时钟顶层模块.................................................................................. 21

5. 系统调试及运行结果分析....................................................................... 22

5.1 硬件调试.....................................................................................................22

5.2 调试注意事项............................................................................................ 23

5.3 调试过程及结果........................................................................................ 23

III

�

6. 总结..........................................................................................................25

参考文献.........................................................................................................27

附 录.............................................................................................................28

致 谢.............................................................................................................32

IV

�

合肥师范学院 2017 届本科生毕业论文(设计)

1. 引言

1.1 背景及选题意义

时间一直与人类的生活息息相关,从古至今时钟的重要性不言而喻,随着科技迅速发

展计时工具也在不断的更新换代。历时千年,钟表从最初的“悬挂的宝石”日晷,到沙钟、

水钟、机械钟、电子钟、数字钟,直到现在的原子钟、分子钟,人类科技文明的进步推动

了每一种时钟的出现。

相比于以机械振动系统为基准和指针显示的机械钟,基于数字电路技术基础的数字钟

是实现精准计时的钟表,其日差小于一秒,通过数码管显示更为直观。它还具有轻便袖珍

易于随身携带,生产成本低,调时简易,功能齐全等优点,未来具有广泛的市场发展空间,

已成为人们日常生活中不可或缺的必需品。

随着 FPGA[1]技术发展的日新月异,新式的数字时钟产品应用领域愈发广泛:在生产

中可用于工业过程控制系统、通断电气动力设备;在生活中可以用于控制家电的工作时间,

启闭路灯,车内的仪表盘显示,通过设置 LCD 屏还能显示周围温度;在学习上可用于学

校的定时打铃和校园广播;在工作中可用于火车站、机场的候车室,体育馆、超市等要显

示标准时间的场所和消防报警系统……所以研究数字时钟及拓展其功能,具有举足轻重的

实用价值。

1.2 国内研究现状

数字时钟不仅是现代最普遍的计时工具,更是世界钟表史上第三次飞跃性进步的智慧

结晶。第一阶段是十七世纪末,伴随古典振动精密计时学的发展以及摆的发明,使时钟的

走时差从分级缩小到秒级。第二阶段是二十世纪二三十年代,压电技术的发展产生计时精

度更准确的石英表,让走时月差从分级缩小到秒级。第三阶段是数码计时技术的应用,使

走时差从分级缩小到万秒级,从指针计时方式变为更加直观清晰的数字显示,还扩展出了

显示当天日期和当地温度等功能,功能的增加使之更符合广大人民群众的日常需求,为原

本功能单一的钟表计时业带来了跨越性的进步革新。

近年来我国以研究多功能数字钟为主,除了显示时间基本功能外还具有闹铃、秒表、

倒计时、整点报时等功能,通过不断的优化改进数字时钟的设计,使之具有更广阔的市场

发展前景。

1

�

合肥师范学院 2017 届本科生毕业论文(设计)

1.3 主要内容安排

第一部分描述了数字时钟的背景和选题意义,简介数字化时钟系统国内外发展的现况,

由现在遇到的问题与可拓展功能之处引出论文的课题。

第二部分介绍了设计语言 Verilog HDL[2]和设计软件 Quartus II[3]。详细描述了 Verilog

HDL 的发展过程及特点,Quartus II 的设计流程和使用步骤。

第三部分根据设计需要介绍了系统芯片的选取及芯片的相关具体资料,从局部到整体

以模块化循序渐进的方式,实现了功能齐全的数字时钟的硬件设计。

第四部分主要概括数字时钟的总体设计流程及思路,通过顶层的原理图文件将各功能

模块有机结合,实现时钟走时、时间调整、秒表、闹铃、日历、整点报时附加功能。

第五部分通过硬件联机调试的结果分析,记录软件设计中的不足及调试过程。

第六部分针对数字时钟功能上机调试中存在的问题,总结系统软件编写的经验教训并

展望未来的研究方向。

2. 设计语言及软件的介绍

2.1 硬件描述语言 Verilog HDL 简介

EDA[4]技术主要涉及四个方面:一是大规模可编程逻辑器件,应用最广泛的是现场可

编程门阵列 FPGA。硬件描述语言 Verilog HDL。软件开发系统,本文采用软件为 QuartusⅡ。

实验开发系统,包括 FPGA 目标芯片和编程下载电路,本文采用的芯片为 CycloneⅡ[5]。

硬件描述语言是一种对硬件逻辑电路进行描述的高级编程语言,包括行为、结构、数

据流方面。HDL 可在不同抽象级上描述电路的连接、功能、时序,表达有并行性。设计者

可由上至下(Top-Down)逐层表示复杂的系统。

HDL 主要包括 Verilog 和 VHDL,在描述结构上两者代码比为 3:1。由于 VHDL 源于

ADA 结构严谨不易学习,高效便捷的 Verilog HDL 就成了主流。Verilog HDL 是由 C 语言

演变而成的一种硬件描述语言,1983 年由一个民间公司 Gateway Design Automation 创建,

在非盈利性组织 Open Verilog International 的推广下,1995 年成为 IEEE 1394 Standard[6]。

Verilog 的流行的原因:在 90 年代 cadence 模拟器广泛流行,它作为 Verilog-XL 的基

础,因此其成熟发展的资源丰富,在硅谷应用广泛。继承了 C 语言的简洁且效率高的编程

风格,提升了建模能力,语法要求宽松,自带仿真指令可随时检测信号变化。

2

�

合肥师范学院 2017 届本科生毕业论文(设计)

2.1.1 Verilog 语言的特点

Verilog 适用于抽象级模型的开发验证,它的主要特点有:

(1) Verilog 可用于模拟从随机和纯行为系统级、算法级、开关级、RTL 级、门级等多

种抽象设计层次的数字系统建模,这五种类型从高到低逐渐接近硬件。

(2) Verilog 有三种常用描述方式:结构、行为、数据流描述。系统级、算法级、RTL

级属于行为建模,是对电路功能的抽象描述。门级建模描述基本门电路的连接方式,属于

结构级。开关级建模层次最低,仅是对 MOS 管的连接。

(3) 结构描述方式侧重电路连接方式的描述,通过调用 Verilog 中 26 个基元(14 个门

元件,12 个开关元件)和用户自定义元件 UDP 连线完成建模过程。行为描述方式用 always、

initial 行为过程语句对电路的功能进行抽象描述[7]。

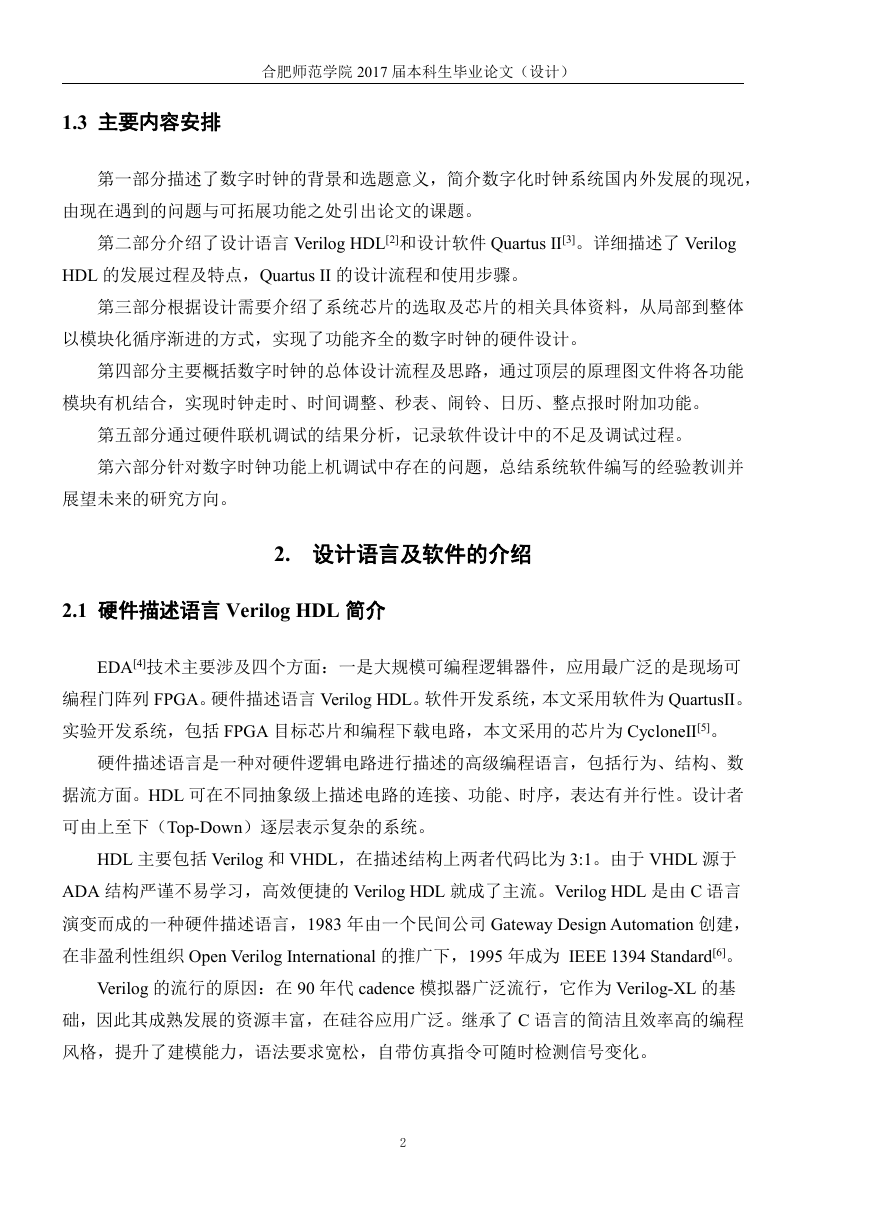

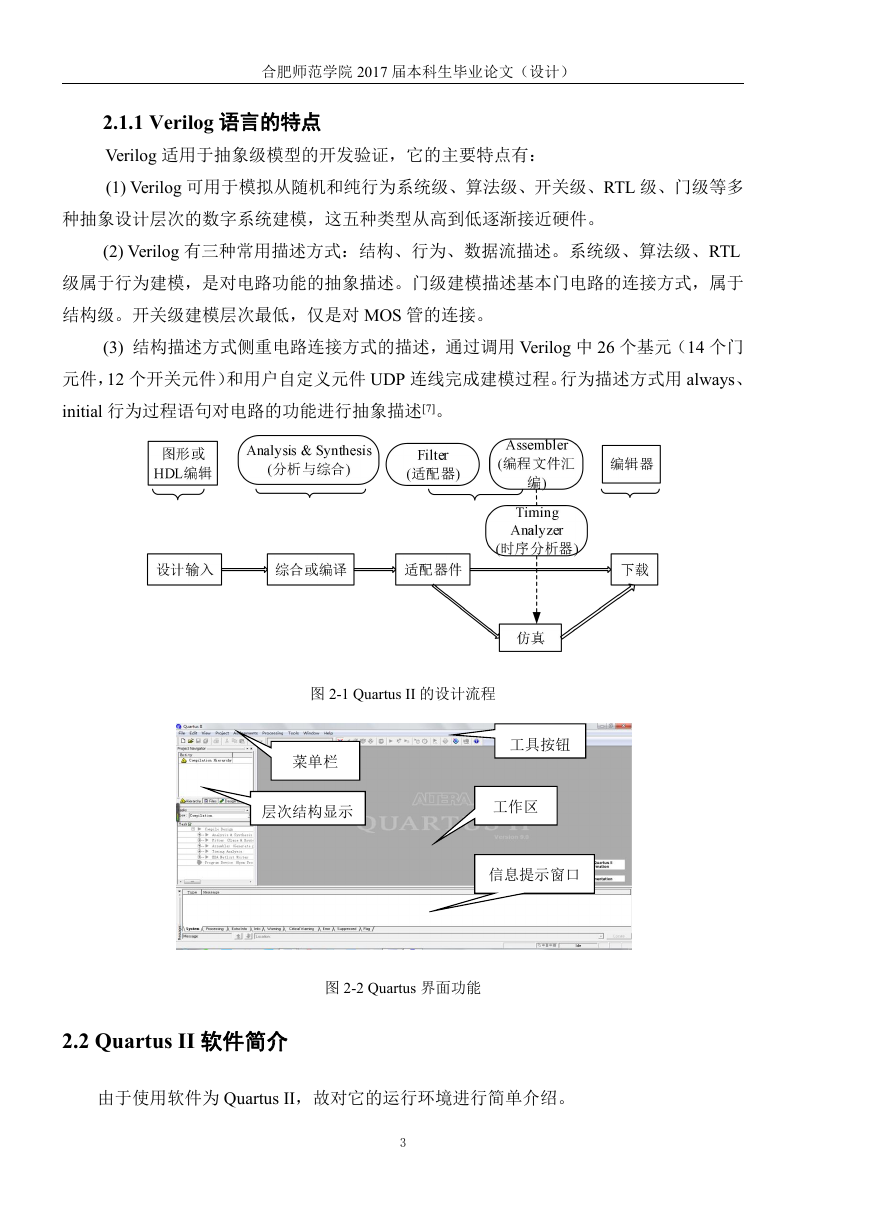

图 2-1 Quartus II 的设计流程

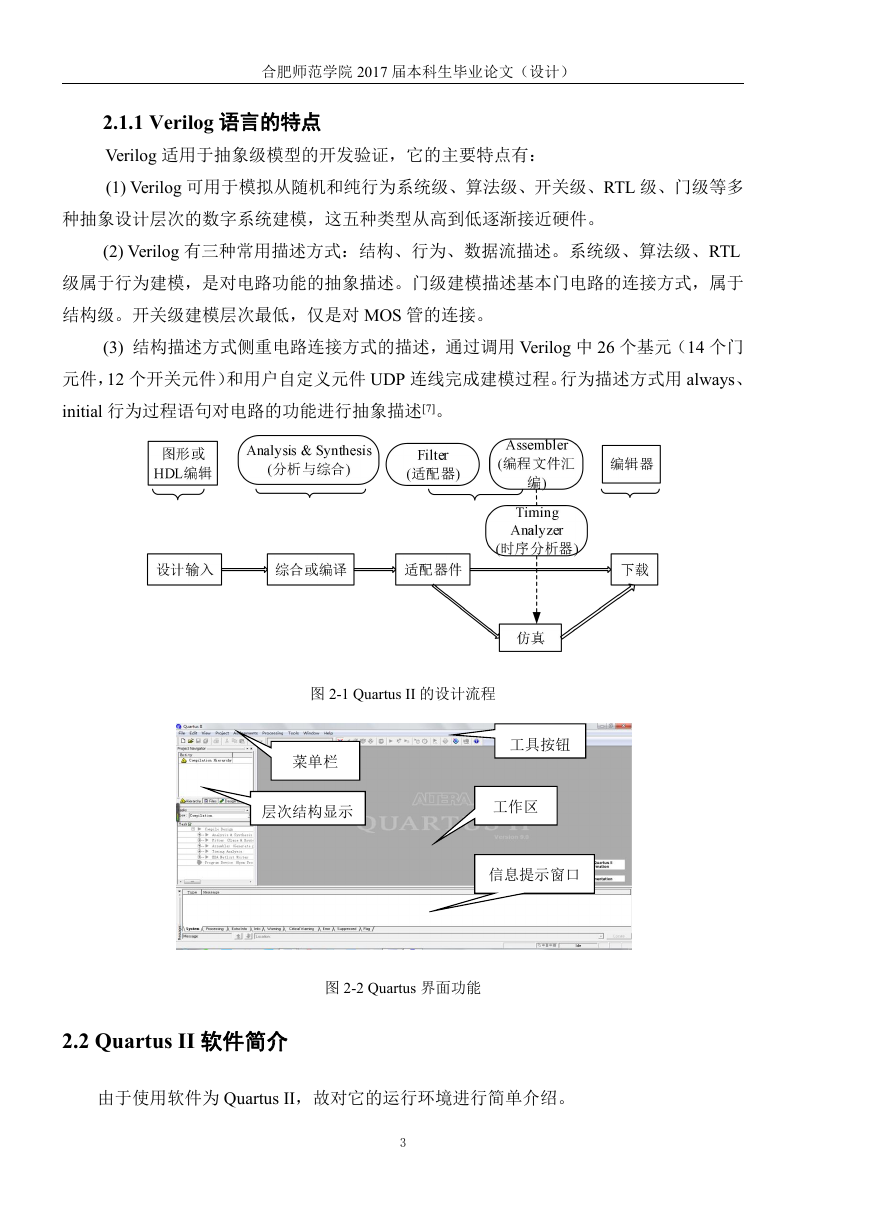

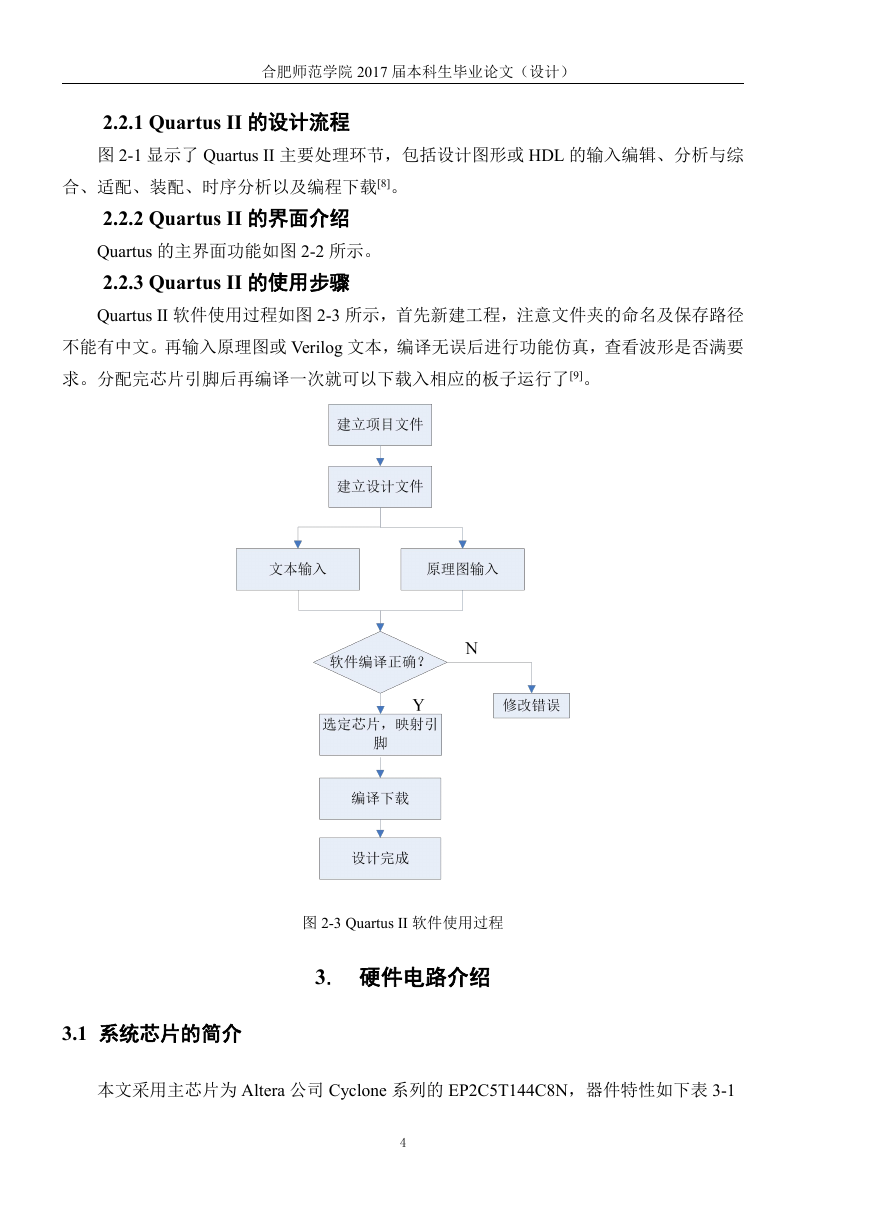

菜单栏

工具按钮

层次结构显示

工作区

信息提示窗口

图 2-2 Quartus 界面功能

2.2 Quartus II 软件简介

由于使用软件为 Quartus II,故对它的运行环境进行简单介绍。

3

�

合肥师范学院 2017 届本科生毕业论文(设计)

2.2.1 Quartus II 的设计流程

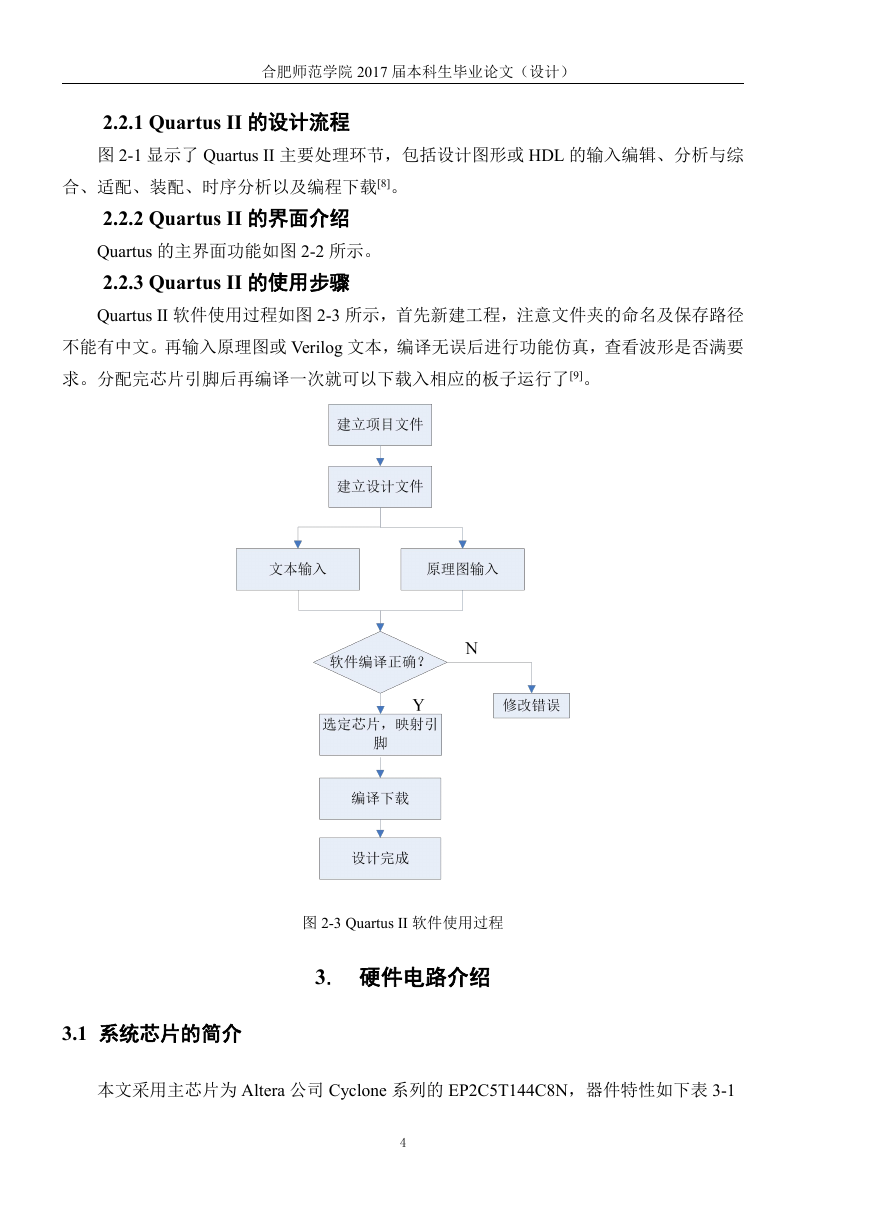

图 2-1 显示了 Quartus II 主要处理环节,包括设计图形或 HDL 的输入编辑、分析与综

合、适配、装配、时序分析以及编程下载[8]。

2.2.2 Quartus II 的界面介绍

Quartus 的主界面功能如图 2-2 所示。

2.2.3 Quartus II 的使用步骤

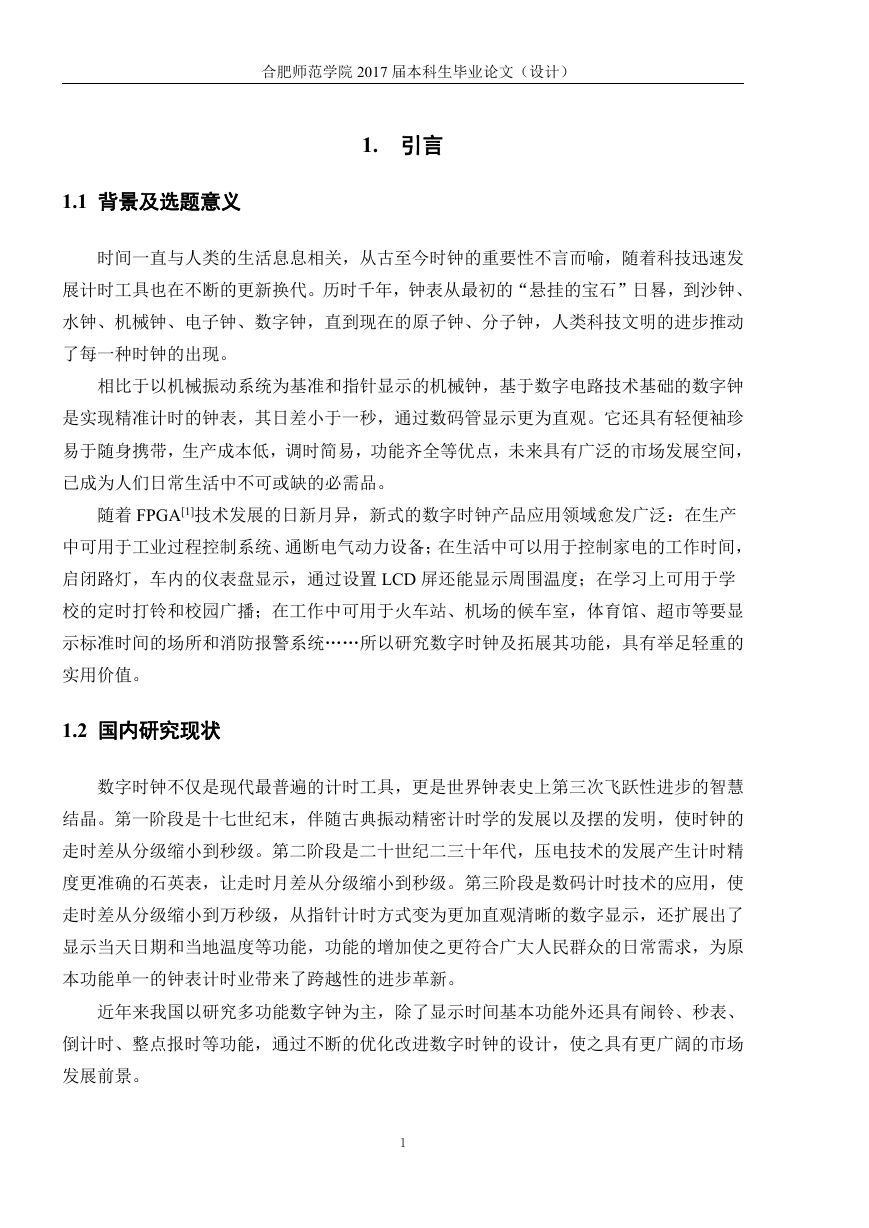

Quartus II 软件使用过程如图 2-3 所示,首先新建工程,注意文件夹的命名及保存路径

不能有中文。再输入原理图或 Verilog 文本,编译无误后进行功能仿真,查看波形是否满要

求。分配完芯片引脚后再编译一次就可以下载入相应的板子运行了[9]。

图 2-3 Quartus II 软件使用过程

3. 硬件电路介绍

3.1 系统芯片的简介

本文采用主芯片为 Altera 公司 Cyclone 系列的 EP2C5T144C8N,器件特性如下表 3-1

4

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc