基于 XDMA 核和 AXI4 协议实现 PCIE 接口的数据读写

1 AXI4 协议简介

AXI 协议是 Xilinx 的 ZYNQ 系列芯片中最为常用的总线协议。其主要分为

AXI4 协议、AXI4-Lite 协议和 AXI4-stream 协议。协议的具体介绍详见我的博客,

地址为:https://blog.csdn.net/m0_46642108/article/details/107163267

2 PCIE 协议简介

PCIe 总线使用端到端的连接方式,在一条 PCIe 链路的两端只能各连接一个

设备,这两个设备互为是数据发送端和数据接收端。PCIe 总线除了总线链路外,

还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使

用这些层次。PCIe 总线使用的层次结构与网络协议栈较为类似。PCIe 链路使用

“端到端的数据传送方式”,发送端和接收端中都含有 TX(发送逻辑)和 RX(接收逻

辑),其结构如图所示。

由上图所示,在 PCIe 总线的物理链路的一个数据通路(Lane)中,由两组差

分信号,共 4 根信号线组成。其中发送端的 TX 部件与接收端的 RX 部件使用一

组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;

而发送端的 RX 部件与接收端的 TX 部件使用另一组差分信号连接,该链路也被

称为发送端的接收链路,也是接收端的发送链路。一个 PCIe 链路可以由多个 Lane

组成。

�

高速差分信号电气规范要求其发送端串接一个电容,以进行 AC 耦合。该电

容也被称为 AC 耦合电容。PCIe 链路使用差分信号进行数据传送,一个差分信

号由 D+和 D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送

端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求

“等长”、“等宽”、“贴近”,而且在同层。因此外部干扰噪声将被“同值”而且“同时”

加载到 D+和 D-两根信号上,其差值在理想情况下为 0,对信号的逻辑值产生的

影响较小。因此差分信号可以使用更高的总线频率。

此外使用差分信号能有效抑制电磁干扰 EMI(Electro Magnetic Interference)。

由于差分信号 D+与 D-距离很近而且信号幅值相等、极性相反。这两根线与地线

间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。

当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;

二是差分信号的布线相对严格一些。

PCIe 链路可以由多条 Lane 组成,目前 PCIe 链路可以支持 1、2、4、8、12、

16 和 32 个 Lane,即×1、×2、×4、×8、×12、×16 和×32 宽度的 PCIe 链路。每一

个 Lane 上使用的总线频率与 PCIe 总线使用的版本相关。

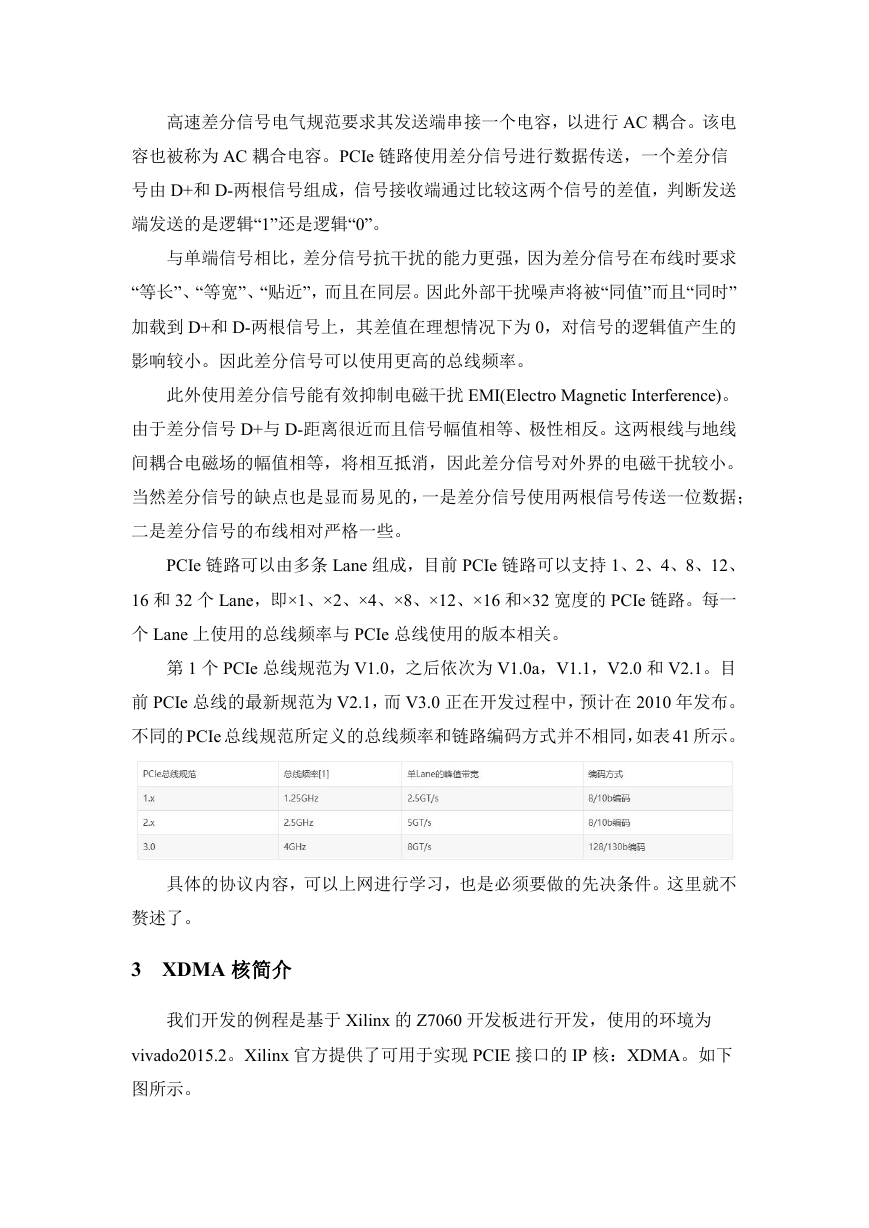

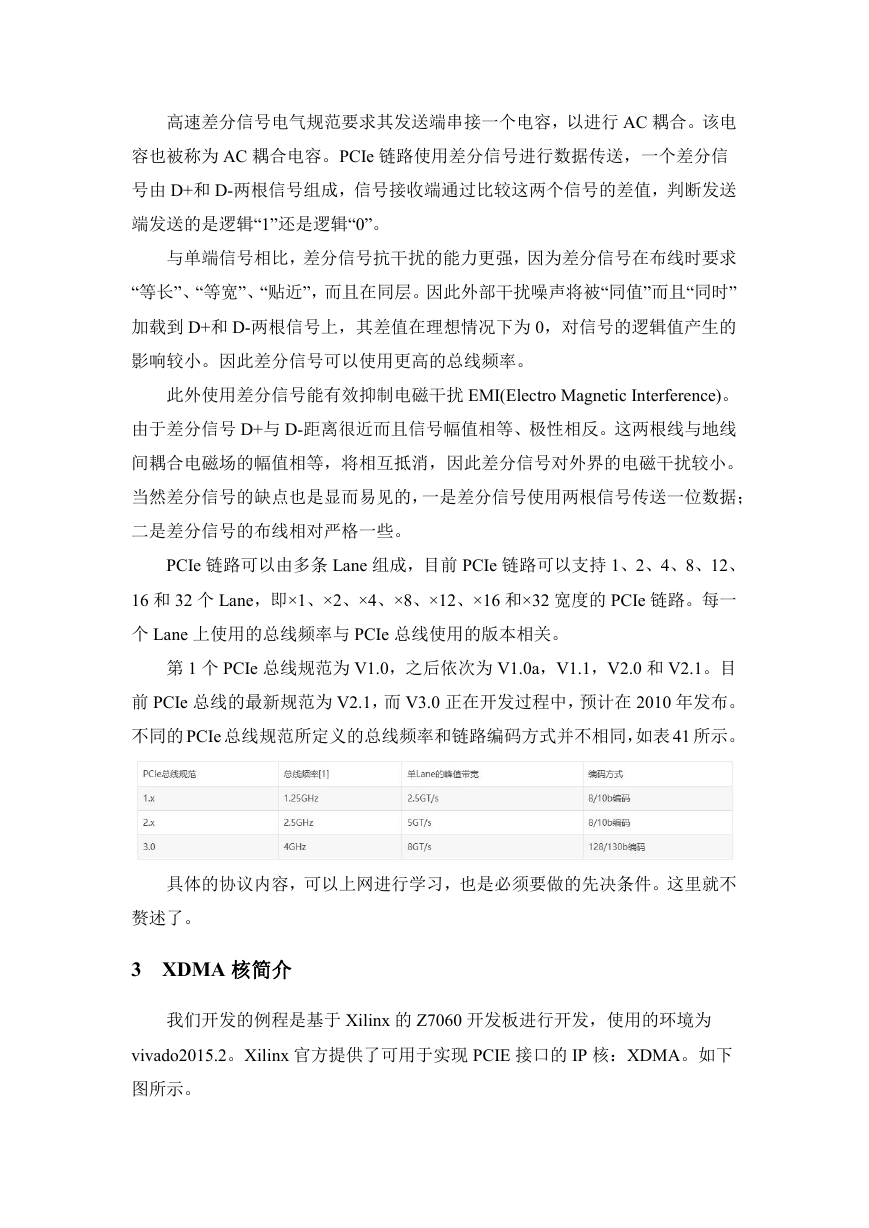

第 1 个 PCIe 总线规范为 V1.0,之后依次为 V1.0a,V1.1,V2.0 和 V2.1。目

前 PCIe 总线的最新规范为 V2.1,而 V3.0 正在开发过程中,预计在 2010 年发布。

不同的 PCIe 总线规范所定义的总线频率和链路编码方式并不相同,如表 41 所示。

具体的协议内容,可以上网进行学习,也是必须要做的先决条件。这里就不

赘述了。

3 XDMA 核简介

我们开发的例程是基于 Xilinx 的 Z7060 开发板进行开发,使用的环境为

vivado2015.2。Xilinx 官方提供了可用于实现 PCIE 接口的 IP 核:XDMA。如下

图所示。

�

IP 核的全称为:DMA/Bridge Subsystem for PCI Express(PCIe)。是专门用来

实现 PCIe 接口协议的。XDMA 核通过 PCIE 差分接口 pci-exp-rx 接收到数据后,

通过内部解析,将数据通过 AXI4 和 AXI4-Lite 协议接口输出。如图所

XDMA 核的配置项主要分为:Basic、PCIe ID、PCIe:BARs、PCIe:MISC、

PCIe:DMA。我们一个一个来介绍一下。

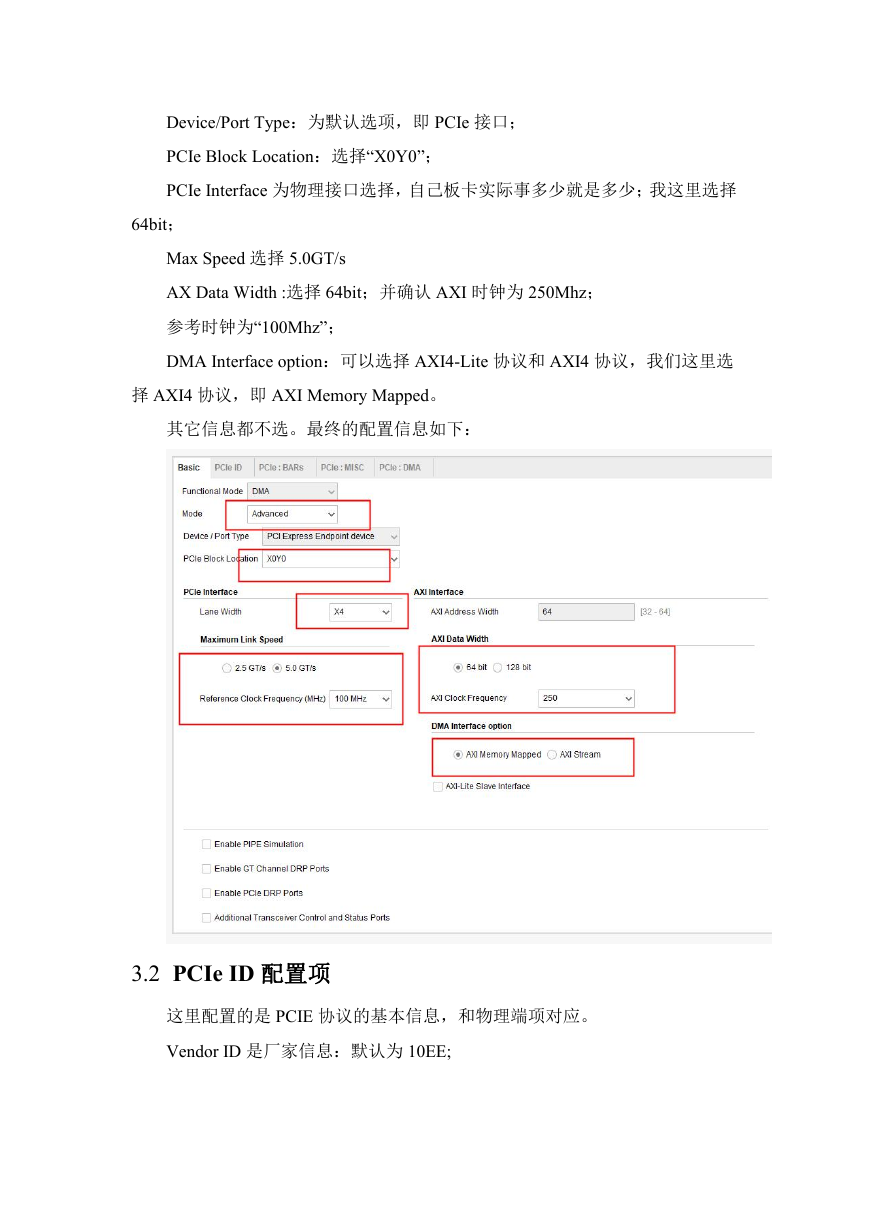

3.1 Basic 配置项

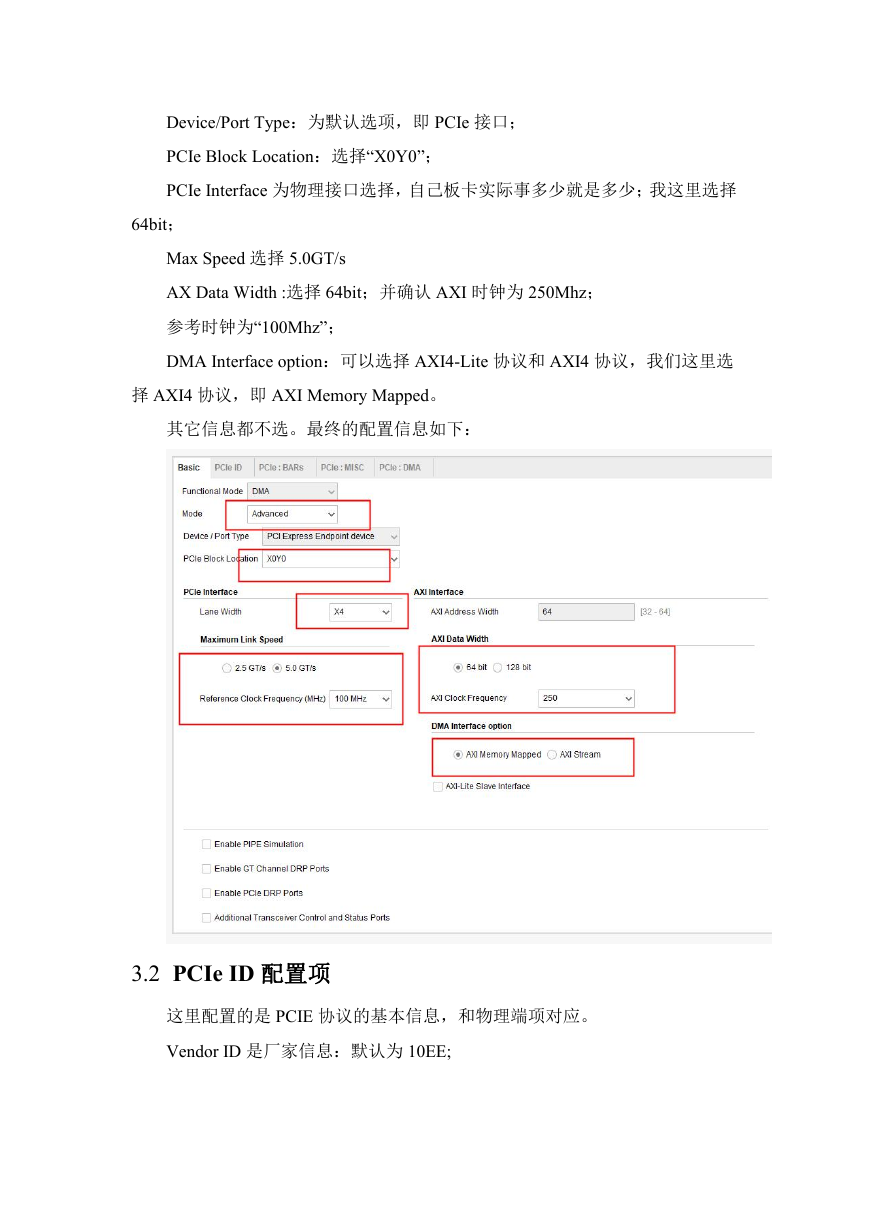

这里配置的是 PCIE 协议的基本信息,和物理端项对应。

Functional Mode :默认为 DMA;

Mode:选择“Advanced”;

�

Device/Port Type:为默认选项,即 PCIe 接口;

PCIe Block Location:选择“X0Y0”;

PCIe Interface 为物理接口选择,自己板卡实际事多少就是多少;我这里选择

64bit;

Max Speed 选择 5.0GT/s

AX Data Width :选择 64bit;并确认 AXI 时钟为 250Mhz;

参考时钟为“100Mhz”;

DMA Interface option:可以选择 AXI4-Lite 协议和 AXI4 协议,我们这里选

择 AXI4 协议,即 AXI Memory Mapped。

其它信息都不选。最终的配置信息如下:

3.2 PCIe ID 配置项

这里配置的是 PCIE 协议的基本信息,和物理端项对应。

Vendor ID 是厂家信息:默认为 10EE;

�

Device ID 是设备信息:默认为 7024;此处可以随意更改,当存在多板卡时,

更改此处信息即可;

其他参数都为默认即可;

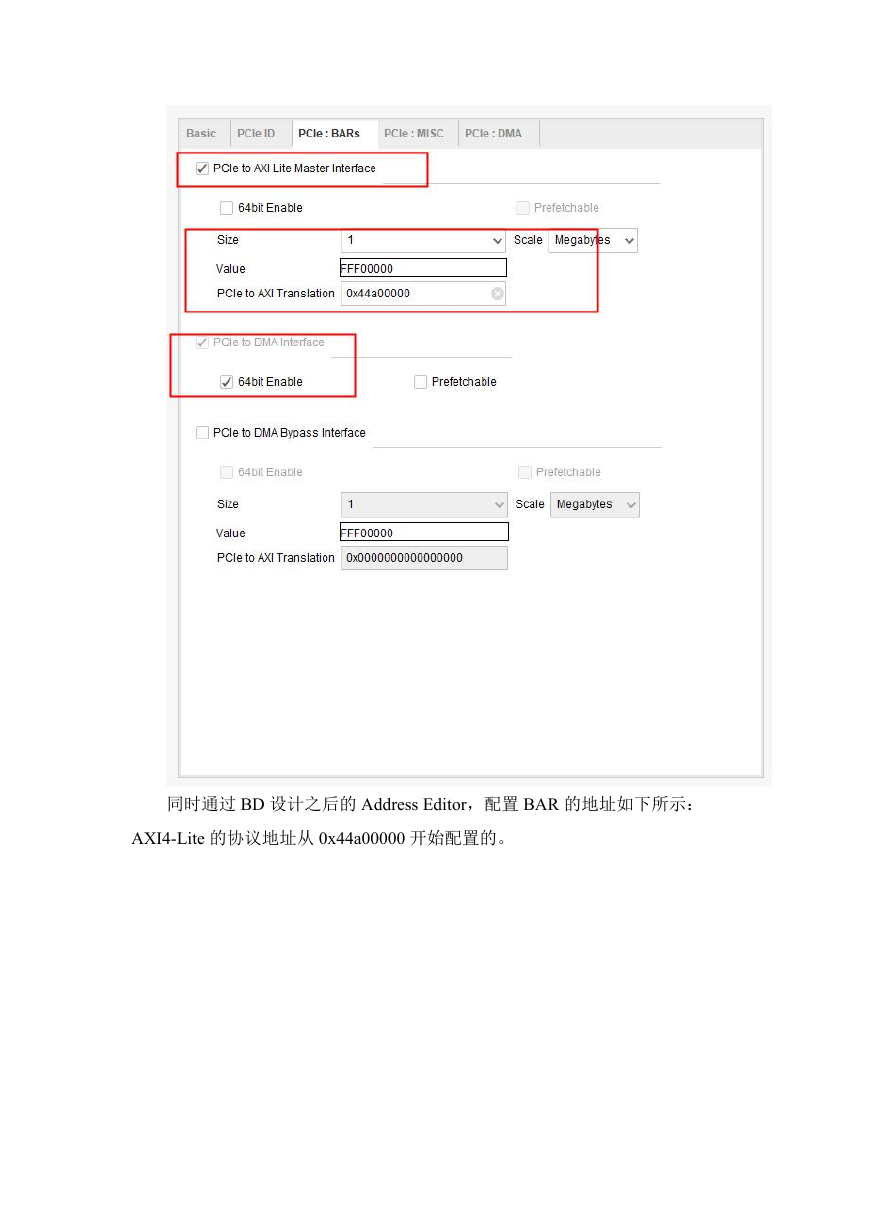

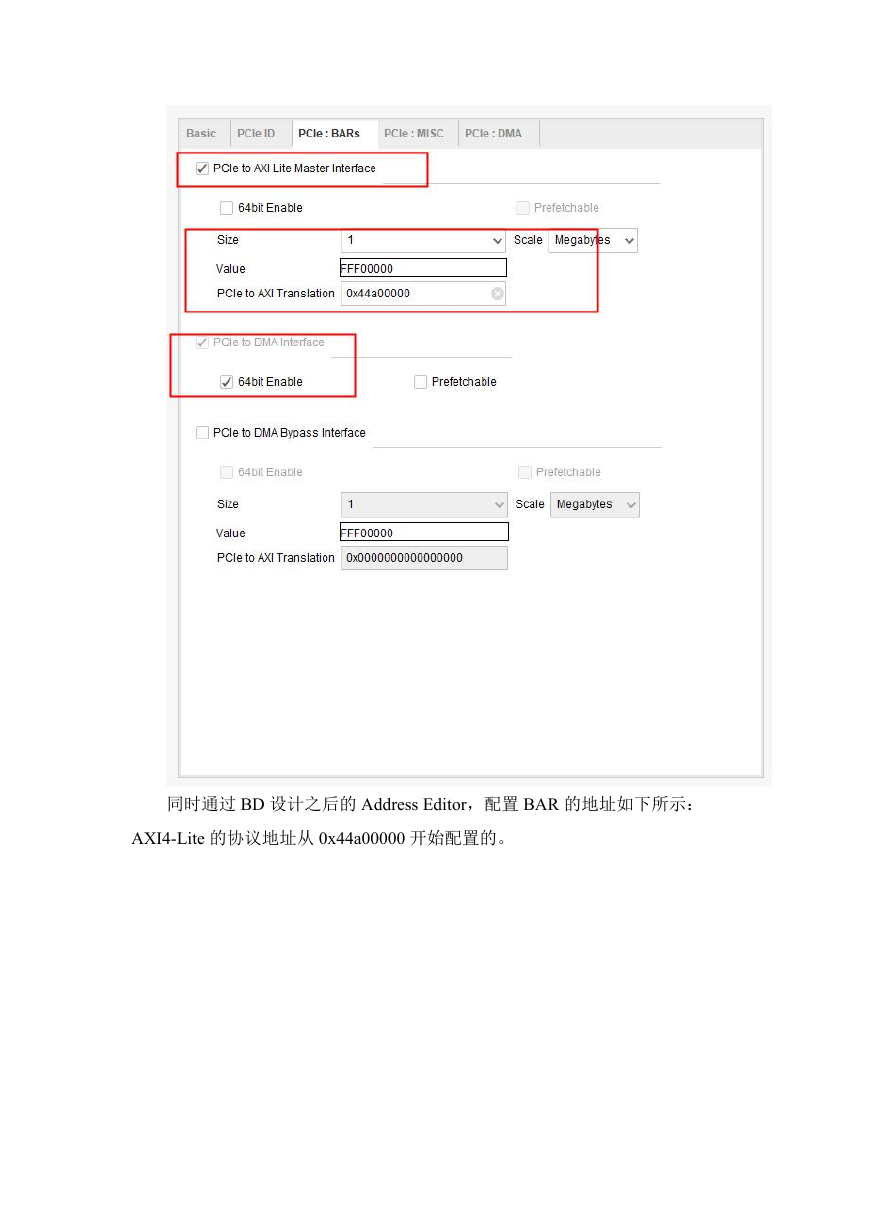

3.3 PCIe BARS 配置项

这里配置的是 PCIE 协议的内存映射,允许上位机通过 PCIE 访问内存 BAR

空间。此处为寄存器机制操作,即上位机通过 PCIE 单独读写某个地址空间。

勾选上“PCIe to AXI Lite Master Interface”,表示上位机可以通过 PCIE 访问

BAR 空间,内部配置的大小为“1M”,也可以依据实际使用进行配置。Value 默

认即可;PCIe to AXI Translation 为 BAR 在 AXI4-Lite 协议中映射的起始地址,

此处配置成了 0x44a00000。

PCIE to DMA Interface :选择 64bit 使能

其他的默认即可。

通过设置后,如图所示。

�

同时通过 BD 设计之后的 Address Editor,配置 BAR 的地址如下所示:

AXI4-Lite 的协议地址从 0x44a00000 开始配置的。

�

3.4 PCIe MISC 配置项

PCIE 中断设置

User Interrupts:用户中断, XDMA 提供 16 条中断线给用户逻辑,这里面

可以配置使用几条中断线。

Legacy Interrupt: XDMA 支持 Legacy 中断

选择 MSI 中断

注意: MSI 中断和 MSI-X 中断只能选择一个,否则会报错,如果选择 MSI 中

断,则可以选择 Legacy 中断, 如果选择了 MSI-X 中断,那么 MSI 必须取消

选择,同时 Legacy 也必须选择 None。此 IP 对于 7 系列设置有这么个问题,

如果使用 Ultrascale 系列,则可以全部选择

3.5 PCIe DMA 配置项

Number of DMA Read Channel(H2C)和 Number of DMA Write Channel(C2H)

通道数,对于 PCIE2.0 来说最大只能选择 2,也就是 XDMA 可以提供最多两个

独立的写通道和两个独立的读通道,独立的通道对于实际应用中有很大的作用,

在带宽允许的前提前,一个 PCIE 可以实现多种不同的传输功能,并且互不影响。

这里我们选择 1;

Number of Request IDs for Read (Write) channel :这个是每个通道设置

允许最大的 outstanding 数量,按照默认即可;

其他的都选则默认即可。

�

4 工程建立

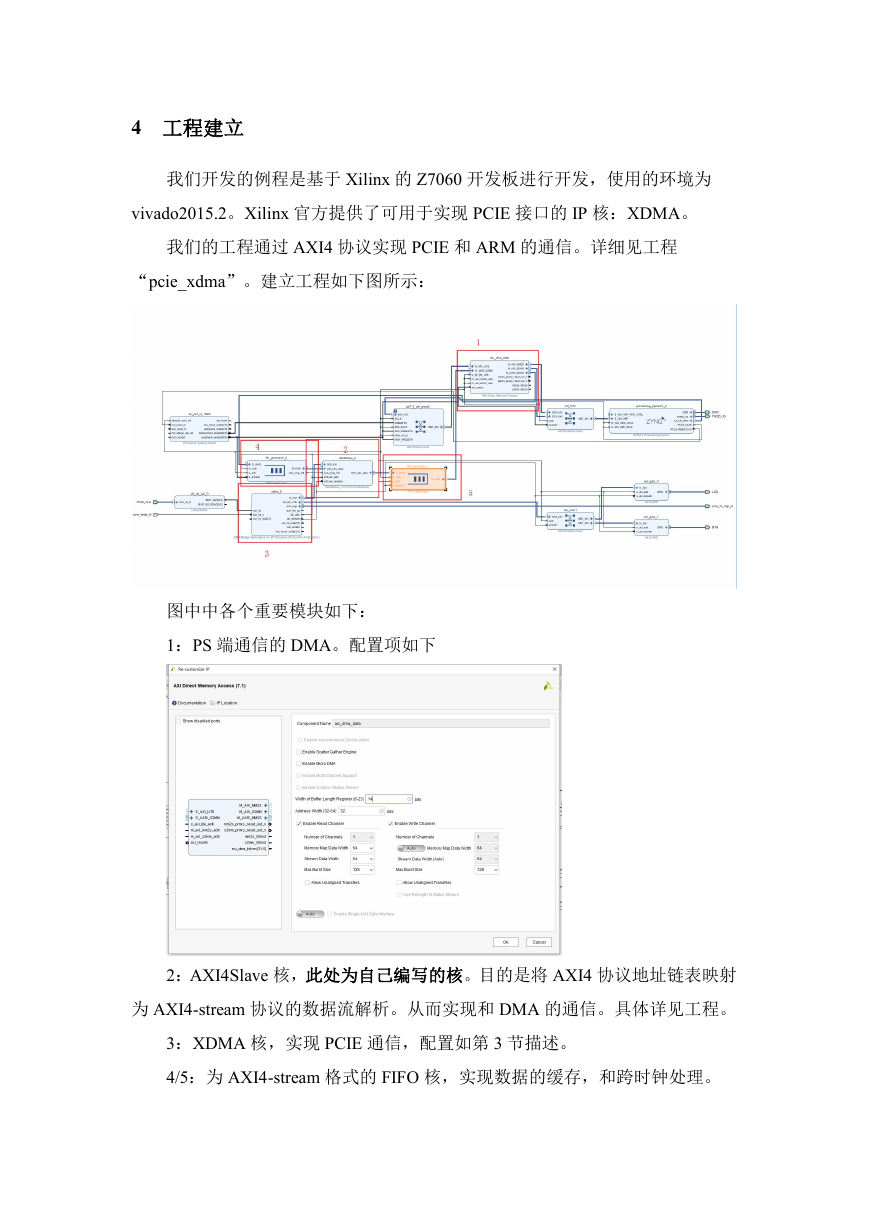

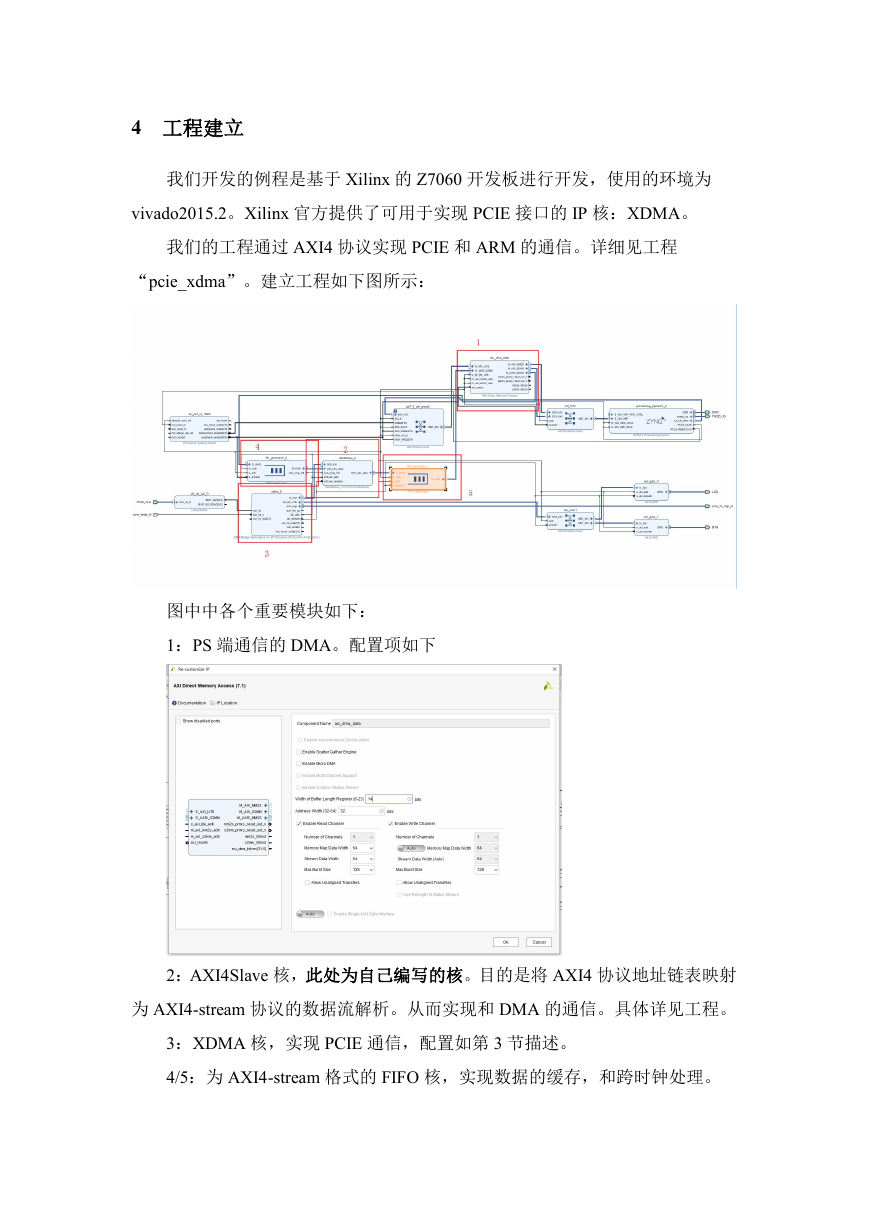

我们开发的例程是基于 Xilinx 的 Z7060 开发板进行开发,使用的环境为

vivado2015.2。Xilinx 官方提供了可用于实现 PCIE 接口的 IP 核:XDMA。

我们的工程通过 AXI4 协议实现 PCIE 和 ARM 的通信。详细见工程

“pcie_xdma”。建立工程如下图所示:

图中中各个重要模块如下:

1:PS 端通信的 DMA。配置项如下

2:AXI4Slave 核,此处为自己编写的核。目的是将 AXI4 协议地址链表映射

为 AXI4-stream 协议的数据流解析。从而实现和 DMA 的通信。具体详见工程。

3:XDMA 核,实现 PCIE 通信,配置如第 3 节描述。

4/5:为 AXI4-stream 格式的 FIFO 核,实现数据的缓存,和跨时钟处理。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc