HDMI 采集芯片 ADV7611 采集 PC 数据调试总结

开发环境:TI DM365 平台, ADV7611 采集板, CCS5.5

第一步:I2C 调通

这张是 ADV7611 读写的时序图,可以看出在写和读的时候发送地址数据的时候的停

止位信息是不同的,在写的时候是不需要停止位的,但是读的时候是要停止位的。如果

I2C 在硬件没问题的时候可以考虑是不是这方面的问题。

第二步:map 配置:

根据官方推荐配置进行配置:

[cpp] view plain copy

1.

2.

3.

4.

5.

6.

7.

8.

0x98, 0xFF, 0x80,

// I2C reset

0x98, 0xF4, 0x80,// CEC SLAVE ADDRESS

0x98, 0xF5, 0x7C,// INFOFRAME SLAVE ADDRESS

0x98, 0xF8, 0x4C,// DPLL SLAVE ADDRESS

0x98, 0xF9, 0x64,// KSV SLAVE ADDRESS

0x98, 0xFA, 0x6C,// EDID SLAVE ADDRESS

0x98, 0xFB, 0x68,// HDMI SLAVE ADDRESS

0x98, 0xFD, 0x44,// CP SLAVE ADDRESS

第三步:EDID

EDID 里面主要是定义了这显示设备所支持的图像分辨率,支持的声音格式,声音通道,及 3D 等等,其目

的是告诉外接设备我所支持的特性,让外接设备输出一个我所支持的 timing,否则外接设备输出的 timing

并不支持的话那就没有图像,声音的显示了。ADV7611 在上电后需要配置 EDID 使得输出端读取 EDID

的内容然后配置相应的输出,下面是相应的 EDID 配置:

�

[cpp] view plain copy

{

unsigned char vga_edid[256]

=

1.

2.

3.

4.

0x00, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0x00, //00

5.

0x06, 0x8F, 0x07, 0x11, 0x01, 0x00, 0x00, 0x00, //08

6.

0x17, 0x11, 0x01, 0x03, 0x80, 0x0C, 0x09, 0x78, //10

7.

0x0A, 0x1E, 0xAC, 0x98, 0x59, 0x56, 0x85, 0x28, //18

8.

0x29, 0x52, 0x57, 0x00, 0x00, 0x00, 0x01, 0x01, //20

9.

0x01, 0x01, 0x01, 0x01, 0x01, 0x01, 0x01, 0x01, //28

10. 0x01, 0x01, 0x01, 0x01, 0x01, 0x01, 0x8C, 0x0A, //30

11. 0xD0, 0x8A, 0x20, 0xE0, 0x2D, 0x10, 0x10, 0x3E, //38

12. 0x96, 0x00, 0x81, 0x60, 0x00, 0x00, 0x00, 0x18, //40

13. 0x01, 0x1D, 0x80, 0x18, 0x71, 0x1C, 0x16, 0x20, //48

14. 0x58, 0x2C, 0x25, 0x00, 0x81, 0x49, 0x00, 0x00, //50

15. 0x00, 0x9E, 0x00, 0x00, 0x00, 0xFC, 0x00, 0x56, //58

16. 0x41, 0x2D, 0x31, 0x38, 0x30, 0x39, 0x41, 0x0A, //60

17. 0x20, 0x20, 0x20, 0x20, 0x00, 0x00, 0x00, 0xFD, //68

18. 0x00, 0x17, 0x3D, 0x0D, 0x3E, 0x11, 0x00, 0x0A, //70

19. 0x20, 0x20, 0x20, 0x20, 0x20, 0x20, 0x01, 0x1C, //78

20. 0x02, 0x03, 0x34, 0x71, 0x4D, 0x82, 0x05, 0x04,

21. 0x01, 0x10, 0x11, 0x14, 0x13, 0x1F,0x06, 0x15,

22. 0x03, 0x12, 0x35, 0x0F, 0x7F, 0x07,0x17, 0x1F,

23. 0x38, 0x1F, 0x07, 0x30, 0x2F, 0x07,0x72, 0x3F,

24. 0x7F, 0x72, 0x57, 0x7F, 0x00, 0x37,0x7F, 0x72,

25. 0x83, 0x4F, 0x00, 0x00, 0x67, 0x03,0x0C, 0x00,

26. 0x10, 0x00, 0x88, 0x2D, 0x00, 0x00,0x00, 0xFF,

27. 0x00, 0x0A, 0x20, 0x20, 0x20, 0x20,0x20, 0x20,

28. 0x20, 0x20, 0x20, 0x20, 0x20, 0x20,0x00, 0x00,

29. 0x00, 0xFF, 0x00, 0x0A, 0x20, 0x20,0x20, 0x20,

30. 0x20, 0x20, 0x20, 0x20, 0x20, 0x20,0x20, 0x20,

31. 0x00, 0x00, 0x00, 0xFF, 0x00, 0x0A,0x20, 0x20,

32. 0x20, 0x20, 0x20, 0x20, 0x20, 0x20,0x20, 0x20,

33. 0x20, 0x20, 0x00, 0x00, 0x00, 0x00,0x00, 0x00,

34. 0x00, 0x00, 0x00, 0x00, 0x00, 0x00,0x00, 0x00,

35. 0x00, 0x00, 0x00, 0x00, 0x00, 0x00,0x00, 0xDA,

36. };

37. void i2c_program_edid(unsigned char *data, int length)

38. {

39. unsigned long i;

40. ADV7611_Write(0x64, 0x77, 0x00);

41. ADV7611_Write(0x64, 0x74, 0x00);

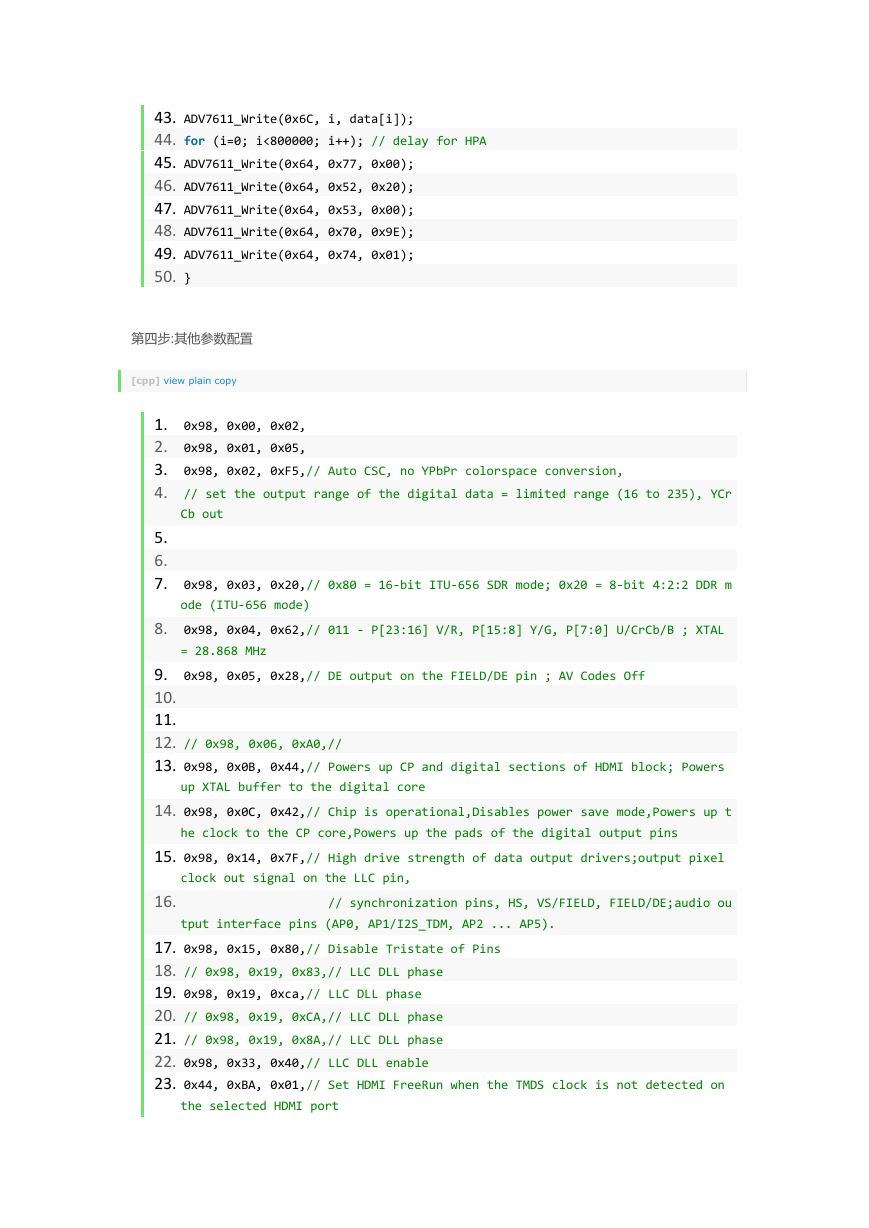

42. for (i=0; i

43. ADV7611_Write(0x6C, i, data[i]);

44. for (i=0; i<800000; i++); // delay for HPA

45. ADV7611_Write(0x64, 0x77, 0x00);

46. ADV7611_Write(0x64, 0x52, 0x20);

47. ADV7611_Write(0x64, 0x53, 0x00);

48. ADV7611_Write(0x64, 0x70, 0x9E);

49. ADV7611_Write(0x64, 0x74, 0x01);

50. }

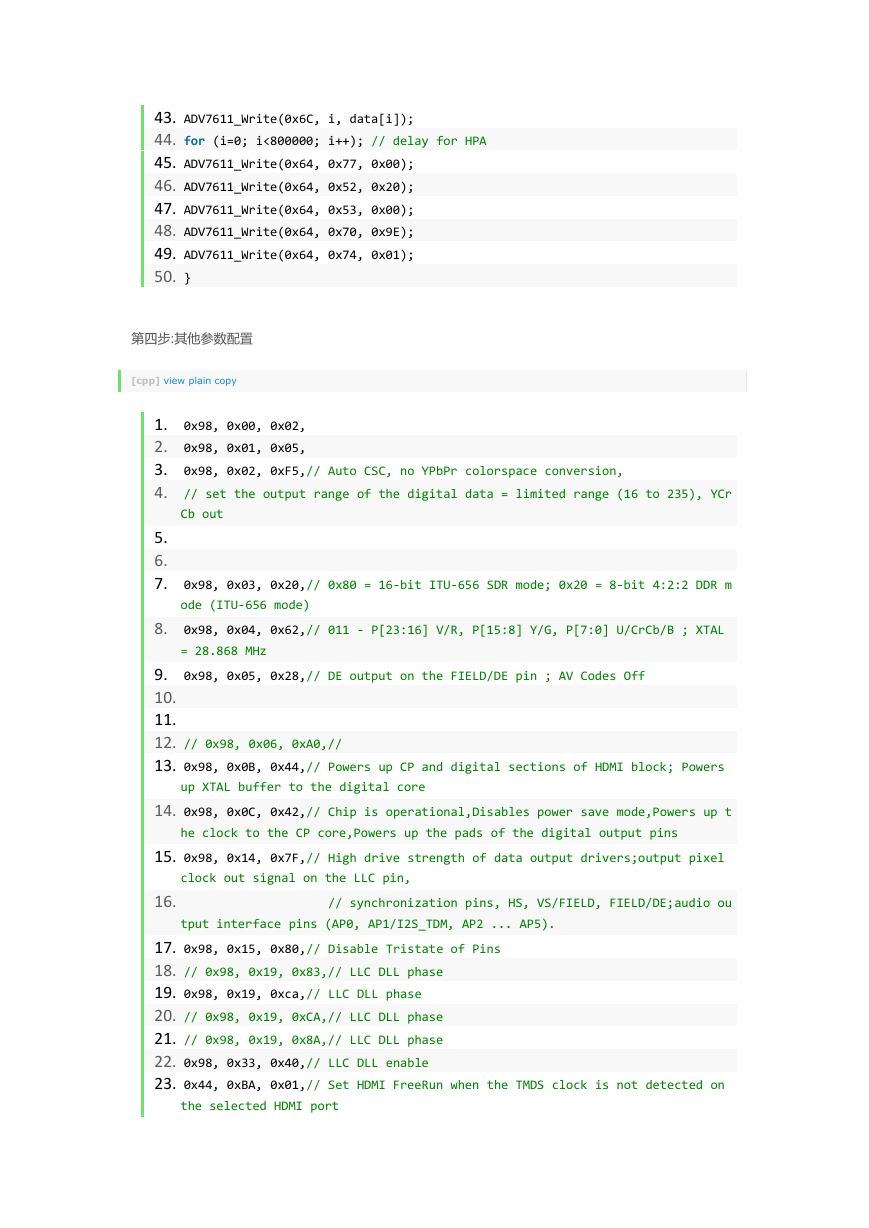

第四步:其他参数配置

[cpp] view plain copy

0x98, 0x00, 0x02,

0x98, 0x01, 0x05,

0x98, 0x02, 0xF5,// Auto CSC, no YPbPr colorspace conversion,

// set the output range of the digital data = limited range (16 to 235), YCr

Cb out

1.

2.

3.

4.

5.

6.

7.

8.

0x98, 0x03, 0x20,// 0x80 = 16-bit ITU-656 SDR mode; 0x20 = 8-bit 4:2:2 DDR m

ode (ITU-656 mode)

0x98, 0x04, 0x62,// 011 - P[23:16] V/R, P[15:8] Y/G, P[7:0] U/CrCb/B ; XTAL

= 28.868 MHz

0x98, 0x05, 0x28,// DE output on the FIELD/DE pin ; AV Codes Off

9.

10.

11.

12. // 0x98, 0x06, 0xA0,//

13. 0x98, 0x0B, 0x44,// Powers up CP and digital sections of HDMI block; Powers

up XTAL buffer to the digital core

14. 0x98, 0x0C, 0x42,// Chip is operational,Disables power save mode,Powers up t

he clock to the CP core,Powers up the pads of the digital output pins

15. 0x98, 0x14, 0x7F,// High drive strength of data output drivers;output pixel

clock out signal on the LLC pin,

16.

// synchronization pins, HS, VS/FIELD, FIELD/DE;audio ou

tput interface pins (AP0, AP1/I2S_TDM, AP2 ... AP5).

17. 0x98, 0x15, 0x80,// Disable Tristate of Pins

18. // 0x98, 0x19, 0x83,// LLC DLL phase

19. 0x98, 0x19, 0xca,// LLC DLL phase

20. // 0x98, 0x19, 0xCA,// LLC DLL phase

21. // 0x98, 0x19, 0x8A,// LLC DLL phase

22. 0x98, 0x33, 0x40,// LLC DLL enable

23. 0x44, 0xBA, 0x01,// Set HDMI FreeRun when the TMDS clock is not detected on

the selected HDMI port

�

24. // 0x44, 0x3E, 0x01,

25. 0x64, 0x00, 0x40,

26. 0x64, 0x40, 0x81,// Disable HDCP 1.1 features

27. 0x68, 0x9B, 0x03,// ADI recommended setting

28. 0x68, 0xC1, 0x01,// ADI recommended setting

29. 0x68, 0xC2, 0x01,// ADI recommended setting

30. 0x68, 0xC3, 0x01,// ADI recommended setting

31. 0x68, 0xC4, 0x01,// ADI recommended setting

32. 0x68, 0xC5, 0x01,// ADI recommended setting

33. 0x68, 0xC6, 0x01,// ADI recommended setting

34. 0x68, 0xC7, 0x01,// ADI recommended setting

35. 0x68, 0xC8, 0x01,// ADI recommended setting

36. 0x68, 0xC9, 0x01,// ADI recommended setting

37. 0x68, 0xCA, 0x01,// ADI recommended setting

38. 0x68, 0xCB, 0x01,// ADI recommended setting

39. 0x68, 0xCC, 0x01,// ADI recommended setting

40. 0x68, 0x00, 0x00,// Set HDMI Input Port A

41. 0x68, 0x83, 0xFE,// Enable clock terminator for port A

42. 0x68, 0x6F, 0x0C,// ADI recommended setting

43. 0x68, 0x85, 0x1F,// ADI recommended setting

44. 0x68, 0x87, 0x70,// ADI recommended setting

45. 0x68, 0x8D, 0x04,// LF gain equalizer settings for dynamic mode range 1

46. 0x68, 0x8E, 0x1E,// HF gain equalizer settings for dynamic mode range 1

47. 0x68, 0x1A, 0x8A,// unmute audio

48. 0x68, 0x57, 0xDA,// ADI recommended setting

49. 0x68, 0x58, 0x01,// ADI recommended setting

50. 0x68, 0x03, 0x98,

// DIS_I2C_ZERO_COMPR

51. 0x68, 0x75, 0x10,// DDC drive strength

这个配置是 yuv4:2:2 8bit 的配置

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc