FPGA 中用定制 ROM 产生正弦信号

简介:

本文详细介绍了在 fpga 中定制 ROM,以及用查表法产生正弦波的方法,并借助 matlab 加以

验证。编译软件用 xilinx13.1.

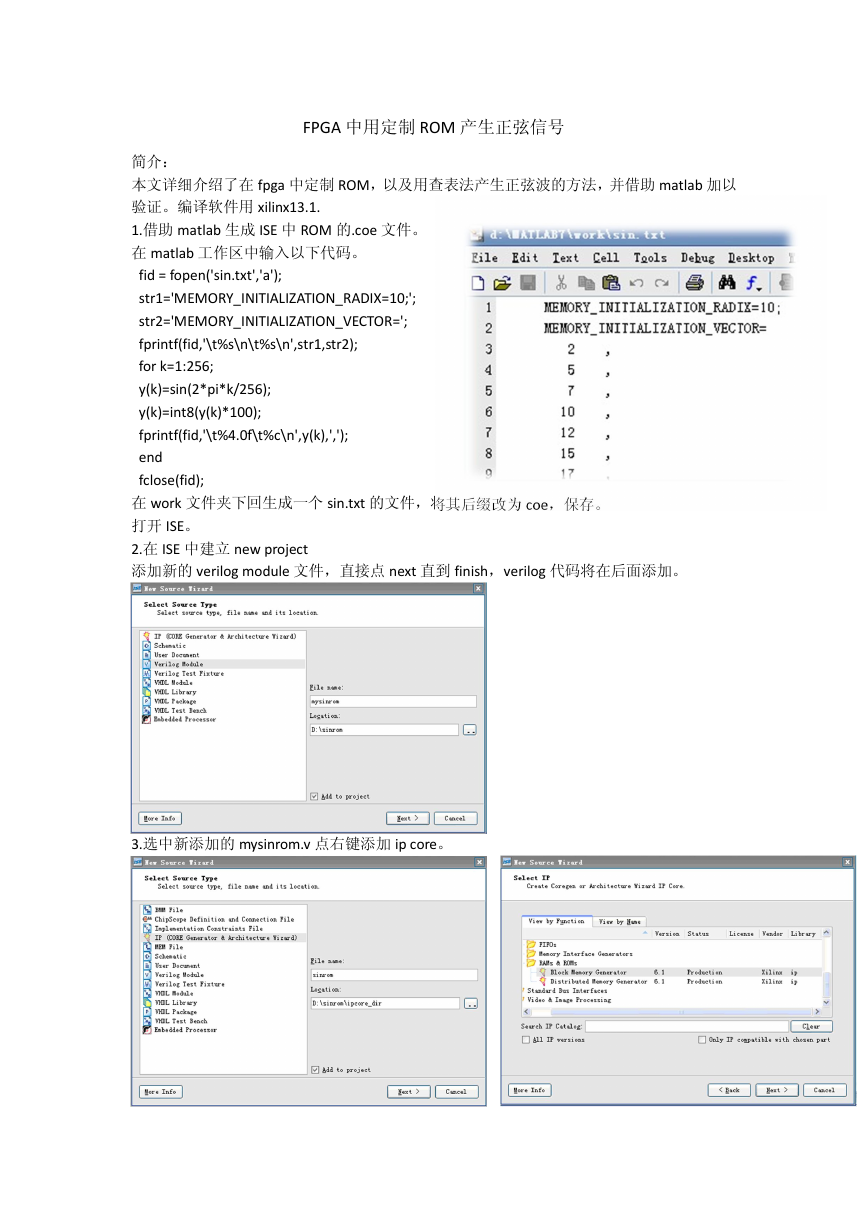

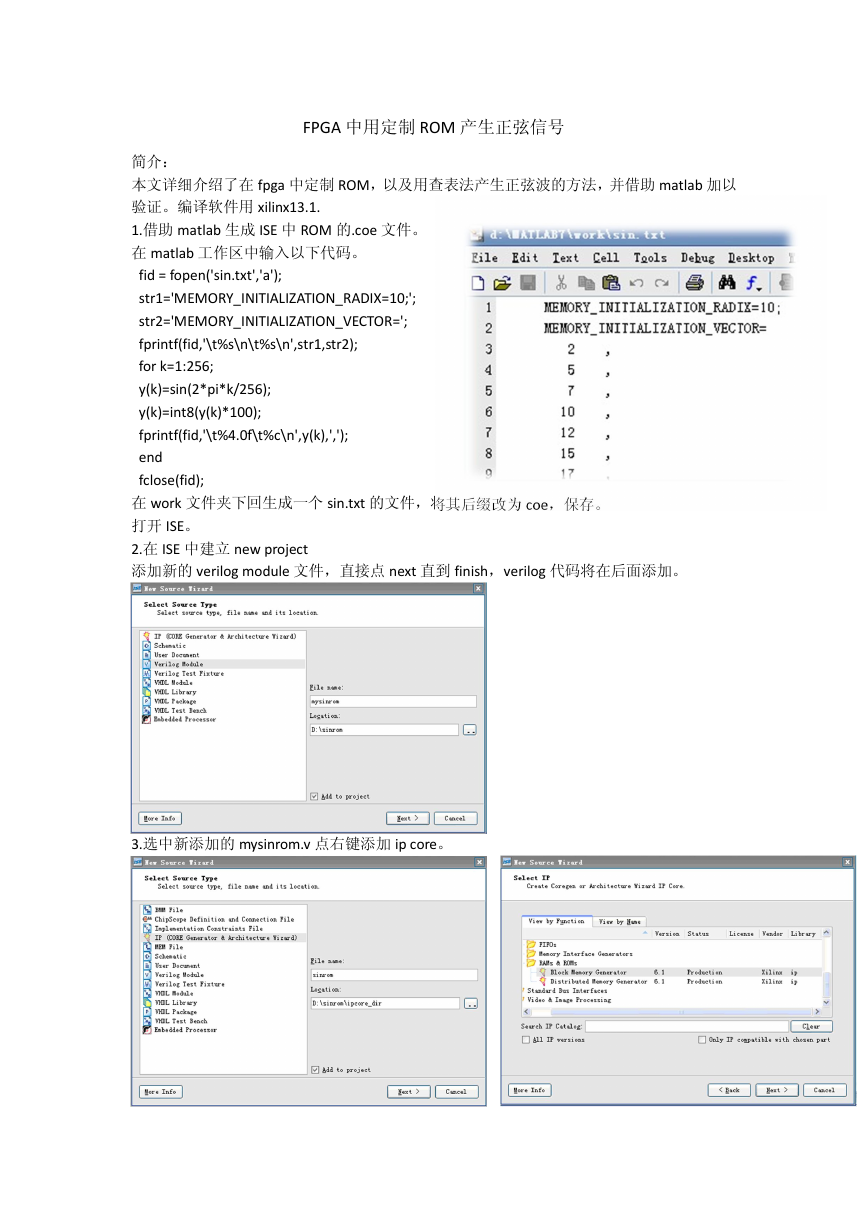

1.借助 matlab 生成 ISE 中 ROM 的.coe 文件。

在 matlab 工作区中输入以下代码。

fid = fopen('sin.txt','a');

str1='MEMORY_INITIALIZATION_RADIX=10;';

str2='MEMORY_INITIALIZATION_VECTOR=';

fprintf(fid,'\t%s\n\t%s\n',str1,str2);

for k=1:256;

y(k)=sin(2*pi*k/256);

y(k)=int8(y(k)*100);

fprintf(fid,'\t%4.0f\t%c\n',y(k),',');

end

fclose(fid);

在 work 文件夹下回生成一个 sin.txt 的文件,将其后缀改为 coe,保存。

打开 ISE。

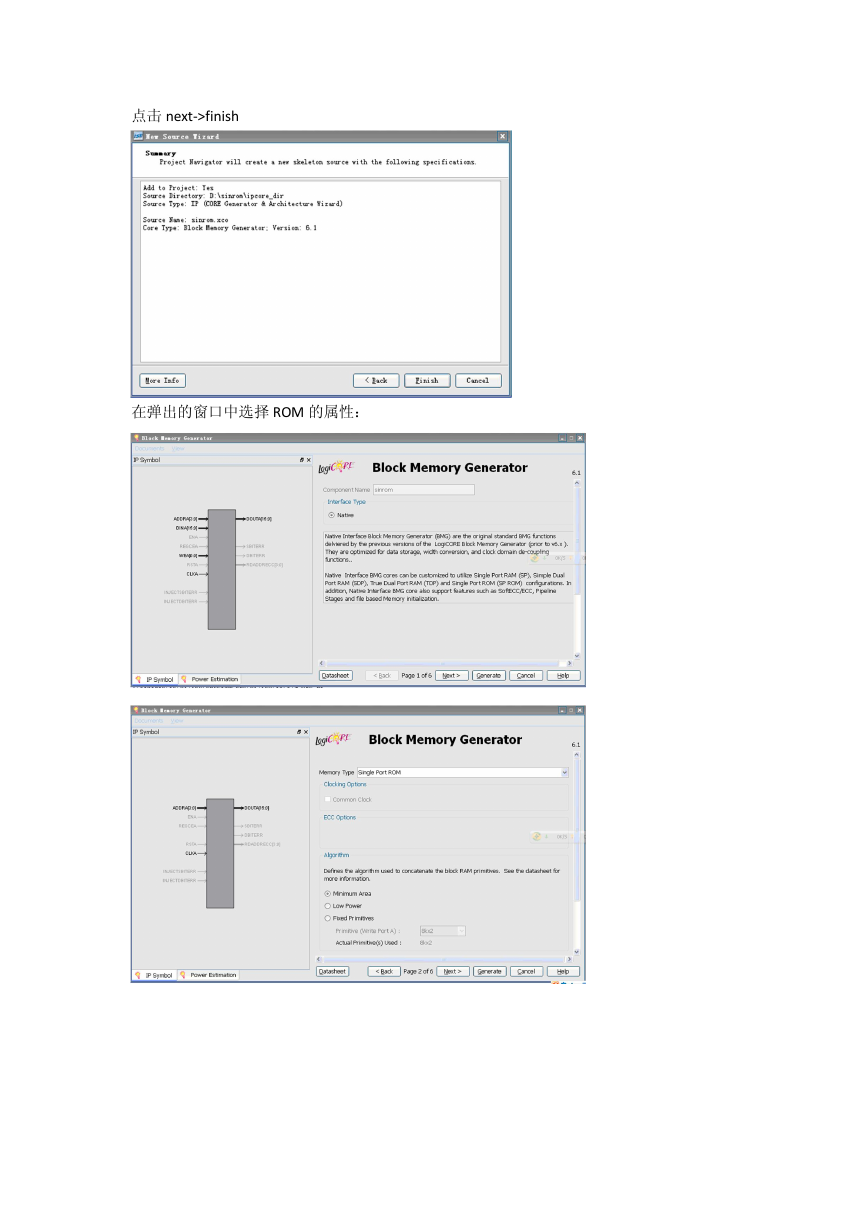

2.在 ISE 中建立 new project

添加新的 verilog module 文件,直接点 next 直到 finish,verilog 代码将在后面添加。

3.选中新添加的 mysinrom.v 点右键添加 ip core。

�

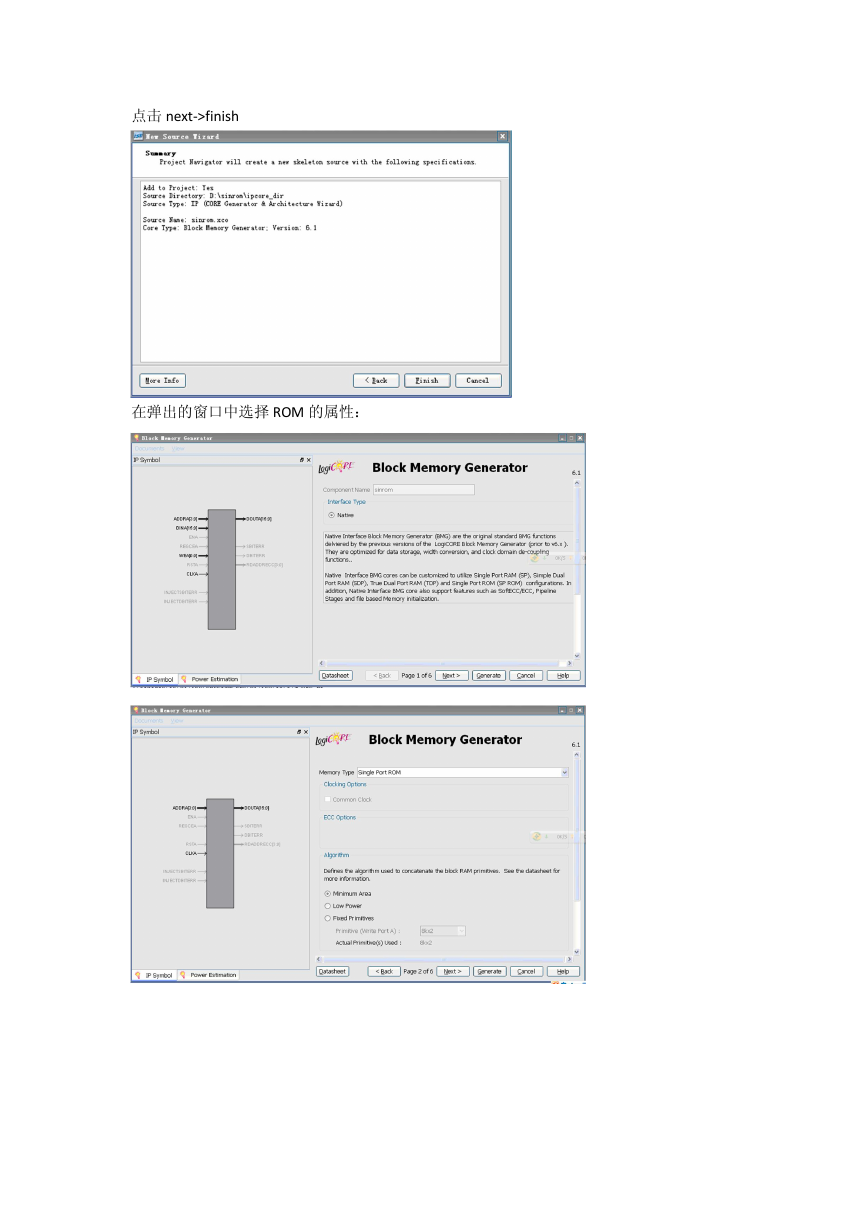

点击 next->finish

在弹出的窗口中选择 ROM 的属性:

�

选择 sin.coe 存放的路径,一直点 next 到 finish。在 hierachy 窗口可以看到新添加的 sinrom。

双击 view HDL Functional…可查看接口代码。

�

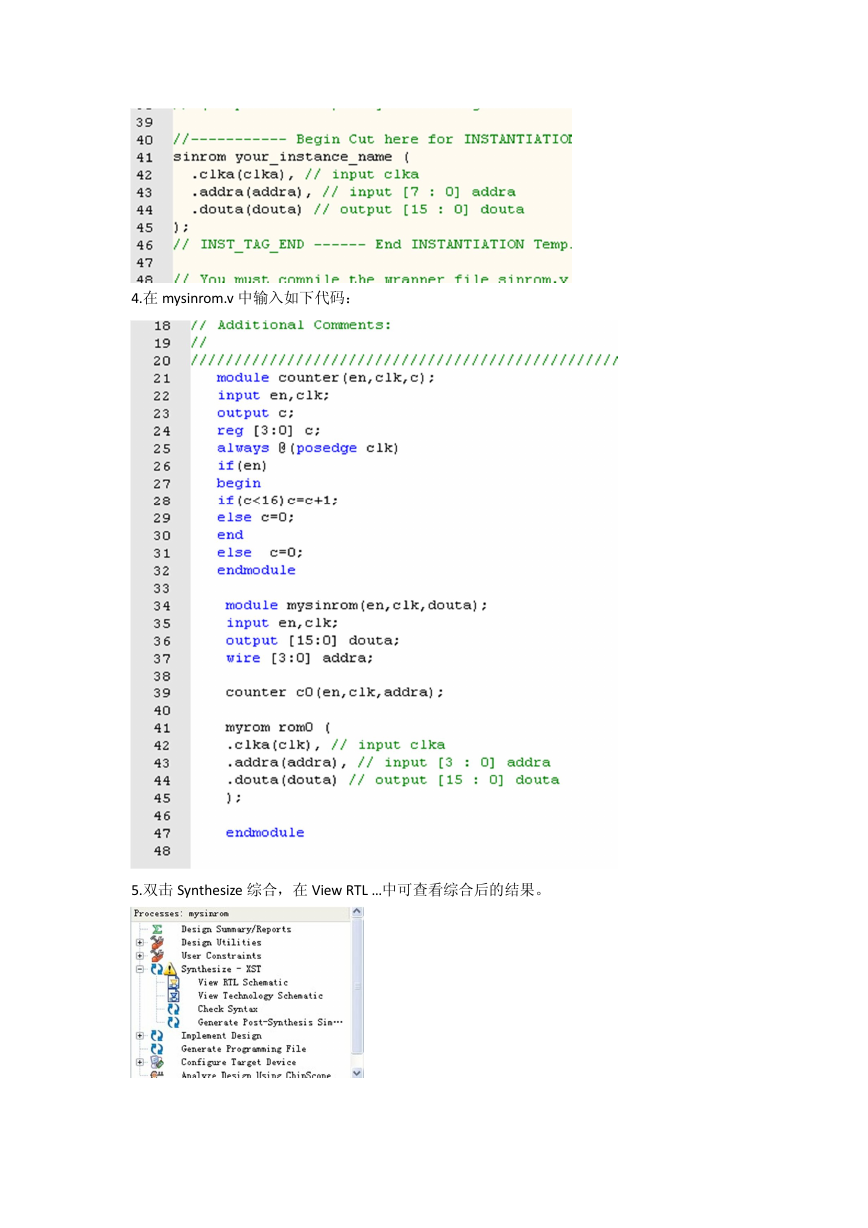

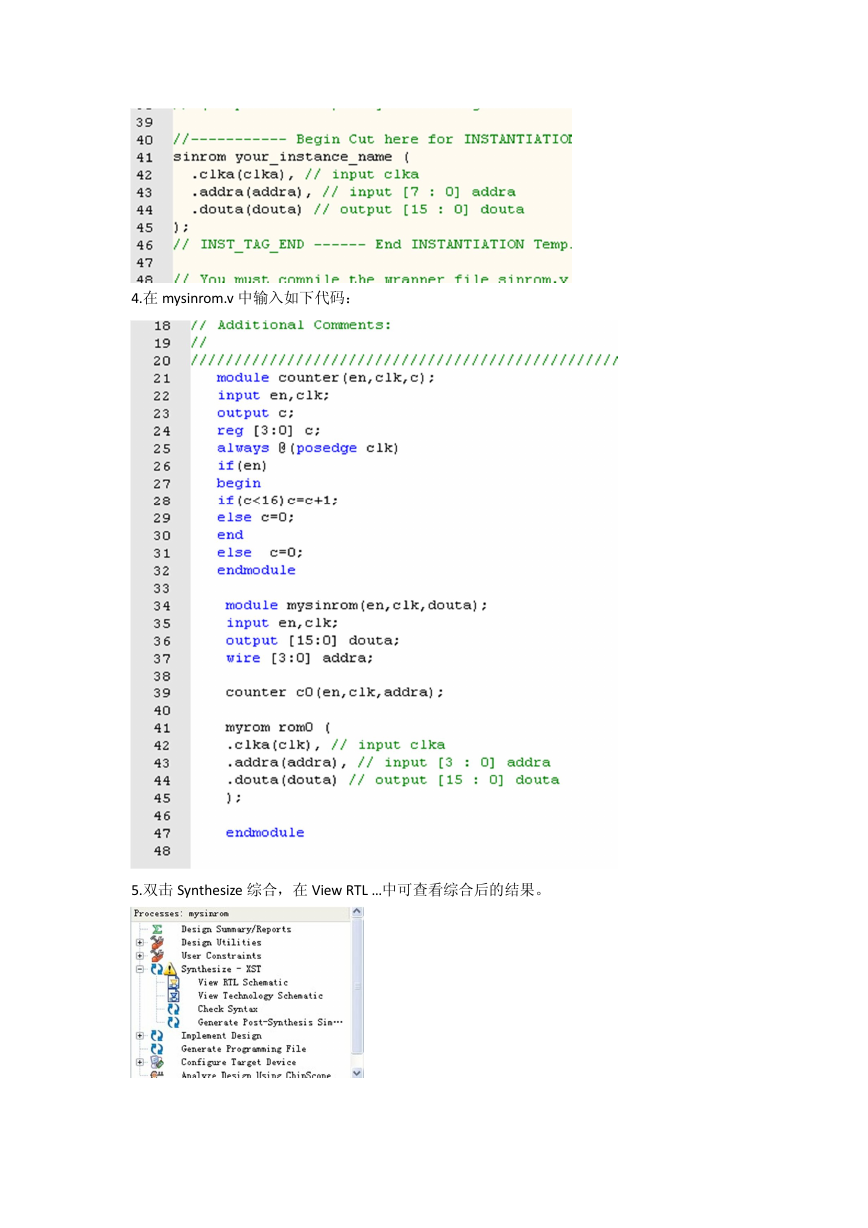

4.在 mysinrom.v 中输入如下代码:

5.双击 Synthesize 综合,在 View RTL …中可查看综合后的结果。

�

顶层示意图以及内部模块连接

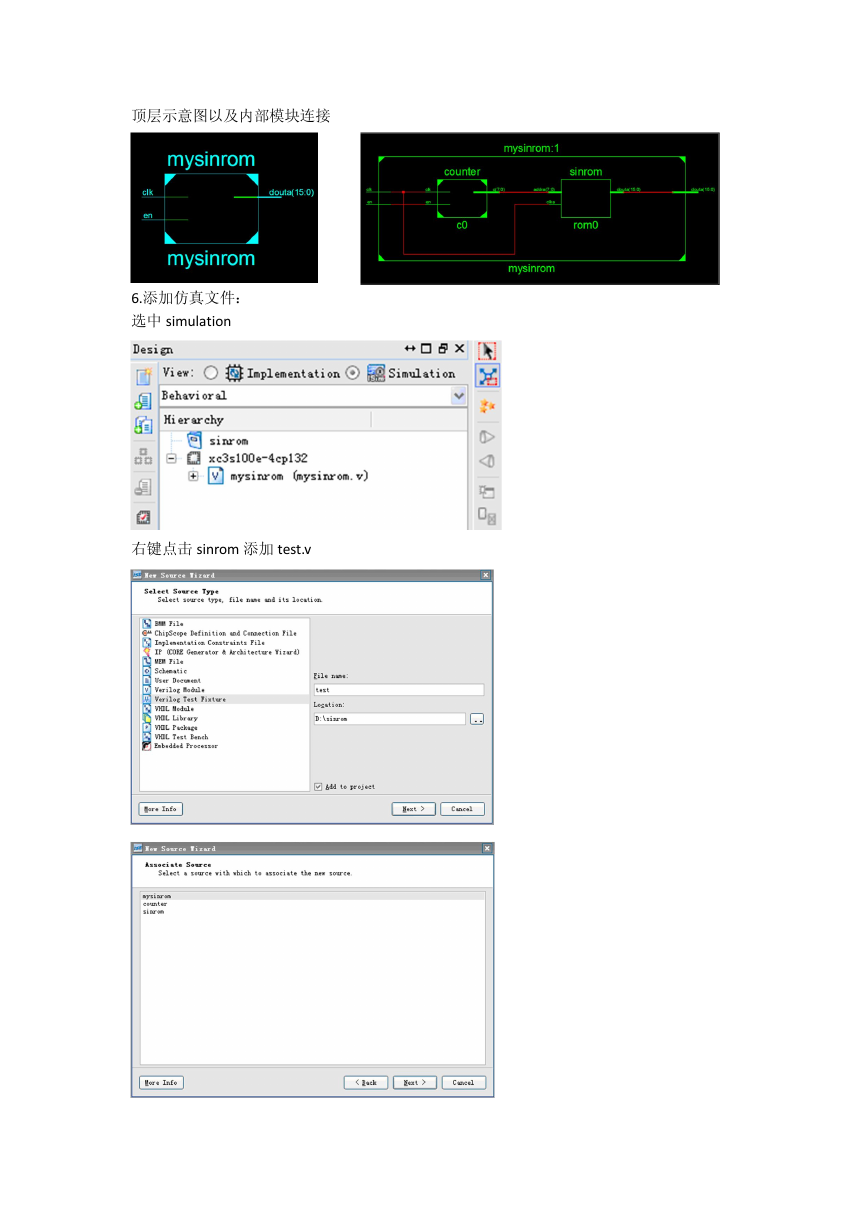

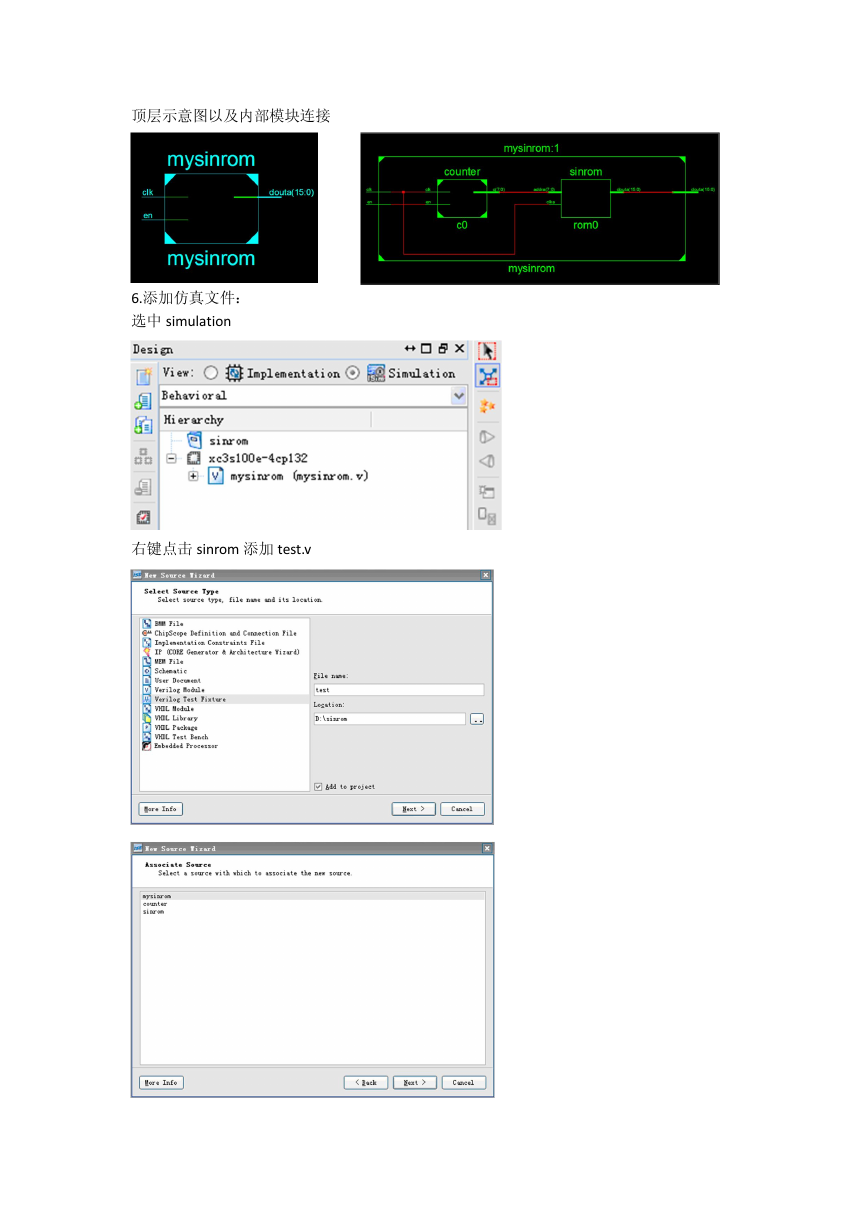

6.添加仿真文件:

选中 simulation

右键点击 sinrom 添加 test.v

�

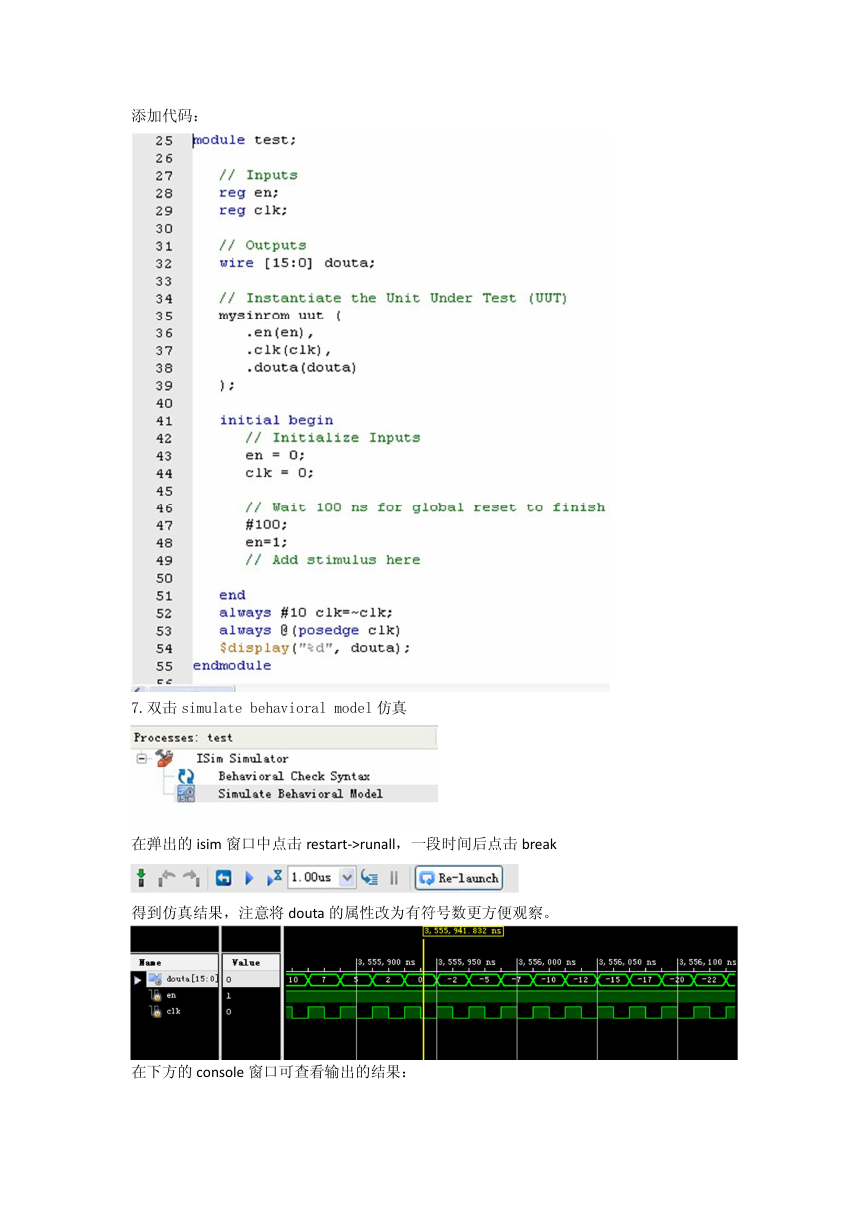

添加代码:

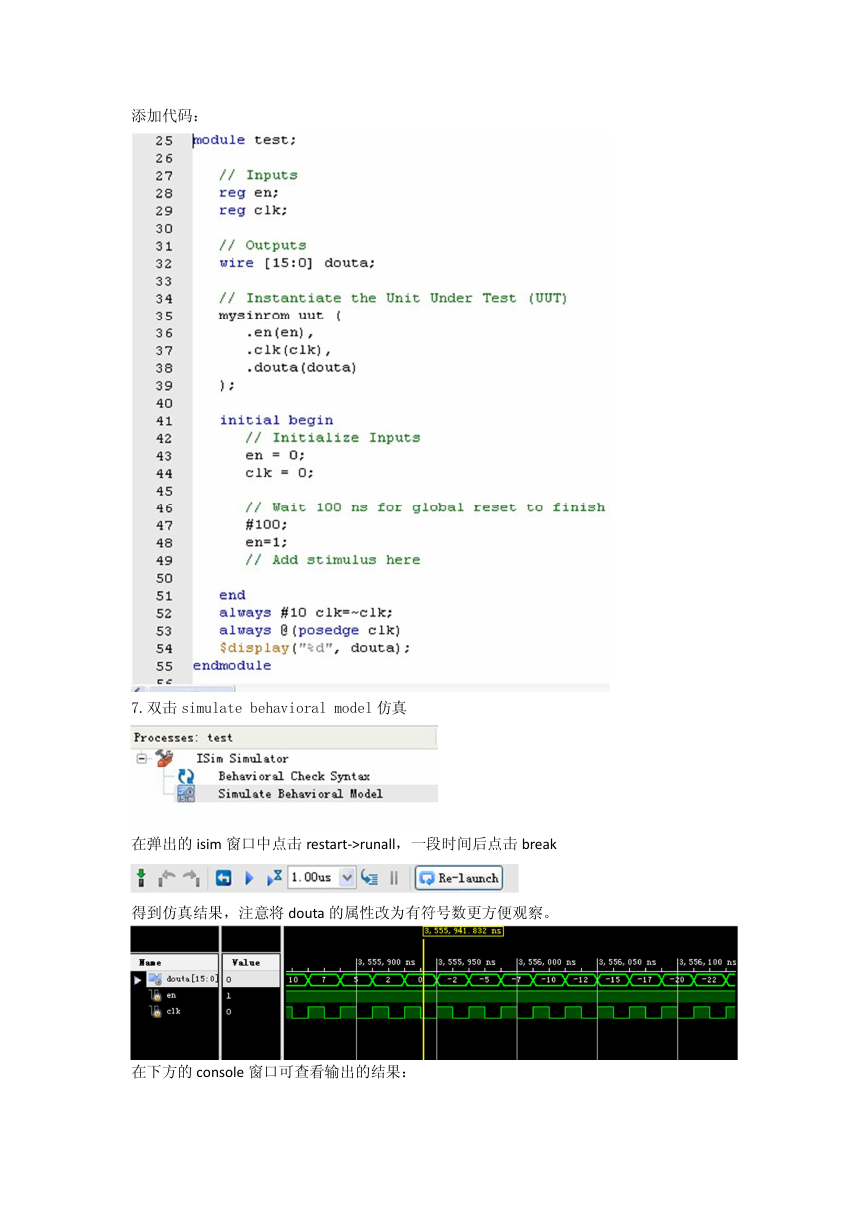

7.双击 simulate behavioral model 仿真

在弹出的 isim 窗口中点击 restart->runall,一段时间后点击 break

得到仿真结果,注意将 douta 的属性改为有符号数更方便观察。

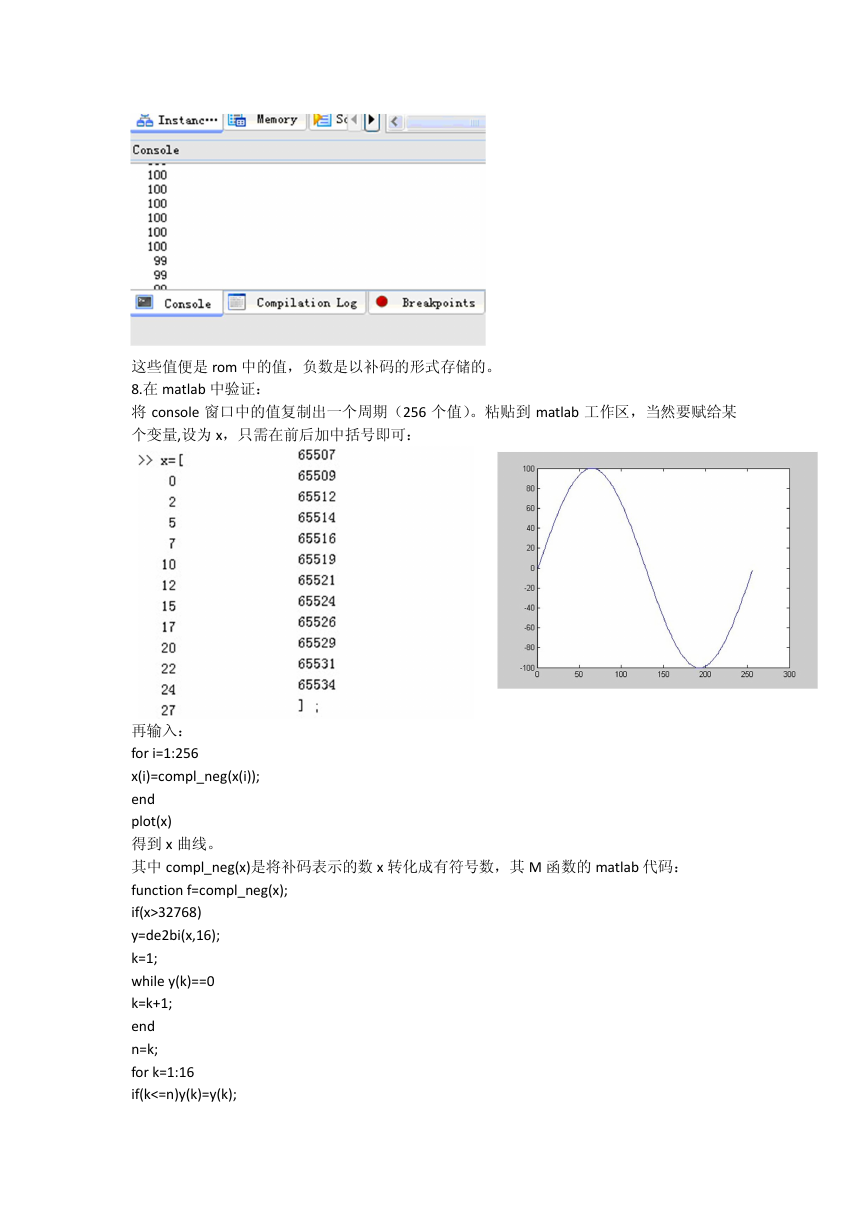

在下方的 console 窗口可查看输出的结果:

�

这些值便是 rom 中的值,负数是以补码的形式存储的。

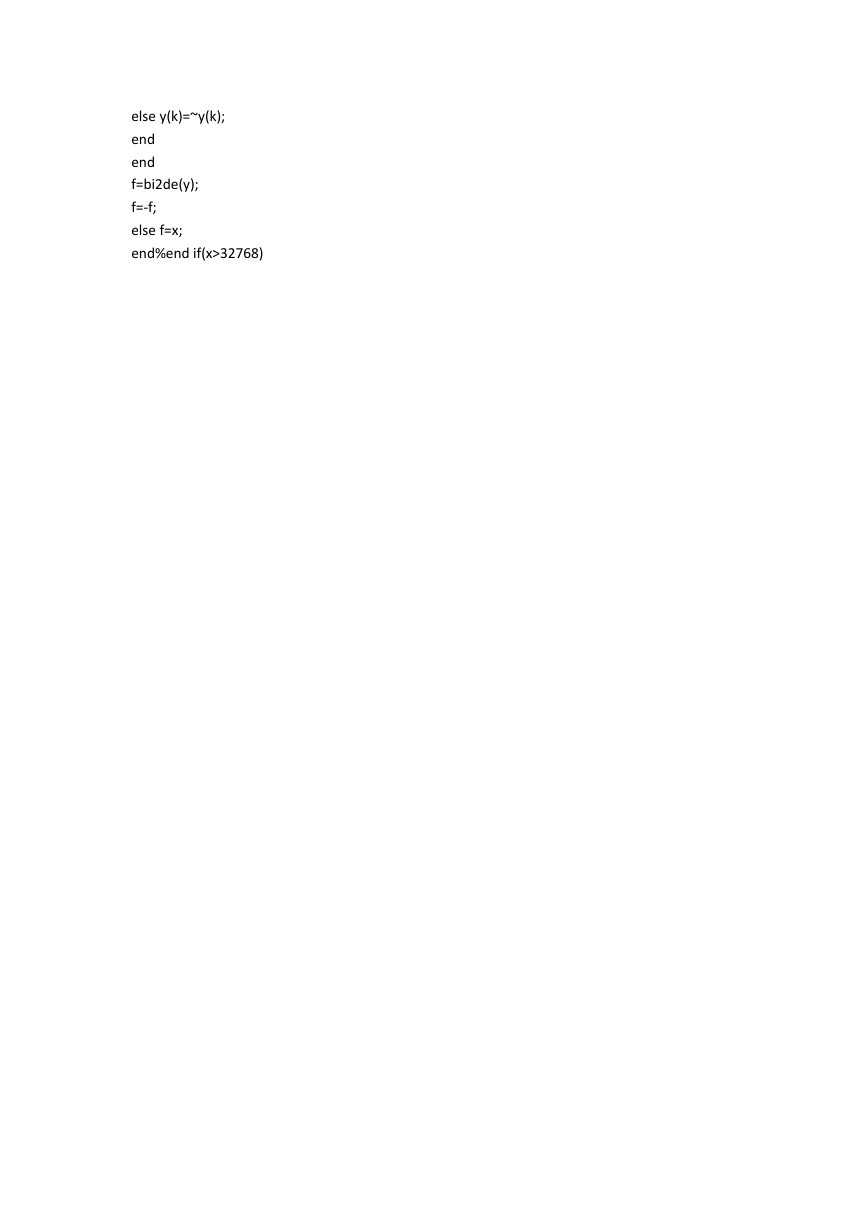

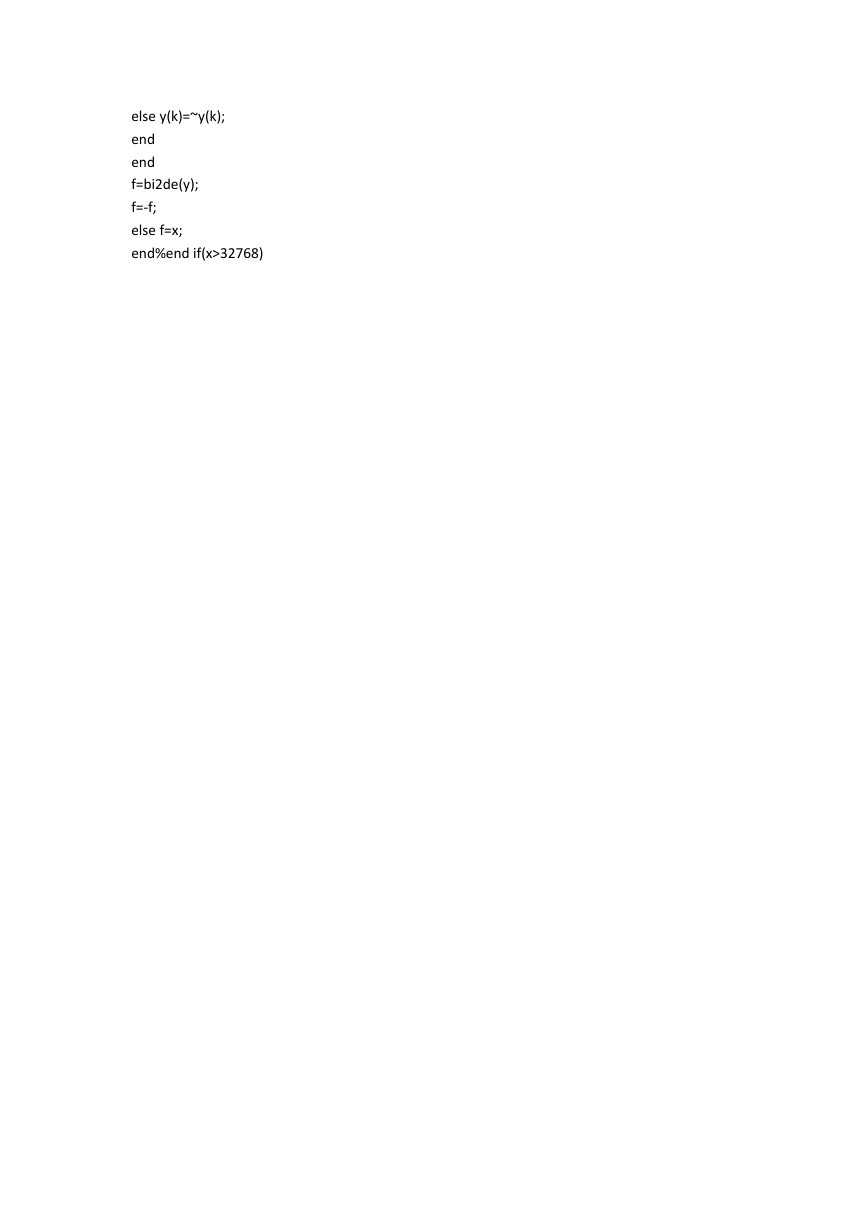

8.在 matlab 中验证:

将 console 窗口中的值复制出一个周期(256 个值)。粘贴到 matlab 工作区,当然要赋给某

个变量,设为 x,只需在前后加中括号即可:

再输入:

for i=1:256

x(i)=compl_neg(x(i));

end

plot(x)

得到 x 曲线。

其中 compl_neg(x)是将补码表示的数 x 转化成有符号数,其 M 函数的 matlab 代码:

function f=compl_neg(x);

if(x>32768)

y=de2bi(x,16);

k=1;

while y(k)==0

k=k+1;

end

n=k;

for k=1:16

if(k<=n)y(k)=y(k);

�

else y(k)=~y(k);

end

end

f=bi2de(y);

f=-f;

else f=x;

end%end if(x>32768)

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc