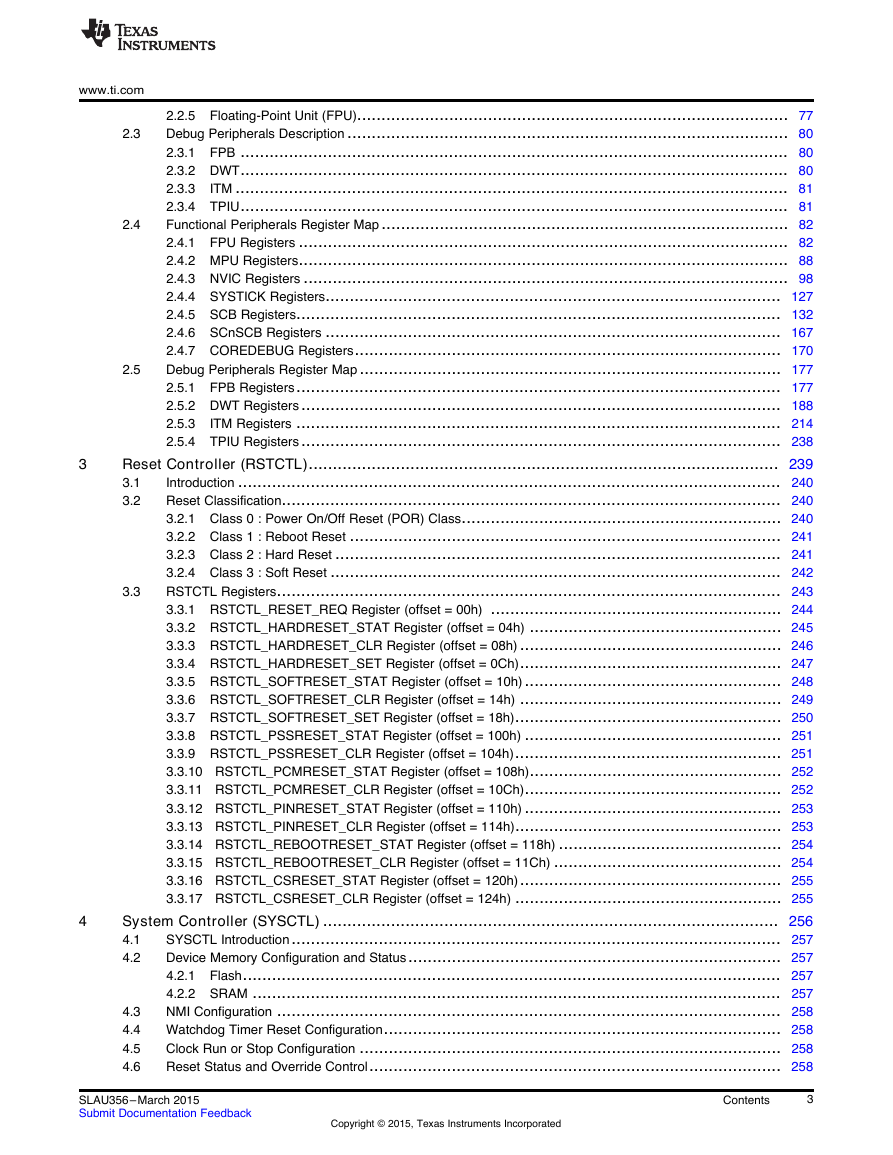

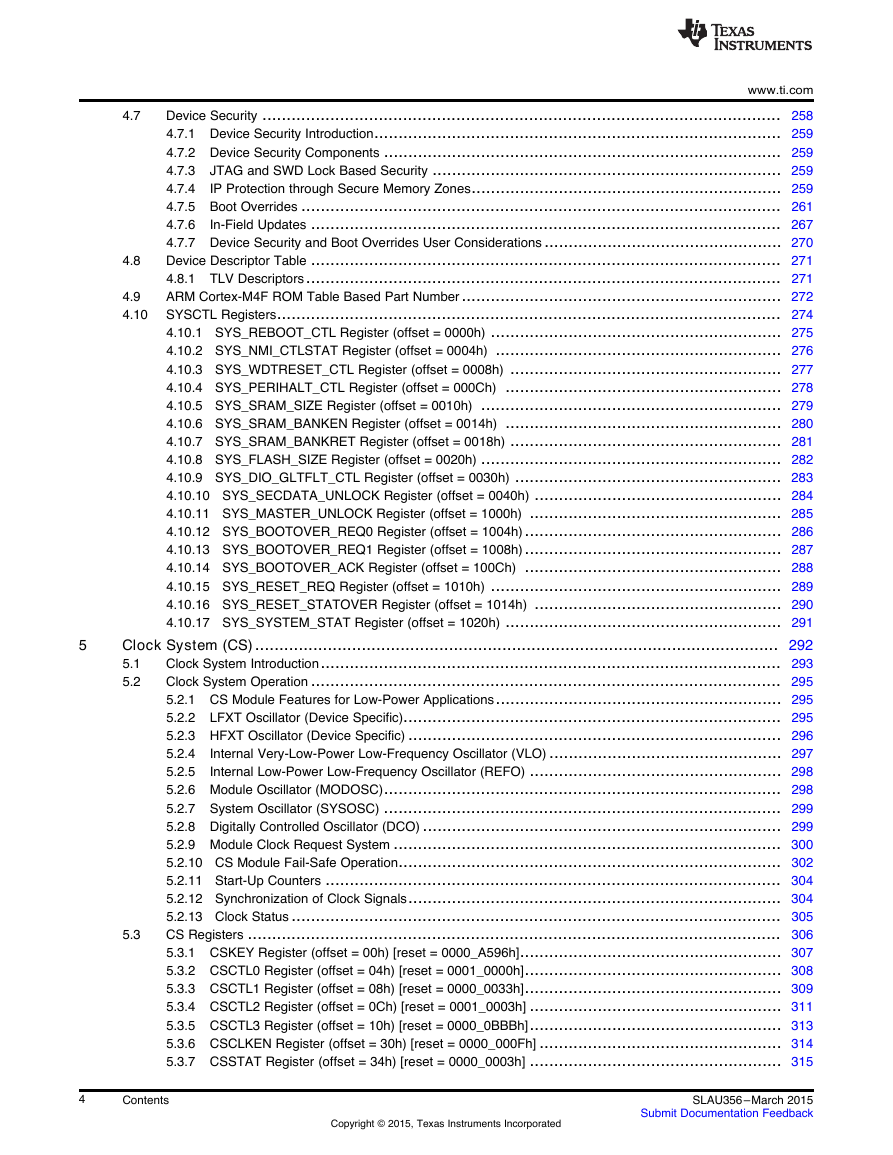

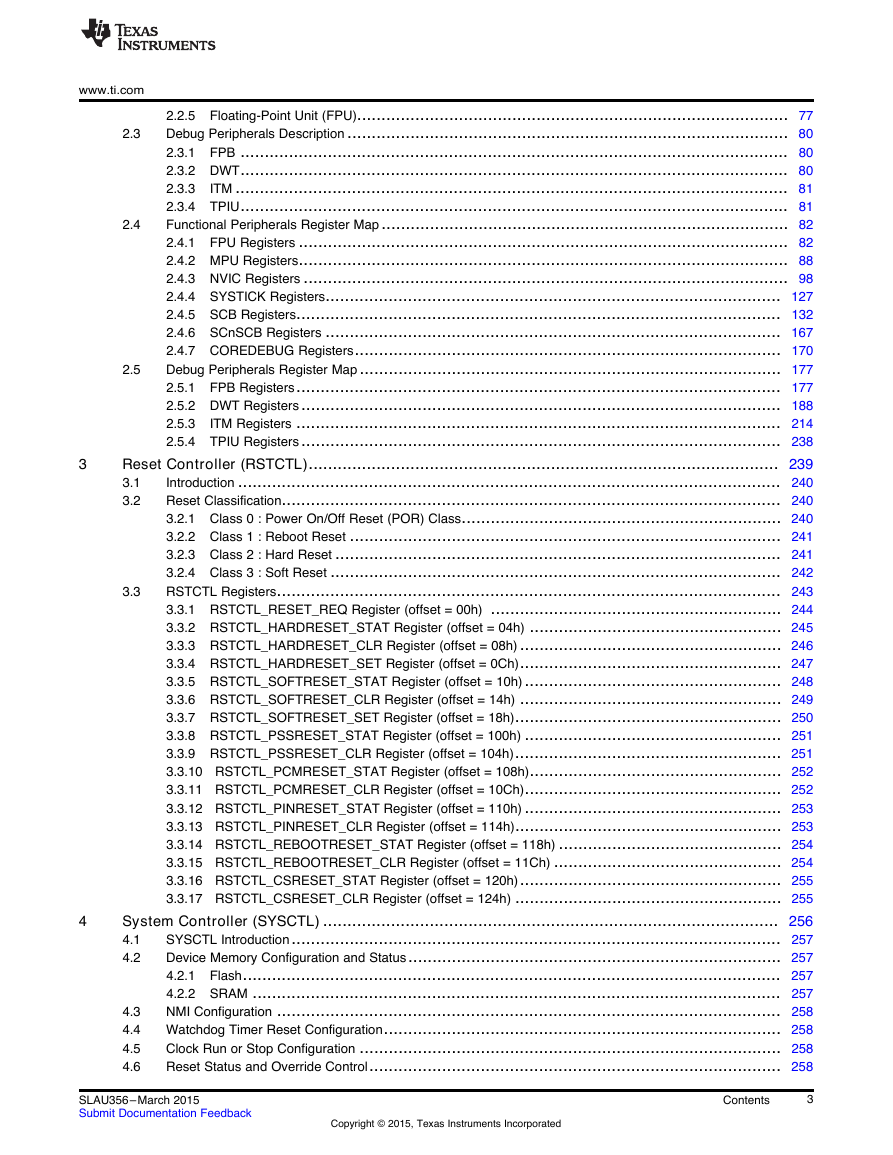

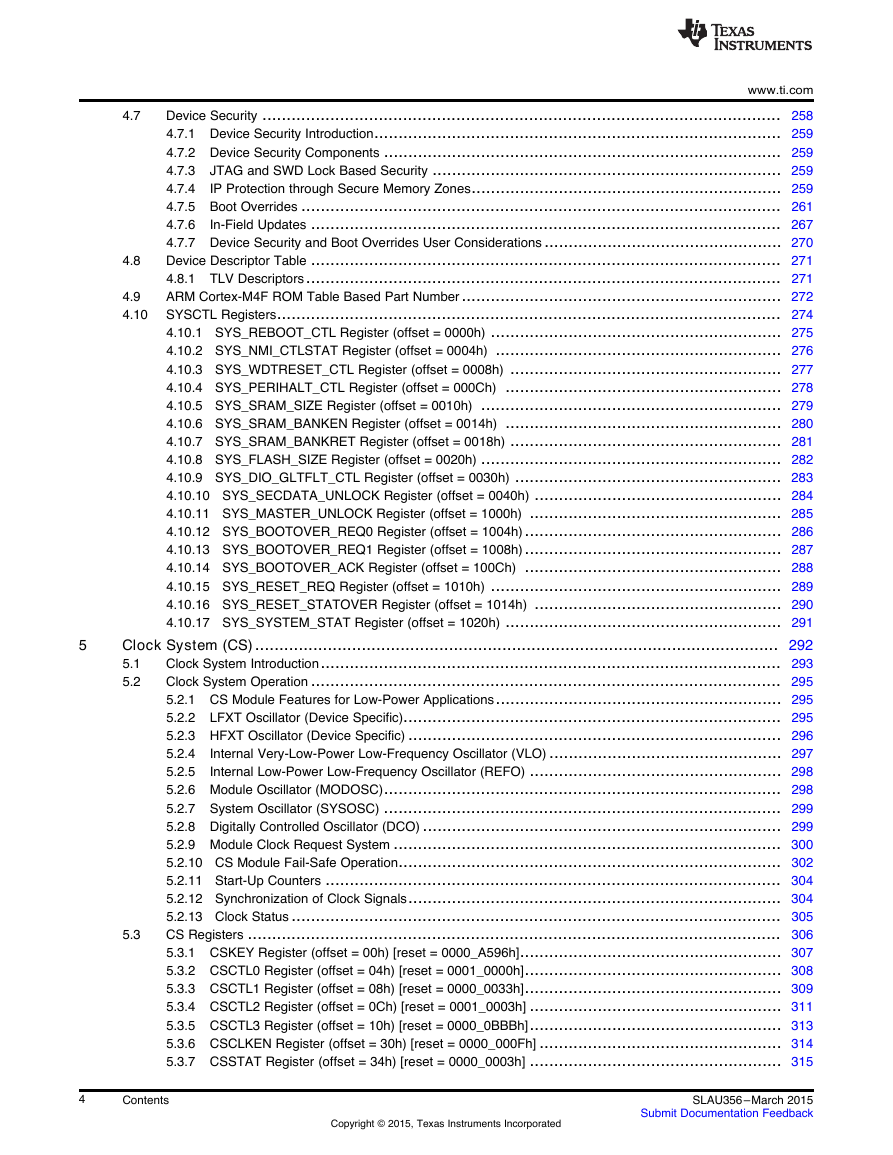

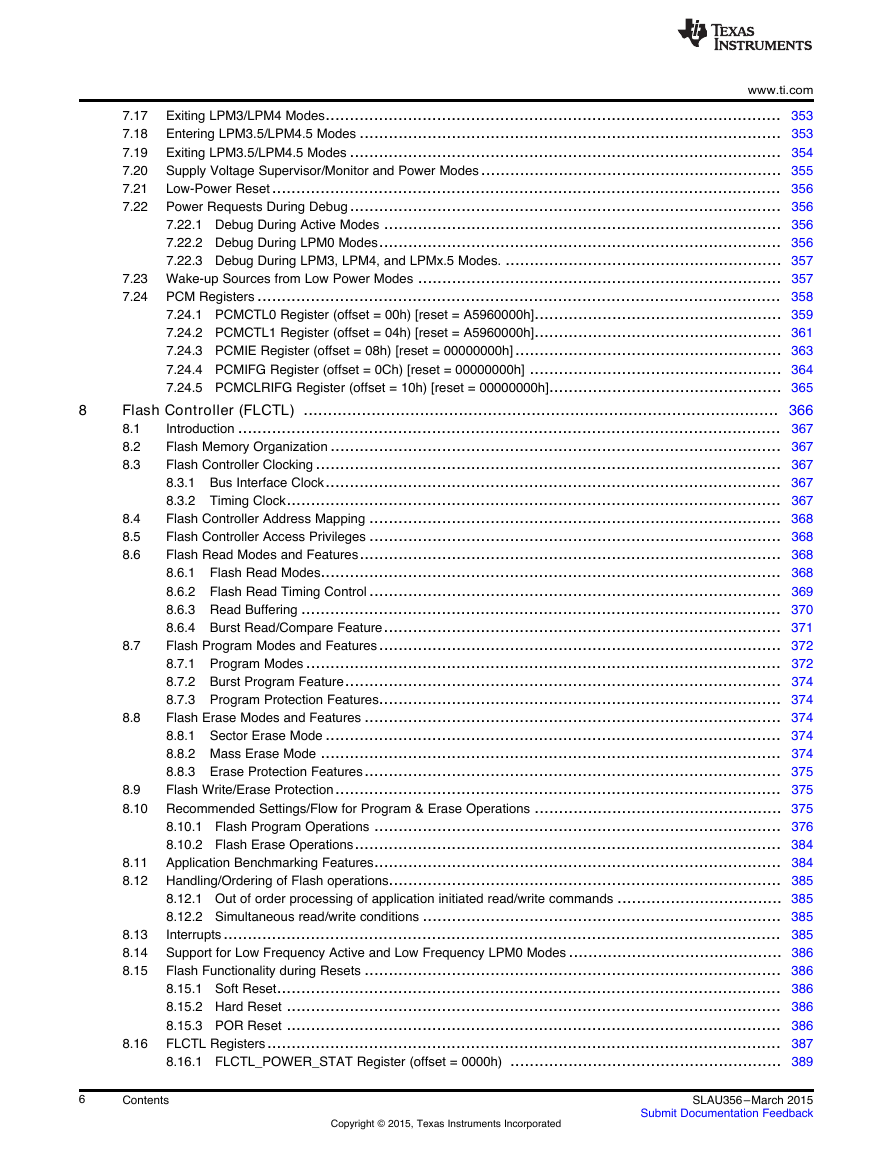

Table of Contents

Preface

1 Cortex-M4F Processor

1.1 Introduction

1.1.1 Block Diagram

1.2 Overview

1.2.1 Bus Interface

1.2.2 Integrated Configurable Debug

1.2.3 Cortex-M4F System Component Details

1.3 Programming Model

1.3.1 Processor Mode and Privilege Levels for Software Execution

1.3.2 Stacks

1.3.3 Register Map

1.3.4 Register Descriptions

1.3.4.1 Register n: Cortex General Purpose Registers

1.3.4.2 Register 14: Stack Pointer (SP, R13)

1.3.4.3 Register 15: Link Register (LR, R14)

1.3.4.4 Register 16: Program Counter (PC, R15)

1.3.4.5 Register 17: Program Status Register (PSR)

1.3.4.6 Register 18: Priority Mask Register (PRIMASK)

1.3.4.7 Register 19: FaultMask Register (FAULTMASK)

1.3.4.8 Register 20: Base Priority Mask Register (BASEPRI)

1.3.4.9 Register 21: Control Register (CONTROL)

1.3.4.10 Register 22: Floating-Point Status Control (FPSC)

1.3.5 Exceptions and Interrupts

1.3.6 Data Types

1.4 Memory Model

1.4.1 Memory Regions, Types, and Attributes

1.4.2 Memory System Ordering of Memory Accesses

1.4.3 Behavior of Memory Accesses

1.4.4 Software Ordering of Memory Accesses

1.4.5 Bit-Banding

1.4.5.1 Directly Accessing an Alias Region

1.4.5.2 Directly Accessing a Bit-Band Region

1.4.6 Data Storage

1.5 Exception Model

1.5.1 Exception States

1.5.2 Exception Types

1.5.3 Exception Handlers

1.5.4 Vector Table

1.5.5 Exception Priorities

1.5.6 Interrupt Priority Grouping

1.5.7 Level and Pulse Interrupts

1.5.8 Exception Entry and Return

1.5.8.1 Exception Entry

1.5.8.2 Exception Return

1.6 Fault Handling

1.6.1 Fault Types

1.6.2 Fault Escalation and Hard Faults

1.6.3 Fault Status Registers and Fault Address Registers

1.6.4 Lockup

1.7 Power Management

1.8 Instruction Set Summary

2 Cortex-M4F Peripherals

2.1 Cortex-M4F Peripherals Introduction

2.2 Functional Peripherals Description

2.2.1 System Timer (SysTick)

2.2.2 Nested Vectored Interrupt Controller (NVIC)

2.2.2.1 Level-Sensitive and Pulse Interrupts

2.2.2.2 Hardware and Software Control of Interrupts

2.2.3 System Control Block (SCB)

2.2.4 Memory Protection Unit (MPU)

2.2.4.1 Updating an MPU Region

2.2.4.2 MPU Access Permission Attributes

2.2.4.2.1 MPU Configuration

2.2.4.3 MPU Mismatch

2.2.5 Floating-Point Unit (FPU)

2.2.5.1 FPU Views of the Register Bank

2.2.5.2 Modes of Operation

2.2.5.3 Compliance With the IEEE 754 Standard

2.2.5.4 Complete Implementation of the IEEE 754 Standard

2.2.5.5 IEEE 754 Standard Implementation Choices

2.2.5.6 Exceptions

2.2.5.7 Enabling the FPU

2.3 Debug Peripherals Description

2.3.1 FPB

2.3.2 DWT

2.3.3 ITM

2.3.4 TPIU

2.3.4.1 TPIU Components

2.4 Functional Peripherals Register Map

2.4.1 FPU Registers

2.4.1.1 FPCCR Register (Offset = F34h) [reset = C0000000h]

2.4.1.2 FPCAR Register (Offset = F38h) [reset = 00000000h]

2.4.1.3 FPDSCR Register (Offset = F3Ch) [reset = 00000000h]

2.4.1.4 MVFR0 Register (Offset = F40h) [reset = 10110021h]

2.4.1.5 MVFR1 Register (Offset = F44h) [reset = 11000011h]

2.4.2 MPU Registers

2.4.2.1 TYPE Register (Offset = D90h) [reset = 00000800h]

2.4.2.2 CTRL Register (Offset = D94h) [reset = 00000000h]

2.4.2.3 RNR Register (Offset = D98h) [reset = 0h]

2.4.2.4 RBAR Register (Offset = D9Ch) [reset = 00000000h]

2.4.2.5 RASR Register (Offset = DA0h) [reset = 00000000h]

2.4.2.6 RBAR_A1 Register (Offset = DA4h) [reset = 00000000h]

2.4.2.7 RASR_A1 Register (Offset = DA8h) [reset = 00000000h]

2.4.2.8 RBAR_A2 Register (Offset = DACh) [reset = 00000000h]

2.4.2.9 RASR_A2 Register (Offset = DB0h) [reset = 00000000h]

2.4.2.10 RBAR_A3 Register (Offset = DB4h)

2.4.2.11 RASR_A3 Register (Offset = DB8h) [reset = 00000000h]

2.4.3 NVIC Registers

2.4.3.1 ISER0 Register (Offset = 100h) [reset = 00000000h]

2.4.3.2 ISER1 Register (Offset = 104h) [reset = 00000000h]

2.4.3.3 ICER0 Register (Offset = 180h) [reset = 00000000h]

2.4.3.4 ICER1 Register (Offset = 184h) [reset = 00000000h]

2.4.3.5 ISPR0 Register (Offset = 200h) [reset = 00000000h]

2.4.3.6 ISPR1 Register (Offset = 204h) [reset = 00000000h]

2.4.3.7 ICPR0 Register (Offset = 280h) [reset = 00000000h]

2.4.3.8 ICPR1 Register (Offset = 284h) [reset = 00000000h]

2.4.3.9 IABR0 Register (Offset = 300h) [reset = 00000000h]

2.4.3.10 IABR1 Register (Offset = 304h) [reset = 00000000h]

2.4.3.11 IPR0 Register (Offset = 400h) [reset = 00000000h]

2.4.3.12 IPR1 Register (Offset = 404h) [reset = 00000000h]

2.4.3.13 IPR2 Register (Offset = 408h) [reset = 00000000h]

2.4.3.14 IPR3 Register (Offset = 40Ch) [reset = 00000000h]

2.4.3.15 IPR4 Register (Offset = 410h) [reset = 00000000h]

2.4.3.16 IPR5 Register (Offset = 414h) [reset = 00000000h]

2.4.3.17 IPR6 Register (Offset = 418h) [reset = 00000000h]

2.4.3.18 IPR7 Register (Offset = 41Ch) [reset = 00000000h]

2.4.3.19 IPR8 Register (Offset = 420h) [reset = 00000000h]

2.4.3.20 IPR9 Register (Offset = 424h) [reset = 00000000h]

2.4.3.21 IPR10 Register (Offset = 428h) [reset = 00000000h]

2.4.3.22 IPR11 Register (Offset = 42Ch) [reset = 00000000h]

2.4.3.23 IPR12 Register (Offset = 430h) [reset = 00000000h]

2.4.3.24 IPR13 Register (Offset = 434h) [reset = 00000000h]

2.4.3.25 IPR14 Register (Offset = 438h) [reset = 00000000h]

2.4.3.26 IPR15 Register (Offset = 43Ch) [reset = 00000000h]

2.4.3.27 STIR Register (Offset = F00h) [reset = 00000000h]

2.4.4 SYSTICK Registers

2.4.4.1 STCSR Register (Offset = 10h) [reset = 00000000h]

2.4.4.2 STRVR Register (Offset = 14h) [reset = 0h]

2.4.4.3 STCVR Register (Offset = 18h) [reset = 0h]

2.4.4.4 STCR Register (Offset = 1Ch) [reset = 0h]

2.4.5 SCB Registers

2.4.5.1 CPUID Register (Offset = D00h) [reset = 410FC241h]

2.4.5.2 ICSR Register (Offset = D04h) [reset = 00000000h]

2.4.5.3 VTOR Register (Offset = D08h) [reset = 00000000h]

2.4.5.4 AIRCR Register (Offset = D0Ch) [reset = FA050000h]

2.4.5.5 SCR Register (Offset = D10h) [reset = 00000000h]

2.4.5.6 CCR Register (Offset = D14h) [reset = 00000200h]

2.4.5.7 SHPR1 Register (Offset = D18h) [reset = 00000000h]

2.4.5.8 SHPR2 Register (Offset = D1Ch) [reset = 00000000h]

2.4.5.9 SHPR3 Register (Offset = D20h) [reset = 00000000h]

2.4.5.10 SHCSR Register (Offset = D24h) [reset = 00000000h]

2.4.5.11 CFSR Register (Offset = D28h) [reset = 00000000h]

2.4.5.12 HFSR Register (Offset = D2Ch) [reset = 00000000h]

2.4.5.13 DFSR Register (Offset = D30h) [reset = 00000000h]

2.4.5.14 MMFAR Register (Offset = D34h) [reset = 0h]

2.4.5.15 BFAR Register (Offset = D38h) [reset = 0h]

2.4.5.16 AFSR Register (Offset = D3Ch) [reset = 00000000h]

2.4.5.17 PFR0 Register (Offset = D40h) [reset = 00000030h]

2.4.5.18 PFR1 Register (Offset = D44h) [reset = 00000200h]

2.4.5.19 DFR0 Register (Offset = D48h) [reset = 00100000h]

2.4.5.20 AFR0 Register (Offset = D4Ch) [reset = 00000000h]

2.4.5.21 MMFR0 Register (Offset = D50h) [reset = 00100030h]

2.4.5.22 MMFR1 Register (Offset = D54h) [reset = 00000000h]

2.4.5.23 MMFR2 Register (Offset = D58h) [reset = 00000000h]

2.4.5.24 MMFR3 Register (Offset = D5Ch) [reset = 00000000h]

2.4.5.25 ISAR0 Register (Offset = D60h) [reset = 01141110h]

2.4.5.26 ISAR1 Register (Offset = D64h) [reset = 02112000h]

2.4.5.27 ISAR2 Register (Offset = D68h) [reset = 21232231h]

2.4.5.28 ISAR3 Register (Offset = D6Ch) [reset = 01111131h]

2.4.5.29 ISAR4 Register (Offset = D70h) [reset = 01310102h]

2.4.5.30 CPACR Register (Offset = D88h) [reset = 0h]

2.4.6 SCnSCB Registers

2.4.6.1 ICTR Register (Offset = 4h) [reset = 00000000h]

2.4.6.2 ACTLR Register (Offset = 8h) [reset = 00000000h]

2.4.7 COREDEBUG Registers

2.4.7.1 DHCSR Register (Offset = DF0h) [reset = 00000000h]

2.4.7.2 DCRSR Register (Offset = DF4h) [reset = 0h]

2.4.7.3 DCRDR Register (Offset = DF8h)

2.4.7.4 DEMCR Register (Offset = DFCh) [reset = 00000000h]

2.5 Debug Peripherals Register Map

2.5.1 FPB Registers

2.5.1.1 FP_CTRL Register (Offset = 0h) [reset = 00000130h]

2.5.1.2 FP_REMAP Register (Offset = 4h) [reset = 0h]

2.5.1.3 FP_COMP0 Register (Offset = 8h) [reset = 00000000h]

2.5.1.4 FP_COMP1 Register (Offset = Ch) [reset = 00000000h]

2.5.1.5 FP_COMP2 Register (Offset = 10h) [reset = 00000000h]

2.5.1.6 FP_COMP3 Register (Offset = 14h) [reset = 00000000h]

2.5.1.7 FP_COMP4 Register (Offset = 18h) [reset = 00000000h]

2.5.1.8 FP_COMP5 Register (Offset = 1Ch) [reset = 00000000h]

2.5.1.9 FP_COMP6 Register (Offset = 20h) [reset = 00000000h]

2.5.1.10 FP_COMP7 Register (Offset = 24h) [reset = 00000000h]

2.5.2 DWT Registers

2.5.2.1 CTRL Register (Offset = 0h) [reset = 40000000h]

2.5.2.2 CYCCNT Register (Offset = 4h) [reset = 00000000h]

2.5.2.3 CPICNT Register (Offset = 8h) [reset = 0h]

2.5.2.4 EXCCNT Register (Offset = Ch) [reset = 0h]

2.5.2.5 SLEEPCNT Register (Offset = 10h) [reset = 0h]

2.5.2.6 LSUCNT Register (Offset = 14h) [reset = 0h]

2.5.2.7 FOLDCNT Register (Offset = 18h) [reset = 0h]

2.5.2.8 PCSR Register (Offset = 1Ch) [reset = 0h]

2.5.2.9 COMP0 Register (Offset = 20h) [reset = 0h]

2.5.2.10 MASK0 Register (Offset = 24h) [reset = 0h]

2.5.2.11 FUNCTION0 Register (Offset = 28h) [reset = 00000000h]

2.5.2.12 COMP1 Register (Offset = 30h) [reset = 0h]

2.5.2.13 MASK1 Register (Offset = 34h) [reset = 0h]

2.5.2.14 FUNCTION1 Register (Offset = 38h) [reset = 00000000h]

2.5.2.15 COMP2 Register (Offset = 40h) [reset = 0h]

2.5.2.16 MASK2 Register (Offset = 44h) [reset = 0h]

2.5.2.17 FUNCTION2 Register (Offset = 48h) [reset = 00000000h]

2.5.2.18 COMP3 Register (Offset = 50h) [reset = 0h]

2.5.2.19 MASK3 Register (Offset = 54h) [reset = 0h]

2.5.2.20 FUNCTION3 Register (Offset = 58h) [reset = 00000000h]

2.5.3 ITM Registers

2.5.3.1 STIM0 Register (Offset = 0h)

2.5.3.2 STIM1 Register (Offset = 4h)

2.5.3.3 STIM2 Register (Offset = 8h)

2.5.3.4 STIM3 Register (Offset = Ch)

2.5.3.5 STIM4 Register (Offset = 10h)

2.5.3.6 STIM5 Register (Offset = 14h)

2.5.3.7 STIM6 Register (Offset = 18h)

2.5.3.8 STIM7 Register (Offset = 1Ch)

2.5.3.9 STIM8 Register (Offset = 20h)

2.5.3.10 STIM9 Register (Offset = 24h)

2.5.3.11 STIM10 Register (Offset = 28h)

2.5.3.12 STIM11 Register (Offset = 2Ch)

2.5.3.13 STIM12 Register (Offset = 30h)

2.5.3.14 STIM13 Register (Offset = 34h)

2.5.3.15 STIM14 Register (Offset = 38h)

2.5.3.16 STIM15 Register (Offset = 3Ch)

2.5.3.17 STIM16 Register (Offset = 40h)

2.5.3.18 STIM17 Register (Offset = 44h)

2.5.3.19 STIM18 Register (Offset = 48h)

2.5.3.20 STIM19 Register (Offset = 4Ch)

2.5.3.21 STIM20 Register (Offset = 50h)

2.5.3.22 STIM21 Register (Offset = 54h)

2.5.3.23 STIM22 Register (Offset = 58h)

2.5.3.24 STIM23 Register (Offset = 5Ch)

2.5.3.25 STIM24 Register (Offset = 60h)

2.5.3.26 STIM25 Register (Offset = 64h)

2.5.3.27 STIM26 Register (Offset = 68h)

2.5.3.28 STIM27 Register (Offset = 6Ch)

2.5.3.29 STIM28 Register (Offset = 70h)

2.5.3.30 STIM29 Register (Offset = 74h)

2.5.3.31 STIM30 Register (Offset = 78h)

2.5.3.32 STIM31 Register (Offset = 7Ch)

2.5.3.33 TER Register (Offset = E00h) [reset = 00000000h]

2.5.3.34 TPR Register (Offset = E40h) [reset = 00000000h]

2.5.3.35 TCR Register (Offset = E80h) [reset = 00000000h]

2.5.3.36 IWR Register (Offset = EF8h) [reset = 00000000h]

2.5.3.37 IMCR Register (Offset = F00h) [reset = 00000000h]

2.5.3.38 LAR Register (Offset = FB0h) [reset = 00000000h]

2.5.3.39 LSR Register (Offset = FB4h) [reset = 00000003h]

2.5.4 TPIU Registers

3 Reset Controller (RSTCTL)

3.1 Introduction

3.2 Reset Classification

3.2.1 Class 0 : Power On/Off Reset (POR) Class

3.2.2 Class 1 : Reboot Reset

3.2.3 Class 2 : Hard Reset

3.2.4 Class 3 : Soft Reset

3.3 RSTCTL Registers

3.3.1 RSTCTL_RESET_REQ Register (offset = 00h)

3.3.2 RSTCTL_HARDRESET_STAT Register (offset = 04h)

3.3.3 RSTCTL_HARDRESET_CLR Register (offset = 08h)

3.3.4 RSTCTL_HARDRESET_SET Register (offset = 0Ch)

3.3.5 RSTCTL_SOFTRESET_STAT Register (offset = 10h)

3.3.6 RSTCTL_SOFTRESET_CLR Register (offset = 14h)

3.3.7 RSTCTL_SOFTRESET_SET Register (offset = 18h)

3.3.8 RSTCTL_PSSRESET_STAT Register (offset = 100h)

3.3.9 RSTCTL_PSSRESET_CLR Register (offset = 104h)

3.3.10 RSTCTL_PCMRESET_STAT Register (offset = 108h)

3.3.11 RSTCTL_PCMRESET_CLR Register (offset = 10Ch)

3.3.12 RSTCTL_PINRESET_STAT Register (offset = 110h)

3.3.13 RSTCTL_PINRESET_CLR Register (offset = 114h)

3.3.14 RSTCTL_REBOOTRESET_STAT Register (offset = 118h)

3.3.15 RSTCTL_REBOOTRESET_CLR Register (offset = 11Ch)

3.3.16 RSTCTL_CSRESET_STAT Register (offset = 120h)

3.3.17 RSTCTL_CSRESET_CLR Register (offset = 124h)

4 System Controller (SYSCTL)

4.1 SYSCTL Introduction

4.2 Device Memory Configuration and Status

4.2.1 Flash

4.2.2 SRAM

4.2.2.1 SRAM Bank Enable Configuration

4.2.2.2 SRAM Bank Retention Configuration

4.3 NMI Configuration

4.4 Watchdog Timer Reset Configuration

4.5 Clock Run or Stop Configuration

4.6 Reset Status and Override Control

4.7 Device Security

4.7.1 Device Security Introduction

4.7.2 Device Security Components

4.7.3 JTAG and SWD Lock Based Security

4.7.4 IP Protection through Secure Memory Zones

4.7.4.1 Execution of IP Protected Secure Zone code

4.7.4.2 IP Protection and Secure Zone Data Access Unlock Register

4.7.5 Boot Overrides

4.7.5.1 Boot Override Through JTAG

4.7.5.2 Boot Override Through Flash Mailbox

4.7.5.2.1 Boot Override Flash Mailbox (FL_BOOTOVER_MAILBOX)

4.7.5.2.2 Boot Override Commands and Acknowlegments

4.7.5.2.3 Using ANY_CONFIG Command

4.7.6 In-Field Updates

4.7.6.1 In-Field Updates: Unsecure Device

4.7.6.2 In-Field Updates: Secure Device

4.7.6.3 In-Field Updates: Secure Device With JTAG and SWD Lock Enabled

4.7.6.3.1 Unencrypted Update: JTAG and SWD Locked Device

4.7.6.3.2 Encrypted Update: JTAG and SWD Locked Device

4.7.6.4 In-Field Updates: Secure Device With IP Protection Enabled

4.7.6.4.1 Unencrypted Update: IP Protected Device

4.7.6.4.2 Encrypted Update: IP Protected Device

4.7.7 Device Security and Boot Overrides User Considerations

4.8 Device Descriptor Table

4.8.1 TLV Descriptors

4.9 ARM Cortex-M4F ROM Table Based Part Number

4.10 SYSCTL Registers

4.10.1 SYS_REBOOT_CTL Register (offset = 0000h)

4.10.2 SYS_NMI_CTLSTAT Register (offset = 0004h)

4.10.3 SYS_WDTRESET_CTL Register (offset = 0008h)

4.10.4 SYS_PERIHALT_CTL Register (offset = 000Ch)

4.10.5 SYS_SRAM_SIZE Register (offset = 0010h)

4.10.6 SYS_SRAM_BANKEN Register (offset = 0014h)

4.10.7 SYS_SRAM_BANKRET Register (offset = 0018h)

4.10.8 SYS_FLASH_SIZE Register (offset = 0020h)

4.10.9 SYS_DIO_GLTFLT_CTL Register (offset = 0030h)

4.10.10 SYS_SECDATA_UNLOCK Register (offset = 0040h)

4.10.11 SYS_MASTER_UNLOCK Register (offset = 1000h)

4.10.12 SYS_BOOTOVER_REQ0 Register (offset = 1004h)

4.10.13 SYS_BOOTOVER_REQ1 Register (offset = 1008h)

4.10.14 SYS_BOOTOVER_ACK Register (offset = 100Ch)

4.10.15 SYS_RESET_REQ Register (offset = 1010h)

4.10.16 SYS_RESET_STATOVER Register (offset = 1014h)

4.10.17 SYS_SYSTEM_STAT Register (offset = 1020h)

5 Clock System (CS)

5.1 Clock System Introduction

5.2 Clock System Operation

5.2.1 CS Module Features for Low-Power Applications

5.2.2 LFXT Oscillator (Device Specific)

5.2.3 HFXT Oscillator (Device Specific)

5.2.4 Internal Very-Low-Power Low-Frequency Oscillator (VLO)

5.2.5 Internal Low-Power Low-Frequency Oscillator (REFO)

5.2.6 Module Oscillator (MODOSC)

5.2.7 System Oscillator (SYSOSC)

5.2.8 Digitally Controlled Oscillator (DCO)

5.2.8.1 DCO Modes

5.2.8.2 DCO Fault in External Resistor Mode

5.2.8.3 DCO Ranges and Tuning

5.2.8.4 Changing DCO Frequency

5.2.9 Module Clock Request System

5.2.10 CS Module Fail-Safe Operation

5.2.11 Start-Up Counters

5.2.12 Synchronization of Clock Signals

5.2.13 Clock Status

5.3 CS Registers

5.3.1 CSKEY Register (offset = 00h) [reset = 0000_A596h]

5.3.2 CSCTL0 Register (offset = 04h) [reset = 0001_0000h]

5.3.3 CSCTL1 Register (offset = 08h) [reset = 0000_0033h]

5.3.4 CSCTL2 Register (offset = 0Ch) [reset = 0001_0003h]

5.3.5 CSCTL3 Register (offset = 10h) [reset = 0000_0BBBh]

5.3.6 CSCLKEN Register (offset = 30h) [reset = 0000_000Fh]

5.3.7 CSSTAT Register (offset = 34h) [reset = 0000_0003h]

5.3.8 CSIE Register (offset = 40h) [reset = 0000_0000h]

5.3.9 CSIFG Register (offset = 48h) [reset = 0000_0001h]

5.3.10 CSCLRIFG Register (offset = 50h) [reset = 0000_0000h]

5.3.11 CSSETIFG Register (offset = 58h) [reset = 0000_0000h]

5.3.12 CSDCOERCAL0 Register (offset=60h) [reset = 0100_0000h]

5.3.13 CSDCOERCAL1 Register (offset=64h) [reset = 0000_0100h]

6 Power Supply System (PSS)

6.1 PSS Introduction

6.2 PSS Operation

6.2.1 Supply Voltage Supervisor / Monitor

6.2.1.1 SVSMH

6.2.1.2 SVMHOUT

6.2.1.3 SVSMH Thresholds

6.2.2 Supply Voltage Supervisor during Power-Up

6.2.3 VCCDET

6.2.4 PSS Interrupts

6.3 PSS Registers

6.3.1 PSSKEY Register (offset = 00h) [reset = 0000A596h]

6.3.2 PSSCTL0 Register (offset = 04h) [reset = 00002000h]

6.3.3 PSSIE Register (offset = 34h) [reset = 0000h]

6.3.4 PSSIFG Register (offset = 38h) [reset = 0000h]

6.3.5 PSSCLRIFG Register (offset = 3Ch) [reset = 0000h]

7 Power Control Manager (PCM)

7.1 PCM Introduction

7.2 PCM Overview

7.3 Core Voltage Regulators

7.3.1 DC-DC Regulator Care Abouts

7.4 Power Modes

7.4.1 Active Modes (AM)

7.4.2 LPM0

7.4.3 LPM3/LPM4

7.4.4 LPM3.5/LPM4.5

7.4.5 Summary of Power Modes

7.5 Power Mode Transitions

7.5.1 Active Mode Transitions

7.5.2 Transitions To and From LPM0

7.5.3 Transitions To and From LPM3/LPM4

7.5.4 Transitions To and From LPM3.5/LPM4.5

7.6 Changing Core Voltages

7.6.1 Increasing VCORE for Higher MCLK Frequencies

7.6.2 Decreasing VCORE for Power Optimization

7.7 ARM Cortex Processor Sleep Modes

7.7.1 WFI, Wait For Interrupt

7.7.2 WFE, Wait For Event

7.7.3 Sleep On Exit

7.7.4 SLEEPDEEP

7.8 Changing Power Modes

7.9 Power Mode Selection

7.10 Power Mode Transition Checks

7.11 Power Mode Clock Checks

7.12 Clock Configuration Changes

7.13 Changing Active Modes

7.13.1 DC-DC Error Checking

7.14 Entering LPM0 Modes

7.15 Exiting LPM0 Modes

7.16 Entering LPM3/LPM4 Modes

7.17 Exiting LPM3/LPM4 Modes

7.18 Entering LPM3.5/LPM4.5 Modes

7.19 Exiting LPM3.5/LPM4.5 Modes

7.20 Supply Voltage Supervisor/Monitor and Power Modes

7.21 Low-Power Reset

7.22 Power Requests During Debug

7.22.1 Debug During Active Modes

7.22.2 Debug During LPM0 Modes

7.22.3 Debug During LPM3, LPM4, and LPMx.5 Modes.

7.23 Wake-up Sources from Low Power Modes

7.24 PCM Registers

7.24.1 PCMCTL0 Register (offset = 00h) [reset = A5960000h]

7.24.2 PCMCTL1 Register (offset = 04h) [reset = A5960000h]

7.24.3 PCMIE Register (offset = 08h) [reset = 00000000h]

7.24.4 PCMIFG Register (offset = 0Ch) [reset = 00000000h]

7.24.5 PCMCLRIFG Register (offset = 10h) [reset = 00000000h]

8 Flash Controller (FLCTL)

8.1 Introduction

8.2 Flash Memory Organization

8.3 Flash Controller Clocking

8.3.1 Bus Interface Clock

8.3.2 Timing Clock

8.4 Flash Controller Address Mapping

8.5 Flash Controller Access Privileges

8.6 Flash Read Modes and Features

8.6.1 Flash Read Modes

8.6.2 Flash Read Timing Control

8.6.3 Read Buffering

8.6.4 Burst Read/Compare Feature

8.6.4.1 Usage Examples for Burst/Compare Read Operations

8.6.4.1.1 Erase Verify for 1 Information memory Sector

8.6.4.1.2 Erase Verify After Mass Erase of Bank1 in 256KB Main Memory

8.7 Flash Program Modes and Features

8.7.1 Program Modes

8.7.1.1 Immediate write mode

8.7.1.2 Full Word write mode

8.7.1.3 Auto-verify Feature

8.7.2 Burst Program Feature

8.7.3 Program Protection Features

8.8 Flash Erase Modes and Features

8.8.1 Sector Erase Mode

8.8.2 Mass Erase Mode

8.8.3 Erase Protection Features

8.9 Flash Write/Erase Protection

8.10 Recommended Settings/Flow for Program & Erase Operations

8.10.1 Flash Program Operations

8.10.2 Flash Erase Operations

8.11 Application Benchmarking Features

8.12 Handling/Ordering of Flash operations

8.12.1 Out of order processing of application initiated read/write commands

8.12.2 Simultaneous read/write conditions

8.13 Interrupts

8.14 Support for Low Frequency Active and Low Frequency LPM0 Modes

8.15 Flash Functionality during Resets

8.15.1 Soft Reset

8.15.2 Hard Reset

8.15.3 POR Reset

8.16 FLCTL Registers

8.16.1 FLCTL_POWER_STAT Register (offset = 0000h)

8.16.2 FLCTL_BANK0_RDCTL Register (offset = 0010h)

8.16.3 FLCTL_BANK1_RDCTL Register (offset = 0014h)

8.16.4 FLCTL_RDBRST_CTLSTAT Register (offset = 0020h)

8.16.5 FLCTL_RDBRST_STARTADDR Register (offset = 0024h)

8.16.6 FLCTL_RDBRST_LEN Register (offset = 0028h)

8.16.7 FLCTL_RDBRST_FAILADDR Register (offset = 003Ch)

8.16.8 FLCTL_RDBRST_FAILCNT Register (offset = 0040h)

8.16.9 FLCTL_PRG_CTLSTAT Register (offset = 0050h)

8.16.10 FLCTL_PRGBRST_CTLSTAT Register (offset = 0054h)

8.16.11 FLCTL_PRGBRST_STARTADDR Register (offset = 0058h)

8.16.12 FLCTL_PRGBRST_DATA0_0 Register (offset = 060h)

8.16.13 FLCTL_PRGBRST_DATA0_1 Register (offset = 064h)

8.16.14 FLCTL_PRGBRST_DATA0_2 Register (offset = 068h)

8.16.15 FLCTL_PRGBRST_DATA0_3 Register (offset = 06Ch)

8.16.16 FLCTL_PRGBRST_DATA1_0 Register (offset = 070h)

8.16.17 FLCTL_PRGBRST_DATA1_1 Register (offset = 074h)

8.16.18 FLCTL_PRGBRST_DATA1_2 Register (offset = 078h)

8.16.19 FLCTL_PRGBRST_DATA1_3 Register (offset = 07Ch)

8.16.20 FLCTL_PRGBRST_DATA2_0 Register (offset = 080h)

8.16.21 FLCTL_PRGBRST_DATA2_1 Register (offset = 084h)

8.16.22 FLCTL_PRGBRST_DATA2_2 Register (offset = 088h)

8.16.23 FLCTL_PRGBRST_DATA2_3 Register (offset = 08Ch)

8.16.24 FLCTL_PRGBRST_DATA3_0 Register (offset = 090h)

8.16.25 FLCTL_PRGBRST_DATA3_1 Register (offset = 094h)

8.16.26 FLCTL_PRGBRST_DATA3_2 Register (offset = 098h)

8.16.27 FLCTL_PRGBRST_DATA3_3 Register (offset = 09Ch)

8.16.28 FLCTL_ERASE_CTLSTAT Register (offset = 00A0h)

8.16.29 FLCTL_ERASE_SECTADDR Register (offset = 00A4h)

8.16.30 FLCTL_BANK0_INFO_WEPROT Register (offset = 00B0h)

8.16.31 FLCTL_BANK0_MAIN_WEPROT Register (offset = 00B4h)

8.16.32 FLCTL_BANK1_INFO_WEPROT Register (offset = 00C0h)

8.16.33 FLCTL_BANK1_MAIN_WEPROT Register (offset = 00C4h)

8.16.34 FLCTL_BMRK_CTLSTAT Register (offset = 00D0h)

8.16.35 FLCTL_BMRK_IFETCH Register (offset = 00D4h)

8.16.36 FLCTL_BMRK_DREAD Register (offset = 00D8h)

8.16.37 FLCTL_BMRK_CMP Register (offset = 00DCh)

8.16.38 FLCTL_IFG Register (offset = 0F0h)

8.16.39 FLCTL_IE Register (offset = 0F4h)

8.16.40 FLCTL_CLRIFG Register (offset = 0F8h)

8.16.41 FLCTL_SETIFG Register (offset = 0FCh)

8.16.42 FLCTL_READ_TIMCTL Register (offset = 0100h)

8.16.43 FLCTL_READMARGIN_TIMCTL Register (offset = 0104h)

8.16.44 FLCTL_PRGVER_TIMCTL Register (offset = 0108h)

8.16.45 FLCTL_ERSVER_TIMCTL Register (offset = 010Ch)

8.16.46 FLCTL_LKGVER_TIMCTL Register (offset = 0110h)

8.16.47 FLCTL_PROGRAM_TIMCTL Register (offset = 0114h)

8.16.48 FLCTL_ERASE_TIMCTL Register (offset = 0118h)

8.16.49 FLCTL_MASSERASE_TIMCTL Register (offset = 011Ch)

8.16.50 FLCTL_BURSTPRG_TIMCTL Register (offset = 0120h)

9 DMA

9.1 DMA Introduction

9.2 DMA Operation

9.2.1 APB Slave Interface

9.2.2 AHB Master Interface

9.2.2.1 Transfer Types

9.2.2.2 Transfer Data Width

9.2.2.3 Protection Control

9.2.2.4 Address Increments

9.2.3 DMA Control Interface

9.2.3.1 DMA Signaling

9.2.3.1.1 Signaling for Pulse Request

9.2.3.1.2 Signaling for Level Request

9.2.3.2 DMA Arbitration Rate

9.2.3.3 Priority

9.2.3.4 DMA Cycle Types

9.2.3.4.1 Invalid Cycle Type

9.2.3.4.2 Basic Cycle Type

9.2.3.4.3 Auto-Request Cycle Type

9.2.3.4.4 Ping-Pong Cycle Type

9.2.3.4.5 Memory Scatter-Gather Cycle Type

9.2.3.4.6 Peripheral Scatter-Gather Cycle Type

9.2.3.4.7 Error Signaling

9.2.4 Channel Control Data Structure

9.2.4.1 Source Data End Pointer

9.2.4.2 Destination Data End Pointer

9.2.4.3 Control Data Configuration

9.2.4.4 Address Calculation

9.2.5 Peripheral Triggers

9.2.6 Interrupts

9.3 DMA Registers

9.3.1 DMA_DEVICE_CFG Register (offset = 000h)

9.3.2 DMA_SW_CHTRIG Register (offset = 004h)

9.3.3 DMA_CHn_SRCCFG Register (offset = 010h + 4h*n, n = 0 through NUM_DMA_CHANNELS)

9.3.4 DMA_INT1_SRCCFG Register (offset = 100h)

9.3.5 DMA_INT2_SRCCFG Register (offset = 104h)

9.3.6 DMA_INT3_SRCCFG Register (offset = 108h)

9.3.7 DMA_INT0_SRCFLG Register (offset = 110h)

9.3.8 DMA_INT0_CLRFLG Register (offset = 114h)

9.3.9 DMA_STAT Register (offset = 1000h) [reset = 0h]

9.3.10 DMA_CFG Register (offset = 1004h) [reset = 0h]

9.3.11 DMA_CTLBASE Register (offset = 1008h) [reset = 0h]

9.3.12 DMA_ALTBASE Register (offset = 100Ch) [reset = 0h]

9.3.13 DMA_WAITSTAT Register (offset = 1010h) [reset = 0h]

9.3.14 DMA_SWREQ Register (offset = 1014h) [reset = 0h]

9.3.15 DMA_USEBURSTSET Register (offset = 1018h) [reset = 0h]

9.3.16 DMA_USEBURSTCLR Register (offset = 101Ch) [reset = 0h]

9.3.17 DMA_REQMASKSET Register (offset = 1020h) [reset = 0h]

9.3.18 DMA_REQMASKCLR Register (offset = 1024h) [reset = 0h]

9.3.19 DMA_ENASET Register (offset = 1028h) [reset = 0h]

9.3.20 DMA_ENACLR Register (offset = 102Ch) [reset = 0h]

9.3.21 DMA_ALTSET Register (offset = 1030h) [reset = 0h]

9.3.22 DMA_ALTCLR Register (offset = 1034h) [reset = 0h]

9.3.23 DMA_PRIOSET Register (offset = 1038h) [reset = 0h]

9.3.24 DMA_PRIOCLR Register (offset = 103Ch) [reset = 0h]

9.3.25 DMA_ERRCLR Register (offset = 104Ch) [reset = 0h]

10 Digital I/O

10.1 Digital I/O Introduction

10.2 Digital I/O Operation

10.2.1 Input Registers (PxIN)

10.2.2 Output Registers (PxOUT)

10.2.3 Direction Registers (PxDIR)

10.2.4 Pullup or Pulldown Resistor Enable Registers (PxREN)

10.2.5 Output Drive Strength Selection Registers (PxDS)

10.2.6 Function Select Registers (PxSEL0, PxSEL1)

10.2.7 Port Interrupts

10.2.7.1 Interrupt Edge Select Registers (PxIES)

10.2.7.2 Interrupt Enable Registers (PxIE)

10.3 I/O Configuration

10.3.1 Configuration After Reset

10.3.2 Configuration of Unused Port Pins

10.3.3 Configuration for LPM3/LPM4 Modes

10.3.4 Configuration for LPM3.5/LPM4.5 Modes

10.4 Digital I/O Registers

10.4.1 PxIV Register

10.4.2 PxIN Register

10.4.3 PxOUT Register

10.4.4 PxDIR Register

10.4.5 PxREN Register

10.4.6 PxDS Register

10.4.7 PxSEL0 Register

10.4.8 PxSEL1 Register

10.4.9 PxSELC Register

10.4.10 PxIES Register

10.4.11 PxIE Register

10.4.12 PxIFG Register

11 Port Mapping Controller (PMAP)

11.1 Port Mapping Controller Introduction

11.2 Port Mapping Controller Operation

11.2.1 Access

11.2.2 Mapping

11.3 PMAP Registers

11.3.1 PMAPKEYID Register (offset = 00h) [reset = 96A5h]

11.3.2 PMAPCTL Register (offset = 02h) [reset = 0001h]

11.3.3 P1MAP0 to P1MAP7 Register (offset = 08h to 0Fh) [reset = Device dependent]

11.3.4 P2MAP0 to P2MAP7 Register (offset = 10h to 17h) [reset = Device dependent]

11.3.5 P3MAP0 to P3MAP7 Register (offset = 18h to 1Fh) [reset = Device dependent]

11.3.6 P4MAP0 to P4MAP7 Register (offset = 20h to 27h) [reset = Device dependent]

11.3.7 P5MAP0 to P5MAP7 Register (offset = 28h to 2Fh) [reset = Device dependent]

11.3.8 P6MAP0 to P6MAP7 Register (offset = 30h to 37h) [reset = Device dependent]

11.3.9 P7MAP0 to P7MAP7 Register (offset = 38h to 3Fh) [reset = Device dependent]

11.3.10 PxMAPyz Register [reset = Device dependent]

12 Capacitive Touch IO (CAPTIO)

12.1 Capacitive Touch IO Introduction

12.2 Capacitive Touch IO Operation

12.3 CapTouch Registers

12.3.1 CAPTIOxCTL Register (offset = 0Eh) [reset = 0000h]

13 CRC32 Module

13.1 Cyclic Redundancy Check (CRC32) Module Introduction

13.2 CRC Checksum Generation

13.2.1 CRC Standard and Bit Order

13.2.2 CRC Implementation

13.3 CRC32 Registers

13.3.0.1 CRC32DI Register

13.3.0.2 CRC32DIRB Register

13.3.0.3 CRC32INIRES_LO Register

13.3.0.4 CRC32INIRES_HI Register

13.3.0.5 CRC32RESR_LO Register

13.3.0.6 CRC32RESR_HI Register

13.3.0.7 CRC16DI Register

13.3.0.8 CRC16DIRB Register

13.3.0.9 CRC16INIRES Register

13.3.0.10 CRC16RESR Register

14 AES256 Accelerator

14.1 AES Accelerator Introduction

14.2 AES Accelerator Operation

14.2.1 Load the Key (128-Bit, 192-Bit, or 256-Bit Keylength)

14.2.2 Load the Data (128-Bit State)

14.2.3 Read the Data (128-Bit State)

14.2.4 Trigger an Encryption or Decryption

14.2.5 Encryption

14.2.6 Decryption

14.2.7 Decryption Key Generation

14.2.8 AES Key Buffer

14.2.9 Using the AES Accelerator With Low-Power Modes

14.2.10 AES Accelerator Interrupts

14.2.11 DMA Operation and Implementing Block Cipher Modes

14.2.11.1 Electronic Codebook (ECB) Mode

14.2.11.1.1 ECB Encryption

14.2.11.1.2 ECB Decryption

14.2.11.2 Cipher Block Chaining (CBC) Mode

14.2.11.2.1 CBC Encryption

14.2.11.2.2 CBC Decryption

14.2.11.3 Output Feedback (OFB) Mode

14.2.11.3.1 OFB Encryption

14.2.11.3.2 OFB Decryption

14.2.11.4 Cipher Feedback (CFB) Mode

14.2.11.4.1 CFB Encryption

14.2.11.4.2 CFB Decryption

14.3 AES256 Registers

14.3.1 AESACTL0 Register

14.3.2 AESACTL1 Register

14.3.3 AESASTAT Register

14.3.4 AESAKEY Register

14.3.5 AESADIN Register

14.3.6 AESADOUT Register

14.3.7 AESAXDIN Register

14.3.8 AESAXIN Register

15 Watchdog Timer (WDT_A)

15.1 WDT_A Introduction

15.2 WDT_A Operation

15.2.1 Watchdog Timer Counter (WDTCNT)

15.2.2 Watchdog Mode

15.2.3 Interval Timer Mode

15.2.4 Watchdog Related Interrupts and Flags

15.2.5 Clock Sources of the WDT_A

15.2.5.1 Clock Fail-Safe Feature

15.2.6 WDT_A Operation in Different Device Power Modes

15.2.6.1 WDT_A Operation in Active Modes

15.2.6.2 WDT_A Operation in LPM0 Modes

15.2.6.3 WDT_A Operation in LPM3 Mode

15.2.6.4 WDT_A Operation in LPM3.5 Mode

15.2.6.5 WDT_A Operation in LPM4 and LPM4.5 Modes

15.3 WDT_A Registers

15.3.1 WDTCTL Register

16 Timer32

16.1 Introduction

16.2 Functional Description

16.3 Operation

16.4 Interrupt Generation

16.5 Timer32 Registers

16.5.1 T32LOAD1 Register (offset = 00h) [reset = 0h]

16.5.2 T32VALUE1 Register (offset = 04h) [reset = FFFFFFFFh]

16.5.3 T32CONTROL1 Register (offset = 08h) [reset = 20h]

16.5.4 T32INTCLR1 Register (offset = 0Ch) [reset = undefined]

16.5.5 T32RIS1 Register (offset = 10h) [reset = 0h]

16.5.6 T32MIS1 Register (offset = 14h) [reset = 0h]

16.5.7 T32BGLOAD1 Register (offset = 18h) [reset = 0h]

16.5.8 T32LOAD2 Register (offset = 20h) [reset = 0h]

16.5.9 T32VALUE2 Register (offset = 24h) [reset = FFFFFFFFh]

16.5.10 T32CONTROL2 Register (offset = 28h) [reset = 20h]

16.5.11 T32INTCLR2 Register (offset = 2Ch) [reset = undefined]

16.5.12 T32RIS2 Register (offset = 30h) [reset = 0h]

16.5.13 T32MIS2 Register (offset = 34h) [reset = 0h]

16.5.14 T32BGLOAD2 Register (offset = 38h) [reset = 0h]

17 Timer_A

17.1 Timer_A Introduction

17.2 Timer_A Operation

17.2.1 16-Bit Timer Counter

17.2.1.1 Clock Source Select and Divider

17.2.2 Starting the Timer

17.2.3 Timer Mode Control

17.2.3.1 Up Mode

17.2.3.1.1 Changing Period Register TAxCCR0

17.2.3.2 Continuous Mode

17.2.3.3 Use of Continuous Mode

17.2.3.4 Up/Down Mode

17.2.3.4.1 Changing Period Register TAxCCR0

17.2.3.5 Use of Up/Down Mode

17.2.4 Capture/Compare Blocks

17.2.4.1 Capture Mode

17.2.4.1.1 Capture Initiated by Software

17.2.4.2 Compare Mode

17.2.5 Output Unit

17.2.5.1 Output Modes

17.2.5.1.1 Output Example—Timer in Up Mode

17.2.5.1.2 Output Example – Timer in Continuous Mode

17.2.5.1.3 Output Example – Timer in Up/Down Mode

17.2.6 Timer_A Interrupts

17.2.6.1 TAxIV, Interrupt Vector Generator

17.3 Timer_A Registers

17.3.1 TAxCTL Register

17.3.2 TAxR Register

17.3.3 TAxCCTL0 to TAxCCTL6 Register

17.3.4 TAxCCR0 to TAxCCR6 Register

17.3.5 TAxIV Register

17.3.6 TAxEX0 Register

18 Real-Time Clock (RTC_C)

18.1 RTC_C Introduction

18.2 RTC_C Operation

18.2.1 Calendar Mode

18.2.2 Real-Time Clock and Prescale Dividers

18.2.3 Real-Time Clock Alarm Function

18.2.4 Real-Time Clock Protection

18.2.5 Reading or Writing Real-Time Clock Registers

18.2.6 Real-Time Clock Interrupts

18.2.7 Real-Time Clock Calibration for Crystal Offset Error

18.2.7.1 Calibration Frequency

18.2.7.1.1 Calibration Mechanism

18.2.8 Real-Time Clock Compensation for Crystal Temperature Drift

18.2.8.1 Temperature Compensation Scheme

18.2.8.2 Writing to RTCTCMP register

18.2.8.3 Temperature Measurement and Updates to RTC

18.2.9 Real-Time Clock Operation in Low-Power Modes

18.3 RTC_C Registers

18.3.1 RTCCTL0_L Register

18.3.2 RTCCTL0_H Register

18.3.3 RTCCTL1 Register

18.3.4 RTCCTL3 Register

18.3.5 RTCOCAL Register

18.3.6 RTCTCMP Register

18.3.7 RTCSEC Register – Hexadecimal Format

18.3.8 RTCSEC Register – BCD Format

18.3.9 RTCMIN Register – Hexadecimal Format

18.3.10 RTCMIN Register – BCD Format

18.3.11 RTCHOUR Register – Hexadecimal Format

18.3.12 RTCHOUR Register – BCD Format

18.3.13 RTCDOW Register

18.3.14 RTCDAY Register – Hexadecimal Format

18.3.15 RTCDAY Register – BCD Format

18.3.16 RTCMON Register – Hexadecimal Format

18.3.17 RTCMON Register – BCD Format

18.3.18 RTCYEAR Register – Hexadecimal Format

18.3.19 RTCYEAR Register – BCD Format

18.3.20 RTCAMIN Register – Hexadecimal Format

18.3.21 RTCAMIN Register – BCD Format

18.3.22 RTCAHOUR Register – Hexadecimal Format

18.3.23 RTCAHOUR Register – BCD Format

18.3.24 RTCADOW Register – Calendar Mode

18.3.25 RTCADAY Register – Hexadecimal Format

18.3.26 RTCADAY Register – BCD Format

18.3.27 RTCPS0CTL Register

18.3.28 RTCPS1CTL Register

18.3.29 RTCPS0 Register

18.3.30 RTCPS1 Register

18.3.31 RTCIV Register

18.3.32 RTCBIN2BCD Register

18.3.33 RTCBCD2BIN Register

19 Reference Module (REF_A)

19.1 REF_A Introduction

19.2 Principle of Operation

19.2.1 Low-Power Operation

19.2.2 Reference System Requests

19.2.2.1 REFBGACT, REFGENACT, REFGENBUSY

19.2.2.2 ADC14

19.3 REF_A Registers

19.3.1 REFCTL0 Register (offset = 00h) [reset = 0008h]

20 ADC14

20.1 ADC14 Introduction

20.2 ADC14 Operation

20.2.1 14-Bit ADC Core

20.2.1.1 Conversion Clock Selection

20.2.2 ADC14 Inputs and Multiplexer

20.2.2.1 Analog Port Selection

20.2.3 Voltage References

20.2.4 Auto Power Down

20.2.5 Power Modes

20.2.6 Sample and Conversion Timing

20.2.6.1 Extended Sample Mode

20.2.6.2 Pulse Sample Mode

20.2.6.3 Sample Timing Considerations

20.2.7 Conversion Memory

20.2.8 ADC14 Conversion Modes

20.2.8.1 Single-Channel Single-Conversion Mode

20.2.8.2 Sequence-of-Channels Mode (Autoscan Mode)

20.2.8.3 Repeat-Single-Channel Mode

20.2.8.4 Repeat-Sequence-of-Channels Mode (Repeated Autoscan Mode)

20.2.8.5 Using the Multiple Sample and Convert (ADC14MSC) Bit

20.2.8.6 Stopping Conversions

20.2.9 Window Comparator

20.2.10 Using the Integrated Temperature Sensor

20.2.11 ADC14 Grounding and Noise Considerations

20.2.12 ADC14 Interrupts

20.2.12.1 ADC14IV, Interrupt Vector Generator

20.3 ADC14 Registers

20.3.1 ADC14CTL0 Register (offset = 00h) [reset = 00000000h]

20.3.2 ADC14CTL1 Register (offset = 04h) [reset = 00000030h]

20.3.3 ADC14LO0 Register (offset = 08h) [reset = 00000000h]

20.3.4 ADC14HI0 Register (offset = 0Ch) [reset = 00003FFFh]

20.3.5 ADC14LO1 Register (offset = 10h) [reset = 00000000h]

20.3.6 ADC14HI1 Register (offset = 14h) [reset = 00003FFFh]

20.3.7 ADC14MCTL0 to ADC14MCTL31 Register (offset = 018h to 094h) [reset = 00000000h]

20.3.8 ADC14MEM0 to ADC14MEM31 Register (offset = 098h to 104h) [reset = Undefined]

20.3.9 ADC14IER0 Register (offset = 13Ch) [reset = 00000000h]

20.3.10 ADC14IER1 Register (offset = 140h) [reset = 00000000h]

20.3.11 ADC14IFGR0 Register (offset = 144h) [reset = 00000000h]

20.3.12 ADC14IFGR1 Register (offset = 148h) [reset = 00000000h]

20.3.13 ADC14CLRIFGR0 Register (offset = 14Ch) [reset = 00000000h]

20.3.14 ADC14CLRIFGR1 Register (offset = 150h) [reset = 00000000h]

20.3.15 ADC14IV Register (offset = 154h) [reset = 00000000h]

21 Comparator E Module (COMP_E)

21.1 COMP_E Introduction

21.2 COMP_E Operation

21.2.1 Comparator

21.2.2 Analog Input Switches

21.2.3 Port Logic

21.2.4 Input Short Switch

21.2.5 Output Filter

21.2.6 Reference Voltage Generator

21.2.7 Comparator, Port Disable Register CEPD

21.2.8 Comparator Interrupts

21.2.9 Comparator Used to Measure Resistive Elements

21.3 COMP_E Registers

21.3.1 CExCTL0 Register (offset = 00h) [reset = 0000h]

21.3.2 CExCTL1 Register (offset = 02h) [reset = 0000h]

21.3.3 CExCTL2 Register (offset = 04h) [reset = 0000h]

21.3.4 CExCTL3 Register (offset = 06h) [reset = 0000h]

21.3.5 CExINT Register (offset = 0Ch) [reset = 0000h]

21.3.6 CExIV Register (offset = 0Eh) [reset = 0000h]

22 Enhanced Universal Serial Communication Interface (eUSCI) – UART Mode

22.1 Enhanced Universal Serial Communication Interface A (eUSCI_A) Overview

22.2 eUSCI_A Introduction – UART Mode

22.3 eUSCI_A Operation – UART Mode

22.3.1 eUSCI_A Initialization and Reset

22.3.2 Character Format

22.3.3 Asynchronous Communication Format

22.3.3.1 Idle-Line Multiprocessor Format

22.3.3.1.1 Transmitting an Idle Frame

22.3.3.2 Address-Bit Multiprocessor Format

22.3.3.2.1 Break Reception and Generation

22.3.4 Automatic Baud-Rate Detection

22.3.4.1 Transmitting a Break/Synch Field

22.3.5 IrDA Encoding and Decoding

22.3.5.1 IrDA Encoding

22.3.5.2 IrDA Decoding

22.3.6 Automatic Error Detection

22.3.7 eUSCI_A Receive Enable

22.3.7.1 Receive Data Glitch Suppression

22.3.8 eUSCI_A Transmit Enable

22.3.9 UART Baud-Rate Generation

22.3.9.1 Low-Frequency Baud-Rate Generation

22.3.9.2 Oversampling Baud-Rate Generation

22.3.10 Setting a Baud Rate

22.3.10.1 Low-Frequency Baud-Rate Mode Setting

22.3.10.2 Oversampling Baud-Rate Mode Setting

22.3.11 Transmit Bit Timing - Error calculation

22.3.11.1 Low-Frequency Baud-Rate Mode Bit Timing

22.3.11.2 Oversampling Baud-Rate Mode Bit Timing

22.3.12 Receive Bit Timing – Error Calculation

22.3.13 Typical Baud Rates and Errors

22.3.14 Using the eUSCI_A Module in UART Mode With Low-Power Modes

22.3.15 eUSCI_A Interrupts

22.3.15.1 eUSCI_A Transmit Interrupt Operation

22.3.15.2 eUSCI_A Receive Interrupt Operation

22.3.15.3 eUSCI_A Receive Interrupt Operation

22.3.15.4 UCAxIV, Interrupt Vector Generator

22.4 eUSCI_A UART Registers

22.4.1 UCAxCTLW0 Register

22.4.2 UCAxCTLW1 Register

22.4.3 UCAxBRW Register

22.4.4 UCAxMCTLW Register

22.4.5 UCAxSTATW Register

22.4.6 UCAxRXBUF Register

22.4.7 UCAxTXBUF Register

22.4.8 UCAxABCTL Register

22.4.9 UCAxIRCTL Register

22.4.10 UCAxIE Register

22.4.11 UCAxIFG Register

22.4.12 UCAxIV Register

23 Enhanced Universal Serial Communication Interface (eUSCI) – SPI Mode

23.1 Enhanced Universal Serial Communication Interfaces (eUSCI_A, eUSCI_B) Overview

23.2 eUSCI Introduction – SPI Mode

23.3 eUSCI Operation – SPI Mode

23.3.1 eUSCI Initialization and Reset

23.3.2 Character Format

23.3.3 Master Mode

23.3.3.1 4-Pin SPI Master Mode (UCSTEM = 0)

23.3.3.2 4-Pin SPI Master Mode (UCSTEM = 1)

23.3.4 Slave Mode

23.3.4.1 4-Pin SPI Slave Mode

23.3.5 SPI Enable

23.3.5.1 Transmit Enable

23.3.5.2 Receive Enable

23.3.6 Serial Clock Control

23.3.6.1 Serial Clock Polarity and Phase

23.3.7 Using the SPI Mode With Low-Power Modes

23.3.8 SPI Interrupts

23.3.8.1 SPI Transmit Interrupt Operation

23.3.8.2 SPI Receive Interrupt Operation

23.3.8.3 UCxIV, Interrupt Vector Generator

23.4 eUSCI_A SPI Registers

23.4.1 UCAxCTLW0 Register

23.4.2 UCAxBRW Register

23.4.3 UCAxSTATW Register

23.4.4 UCAxRXBUF Register

23.4.5 UCAxTXBUF Register

23.4.6 UCAxIE Register

23.4.7 UCAxIFG Register

23.4.8 UCAxIV Register

23.5 eUSCI_B SPI Registers

23.5.1 UCBxCTLW0 Register

23.5.2 UCBxBRW Register

23.5.3 UCBxSTATW Register

23.5.4 UCBxRXBUF Register

23.5.5 UCBxTXBUF Register

23.5.6 UCBxIE Register

23.5.7 UCBxIFG Register

23.5.8 UCBxIV Register

24 Enhanced Universal Serial Communication Interface (eUSCI) – I2C Mode

24.0.9 Glitch Filtering

24.0.10 Byte Counter

24.0.10.1 Byte Counter Interrupt

24.0.11 Multiple Slave Addresses

24.1 eUSCI_B I2C Registers

24.1.1 UCBxCTLW0 Register

24.1.2 UCBxCTLW1 Register

24.1.3 UCBxBRW Register

24.1.4 UCBxSTATW

24.1.5 UCBxTBCNT Register

24.1.6 UCBxRXBUF Register

24.1.7 UCBxTXBUF

24.1.8 UCBxI2COA0 Register

24.1.9 UCBxI2COA1 Register

24.1.10 UCBxI2COA2 Register

24.1.11 UCBxI2COA3 Register

24.1.12 UCBxADDRX Register

24.1.13 UCBxADDMASK Register

24.1.14 UCBxI2CSA Register

24.1.15 UCBxIE Register

24.1.16 UCBxIFG Register

24.1.17 UCBxIV Register

Important Notice

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc