摘 要

本课题基于 FPGA 实现了数字示波器的设计,采用 FPGA+MCU 的整体结构,整

个系统由信号调理电路,采样保持电路、AD 转换电路,触发控制电路,采样控制电路,

信号存储电路,信号输出电路等部分组成。MCU 作为主控芯片,完成人机交互,由触

发电路给出的触发信号经过 FPGA 处理后,控制产生实时采样信号或者等效采样信号,

经过调理的高频信号由 FPGA 控制采样保持并进行 AD 转换,量化后的信号存放入

FPGA 内部的双口 RAM,同时 FPGA 通过控制双口 RAM 读地址产生信号波形以及对应

据此波信号,通过 MCU 进行处理,然后由 LCD 显示波形。

被测周期信号的频率范围为 10Hz~10MHz,仪器输入阻抗为 1M,显示屏的刻

度为 8 div×10div,垂直分辨率为 8bits,水平显示分辨率≥20 点/ div。垂直灵敏度要

求含 1V/div、0.1V/div 两档。电压测量误差≤5%。实时采样速率≤1MSa/s,等效采样

速率≥200MSa/s;扫描速度要求含 20ms/div、2μs /div、100 ns/div 三档,波形周期测

量误差≤5%。采用内触发方式,上升沿触发,触发电平可调。被测信号的显示波形应

无明显失真。

关键词: FPGA 示波器 MCU

i

�

ABSTRACT

This subject based on FPGA to achieve the design of digital oscilloscope, using FPGA

+ MCU's overall structure, the entire system by the signal conditioning circuit, sample and

hold circuit, AD conversion circuit, trigger control circuit, sampling control circuit, signal

storage circuit, signal output circuit Partly composed. The MCU is used as the master chip

to complete the human-computer interaction. After the trigger signal given by the trigger

circuit is processed by the FPGA, the real-time sampling signal or the equivalent sampling

signal is controlled. The high-frequency signal after conditioning is controlled by the FPGA

to sample and hold and perform AD conversion. The quantized signal is stored in the

dual-port RAM inside the FPGA. At

the FPGA generates the signal

waveform and the corresponding data signal by controlling the dual-port RAM read address.

The MCU processes the waveform and displays the waveform by the LCD.

the same time,

The frequency range of the measured periodic signal is 10Hz ~ 10MHz, the input

impedance of the instrument is 1M , the display scale is 8 div × 10div, the vertical

resolution is 8bits, and the horizontal display resolution is ≥20 points/div. Vertical sensitivity

requirements include 1V/div and 0.1V/div. Voltage measurement error ≤ 5%. Real-time

sampling rate ≤ 1MSa/s, equivalent sampling rate ≥ 200MSa/s; scanning speed requirements

include 20ms/div, 2μs/div, and 100 ns/div third gear, waveform cycle measurement error ≤

5%. Internal trigger mode, rising edge trigger, adjustable trigger level. The waveform of the

signal under test should not be significantly distorted.

Keywords: FPGA Oscilloscope MCU

ii

�

目 录

摘 要 ............................................................................................................................... i

目 录 ............................................................................................................................. iii

第一章 绪 论....................................................................................................................1

1.1 引言......................................................................................................................... 1

1.2 国内外研究现状..................................................................................................... 1

1.3 本文主要研究内容................................................................................................. 1

第二章 系统的整体设计....................................................................................................3

2.1 数字示波器简介........................................................................................................ 3

2.1.1 模拟示波器..................................................................................................... 3

2.1.2 数字示波器..................................................................................................... 3

2.2 FPGA 简介.................................................................................................................4

2.3 系统的整体需求....................................................................................................... 5

2.4 系统的方案设计....................................................................................................... 6

第三章 FPGA 的设计流程.................................................................................................8

3.1 FPGA 设计流程简介.................................................................................................8

3.2 FPGA 开发编程原理.................................................................................................9

3.3 FPGA 软件开发环境.............................................................................................. 10

3.3 FPGA 具体流程...................................................................................................... 11

第四章 系统的硬件设计..................................................................................................13

4.1 FPGA 与 MCU 选型................................................................................................13

4.1.1 ALTERA FPGA..............................................................................................13

4.1.2 STM32 单片机...............................................................................................13

4.2 AD 转换电路模块..............................................................................................15

4.3 阻抗变换..............................................................................................................16

4.4 增益控制方案......................................................................................................17

第五章 系统的软件设计..................................................................................................19

5.1 数字示波器软件设计的系统方案.......................................................................... 19

5.2 FPGA 软件设计.......................................................................................................19

5.3 STM32 软件设计.....................................................................................................19

........................................................................................ 错误!未定义书签。

结束语

.............................................................................................................................22

致谢

参考文献 .............................................................................................................................23

iii

�

第一章 绪 论

1.1 引言

在过去,我们采用各种的集成电路来完成数字系统的设计,因此,我们需要精心

的选择各种各样的器件来搭建系统,而且还需要真值表等设计的工具来完成电路的设

计,在今天,越来越多的大规模系统被开发,显然这种方法不能满足目前的要求。

因此,出现了一种芯片内部的设计方法,我们可以通过自己的需求来定义这些器

件的引脚和功能,只需要对这些可编程的逻辑器件进行设计就可以完成我们所需的功

能,因此出现了强大的自动化电子设计工具,以及完善的硬件描述语言,这种可编程

的逻辑器件,将是以后数字系统发展的重要途径。本课题采用 FPGA 实现数字示波器

的设计,具有极大的理论研究意义和实践的价值。

1.2 国内外研究现状

高端市场上的数字存储示波器已被国外垄断,特别是在绝大多数泰克示波器市场

中,并且是示波器安捷伦电力巨头垄断企业的代表。目前,数字示波器不仅向高带宽,

高采样率方向发展,而且向多功能方向发展。由于现代电路的复杂性越来越高,测试

电路需要更多的辅助工具,因此示波器增加了专用分析模块,例如高速串行数据分析

功能可以对串行数据进行解码,并从数据串中恢复原始数据。美国公司专注于开发虚

拟设备,其虚拟示波器的发展非常迅速。现在,一款模拟混合示波器已经开发完成。

它结合了数字示波器和逻辑分析仪。它不仅可以分析模拟信号,还可以分析多路数字

信号,适合分析和调试混合信号电路。数字存储示波器没有余辉效应,因此无法观察

到复杂的信号。数字荧光示波器成功解决了这个问题。它采用特殊的显示模式将采集

到的数据直接显示在显示屏上,提高了波形的刷新率。光通信示波器还有专门用于现

代光纤通信应用的专用光学示波器。有示波器组合“,它将数字示波器和模拟示波器

集成在一起,充分发挥这两种示波器的优势。

示波器在中国的发展起步较晚,核心采样芯片受到国外的限制。数字存储示波器

市场一直处于中低端产品。目前,国内市场上带宽最高的数字存储示波器产品显示为

“,作为 RIGOL 公司之一的中国数字示波器是增长最快的公司之一,在生产低端示波

器方面与国外的性能并没有太大的差别。但高端示波器与国外同类产品存在较大差距,

因此高端示波器的研究是我国未来的主要目标。

1.3 本文主要研究内容

- 1 -

�

本文选择 Altera 公司的低端 FPGA Cyclone EP1C6Q240 和 STM32 单片机作为

主控单元,论文主要工作如下:

(1)示波器的整体设计,包括示波器的的介绍以及 FPGA 的介绍,完成系统的整

体需求分析,制订了系统的方案。

(2)掌握 FPGA 设计的整体流程

(3)系统的硬件设计,包括 FPGA 和 MCU 的选型,以及 ADC 电路、阻抗变换

电路和增益控制电路的设计

(4)系统的软件设计,包括示波器的软件设计整体方案,以及 FPGA 软件和 STM32

软件的设计。

- 2 -

�

第二章 系统的整体设计

2.1 数字示波器简介

2.1.1 模拟示波器

模拟示波器的工作模式是直接测量信号电压,并通过示波器屏幕的电子束在垂直

方向上显示电压以显示波形[7]。模拟示波器的基本组件包括前端衰减电路,前端放大

器电路和平衡反相阶段。在模拟电路中,通过时钟的时基电路产生各种频率,并发送

给电子开关,电子开关利用该时间对采样信号进行采样,然后使用相应的时基发送给

放大器,信号经过发送给 CRT 来显示。

传统的模拟示波器已经观测到两个电信号被加到 CRT 的 X 和 Y 上来控制电子束的

偏移,以便我们可以在屏幕上得到两个电信号的波形。模拟示波器通常由示波器管,Y

轴放大器,X 轴放大器扫描发生器,电源和测试探头组成。

模拟示波器由垂直系统,水平系统,Z 轴电路,中央处理器(CPU)和电源模块组

成。

2.1.2 数字示波器

数字存储示波器(DSO)利用 A/D 转换技术和数字存储术,根据取样定理的原则,

迅速捕捉瞬时信号并保存、重现信号[8]。首先它可以对模拟信号进行高速采样转换,

相应的采样数据将被储存下来,送到处理器进行相关的处理和运算,得到所需要的被

测信号参数。最后,根据获得的信号参数在液晶显示屏上重建信号波形,可以对被测

信号进行实时瞬态信号分析,让用户了解信号的特性,帮助用户既准确由快速地进行

故障诊断。由于数字存储示波器有实时采样的特性,因此数字存储示波器不但可以检

测到重复周期信号,还能检测到非周期性单次信号或随机信号。

与传统的模拟示波器相比,数字存储示波器具有很大的优势,主要体现在以下几

个方面[9]:

1,多通道信号采集:数字存储示波器可以在多个通道中同时采集单个瞬态事件。

2,波形处理:数字存储示波器在微处理器内部使用,它可以完成波形和波形运算

功能中的幅度和时间参数,再加上一些选项将在更复杂的数学运算后完成,如积分,

指数,对数,平均值,数字滤波,极速,快速傅里叶变换方式,帮助用户快速获取信

号参数。

3,数据存储和回放:数字存储示波器具有非易失性波形存储器。他们可以提供与

- 3 -

�

DSO 兼容的存储设备,如 U 盘,软盘等,并且很容易与许多绘图仪和打印机连接。

高质量的硬拷贝被执行。

4,更多触发功能:数字存储示波器还不提供模拟示波器的触发功能。例如,发生

故障时,可以在触发前触发并获取波形数据,便于比较。

5,自动测试:数字存储示波器提供自动测试功能,简化用户操作,智能仪表的特

点,信号触发捕捉过程中,往往只需按下自动调节按钮,即可获得最佳观测信号波形。

测得的信号被送到衰减电路,前置放大电路,然后通过 AD 转换转换成数字信号。

首先,数字信号被存储在数据缓冲器中。然后处理器从缓冲区读取数据并对其进行处

理。处理完成后,它将它发送到控制单元驱动 LCD 显示。同时,控制单元接受按键控

制并更改波形显示的参数。

2.2 FPGA 简介

FPGA 和 CPLD 并没有本质的区别,只不过实现的方式略有不同,采用现场可编

程门阵列和复杂可编程逻辑器件,我们可以实现几乎所有的数字系统,他们都是可编

程的,而实现的方式主要有采用 VHDL 或者 Verilog 语言、原理图这两种的方式,而

且,强大的 EDA 软件可以仿真用户所设计的数字系统是否可以满足要求。

采用 FPGA 的另外的一个优点是,在硬件电路板设计完成后,我们可以通过自己

的实际需求来更改系统,而不需要重新制作电路,这样不仅节省了时间,而且还介绍

了硬件的成本,可以在很大的程度上提高开发的效率。

近年来,硬件描述语言也有了快速的发展,可以说,EDA 软件和硬件描述语言共

同促进了 FPGA 在电子设计中的应用,FPGA 通常由以下的三种组成:

1、可编程逻辑模块

可编程逻辑模块是 FPGA 的主要组成部分。其组成部分如下:

(1) 逻辑函数发生器

这 3 个函数发生器可以命名为 G、F 和 H。则 G’、F’和 H’为对应的输出。

G

F

G 和 F 相互独立,可以完成任意的逻辑的组合。

H

前两个是 G 和 F 的输出,而第三个为电路的输入,所以,函数发生器只需要 3 个

也有 个输入变量 、 、 和 ;

有 个输入变量 、 、 和 ;

有 个输入变量 、 、 ;

G G

1

1

F

2

F

3

F

H H

1

2

H

3

G

4

G

4

F

4

3

2

4

3

输入,就可以实现 9 路不同的输出。

- 4 -

�

(2) 触发器

(3) 数据选择器

FPGA 中有许多不同的数据选择器,比如 4 选 1 或者 2 选 1,通过硬件描述语言,

我们可以实现不同输入信号的选择性输出,改变的只是内部选择器的结构,并且对输

入信号的模式,比如上升沿、下降等等特征作出体现,改变 FPGA 内部的结构。

2、输入/输出模块

输入/输出模块提供了器件引脚和内部逻辑阵列之间的连接。其主要的组成是:

(1) 输入触发器;

(2) 输入缓冲器;

(3) 输出触发/锁存器;

(4) 输出缓冲器组成。

每一个的输入/输出对应了一个 FPGA 的引脚,这些引脚可以被方便的配置为

Input、output 或者 inout 这三种不同的模式。被配置为 Input 的时候,信号首先经过的

是缓存器。而缓存器的输出也有两种,一是直接的输出,二是通过 D 触发器和数据选

择器的延时输出。同样,通过编程,我们可以实现对这两种方式的控制。

当引脚被配置为输出时,同样是两种,直接输出和延时输出。延时输出通过缓存

器保存输出的内容。

3、互连资源

2.3 系统的整体需求

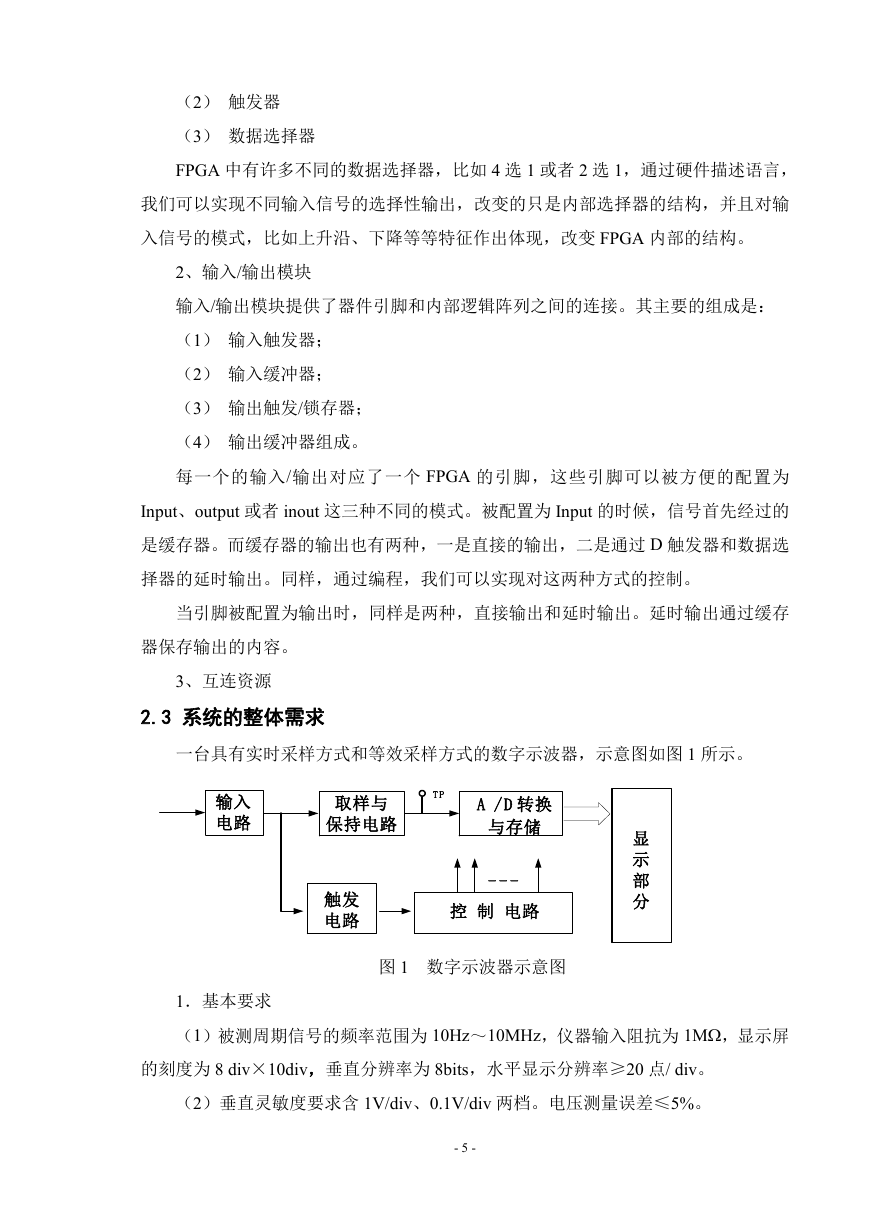

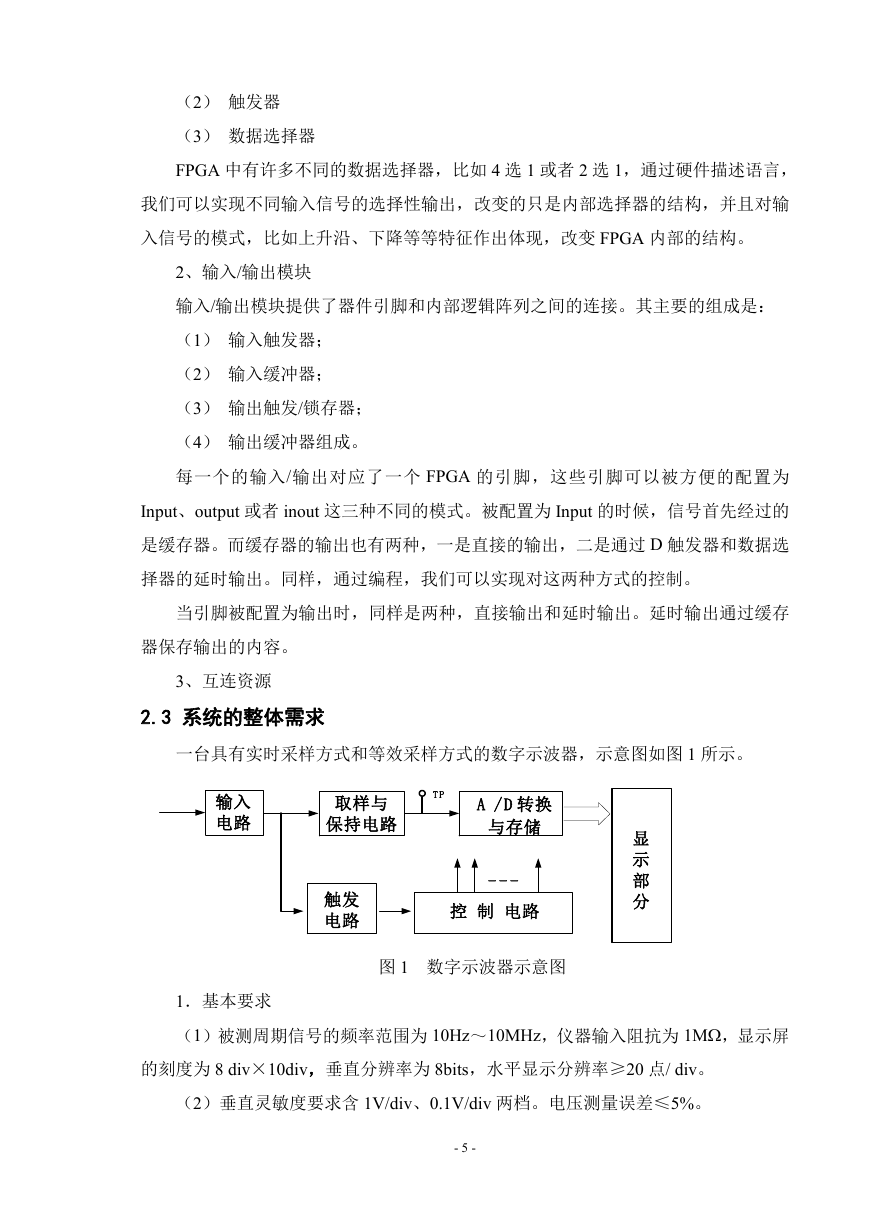

一台具有实时采样方式和等效采样方式的数字示波器,示意图如图 1 所示。

输入

电路

T P

取样与

保持电路

A / D 转换

与存储

触发

电路

控 制 电路

图 1 数字示波器示意图

显

示

部

分

1.基本要求

(1)被测周期信号的频率范围为 10Hz~10MHz,仪器输入阻抗为 1M,显示屏

的刻度为 8 div×10div,垂直分辨率为 8bits,水平显示分辨率≥20 点/ div。

(2)垂直灵敏度要求含 1V/div、0.1V/div 两档。电压测量误差≤5%。

- 5 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc