基于 FPGA 的 CPLD 可编程器件的信号音发生器设计

一、 技术指标

1、设计目的

<1>.掌握 CPLD 可编程器件的编程和下载方法。

<2>.熟悉用 CPLD 可编程器件产生程控交换中信令信号的方法。

2、设计要求

系统给 CPLD 可编程器件提供的全局时钟为 32.768KHz,在 CPLD 可编程器

件中通过分频近似地产生出如下 4 种信号音:

拨号音:连续发送的 512Hz 信号。

回铃音:1 秒通,4 秒断的 5 秒断续的 512Hz 信号。

忙音:0.5 秒通,0.5 秒断的 1 秒断续的 512Hz 信号。

振铃信号(铃流):频率为 25Hz,以 1 秒通,4 秒断的 5 秒断续方式发送。

二、设计的原理及设计流程

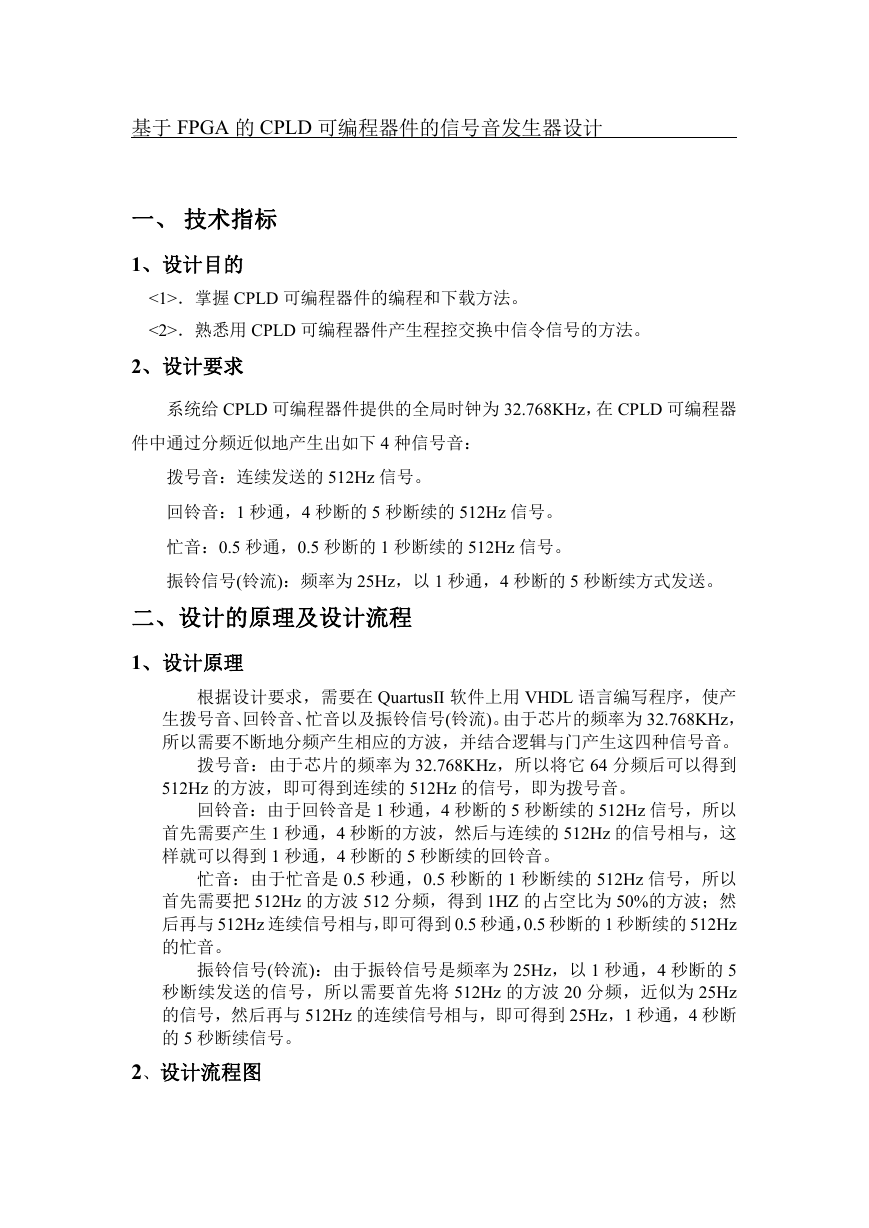

1、设计原理

根据设计要求,需要在 QuartusII 软件上用 VHDL 语言编写程序,使产

生拨号音、回铃音、忙音以及振铃信号(铃流)。由于芯片的频率为 32.768KHz,

所以需要不断地分频产生相应的方波,并结合逻辑与门产生这四种信号音。

拨号音:由于芯片的频率为 32.768KHz,所以将它 64 分频后可以得到

512Hz 的方波,即可得到连续的 512Hz 的信号,即为拨号音。

回铃音:由于回铃音是 1 秒通,4 秒断的 5 秒断续的 512Hz 信号,所以

首先需要产生 1 秒通,4 秒断的方波,然后与连续的 512Hz 的信号相与,这

样就可以得到 1 秒通,4 秒断的 5 秒断续的回铃音。

忙音:由于忙音是 0.5 秒通,0.5 秒断的 1 秒断续的 512Hz 信号,所以

首先需要把 512Hz 的方波 512 分频,得到 1HZ 的占空比为 50%的方波;然

后再与 512Hz 连续信号相与,即可得到 0.5 秒通,0.5 秒断的 1 秒断续的 512Hz

的忙音。

振铃信号(铃流):由于振铃信号是频率为 25Hz,以 1 秒通,4 秒断的 5

秒断续发送的信号,所以需要首先将 512Hz 的方波 20 分频,近似为 25Hz

的信号,然后再与 512Hz 的连续信号相与,即可得到 25Hz,1 秒通,4 秒断

的 5 秒断续信号。

2、设计流程图

�

三、 调试与仿真

1、调试与仿真

打开 QuartusII 软件,建立新的工程,输入相应的程序并运行。当运行没有错误时,把它

下载到 EPM7064LC44-10 芯片上,用排线连接相应的引脚,听蜂鸣器发出的声音,看是

否符合实验的要求。当声音符合要求时,用示波器看各个引脚的波形,如果也是正确的,

即完成了实验的要求,达到了实验的目的。

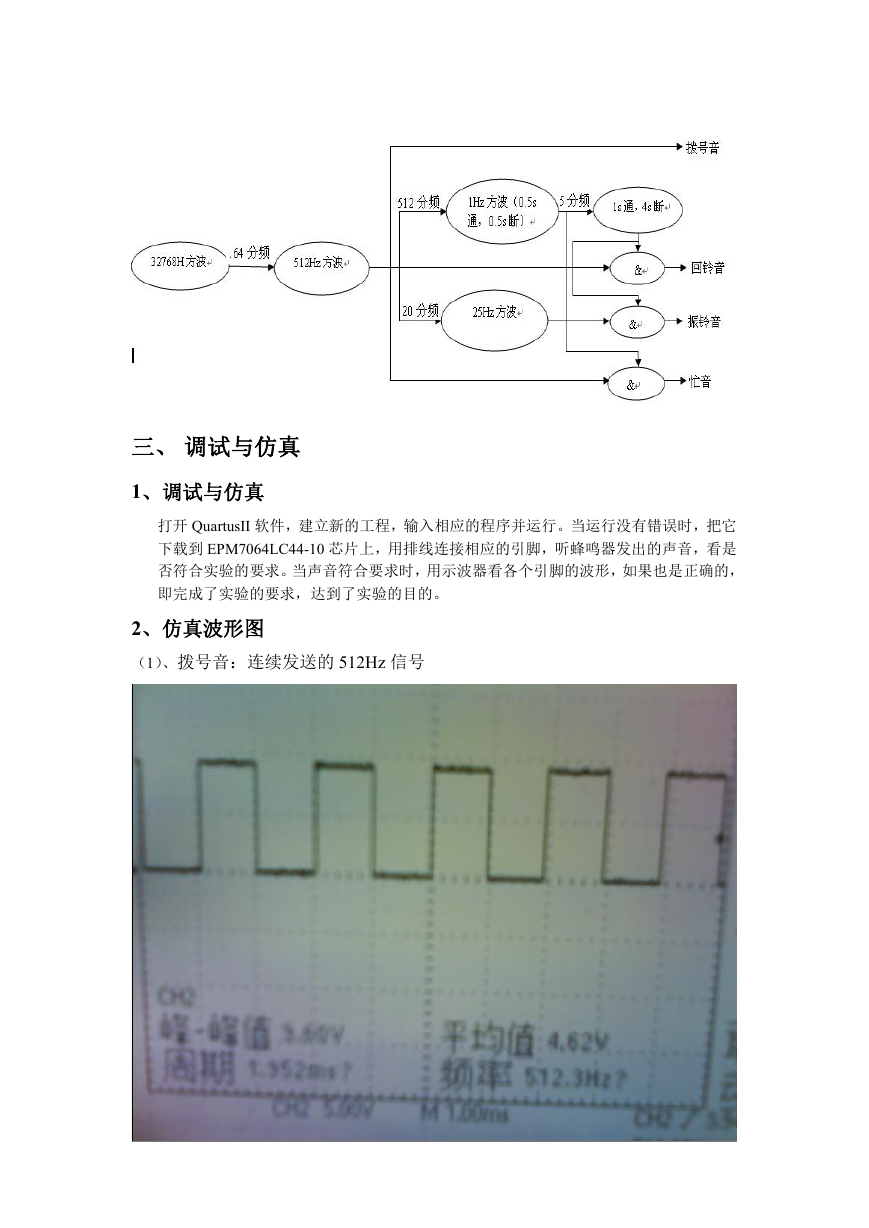

2、仿真波形图

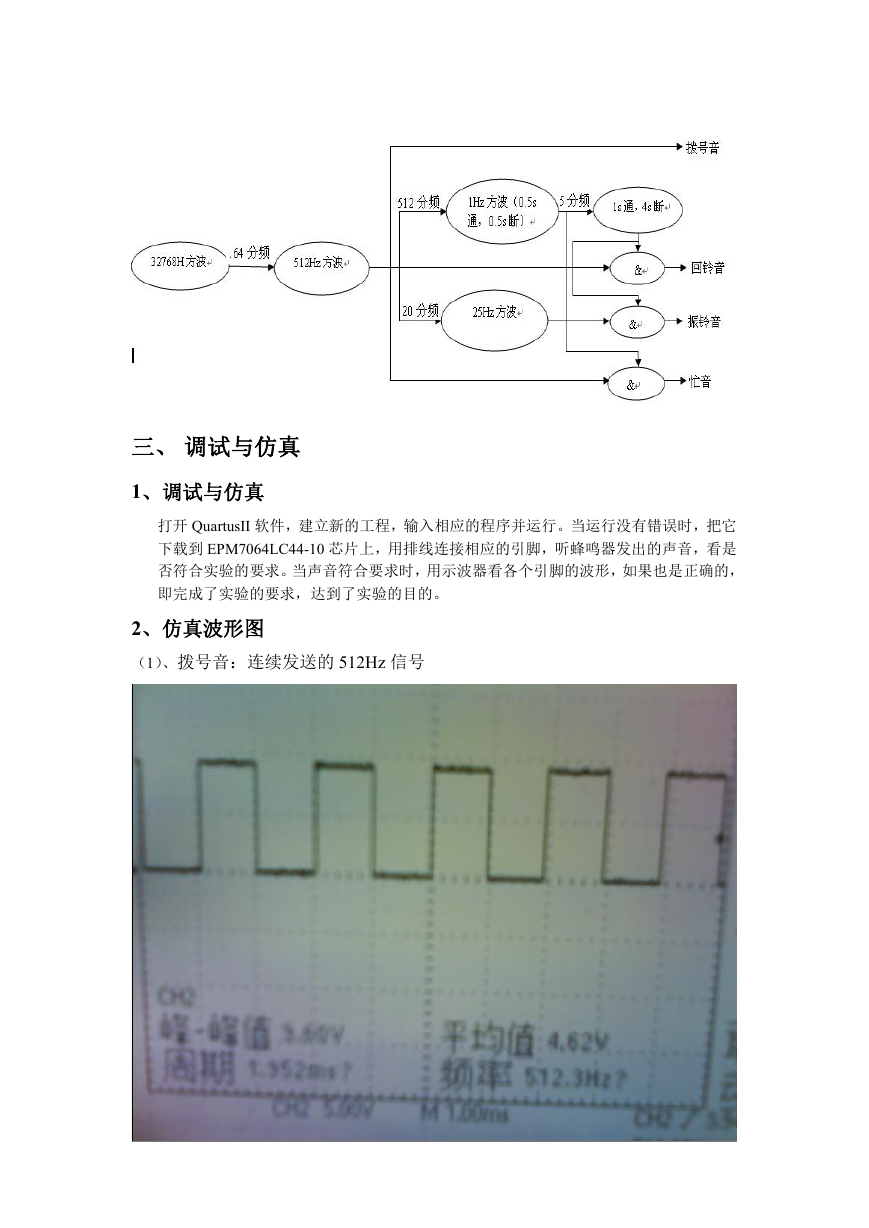

(1)、拨号音:连续发送的 512Hz 信号

�

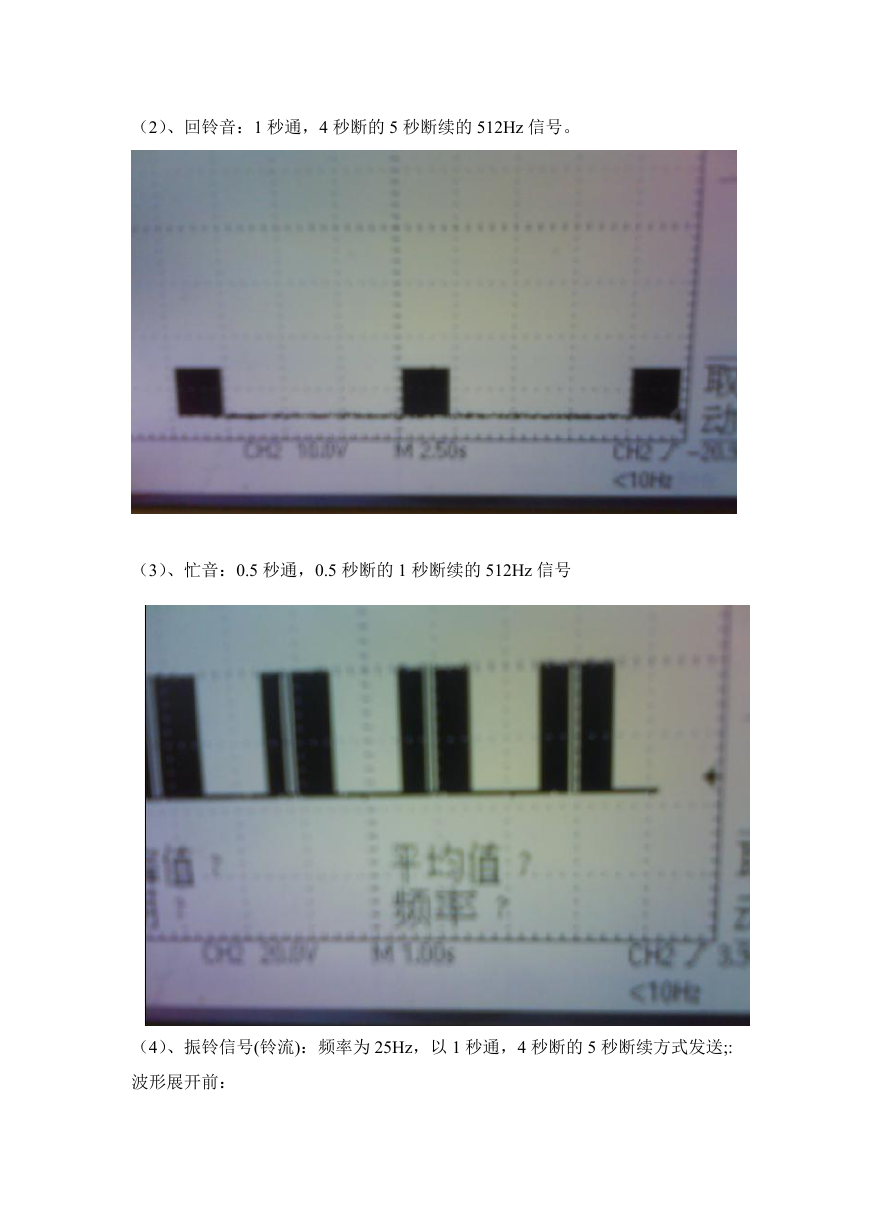

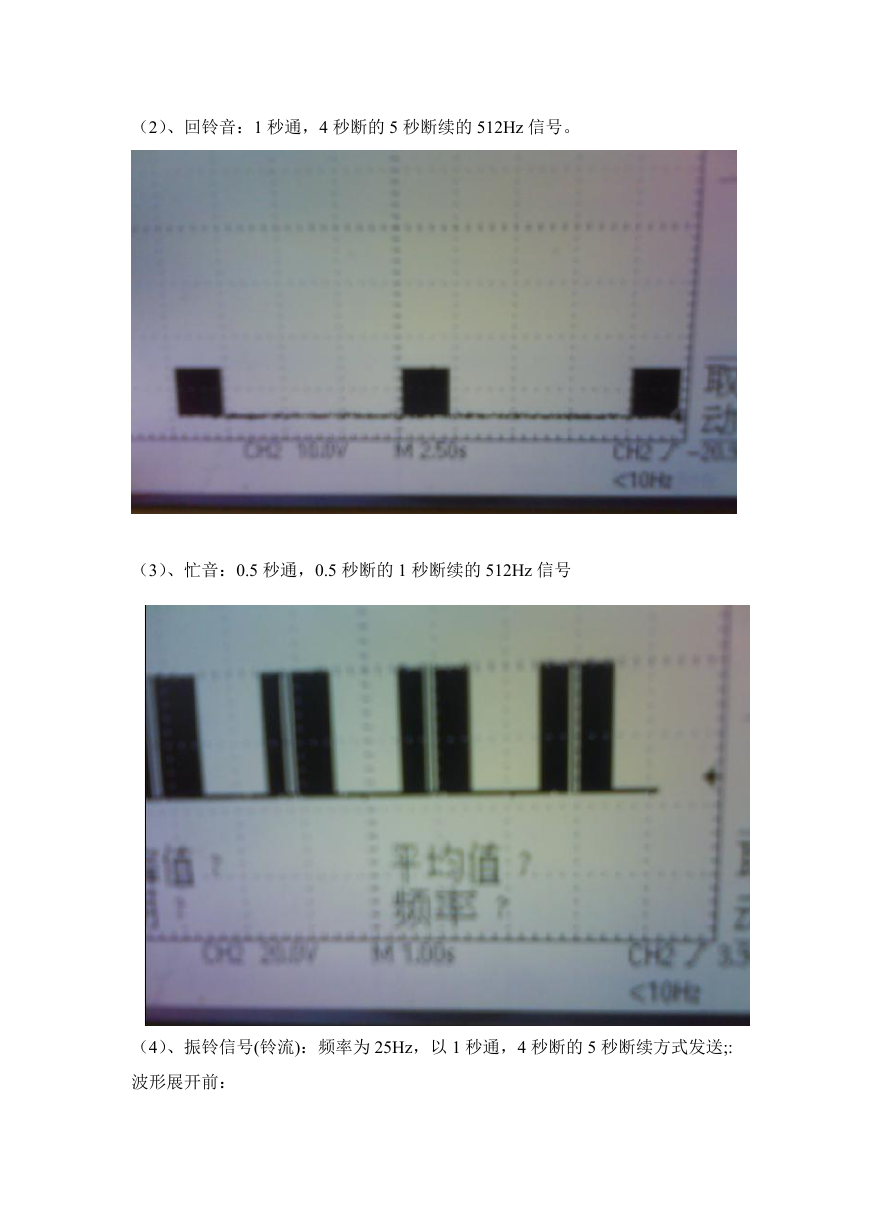

(2)、回铃音:1 秒通,4 秒断的 5 秒断续的 512Hz 信号。

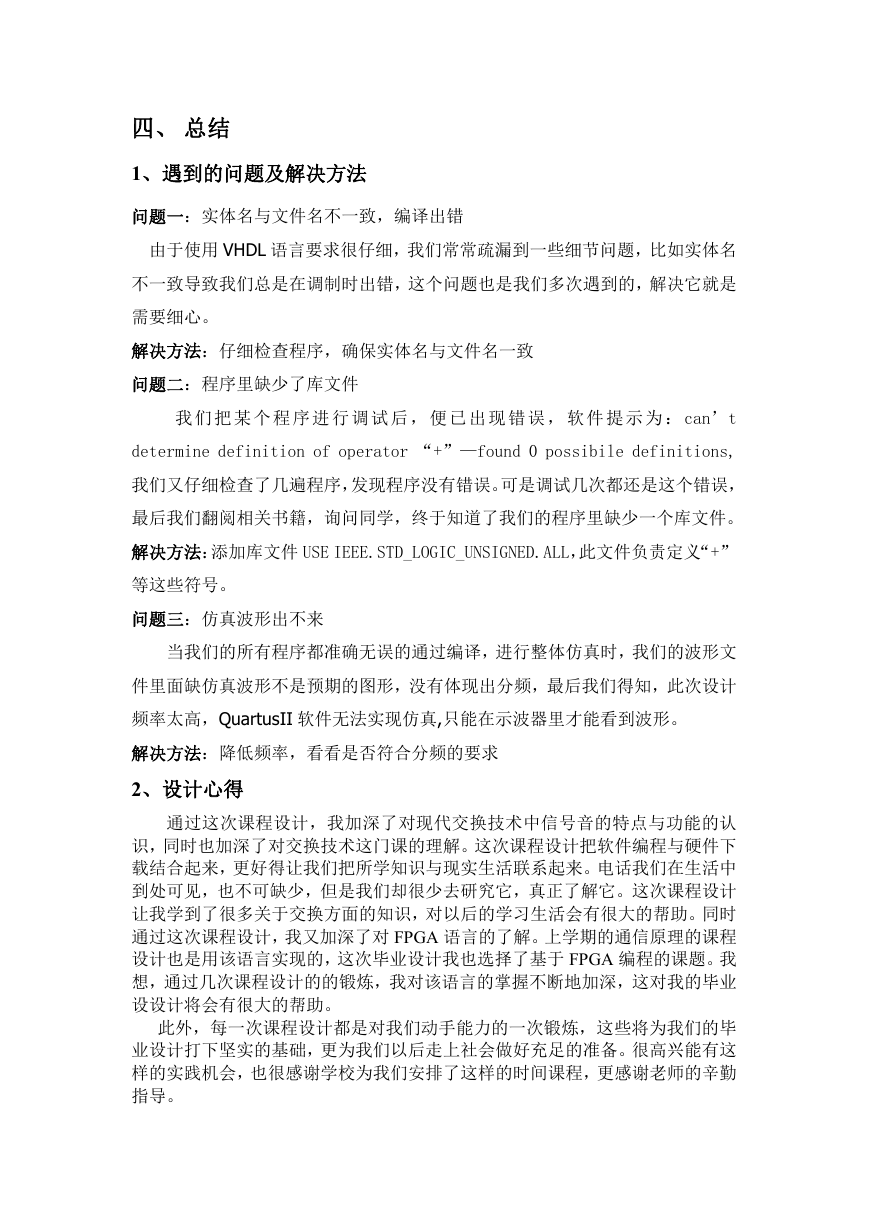

(3)、忙音:0.5 秒通,0.5 秒断的 1 秒断续的 512Hz 信号

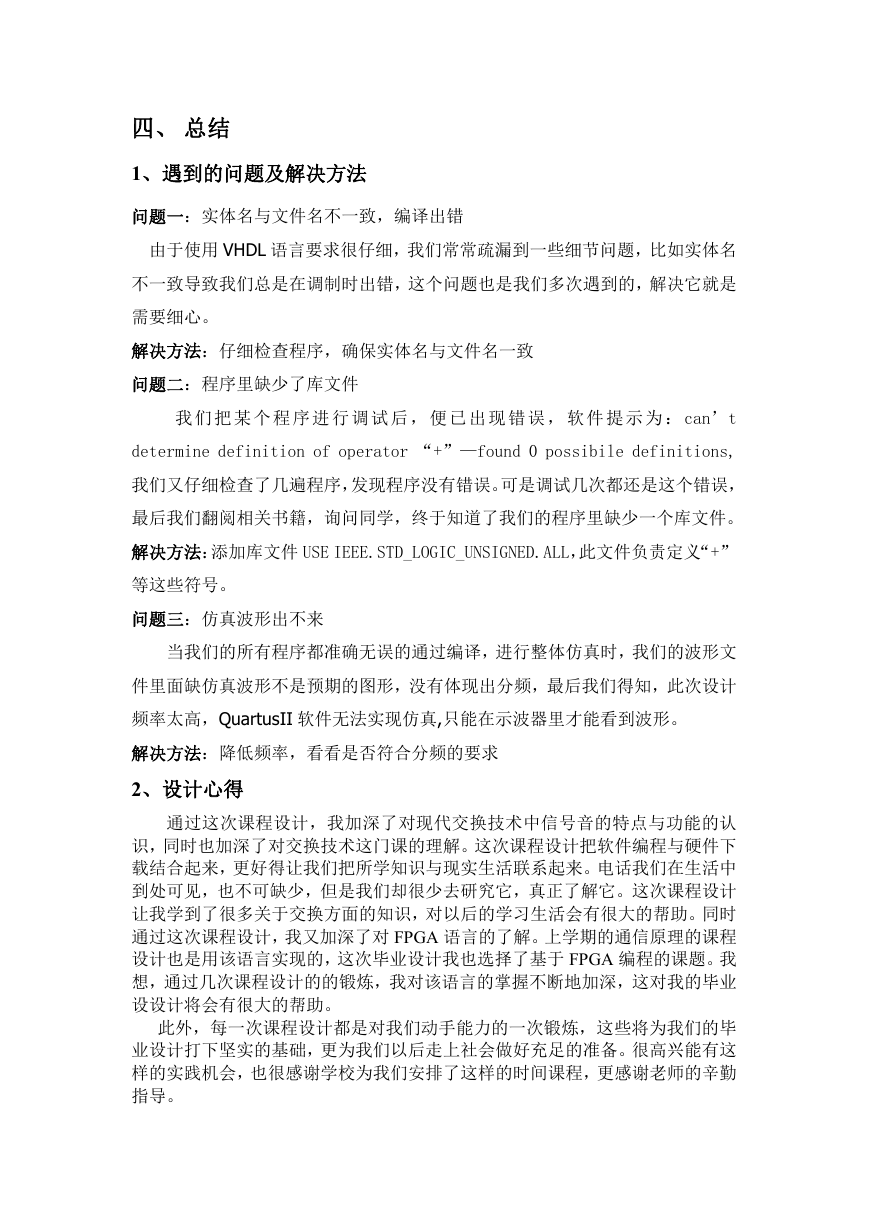

(4)、振铃信号(铃流):频率为 25Hz,以 1 秒通,4 秒断的 5 秒断续方式发送;:

波形展开前:

�

波形展开后:

�

四、 总结

1、遇到的问题及解决方法

问题一:实体名与文件名不一致,编译出错

由于使用 VHDL 语言要求很仔细,我们常常疏漏到一些细节问题,比如实体名

不一致导致我们总是在调制时出错,这个问题也是我们多次遇到的,解决它就是

需要细心。

解决方法:仔细检查程序,确保实体名与文件名一致

问题二:程序里缺少了库文件

我 们 把 某 个 程 序 进 行 调 试 后 , 便 已 出 现 错 误 , 软 件 提 示 为 : can’t

determine definition of operator “+”—found 0 possibile definitions,

我们又仔细检查了几遍程序,发现程序没有错误。可是调试几次都还是这个错误,

最后我们翻阅相关书籍,询问同学,终于知道了我们的程序里缺少一个库文件。

解决方法:添加库文件 USE IEEE.STD_LOGIC_UNSIGNED.ALL,此文件负责定义“+”

等这些符号。

问题三:仿真波形出不来

当我们的所有程序都准确无误的通过编译,进行整体仿真时,我们的波形文

件里面缺仿真波形不是预期的图形,没有体现出分频,最后我们得知,此次设计

频率太高,QuartusII 软件无法实现仿真,只能在示波器里才能看到波形。

解决方法:降低频率,看看是否符合分频的要求

2、设计心得

通过这次课程设计,我加深了对现代交换技术中信号音的特点与功能的认

识,同时也加深了对交换技术这门课的理解。这次课程设计把软件编程与硬件下

载结合起来,更好得让我们把所学知识与现实生活联系起来。电话我们在生活中

到处可见,也不可缺少,但是我们却很少去研究它,真正了解它。这次课程设计

让我学到了很多关于交换方面的知识,对以后的学习生活会有很大的帮助。同时

通过这次课程设计,我又加深了对 FPGA 语言的了解。上学期的通信原理的课程

设计也是用该语言实现的,这次毕业设计我也选择了基于 FPGA 编程的课题。我

想,通过几次课程设计的的锻炼,我对该语言的掌握不断地加深,这对我的毕业

设设计将会有很大的帮助。

此外,每一次课程设计都是对我们动手能力的一次锻炼,这些将为我们的毕

业设计打下坚实的基础,更为我们以后走上社会做好充足的准备。很高兴能有这

样的实践机会,也很感谢学校为我们安排了这样的时间课程,更感谢老师的辛勤

指导。

�

五、 参考文献

【1】《现代程控交换实验指导书》 陶剑锋、盛惠兴、张秀平编,2005 年 6 月

【2】《EDA 技术及应用》 谭会生 张昌凡 编著 西安电子科技大学出版,2006 年 12 月

【3】《CPLD/FPGA 应用开发技术与工程实践》求是科技 编著 人民邮电出版 2004 年 11 月

【4】《现代交换原理》 金惠文 陈建亚 编著 电子工业出版社 2006 年 1 月

六、附件

--1Hz

源程序代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity entity512 is

port(clk:in std_logic;

clk_div512:out std_logic);

end entity512;

architecture rtl256 of entity512

signal clk_temp:std_logic:='0';

signal

begin

process(clk)

begin

is

count:std_logic_vector(8 downto 0):="000000000";

if(clk'event and clk='1') then

if(count="111111111")then

clk_temp<=not clk_temp;

count<="000000000";

else count<=count+1;

end if;

end if;

end process;

clk_div512<=clk_temp;

end rtl256;

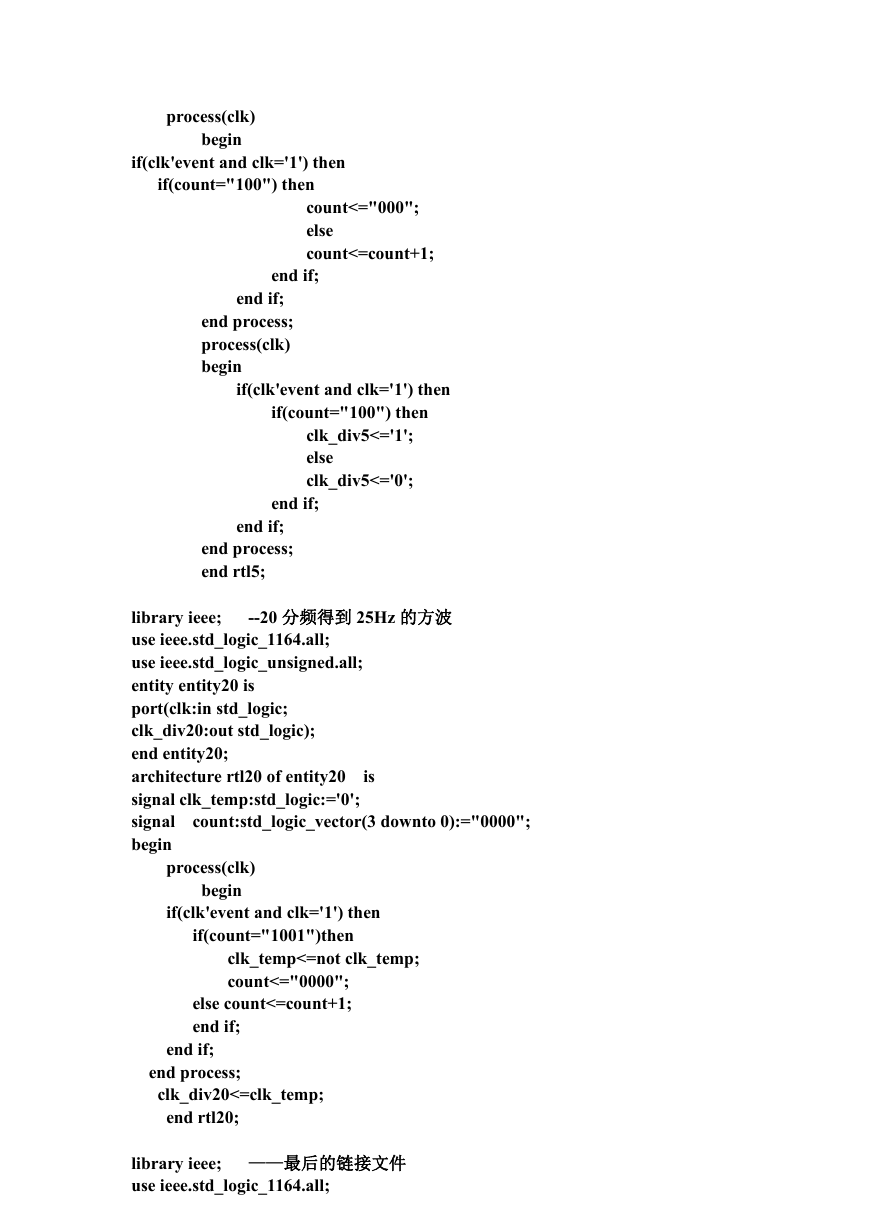

library ieee; ——1 秒通 4 秒断的脉冲信号

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity entity5 is

port(clk:in std_logic;

clk_div5:out std_logic);

end entity5;

architecture rtl5 of entity5

signal count:std_logic_vector(2 downto 0):="000";

begin

is

�

process(clk)

begin

if(clk'event and clk='1') then

if(count="100") then

count<="000";

else

count<=count+1;

count:std_logic_vector(3 downto 0):="0000";

end if;

end if;

end process;

process(clk)

begin

end if;

end if;

end process;

end rtl5;

if(clk'event and clk='1') then

if(count="100") then

clk_div5<='1';

else

clk_div5<='0';

--20 分频得到 25Hz 的方波

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity entity20 is

port(clk:in std_logic;

clk_div20:out std_logic);

end entity20;

architecture rtl20 of entity20

signal clk_temp:std_logic:='0';

signal

begin

is

process(clk)

begin

if(clk'event and clk='1') then

if(count="1001")then

clk_temp<=not clk_temp;

count<="0000";

else count<=count+1;

end if;

end if;

end process;

clk_div20<=clk_temp;

end rtl20;

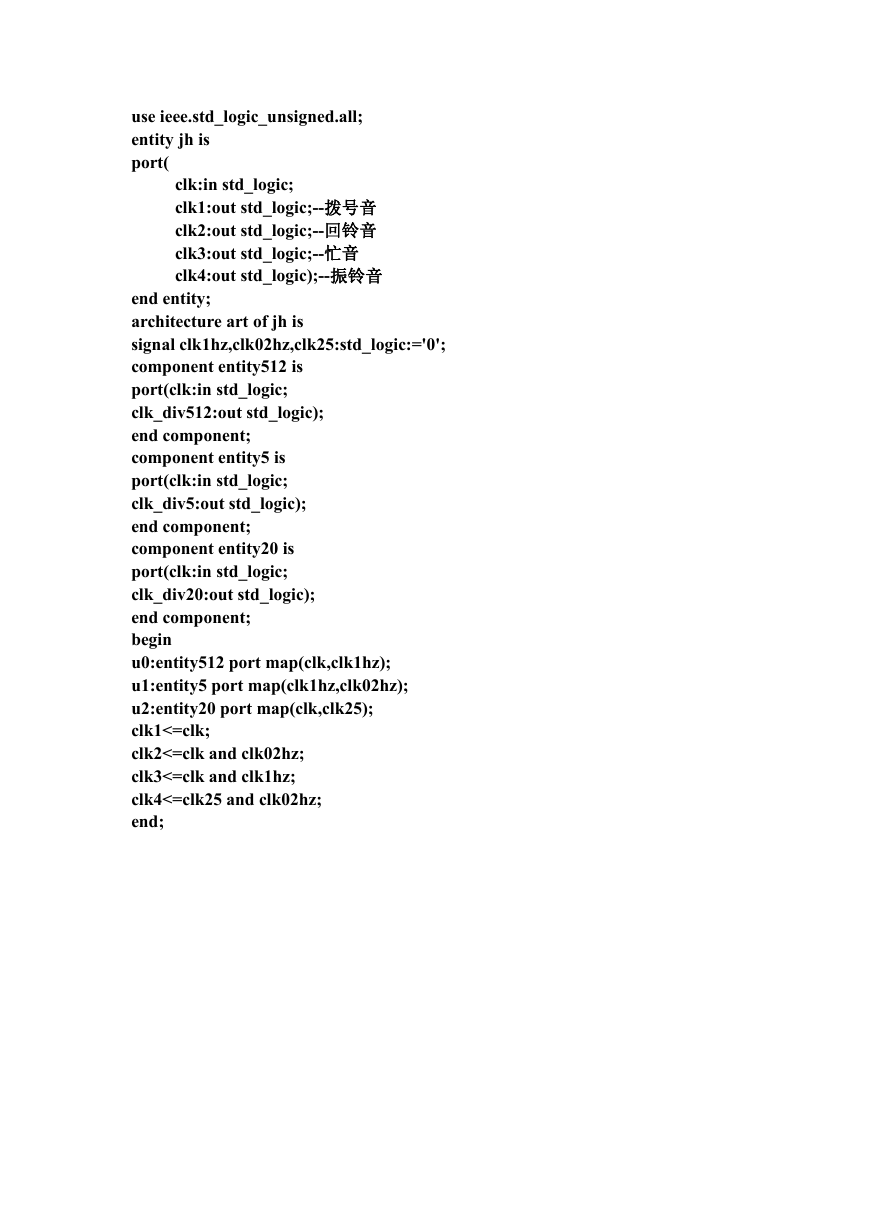

library ieee; ——最后的链接文件

use ieee.std_logic_1164.all;

�

use ieee.std_logic_unsigned.all;

entity jh is

port(

clk:in std_logic;

clk1:out std_logic;--拨号音

clk2:out std_logic;--回铃音

clk3:out std_logic;--忙音

clk4:out std_logic);--振铃音

end entity;

architecture art of jh is

signal clk1hz,clk02hz,clk25:std_logic:='0';

component entity512 is

port(clk:in std_logic;

clk_div512:out std_logic);

end component;

component entity5 is

port(clk:in std_logic;

clk_div5:out std_logic);

end component;

component entity20 is

port(clk:in std_logic;

clk_div20:out std_logic);

end component;

begin

u0:entity512 port map(clk,clk1hz);

u1:entity5 port map(clk1hz,clk02hz);

u2:entity20 port map(clk,clk25);

clk1<=clk;

clk2<=clk and clk02hz;

clk3<=clk and clk1hz;

clk4<=clk25 and clk02hz;

end;

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc