PCIE 系统架构及物理层一致性测试

�

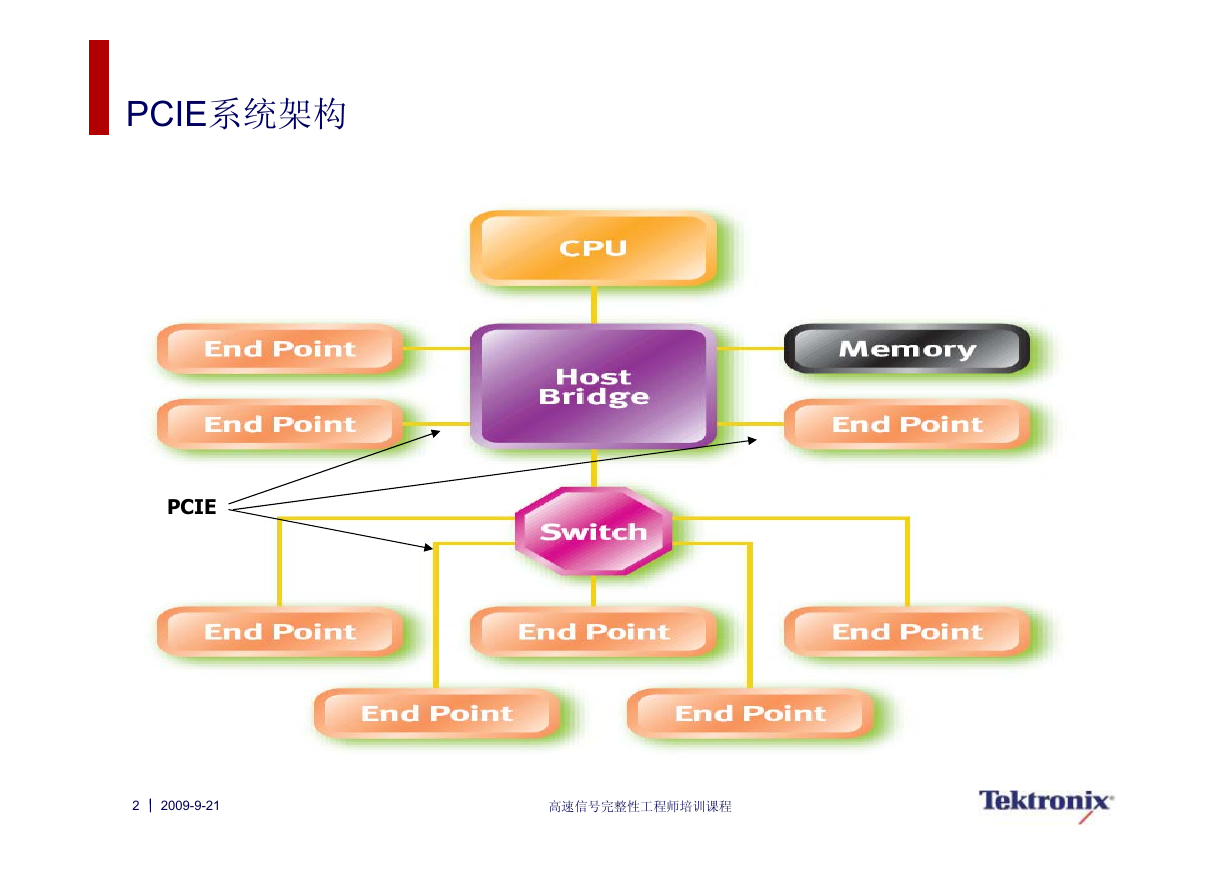

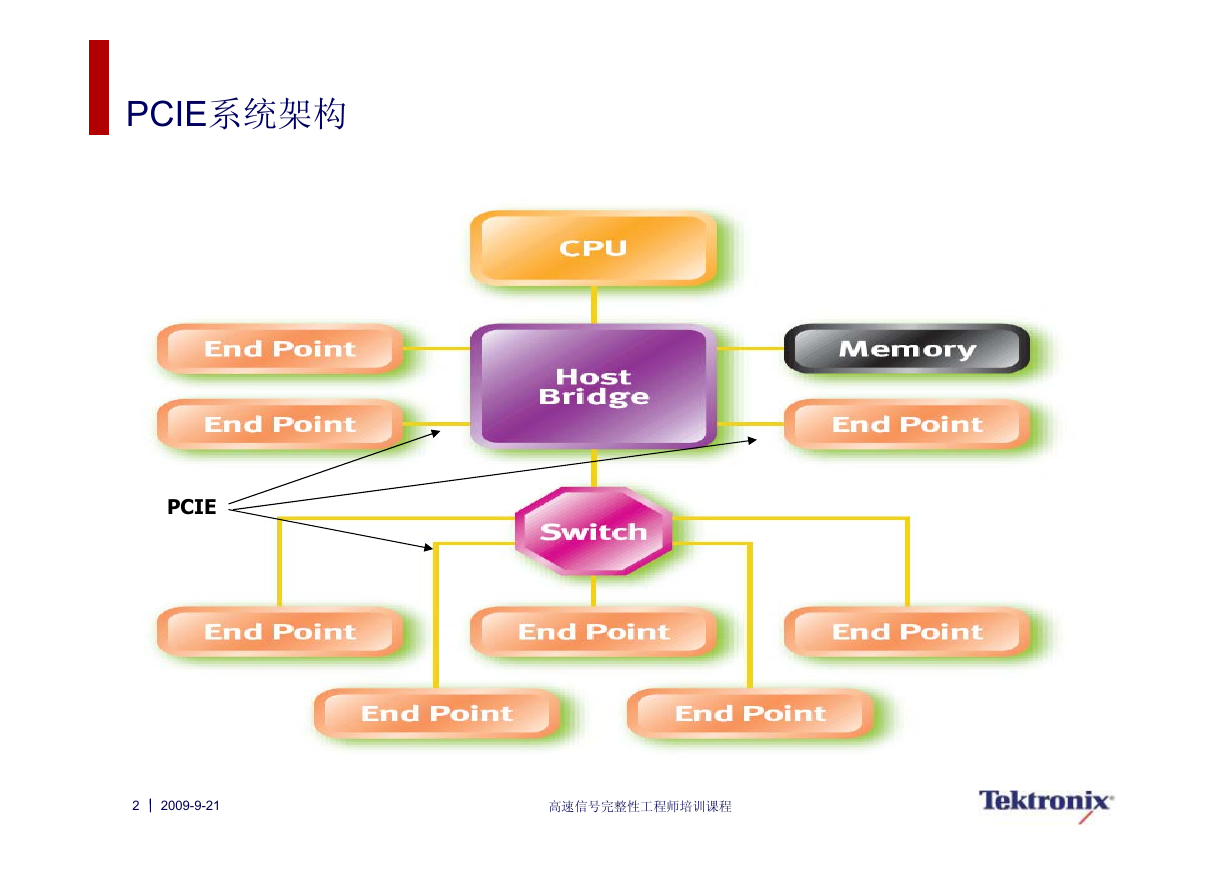

PCIE系统架构

PCIE

2

2009-9-21

高速信号完整性工程师培训课程

�

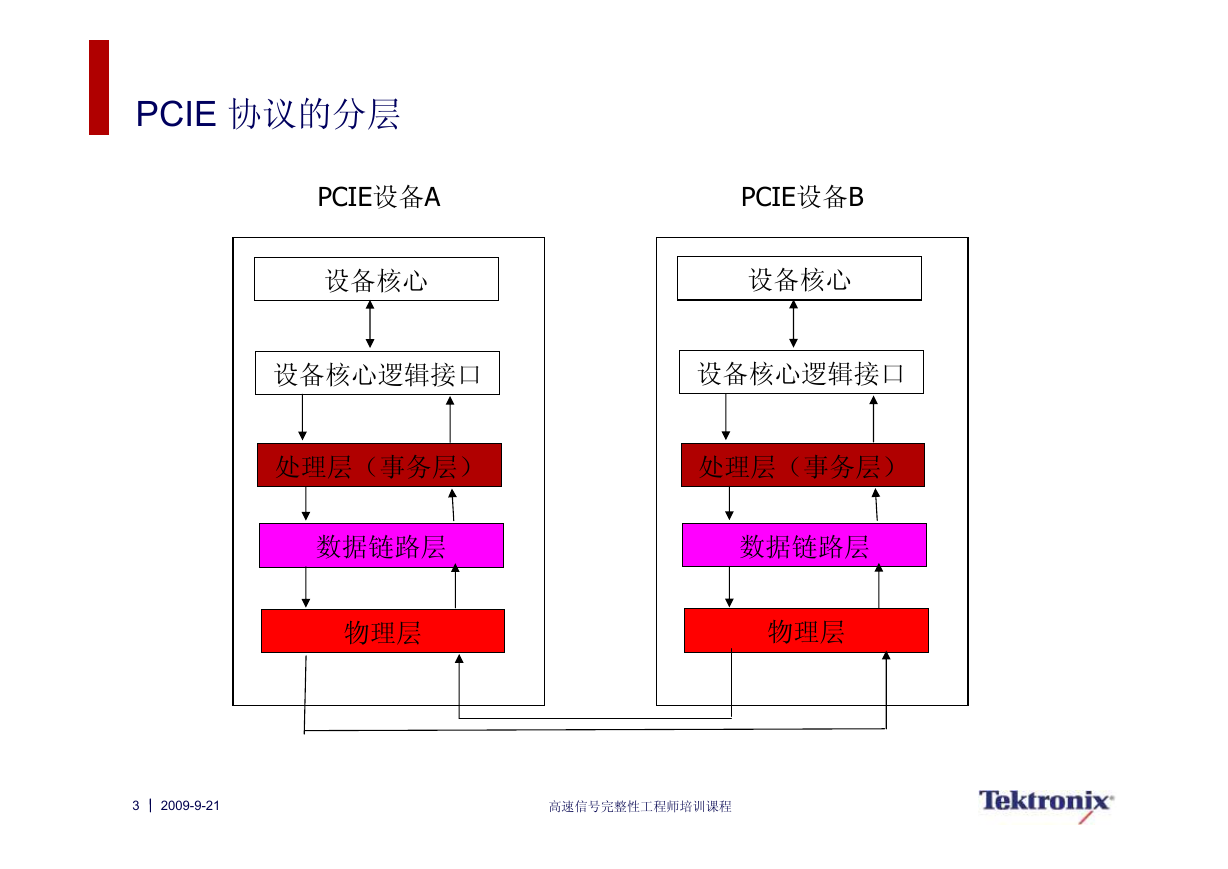

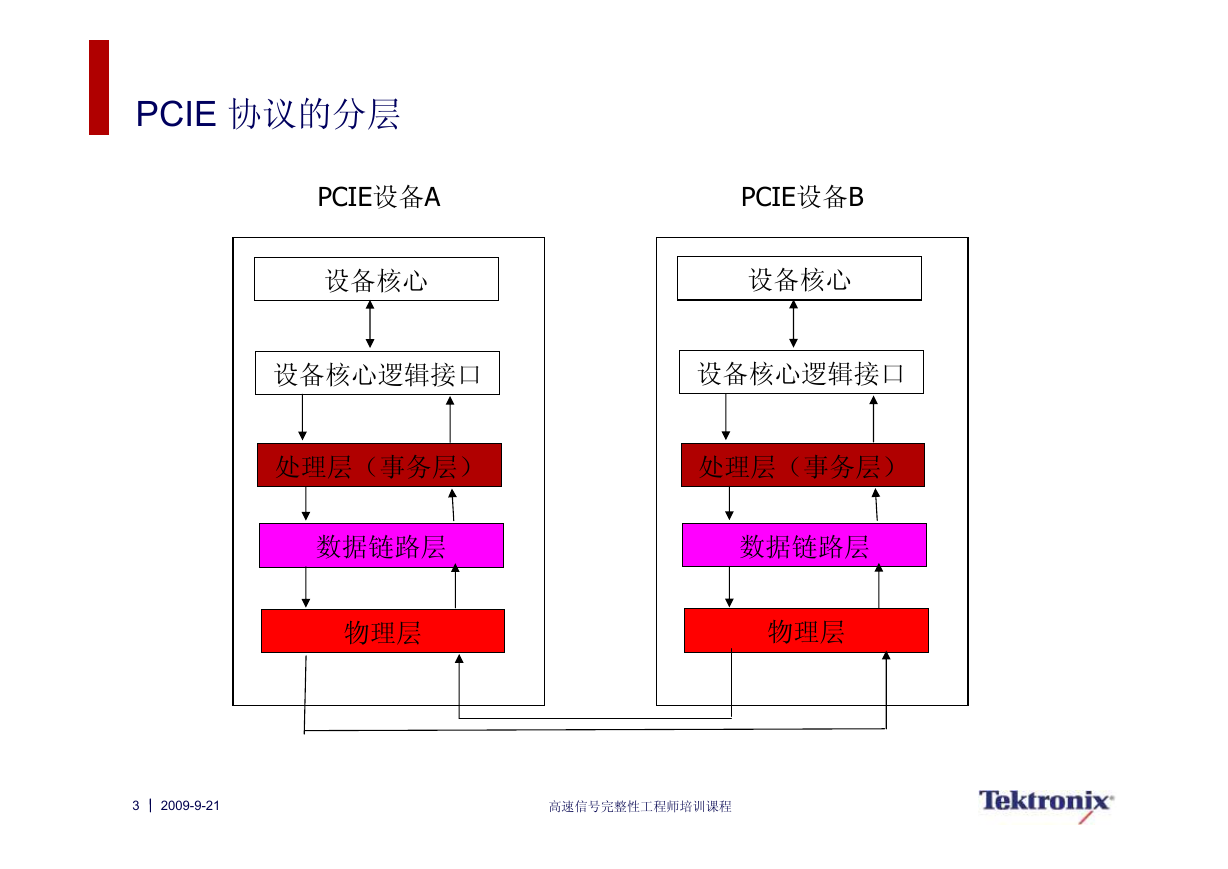

PCIE 协议的分层

PCIE设备A

设备核心

PCIE设备B

设备核心

设备核心逻辑接口

设备核心逻辑接口

处理层(事务层)

处理层(事务层)

数据链路层

数据链路层

物理层

物理层

3

2009-9-21

高速信号完整性工程师培训课程

�

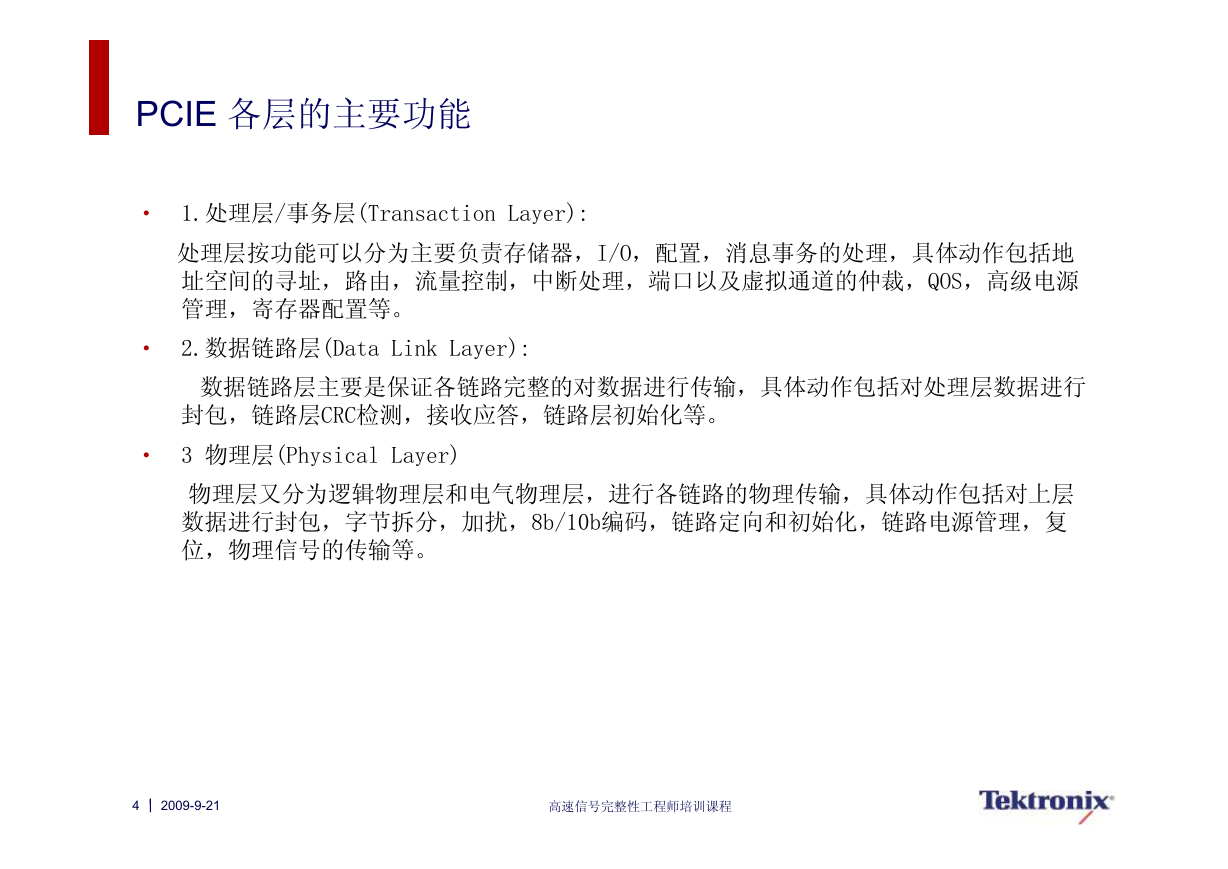

PCIE 各层的主要功能

•

1.处理层/事务层(Transaction Layer):

处理层按功能可以分为主要负责存储器,I/O,配置,消息事务的处理,具体动作包括地

址空间的寻址,路由,流量控制,中断处理,端口以及虚拟通道的仲裁,QOS,高级电源

管理,寄存器配置等。

•

2.数据链路层(Data Link Layer):

数据链路层主要是保证各链路完整的对数据进行传输,具体动作包括对处理层数据进行

封包,链路层CRC检测,接收应答,链路层初始化等。

•

3 物理层(Physical Layer)

物理层又分为逻辑物理层和电气物理层,进行各链路的物理传输,具体动作包括对上层

数据进行封包,字节拆分,加扰,8b/10b编码,链路定向和初始化,链路电源管理,复

位,物理信号的传输等。

4

2009-9-21

高速信号完整性工程师培训课程

�

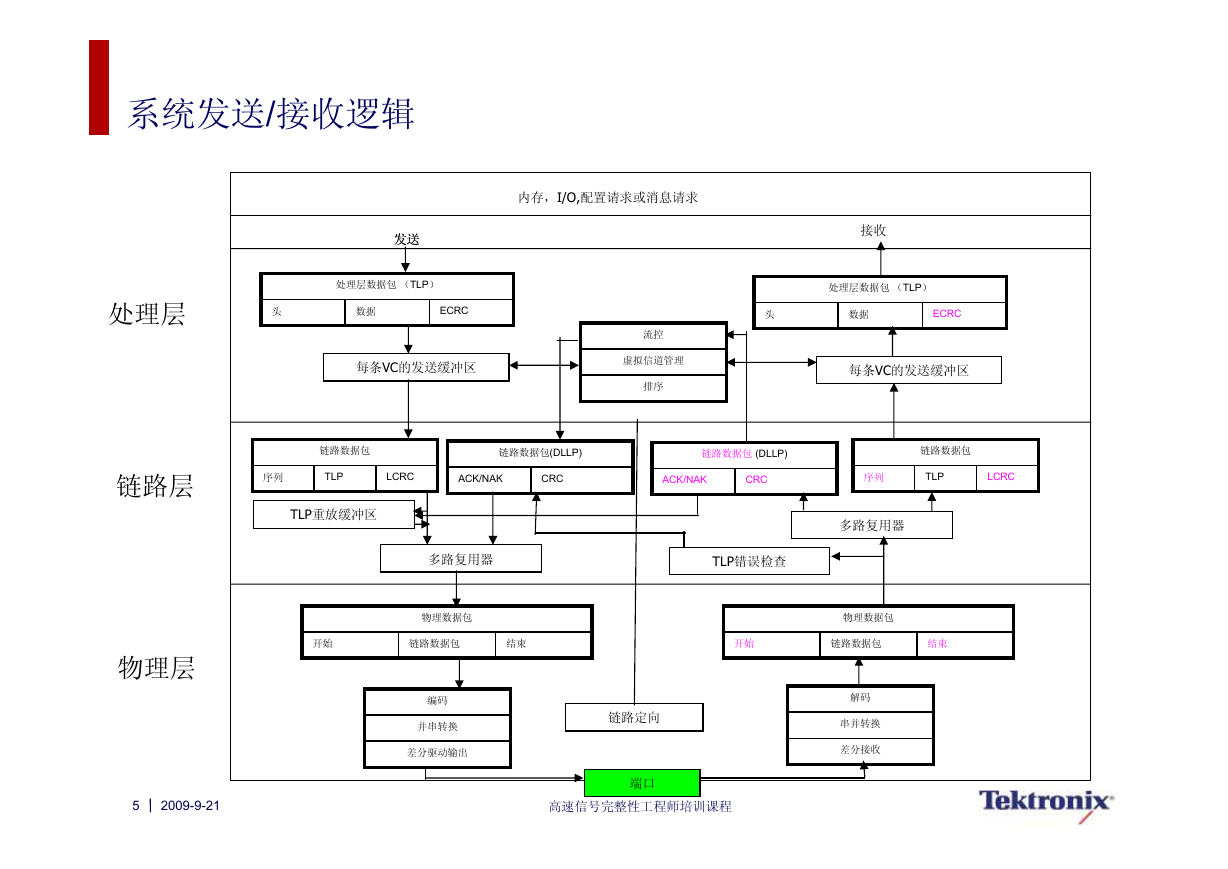

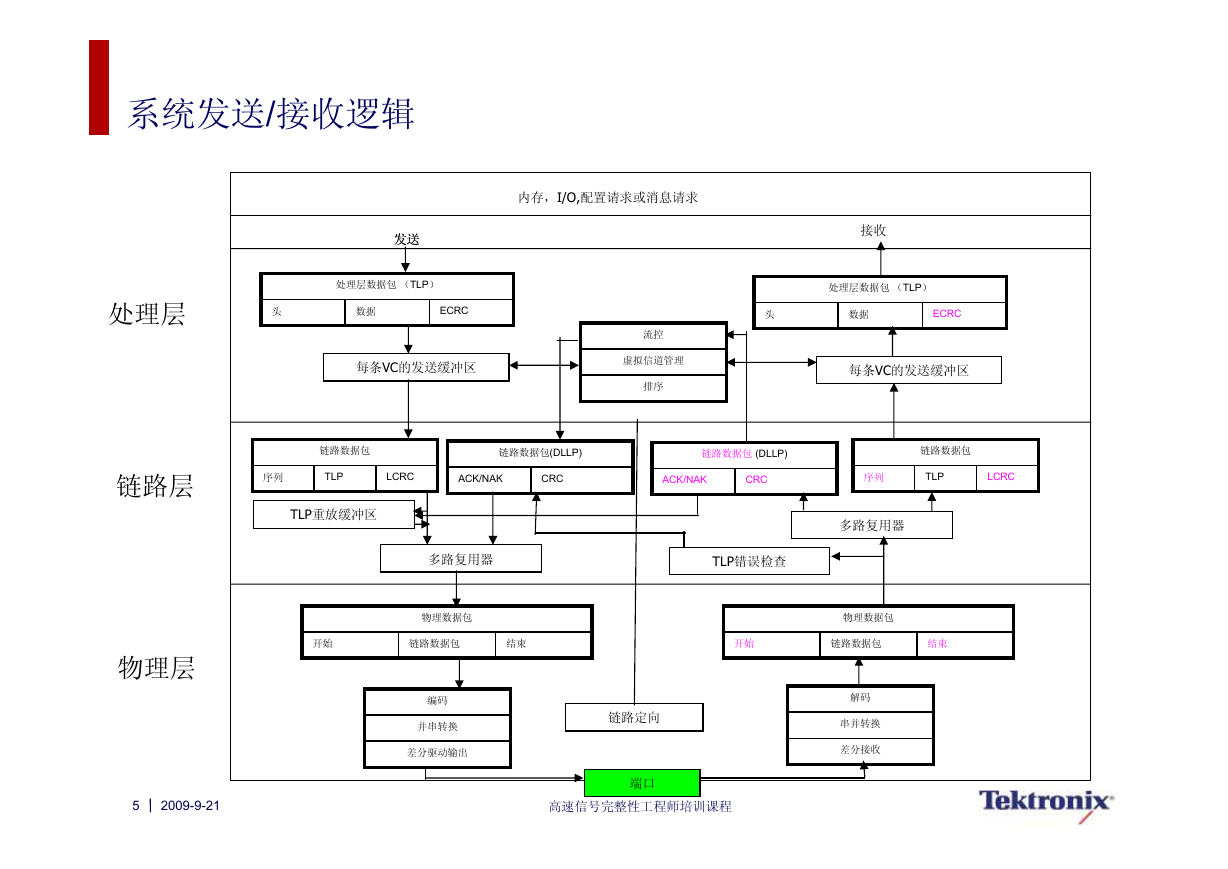

系统发送/接收逻辑

内存,I/O,配置请求或消息请求

发送发送

接收

处理层

处理层数据包 (TLP)

头

数据

ECRC

每条VC的发送缓冲区

流控

虚拟信道管理

排序

处理层数据包 (TLP)

头

数据

ECRC

每条VC的发送缓冲区

链路数据包

链路数据包(DLLP)

链路数据包 (DLLP)

链路数据包

序列

TLP

LCRC

ACK/NAK

CRC

ACK/NAK

CRC

序列

TLP

LCRC

TLP重放缓冲区

多路复用器

物理数据包

TLP错误检查

多路复用器

物理数据包

开始

链路数据包

结束

开始

链路数据包

结束

链路层

物理层

编码

并串转换

差分驱动输出

链路定向

端口

解码

串并转换

差分接收

5

2009-9-21

高速信号完整性工程师培训课程

�

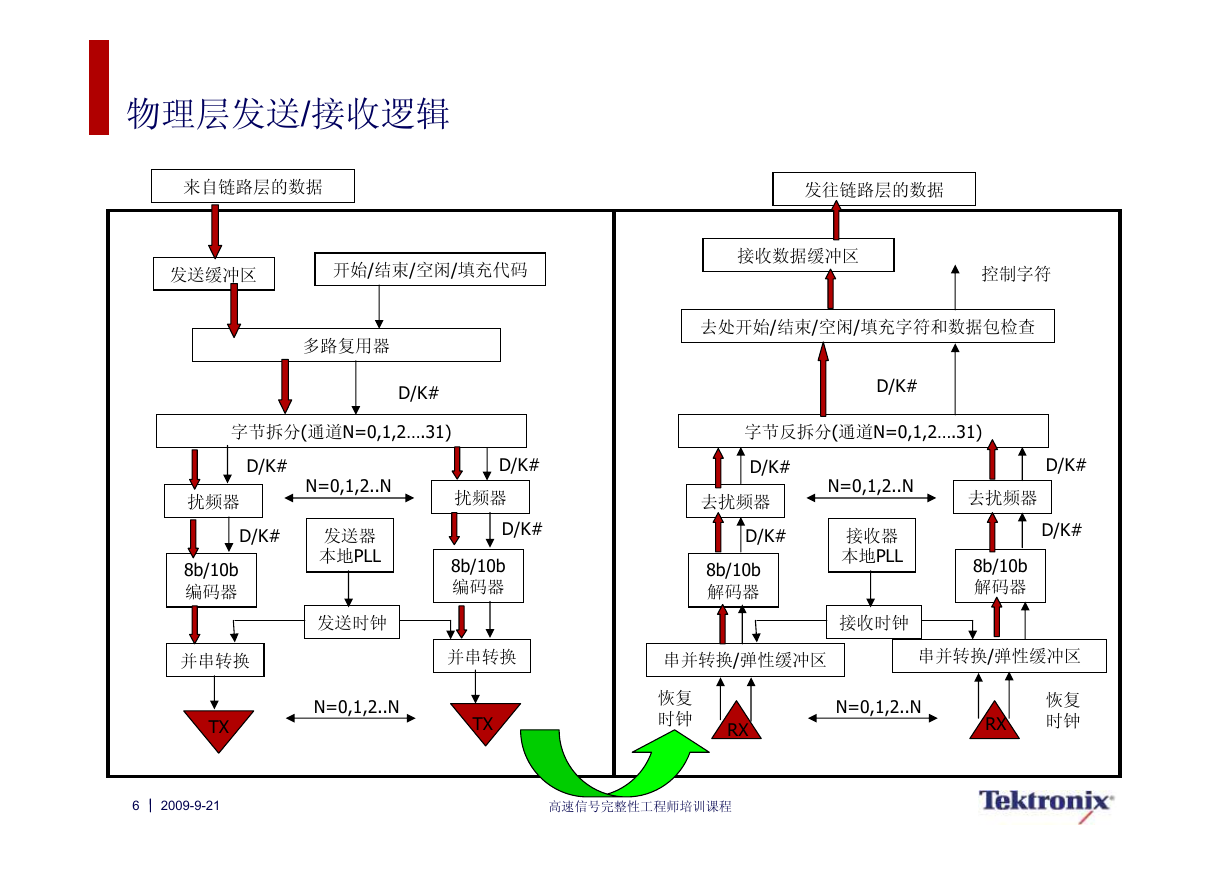

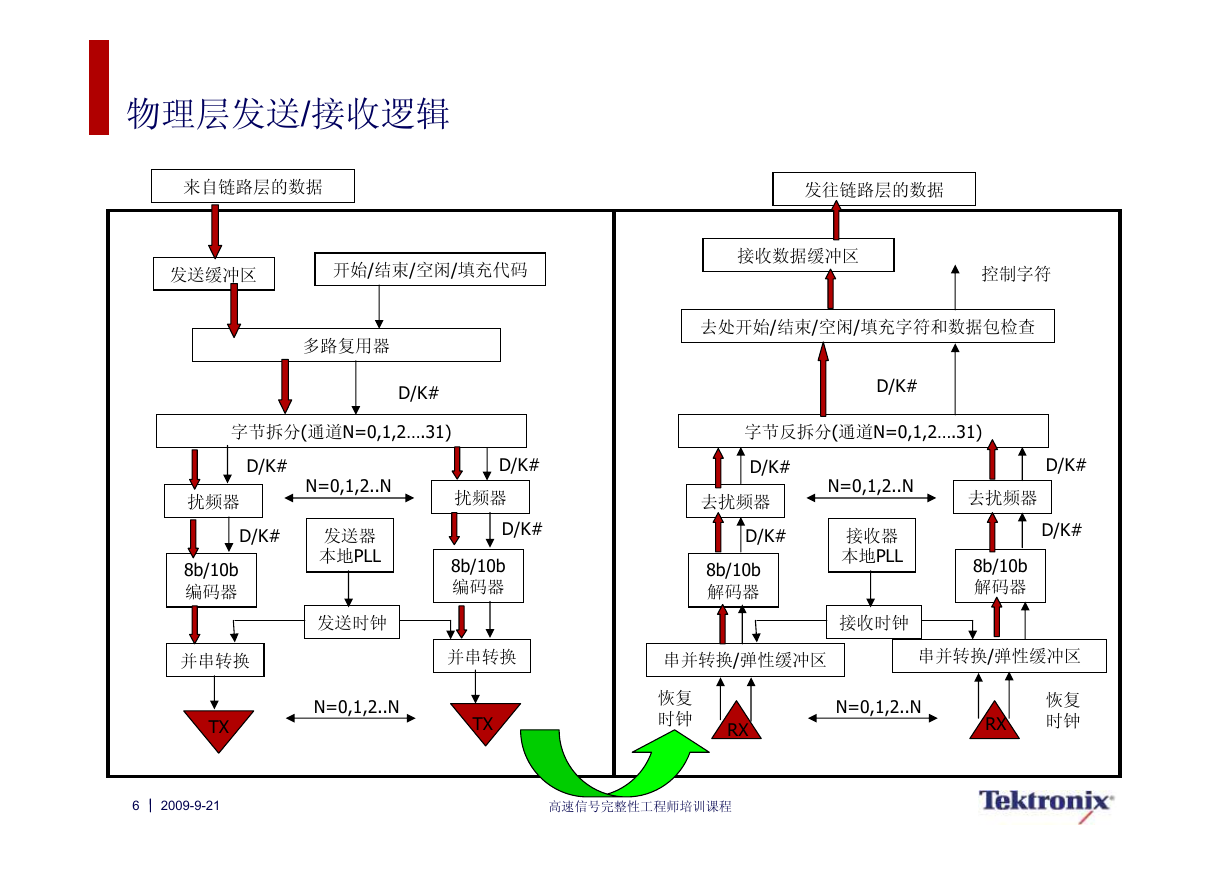

物理层发送/接收逻辑

来自链路层的数据

发往链路层的数据

发送缓冲区

开始/结束/空闲/填充代码

接收数据缓冲区

控制字符

多路复用器

D/K#

去处开始/结束/空闲/填充字符和数据包检查

D/K#

字节拆分(通道N=0,1,2….31)

字节反拆分(通道N=0,1,2….31)

D/K#

N=0,1,2..N

扰频器

D/K#

发送器

本地PLL

8b/10b

编码器

发送时钟

D/K#

扰频器

D/K#

8b/10b

编码器

D/K#

去扰频器

D/K#

8b/10b

解码器

N=0,1,2..N

接收器

本地PLL

接收时钟

D/K#

D/K#

去扰频器

8b/10b

解码器

并串转换

TX

并串转换

串并转换/弹性缓冲区

串并转换/弹性缓冲区

N=0,1,2..N

TX

恢复

时钟

RX

N=0,1,2..N

恢复

时钟

RX

6

2009-9-21

高速信号完整性工程师培训课程

�

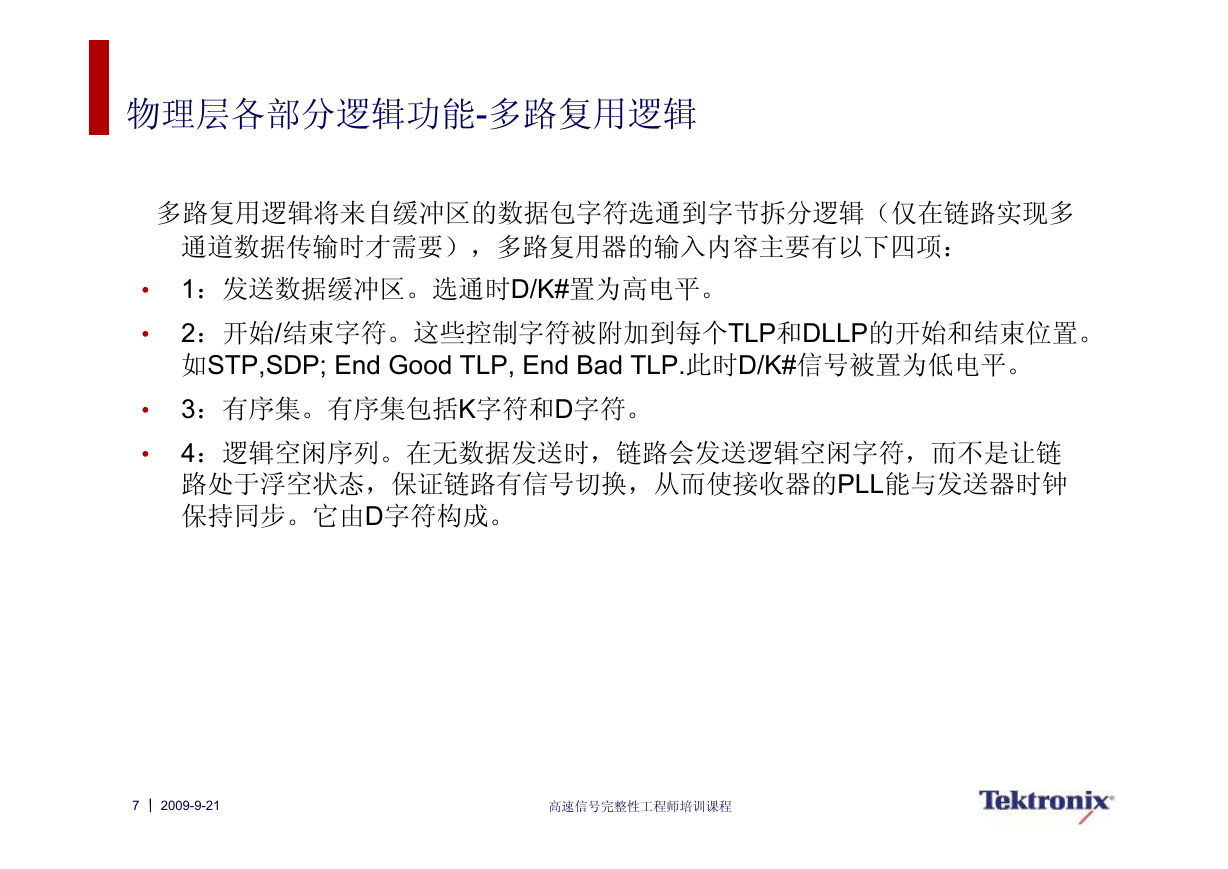

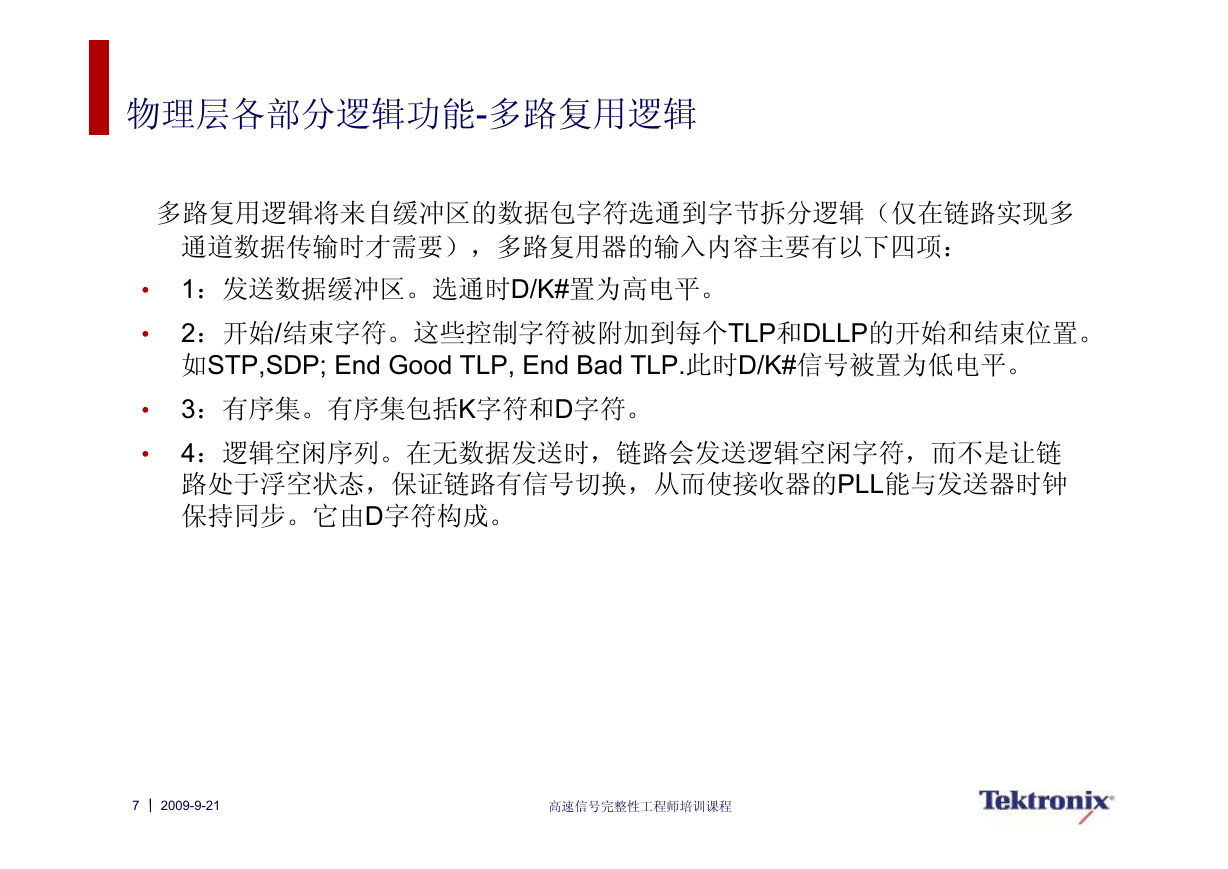

物理层各部分逻辑功能-多路复用逻辑

多路复用逻辑将来自缓冲区的数据包字符选通到字节拆分逻辑(仅在链路实现多

•

•

•

•

通道数据传输时才需要),多路复用器的输入内容主要有以下四项:

1:发送数据缓冲区。选通时D/K#置为高电平。

2:开始/结束字符。这些控制字符被附加到每个TLP和DLLP的开始和结束位置。

如STP,SDP; End Good TLP, End Bad TLP.此时D/K#信号被置为低电平。

3:有序集。有序集包括K字符和D字符。

4:逻辑空闲序列。在无数据发送时,链路会发送逻辑空闲字符,而不是让链

路处于浮空状态,保证链路有信号切换,从而使接收器的PLL能与发送器时钟

保持同步。它由D字符构成。

7

2009-9-21

高速信号完整性工程师培训课程

�

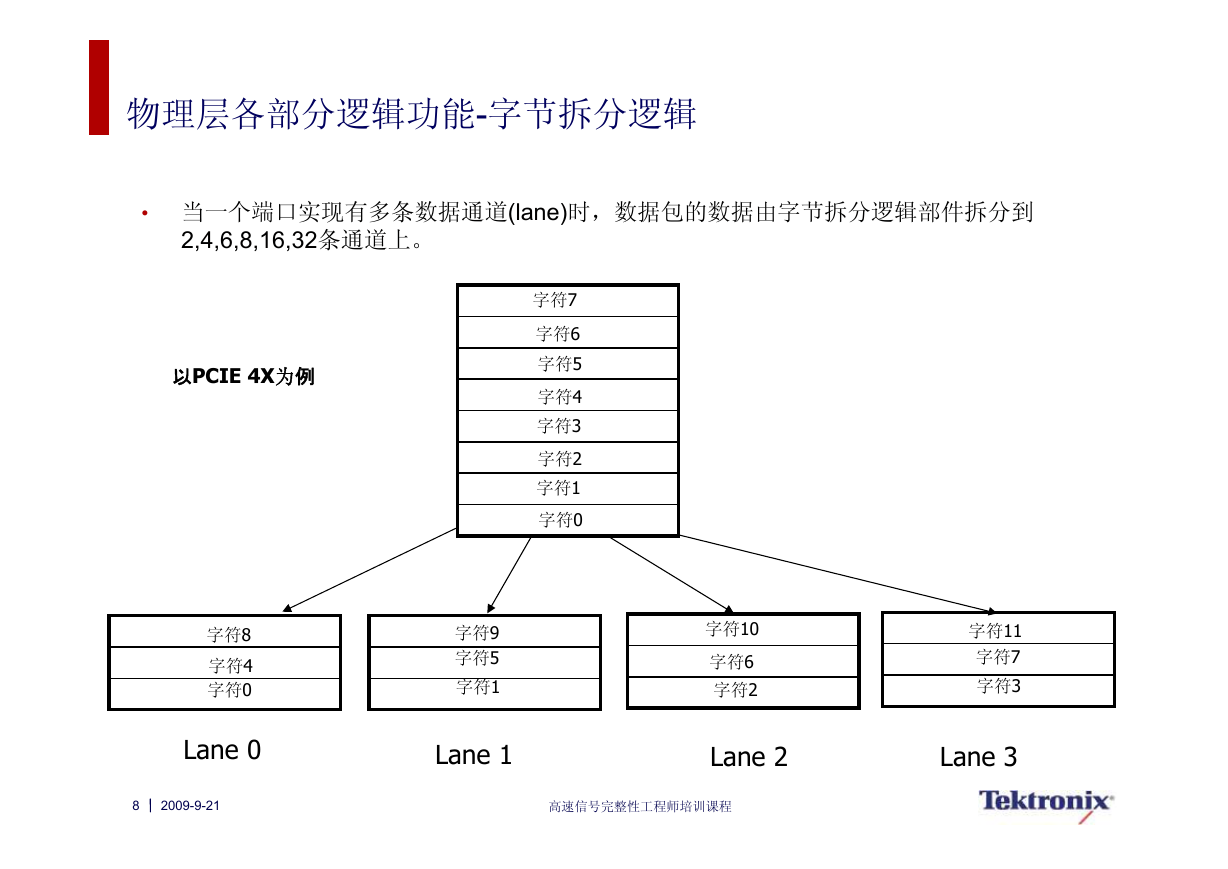

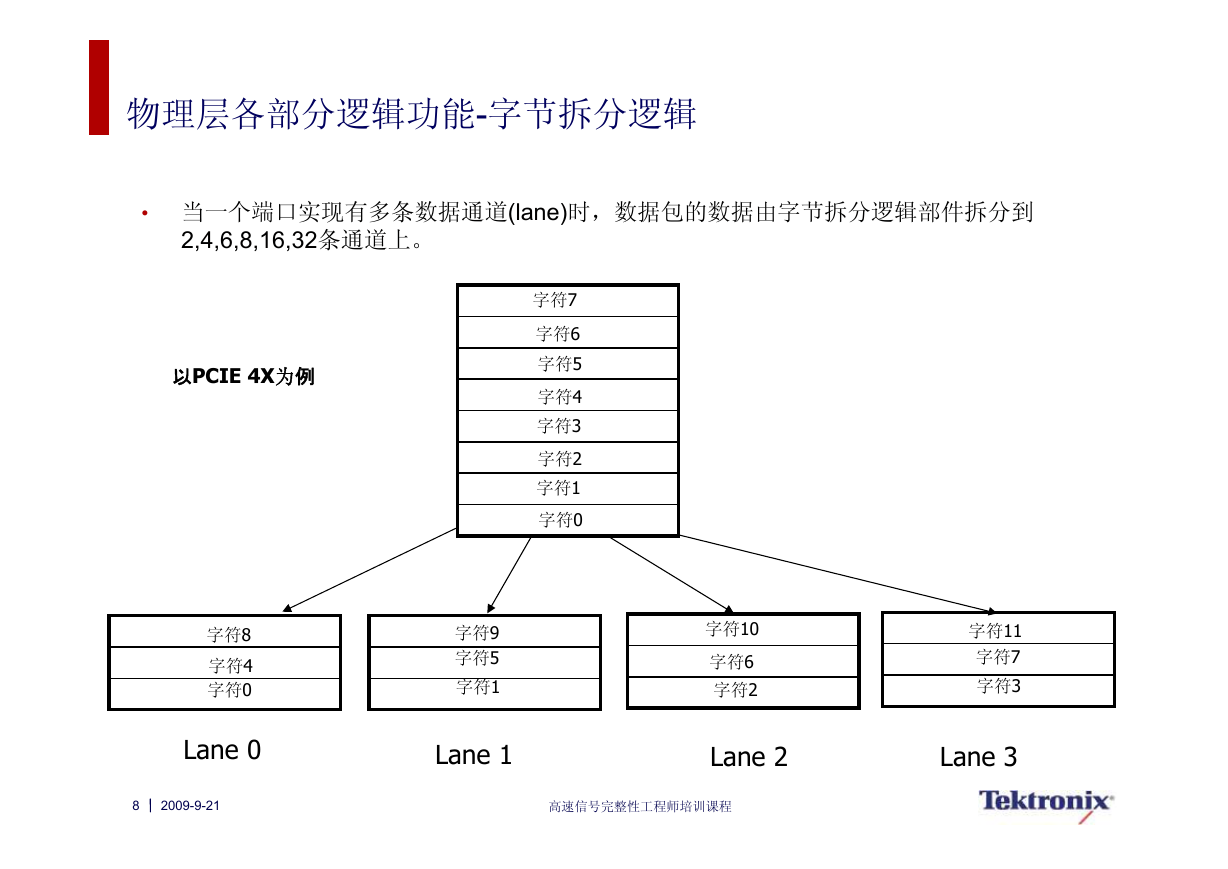

物理层各部分逻辑功能-字节拆分逻辑

• 当一个端口实现有多条数据通道(lane)时,数据包的数据由字节拆分逻辑部件拆分到

2,4,6,8,16,32条通道上。

以PCIE 4X为例

字符7

字符6

字符5

字符4

字符3

字符2

字符1

字符0

字符8

字符4

字符0

Lane 0

字符9

字符5

字符1

Lane 1

字符10

字符6

字符2

字符11

字符7

字符3

Lane 2

Lane 3

8

2009-9-21

高速信号完整性工程师培训课程

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc