6/8/12

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

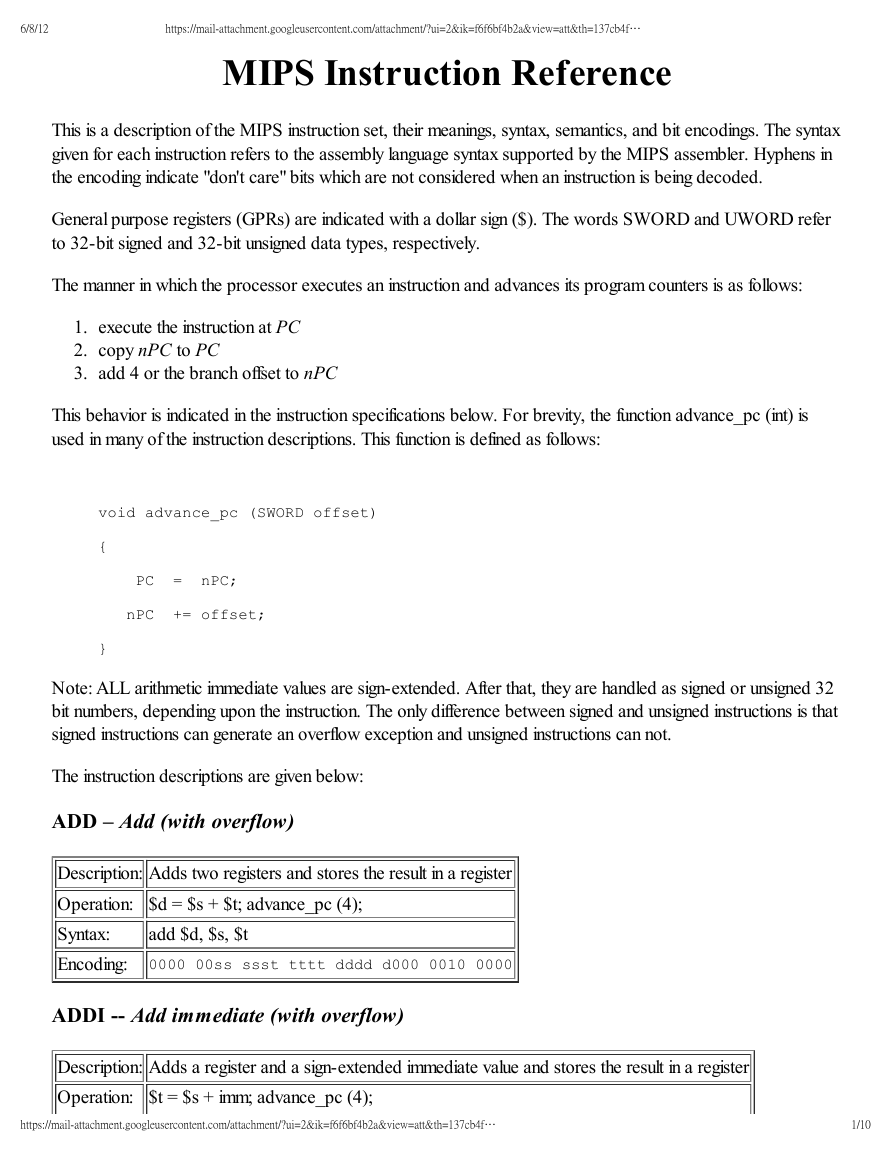

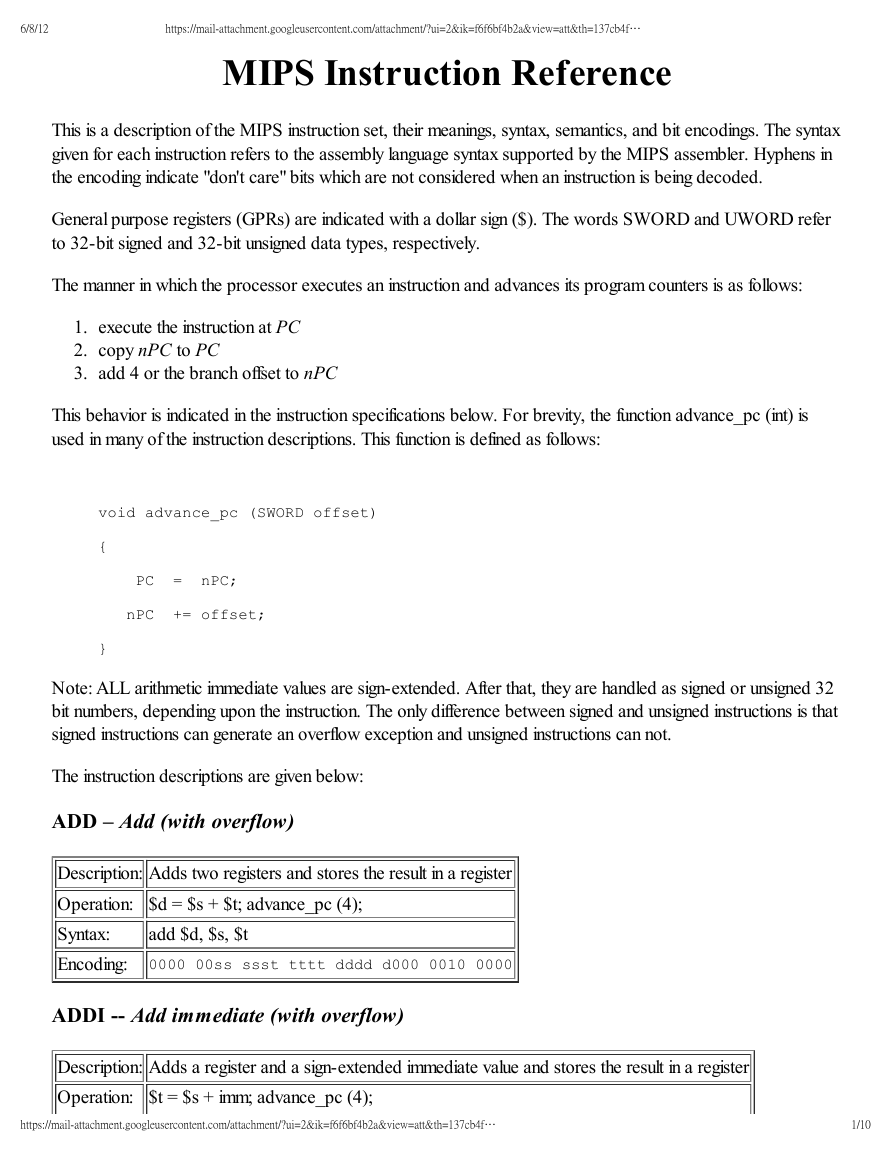

MIPS Instruction Reference

This is a description of the MIPS instruction set, their meanings, syntax, semantics, and bit encodings. The syntax

given for each instruction refers to the assembly language syntax supported by the MIPS assembler. Hyphens in

the encoding indicate "don't care" bits which are not considered when an instruction is being decoded.

General purpose registers (GPRs) are indicated with a dollar sign ($). The words SWORD and UWORD refer

to 32-bit signed and 32-bit unsigned data types, respectively.

The manner in which the processor executes an instruction and advances its program counters is as follows:

1. execute the instruction at PC

2. copy nPC to PC

3. add 4 or the branch offset to nPC

This behavior is indicated in the instruction specifications below. For brevity, the function advance_pc (int) is

used in many of the instruction descriptions. This function is defined as follows:

void advance_pc (SWORD offset)

{

PC = nPC;

nPC += offset;

}

Note: ALL arithmetic immediate values are sign-extended. After that, they are handled as signed or unsigned 32

bit numbers, depending upon the instruction. The only difference between signed and unsigned instructions is that

signed instructions can generate an overflow exception and unsigned instructions can not.

The instruction descriptions are given below:

ADD – Add (with overflow)

Description: Adds two registers and stores the result in a register

Operation: $d = $s + $t; advance_pc (4);

Syntax:

Encoding: 0000 00ss ssst tttt dddd d000 0010 0000

add $d, $s, $t

ADDI -- Add immediate (with overflow)

Description: Adds a register and a sign-extended immediate value and stores the result in a register

Operation: $t = $s + imm; advance_pc (4);

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

1/10

�

6/8/12

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

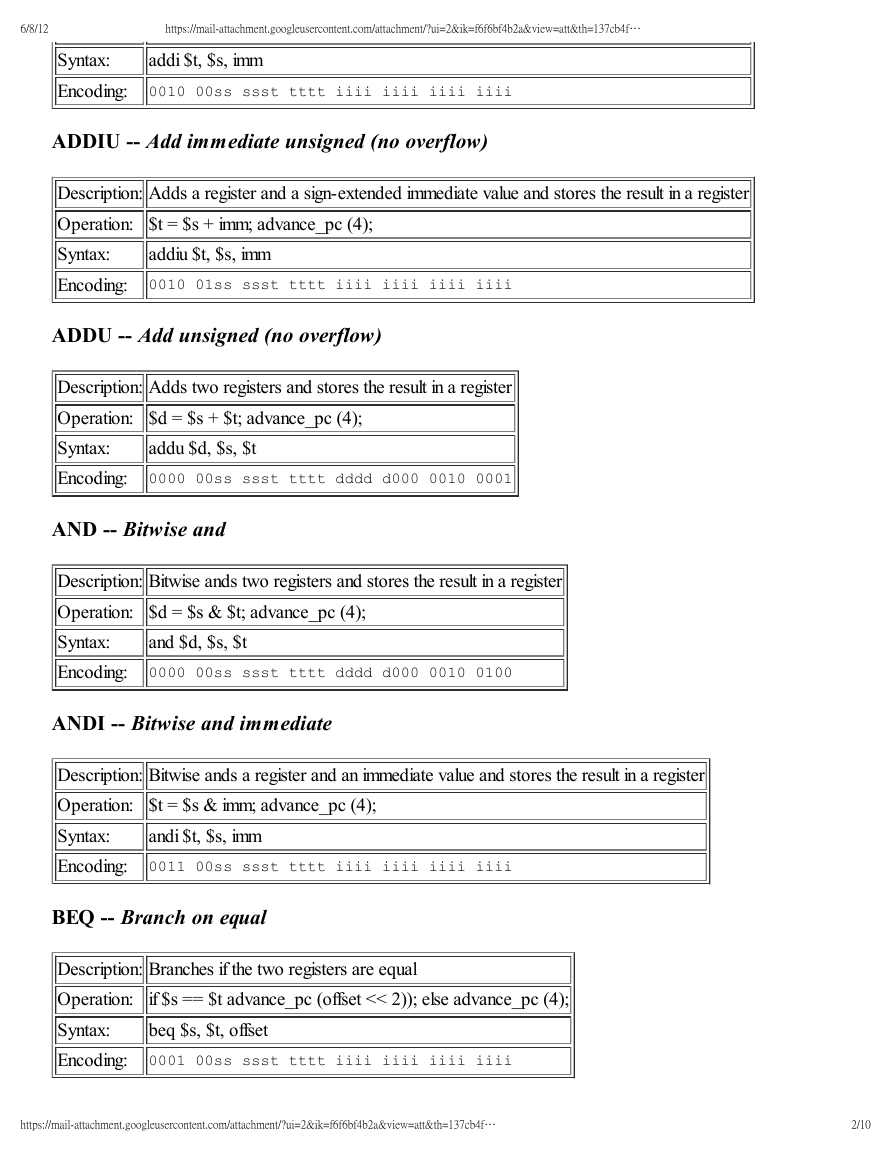

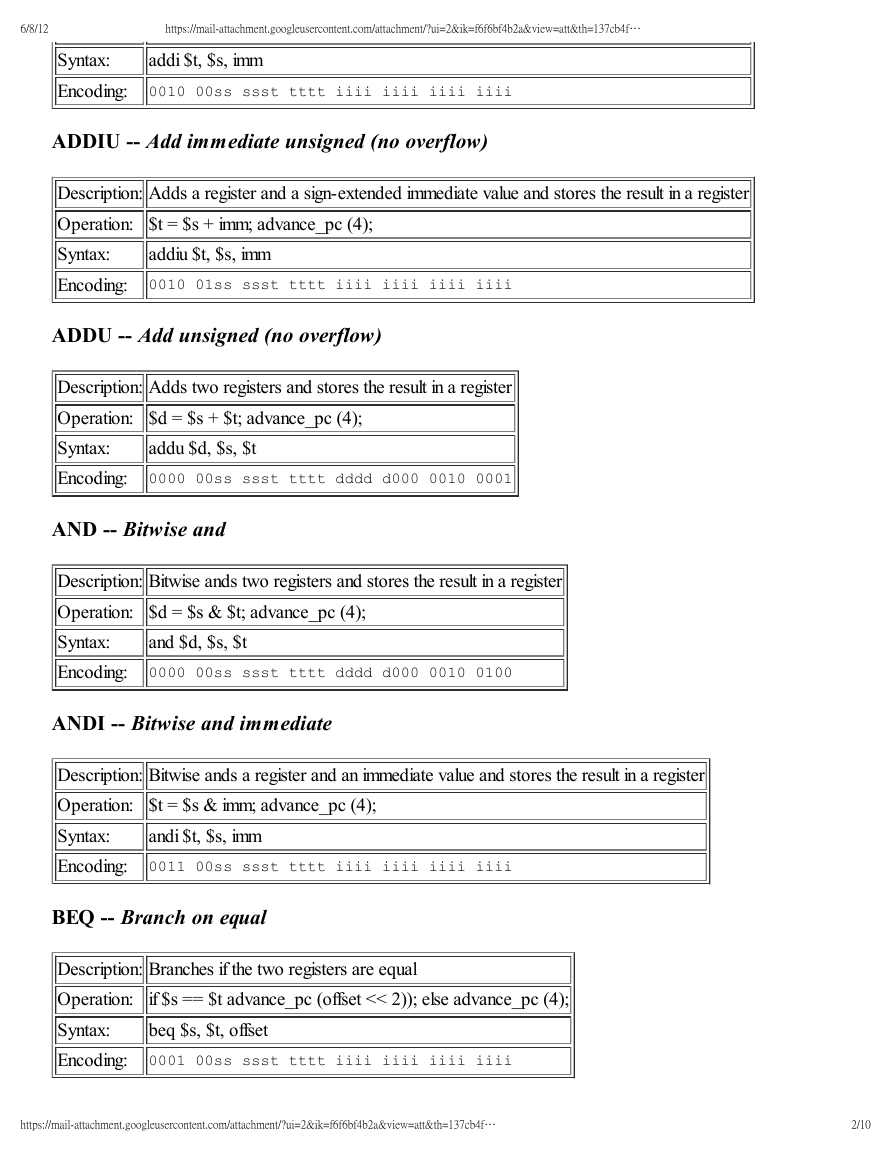

Syntax:

Encoding: 0010 00ss ssst tttt iiii iiii iiii iiii

addi $t, $s, imm

ADDIU -- Add immediate unsigned (no overflow)

Description: Adds a register and a sign-extended immediate value and stores the result in a register

Operation: $t = $s + imm; advance_pc (4);

Syntax:

Encoding: 0010 01ss ssst tttt iiii iiii iiii iiii

addiu $t, $s, imm

ADDU -- Add unsigned (no overflow)

Description: Adds two registers and stores the result in a register

Operation: $d = $s + $t; advance_pc (4);

Syntax:

Encoding: 0000 00ss ssst tttt dddd d000 0010 0001

addu $d, $s, $t

AND -- Bitwise and

Description: Bitwise ands two registers and stores the result in a register

Operation: $d = $s & $t; advance_pc (4);

Syntax:

Encoding: 0000 00ss ssst tttt dddd d000 0010 0100

and $d, $s, $t

ANDI -- Bitwise and immediate

Description: Bitwise ands a register and an immediate value and stores the result in a register

Operation: $t = $s & imm; advance_pc (4);

Syntax:

Encoding: 0011 00ss ssst tttt iiii iiii iiii iiii

andi $t, $s, imm

BEQ -- Branch on equal

Description: Branches if the two registers are equal

Operation:

Syntax:

Encoding: 0001 00ss ssst tttt iiii iiii iiii iiii

if $s == $t advance_pc (offset << 2)); else advance_pc (4);

beq $s, $t, offset

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

2/10

�

6/8/12

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

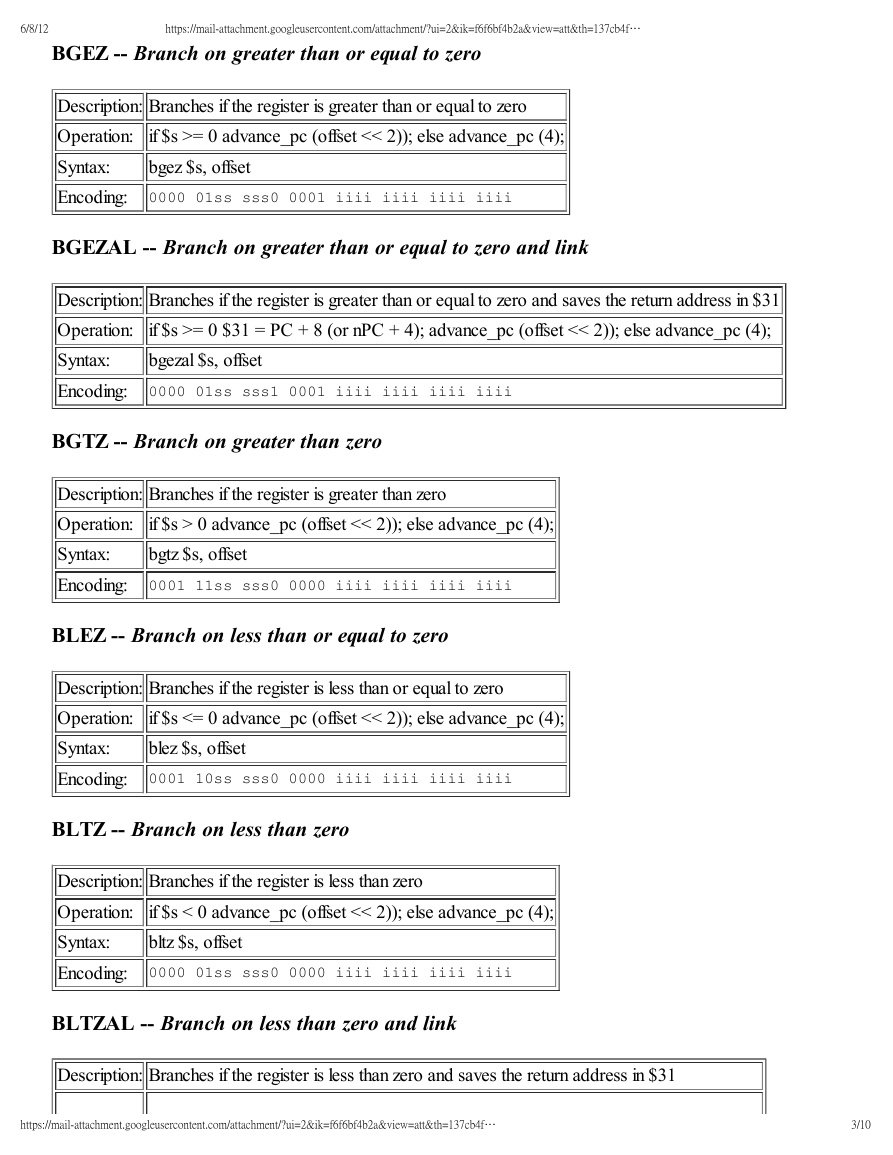

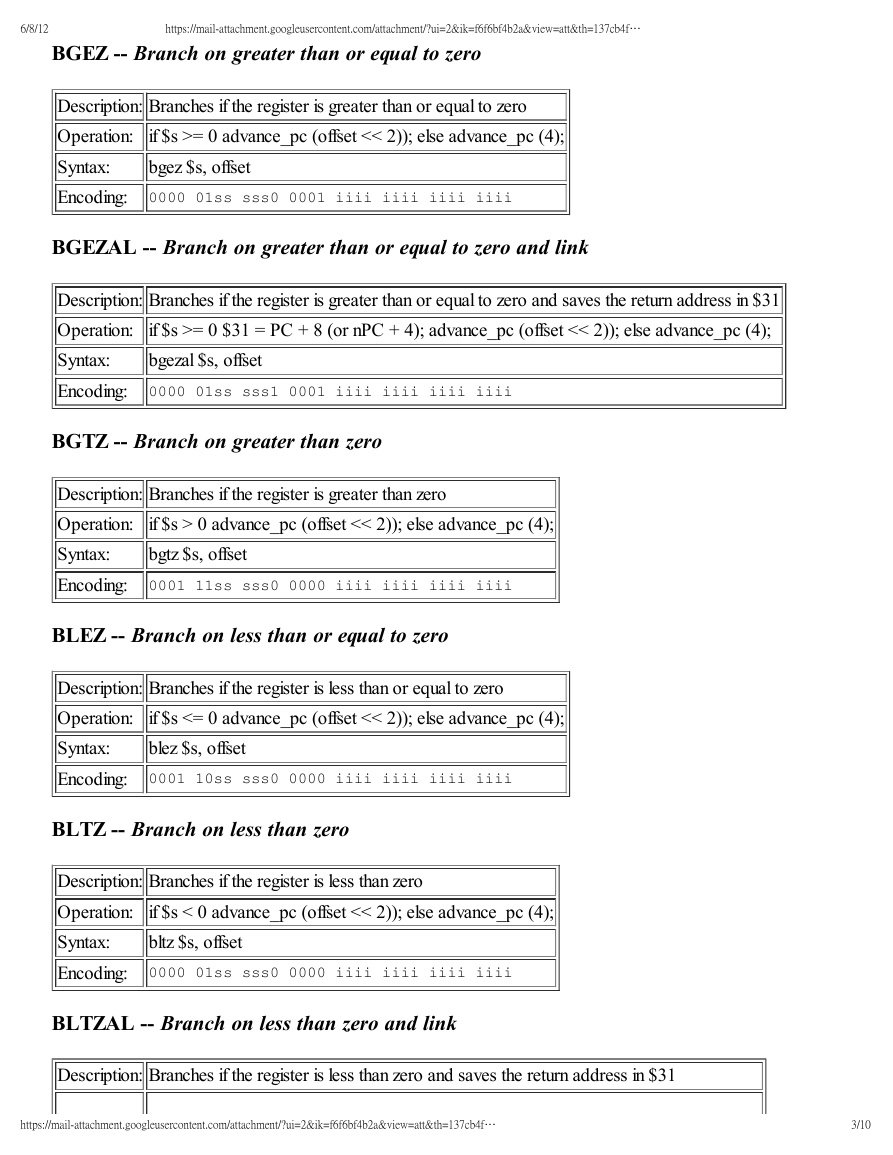

BGEZ -- Branch on greater than or equal to zero

Description: Branches if the register is greater than or equal to zero

Operation:

Syntax:

Encoding: 0000 01ss sss0 0001 iiii iiii iiii iiii

if $s >= 0 advance_pc (offset << 2)); else advance_pc (4);

bgez $s, offset

BGEZAL -- Branch on greater than or equal to zero and link

Description: Branches if the register is greater than or equal to zero and saves the return address in $31

Operation:

if $s >= 0 $31 = PC + 8 (or nPC + 4); advance_pc (offset << 2)); else advance_pc (4);

Syntax:

bgezal $s, offset

Encoding: 0000 01ss sss1 0001 iiii iiii iiii iiii

BGTZ -- Branch on greater than zero

Description: Branches if the register is greater than zero

Operation:

Syntax:

Encoding: 0001 11ss sss0 0000 iiii iiii iiii iiii

if $s > 0 advance_pc (offset << 2)); else advance_pc (4);

bgtz $s, offset

BLEZ -- Branch on less than or equal to zero

Description: Branches if the register is less than or equal to zero

Operation:

Syntax:

Encoding: 0001 10ss sss0 0000 iiii iiii iiii iiii

if $s <= 0 advance_pc (offset << 2)); else advance_pc (4);

blez $s, offset

BLTZ -- Branch on less than zero

Description: Branches if the register is less than zero

Operation:

Syntax:

Encoding: 0000 01ss sss0 0000 iiii iiii iiii iiii

if $s < 0 advance_pc (offset << 2)); else advance_pc (4);

bltz $s, offset

BLTZAL -- Branch on less than zero and link

Description: Branches if the register is less than zero and saves the return address in $31

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

3/10

�

6/8/12

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

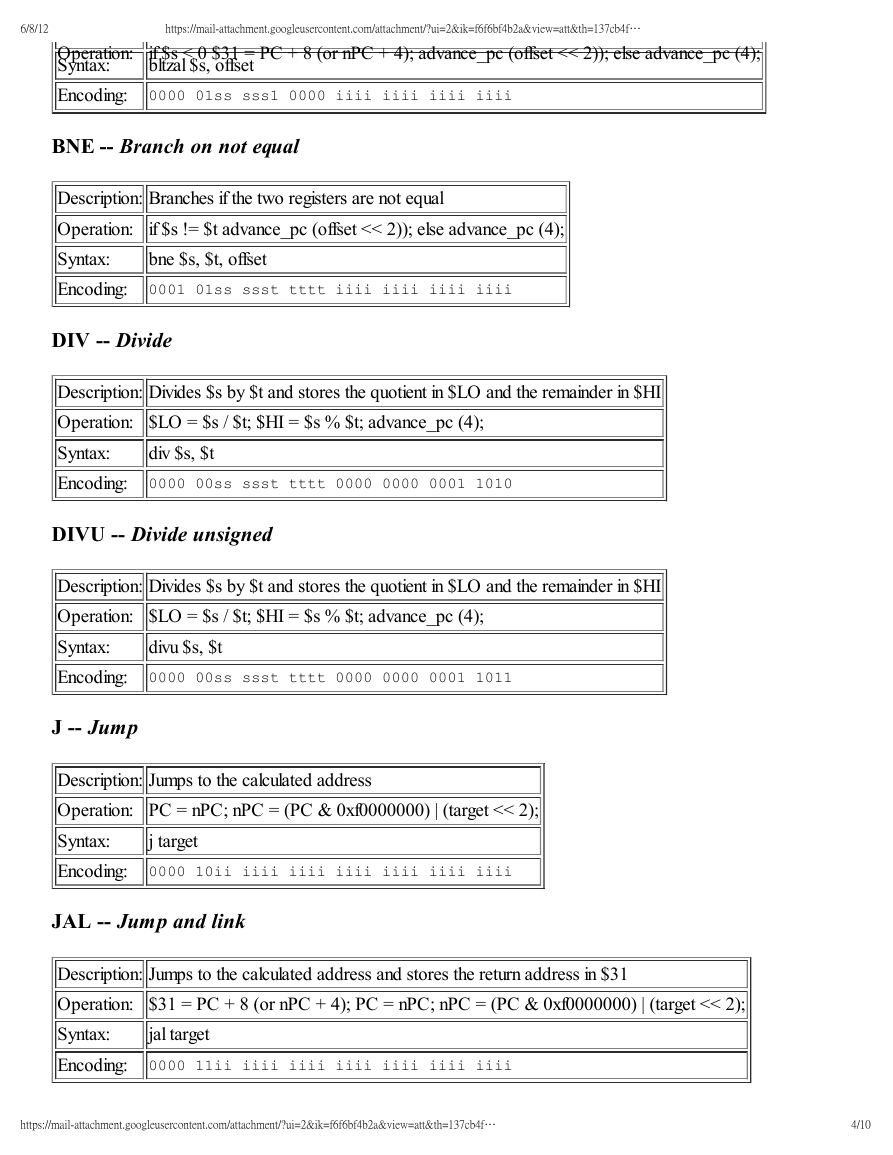

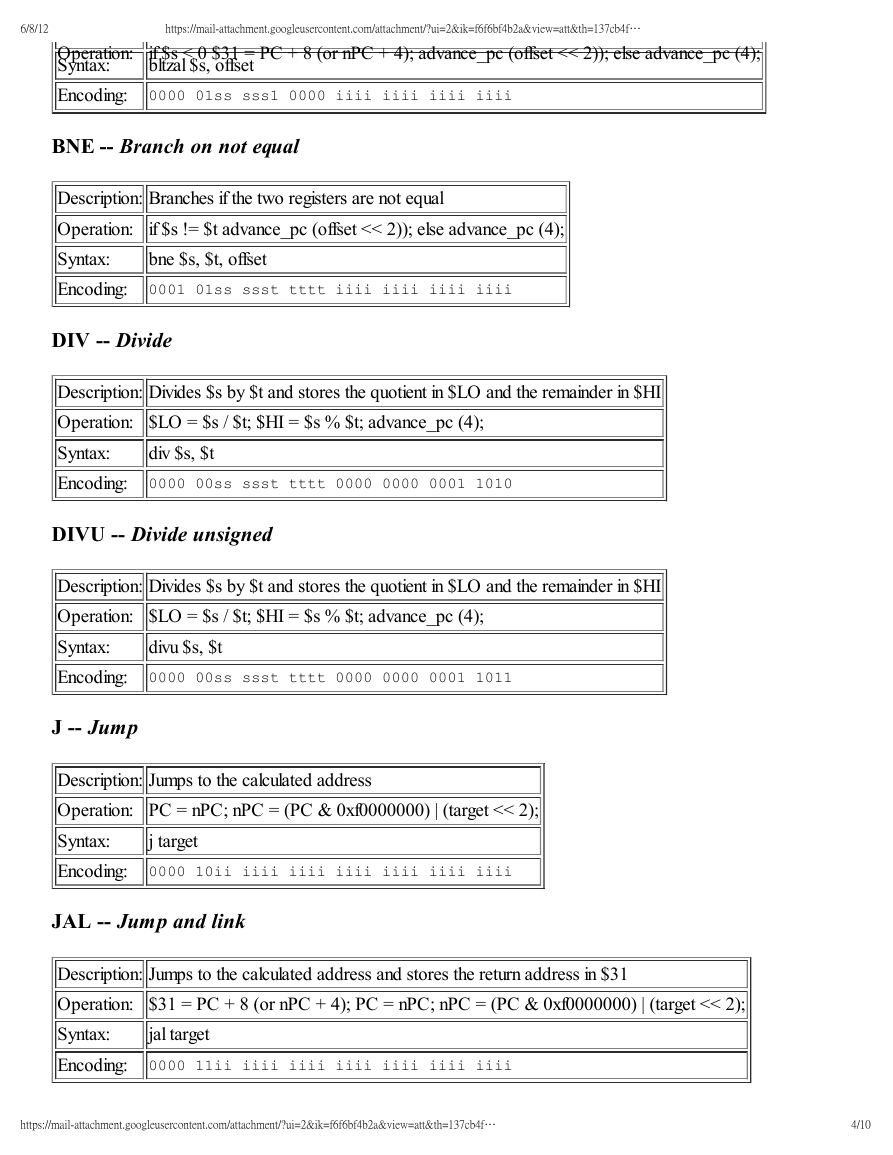

Operation:

Syntax:

Encoding: 0000 01ss sss1 0000 iiii iiii iiii iiii

if $s < 0 $31 = PC + 8 (or nPC + 4); advance_pc (offset << 2)); else advance_pc (4);

bltzal $s, offset

BNE -- Branch on not equal

Description: Branches if the two registers are not equal

Operation:

Syntax:

Encoding: 0001 01ss ssst tttt iiii iiii iiii iiii

if $s != $t advance_pc (offset << 2)); else advance_pc (4);

bne $s, $t, offset

DIV -- Divide

Description: Divides $s by $t and stores the quotient in $LO and the remainder in $HI

Operation: $LO = $s / $t; $HI = $s % $t; advance_pc (4);

Syntax:

Encoding: 0000 00ss ssst tttt 0000 0000 0001 1010

div $s, $t

DIVU -- Divide unsigned

Description: Divides $s by $t and stores the quotient in $LO and the remainder in $HI

Operation: $LO = $s / $t; $HI = $s % $t; advance_pc (4);

Syntax:

Encoding: 0000 00ss ssst tttt 0000 0000 0001 1011

divu $s, $t

J -- Jump

Description: Jumps to the calculated address

Operation: PC = nPC; nPC = (PC & 0xf0000000) | (target << 2);

Syntax:

Encoding: 0000 10ii iiii iiii iiii iiii iiii iiii

j target

JAL -- Jump and link

Description: Jumps to the calculated address and stores the return address in $31

Operation: $31 = PC + 8 (or nPC + 4); PC = nPC; nPC = (PC & 0xf0000000) | (target << 2);

Syntax:

Encoding: 0000 11ii iiii iiii iiii iiii iiii iiii

jal target

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

4/10

�

6/8/12

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

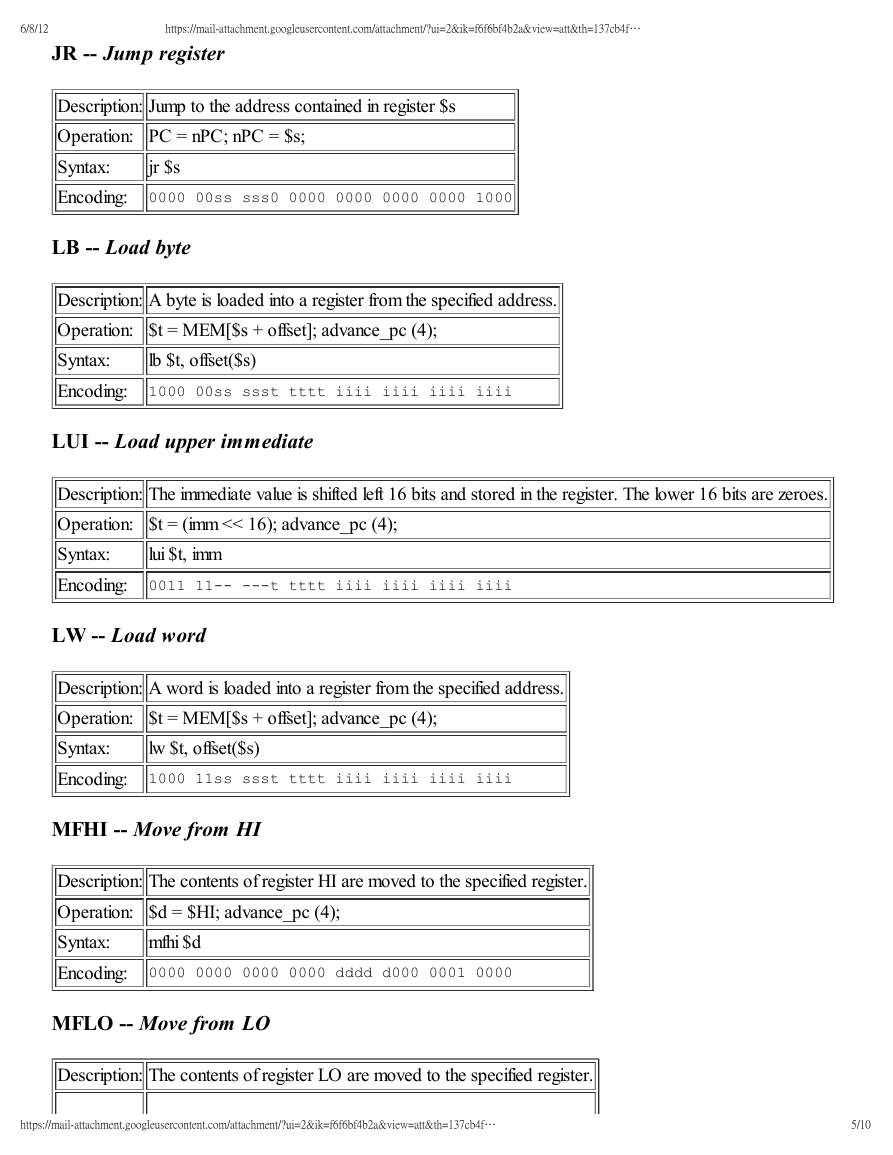

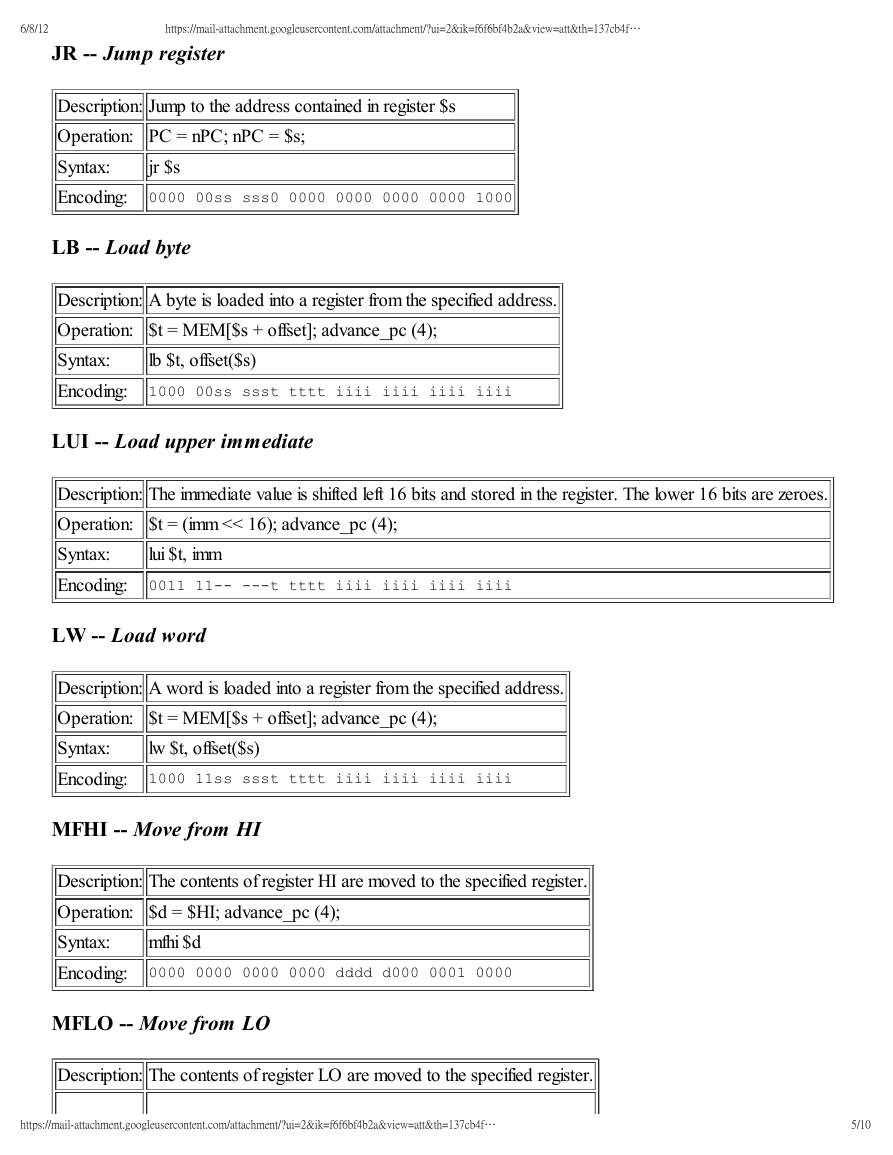

JR -- Jump register

Description: Jump to the address contained in register $s

Operation: PC = nPC; nPC = $s;

Syntax:

Encoding: 0000 00ss sss0 0000 0000 0000 0000 1000

jr $s

LB -- Load byte

Description: A byte is loaded into a register from the specified address.

Operation: $t = MEM[$s + offset]; advance_pc (4);

Syntax:

Encoding: 1000 00ss ssst tttt iiii iiii iiii iiii

lb $t, offset($s)

LUI -- Load upper immediate

Description: The immediate value is shifted left 16 bits and stored in the register. The lower 16 bits are zeroes.

Operation: $t = (imm << 16); advance_pc (4);

Syntax:

Encoding: 0011 11-- ---t tttt iiii iiii iiii iiii

lui $t, imm

LW -- Load word

Description: A word is loaded into a register from the specified address.

Operation: $t = MEM[$s + offset]; advance_pc (4);

Syntax:

Encoding: 1000 11ss ssst tttt iiii iiii iiii iiii

lw $t, offset($s)

MFHI -- Move from HI

Description: The contents of register HI are moved to the specified register.

Operation: $d = $HI; advance_pc (4);

Syntax:

Encoding: 0000 0000 0000 0000 dddd d000 0001 0000

mfhi $d

MFLO -- Move from LO

Description: The contents of register LO are moved to the specified register.

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

5/10

�

6/8/12

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

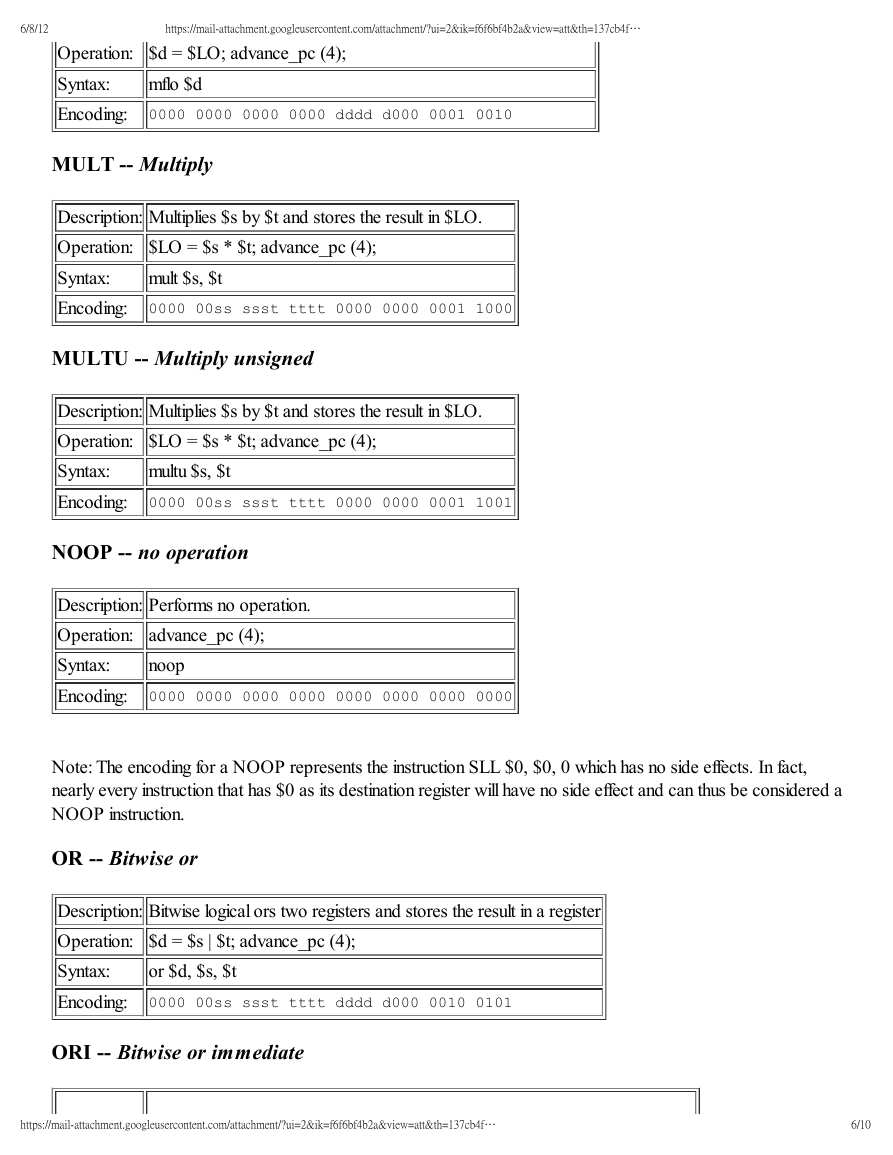

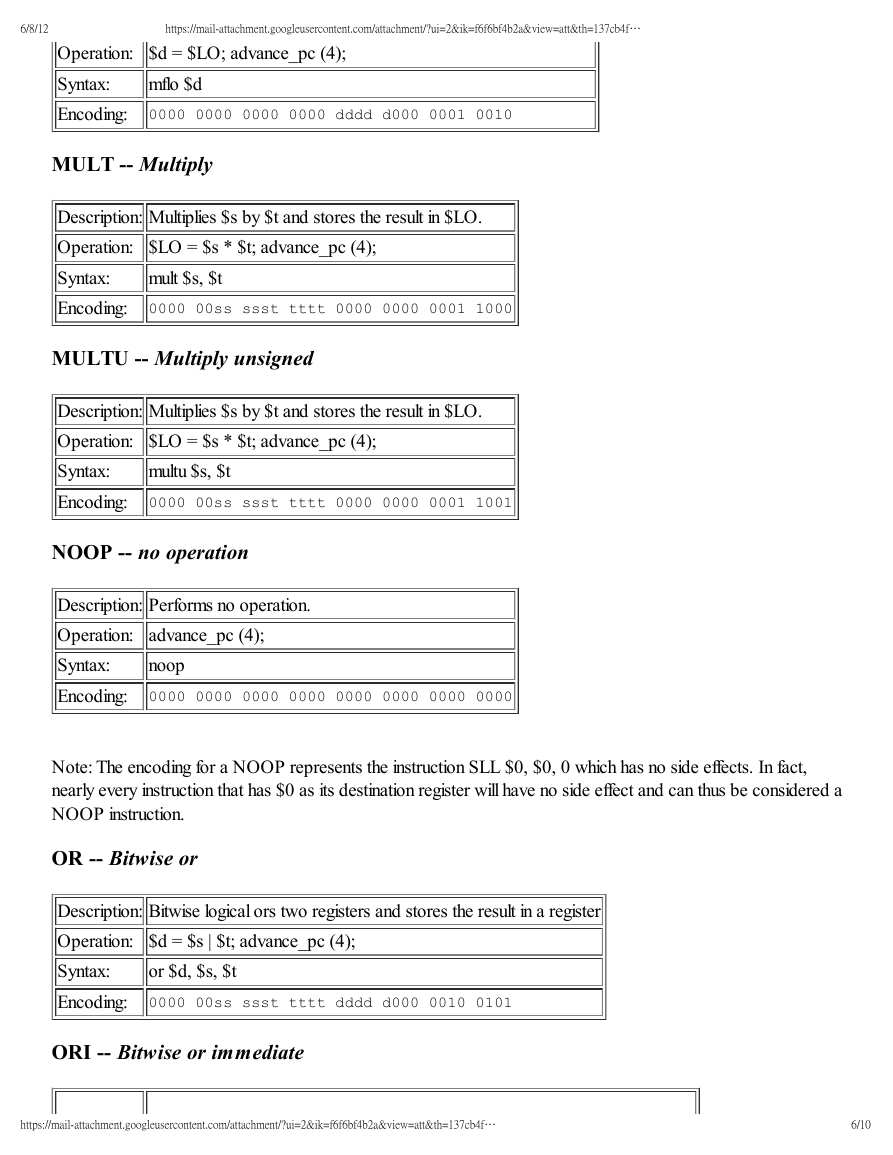

Operation: $d = $LO; advance_pc (4);

Syntax:

Encoding: 0000 0000 0000 0000 dddd d000 0001 0010

mflo $d

MULT -- Multiply

Description: Multiplies $s by $t and stores the result in $LO.

Operation: $LO = $s * $t; advance_pc (4);

Syntax:

Encoding: 0000 00ss ssst tttt 0000 0000 0001 1000

mult $s, $t

MULTU -- Multiply unsigned

Description: Multiplies $s by $t and stores the result in $LO.

Operation: $LO = $s * $t; advance_pc (4);

Syntax:

Encoding: 0000 00ss ssst tttt 0000 0000 0001 1001

multu $s, $t

NOOP -- no operation

Description: Performs no operation.

Operation: advance_pc (4);

Syntax:

Encoding: 0000 0000 0000 0000 0000 0000 0000 0000

noop

Note: The encoding for a NOOP represents the instruction SLL $0, $0, 0 which has no side effects. In fact,

nearly every instruction that has $0 as its destination register will have no side effect and can thus be considered a

NOOP instruction.

OR -- Bitwise or

Description: Bitwise logical ors two registers and stores the result in a register

Operation: $d = $s | $t; advance_pc (4);

Syntax:

Encoding: 0000 00ss ssst tttt dddd d000 0010 0101

or $d, $s, $t

ORI -- Bitwise or immediate

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

6/10

�

6/8/12

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

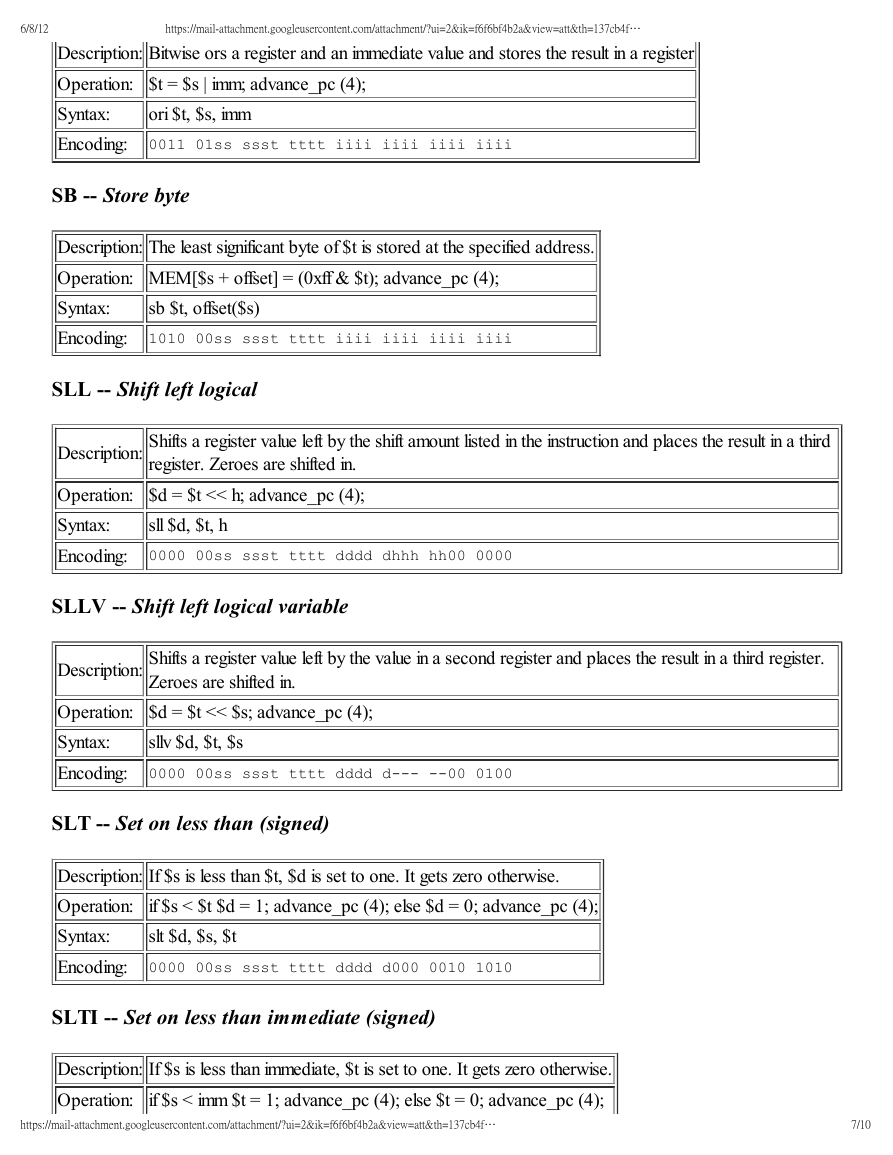

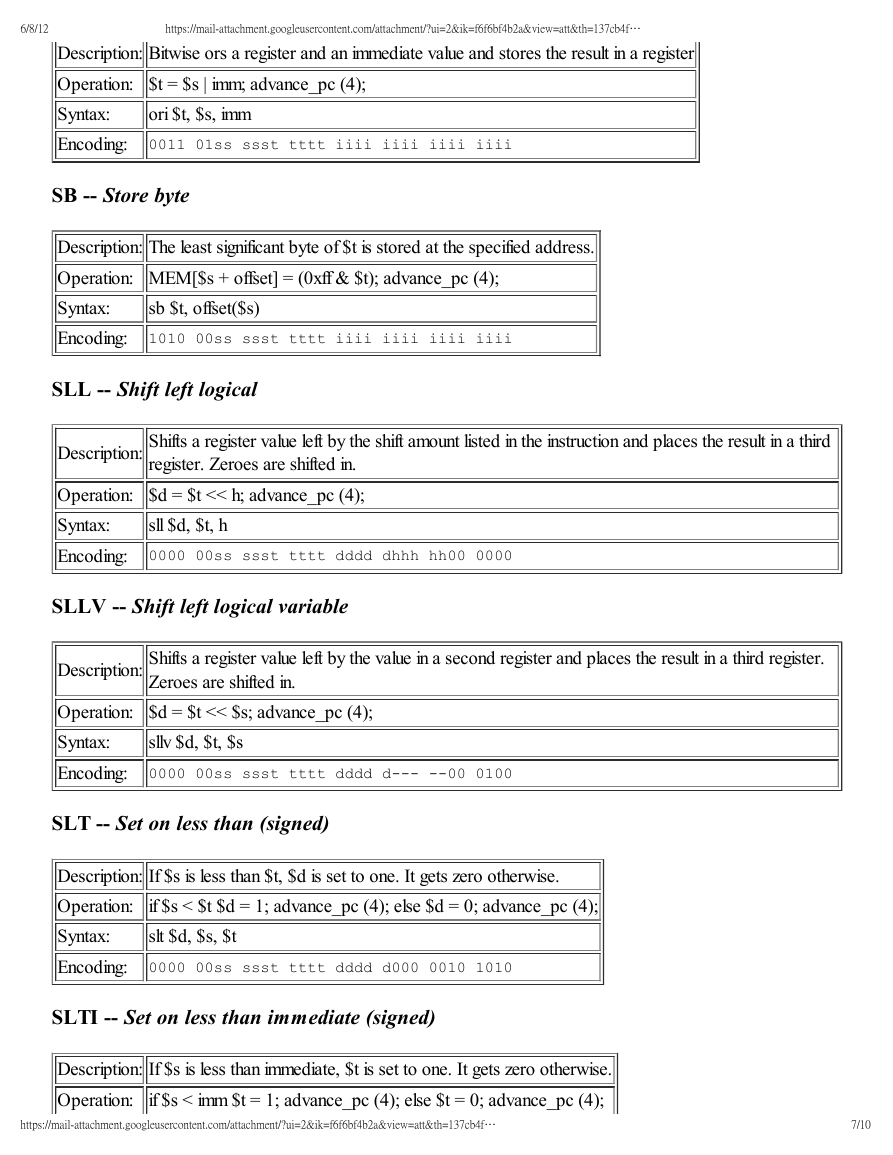

Description: Bitwise ors a register and an immediate value and stores the result in a register

Operation: $t = $s | imm; advance_pc (4);

Syntax:

Encoding: 0011 01ss ssst tttt iiii iiii iiii iiii

ori $t, $s, imm

SB -- Store byte

Description: The least significant byte of $t is stored at the specified address.

Operation: MEM[$s + offset] = (0xff & $t); advance_pc (4);

Syntax:

Encoding: 1010 00ss ssst tttt iiii iiii iiii iiii

sb $t, offset($s)

SLL -- Shift left logical

Description: Shifts a register value left by the shift amount listed in the instruction and places the result in a third

register. Zeroes are shifted in.

Operation: $d = $t << h; advance_pc (4);

Syntax:

Encoding: 0000 00ss ssst tttt dddd dhhh hh00 0000

sll $d, $t, h

SLLV -- Shift left logical variable

Zeroes are shifted in.

Description: Shifts a register value left by the value in a second register and places the result in a third register.

Operation: $d = $t << $s; advance_pc (4);

Syntax:

Encoding: 0000 00ss ssst tttt dddd d--- --00 0100

sllv $d, $t, $s

SLT -- Set on less than (signed)

Description: If $s is less than $t, $d is set to one. It gets zero otherwise.

Operation:

Syntax:

Encoding: 0000 00ss ssst tttt dddd d000 0010 1010

if $s < $t $d = 1; advance_pc (4); else $d = 0; advance_pc (4);

slt $d, $s, $t

SLTI -- Set on less than immediate (signed)

Description: If $s is less than immediate, $t is set to one. It gets zero otherwise.

if $s < imm $t = 1; advance_pc (4); else $t = 0; advance_pc (4);

Operation:

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

7/10

�

6/8/12

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

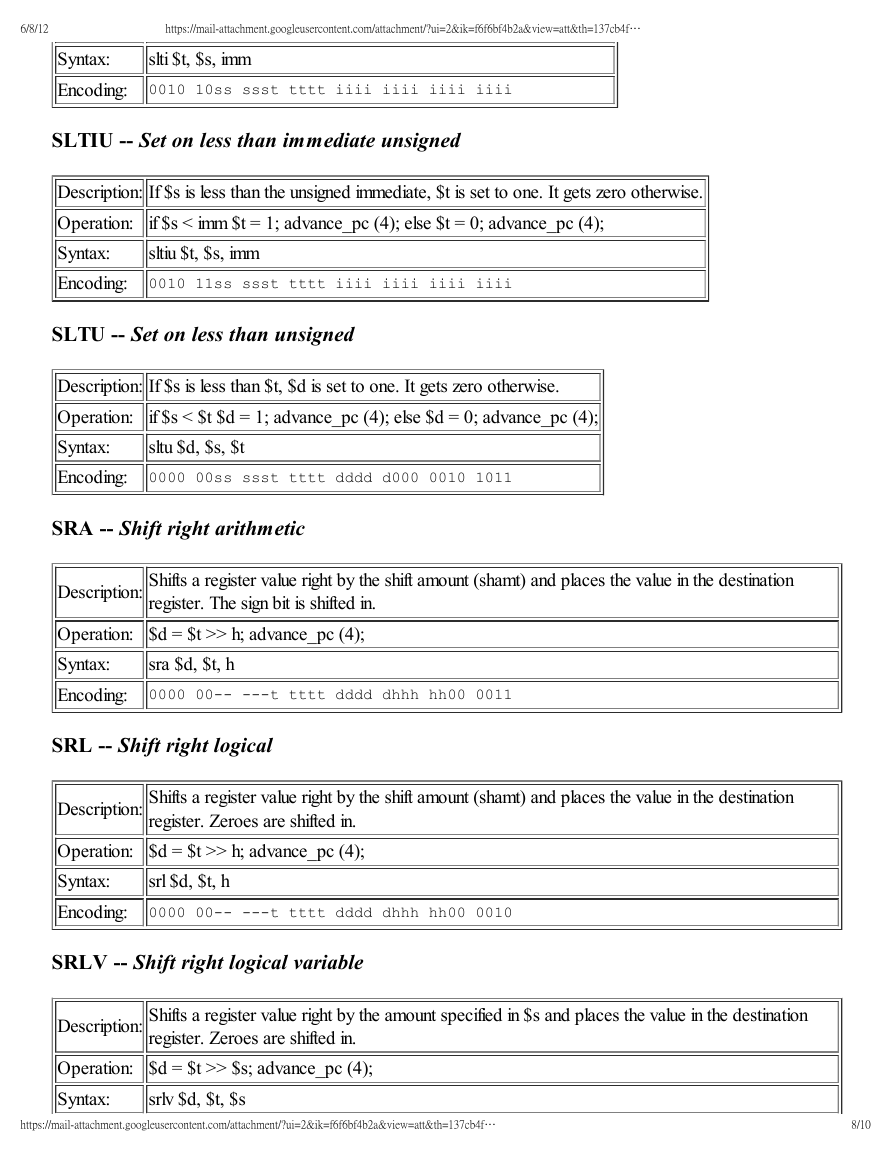

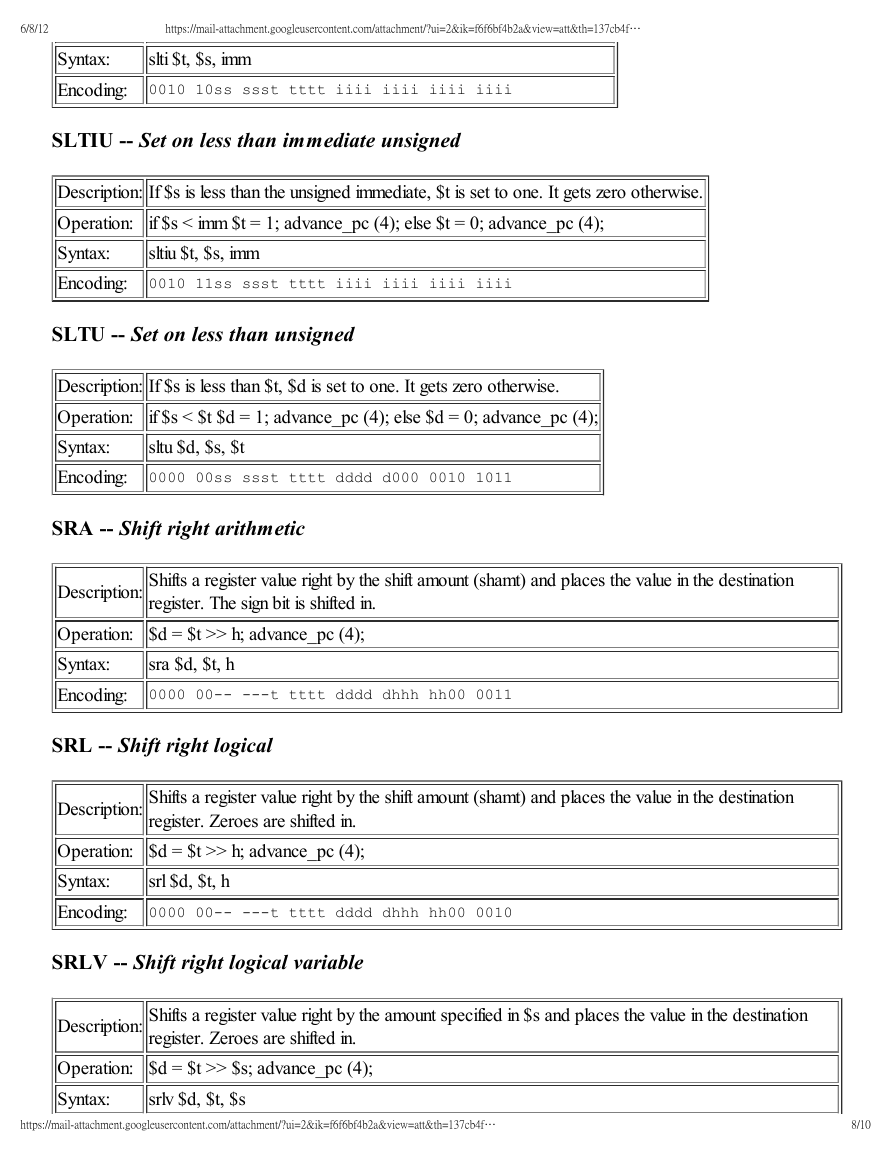

Syntax:

Encoding: 0010 10ss ssst tttt iiii iiii iiii iiii

slti $t, $s, imm

SLTIU -- Set on less than immediate unsigned

Description: If $s is less than the unsigned immediate, $t is set to one. It gets zero otherwise.

Operation:

Syntax:

Encoding: 0010 11ss ssst tttt iiii iiii iiii iiii

if $s < imm $t = 1; advance_pc (4); else $t = 0; advance_pc (4);

sltiu $t, $s, imm

SLTU -- Set on less than unsigned

Description: If $s is less than $t, $d is set to one. It gets zero otherwise.

Operation:

Syntax:

Encoding: 0000 00ss ssst tttt dddd d000 0010 1011

if $s < $t $d = 1; advance_pc (4); else $d = 0; advance_pc (4);

sltu $d, $s, $t

SRA -- Shift right arithmetic

Description: Shifts a register value right by the shift amount (shamt) and places the value in the destination

register. The sign bit is shifted in.

Operation: $d = $t >> h; advance_pc (4);

Syntax:

Encoding: 0000 00-- ---t tttt dddd dhhh hh00 0011

sra $d, $t, h

SRL -- Shift right logical

Description: Shifts a register value right by the shift amount (shamt) and places the value in the destination

register. Zeroes are shifted in.

Operation: $d = $t >> h; advance_pc (4);

Syntax:

Encoding: 0000 00-- ---t tttt dddd dhhh hh00 0010

srl $d, $t, h

SRLV -- Shift right logical variable

register. Zeroes are shifted in.

Description: Shifts a register value right by the amount specified in $s and places the value in the destination

Operation: $d = $t >> $s; advance_pc (4);

Syntax:

srlv $d, $t, $s

https://mail-attachment.googleusercontent.com/attachment/?ui=2&ik=f6f6bf4b2a&view=att&th=137cb4f…

8/10

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc