FEATURES

n Video Decoder

Small Size LCD TV Processor with Video Decoder

Preliminary Data Sheet Version 0.1

MST703

n Color Engine

Supports NTSC, PAL and SECAM video input

Brightness, contrast, saturation, and hue

formats

adjustment

2D NTSC and PAL comb-filter for Y/C

9-tap programmable multi-purpose FIR (Finite

separation of CVBS input

Multiple CVBS and S-video inputs

ACC, AGC, and DCGC (Digital Chroma Gain

Control)

n Analog Input

Supports RGB input format from PC,

camcorders and GPS

Supports YCbCr inputs from conventional video

Impulse Response) filter

Differential 3-band peaking engine

Luminance Transient Improvement (LTI)

Chrominance Transient Improvement (CTI)

Black Level Extension (BLE)

White Level Extension (WLE)

Favor Color Compensation (FCC)

3-channel gamma curve adjustment

source and HDTV

n Scaling Engine/Panel Interface

Supports video input 480i, 480p, 576i, 576p,

720p, 1080i; 1080P; RGB input resolution in

640x480, 800x480, and 800x600, 1024x768,

1280x1024

3-channel low-power 10-bit ADCs integration

for YCbCr and RGB

Supports RGB composite sync input (CSYNC),

SOY, SOG, HSYNC, and VSYNC

On-chip clock synthesizer and PLL

Auto-position adjustment, auto-phase

adjustment, auto-gain adjustment, and

auto-mode detection

Supports TTL/TCON and analog TCON panel

Supports single 8-bit TTL panel output

Supports various displaying modes

Supports horizontal panorama scaling

n Miscellaneous

Built-in MCU

Supports CCIR656 digital input

Built-in internal OSD with 256 programmable

fonts, 16-color palettes, and 12-bit color

resolution

Spread spectrum clocks

3.3V output pads with programmable driving

current

100-pin LQFP package

Copyright © 2010 MStar Semiconductor, Inc. All rights reserved.

- 1 -

11/24/2010

Mstar Confidential for 深圳市江启科技有限公司 Internal Use Only �

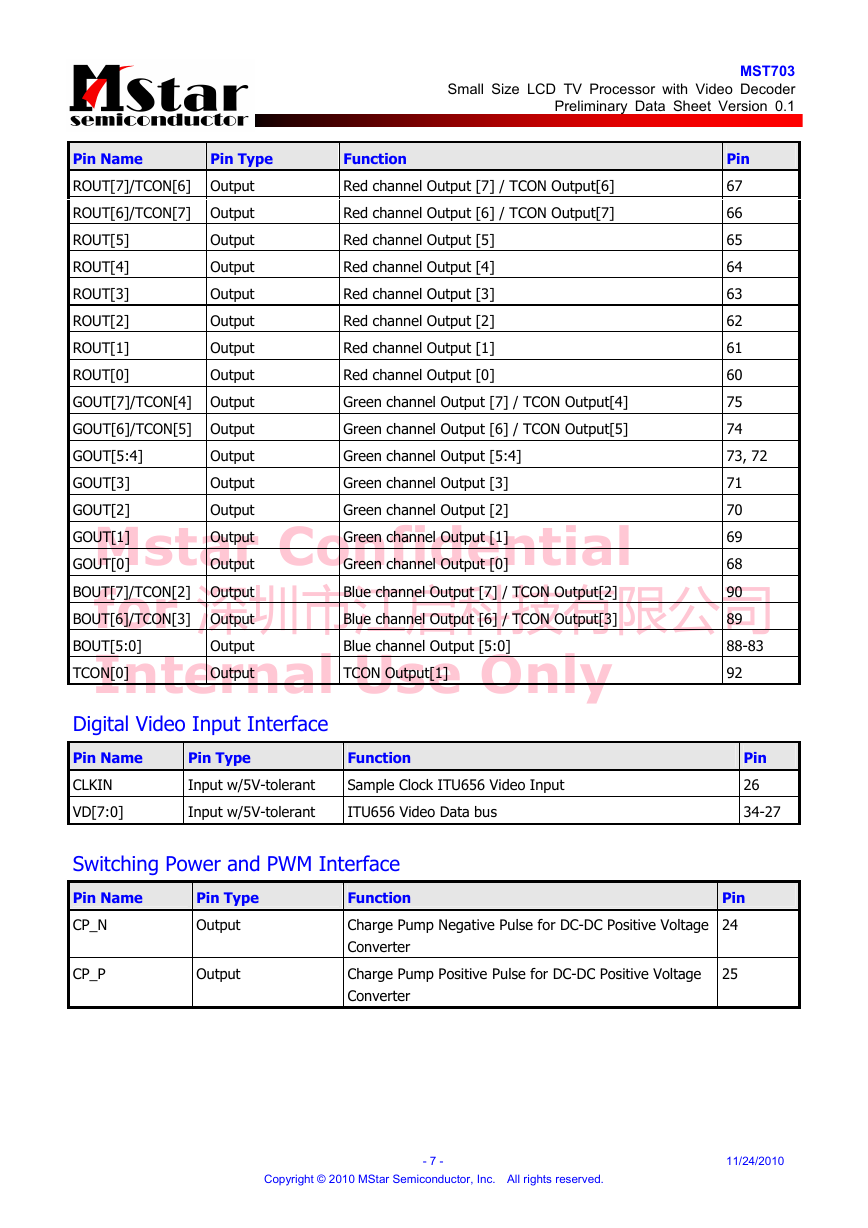

BLOCK DIAGRAM

RGB /YCbCr

CVBS 1/2

Switch

S-Video 1/2

R/Cr

G/Y

B/Cb

SY/CVBS

SC

Small Size LCD TV Processor with Video Decoder

Preliminary Data Sheet Version 0.1

MST703

Auto Function for RGB / YCbCr

ADC Input

2-Channel

AFE

Video Decoder

Timing Generator

YC Separation

2D Comb Filter

Chroma

Demodulator

M

U

X

3x3 Color Space

Conversion

MACE

Scaling Engine

CSC

(RGB to YCbCr)

OSD

Gamma

Display Unit

T-CON

Display

Device

MCU

BIU

Flash Memory or

EEPROM

External MCU

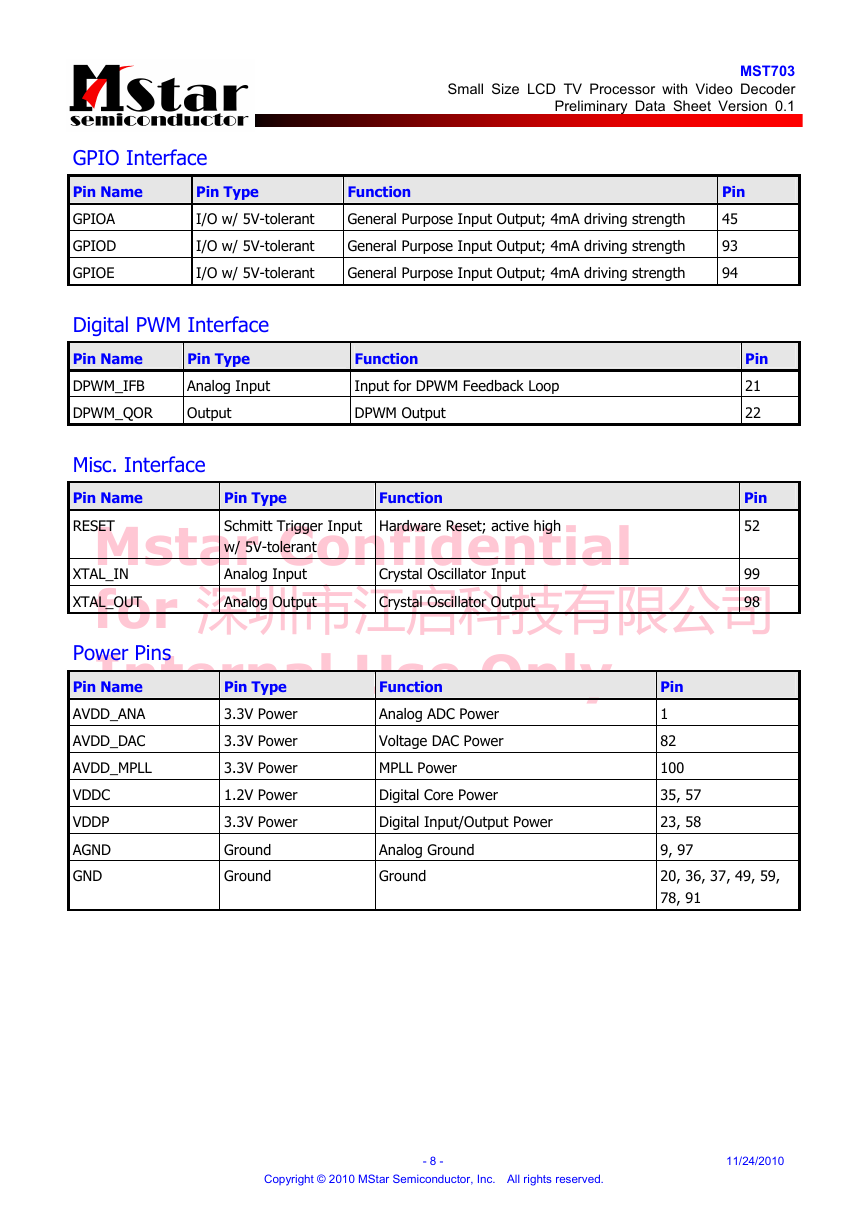

SYSTEM APPLICATION DIAGRAM

TV / Cable Signal

TV Tuner

Additional CVBS

DVD / VCD S-Video Signal

Additional S-Video

Additional RGB Signal

HDTV YPbPr Signal

Flash / ROM

1.8V

Micro-

Controller

Video

Decoder

PWM

Step-Down

TCON

To Digital Panel

Deinterlacer /

Scaler

TTL

TTL Out

Copyright © 2010 MStar Semiconductor, Inc. All rights reserved.

- 2 -

11/24/2010

Mstar Confidential for 深圳市江启科技有限公司 Internal Use Only �

Small Size LCD TV Processor with Video Decoder

Preliminary Data Sheet Version 0.1

MST703

GENERAL DESCRIPTION

The MST703 is a high quality ASIC for NTSC/PAL/SECAM car TV application. It receives analog

NTSC/PAL/SECAM CVBS and S-Video inputs from TV tuners, DVD or VCR sources, including weak and distorted

signals, as well as analog YCbCr input from HDTV/SDTV systems. Automatic gain control (AGC) and 10-bit

3-channel A/D converters provide high resolution video quantization. With automatic video source and mode

detection, users can easily switch and adjust variety of signal sources. Multiple internal adaptive PLLs precisely

extract pixel clock from video source and perform sharp color demodulation. Built-in line-buffer supports

adaptive 2-D comb-filter, 2-D sharpening, and synchronization stabler in a condense manner. The output

format of MST703 supports 6-bit TTL/TCON digital TFT-LCD modules.

Copyright © 2010 MStar Semiconductor, Inc. All rights reserved.

- 3 -

11/24/2010

Mstar Confidential for 深圳市江启科技有限公司 Internal Use Only �

Small Size LCD TV Processor with Video Decoder

Preliminary Data Sheet Version 0.1

MST703

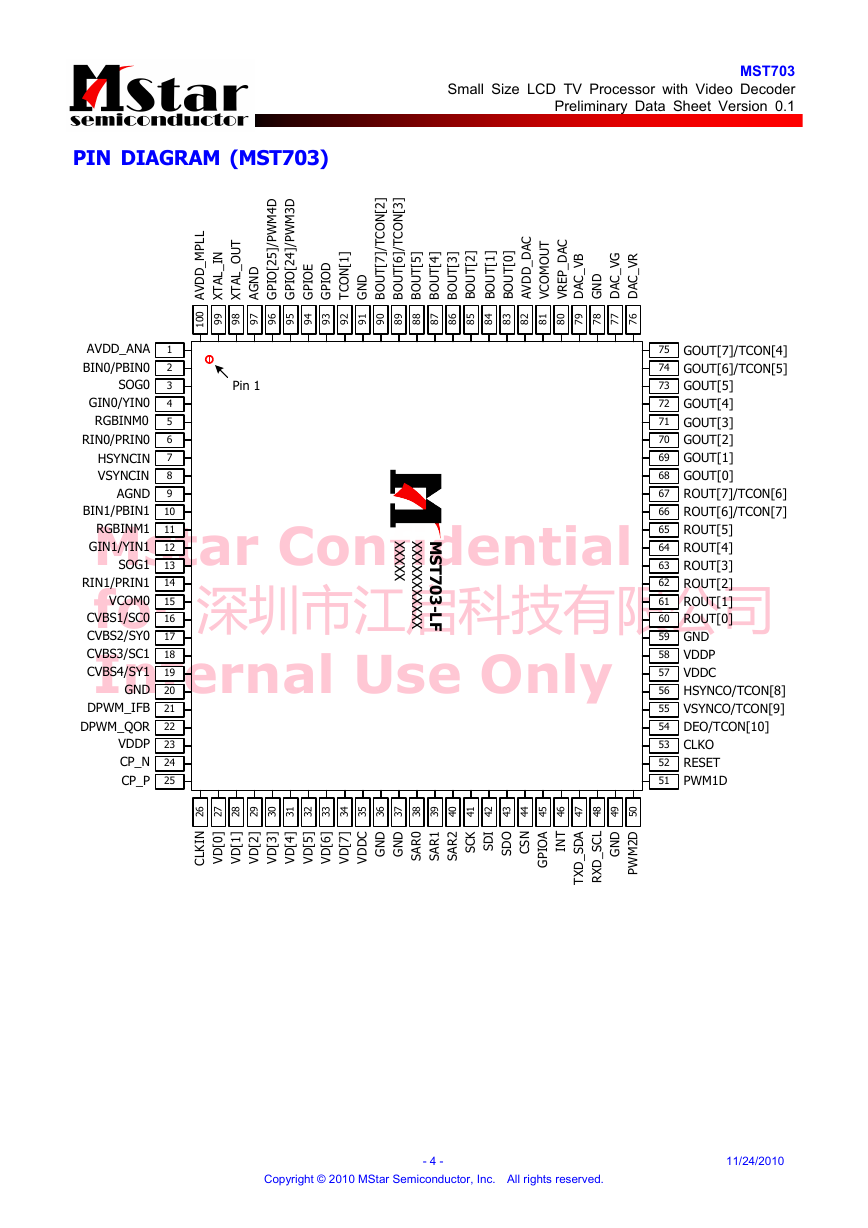

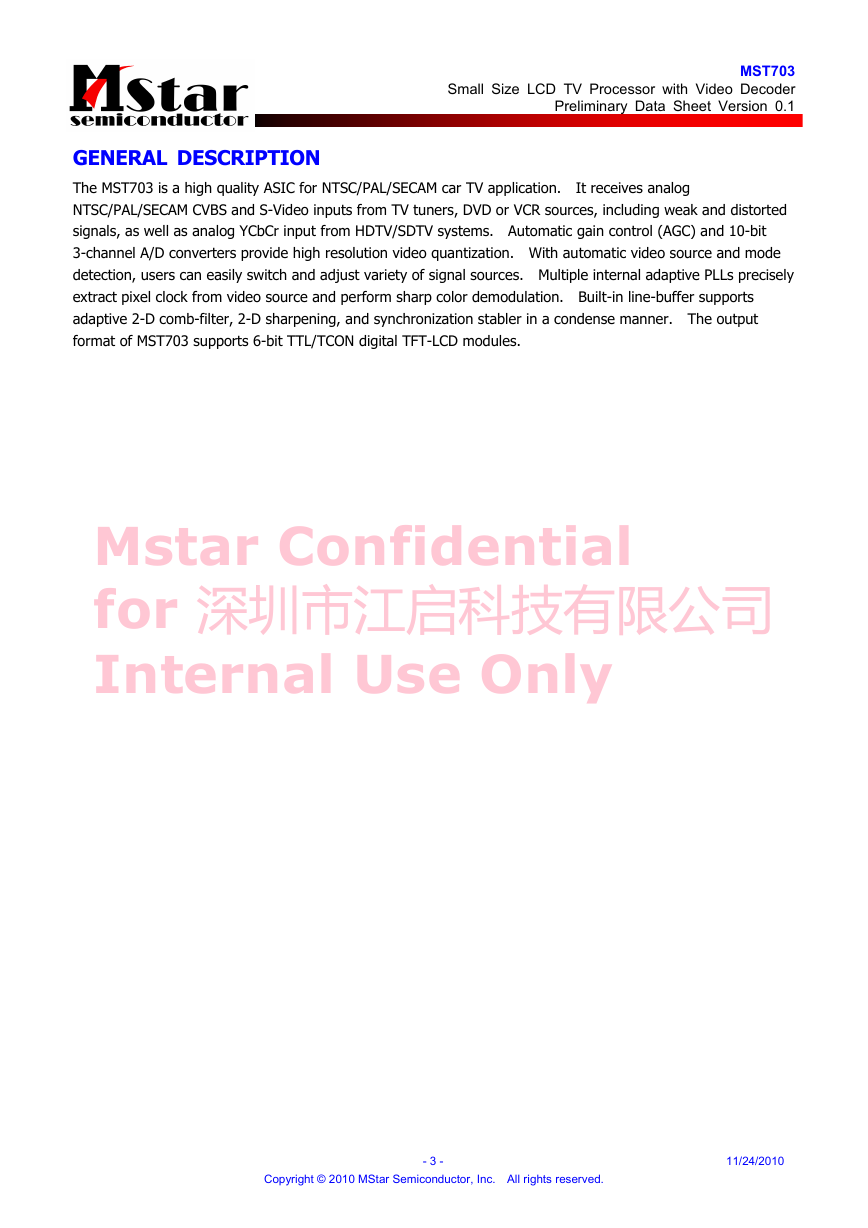

PIN DIAGRAM (MST703)

D

4

M

W

P

/

]

5

2

[

O

I

P

G

D

3

M

W

P

/

]

4

2

[

O

I

P

G

T

U

O

_

L

A

T

X

N

I

_

L

A

T

X

D

N

G

A

E

O

I

P

G

D

O

I

P

G

]

1

[

N

O

C

T

D

N

G

]

2

[

N

O

C

T

/

]

7

[

T

U

O

B

]

3

[

N

O

C

T

/

]

6

[

T

U

O

B

]

5

[

T

U

O

B

]

4

[

T

U

O

B

]

3

[

T

U

O

B

]

2

[

T

U

O

B

]

1

[

T

U

O

B

]

0

[

T

U

O

B

C

A

D

_

D

D

V

A

T

U

O

M

O

C

V

C

A

D

_

P

E

R

V

B

V

_

C

A

D

G

V

_

C

A

D

R

V

_

C

A

D

D

N

G

9

9

8

9

7

9

6

9

5

9

4

9

3

9

2

9

1

9

0

9

9

8

8

8

7

8

6

8

5

8

4

8

3

8

2

8

1

8

0

8

9

7

8

7

7

7

6

7

L

L

P

M

_

D

D

V

A

0

0

1

Pin 1

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

M

S

T

7

0

3

-

L

F

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

GOUT[7]/TCON[4]

GOUT[6]/TCON[5]

GOUT[5]

GOUT[4]

GOUT[3]

GOUT[2]

GOUT[1]

GOUT[0]

ROUT[7]/TCON[6]

ROUT[6]/TCON[7]

ROUT[5]

ROUT[4]

ROUT[3]

ROUT[2]

ROUT[1]

ROUT[0]

GND

VDDP

VDDC

HSYNCO/TCON[8]

VSYNCO/TCON[9]

DEO/TCON[10]

CLKO

RESET

PWM1D

6

2

7

2

8

2

9

2

0

3

1

3

2

3

3

3

4

3

5

3

6

3

7

3

8

3

9

3

0

4

1

4

2

4

3

4

4

4

5

4

6

4

7

4

8

4

9

4

0

5

N

I

K

L

C

]

0

[

D

V

]

1

[

D

V

]

2

[

D

V

]

3

[

D

V

]

4

[

D

V

]

5

[

D

V

]

6

[

D

V

]

7

[

D

V

C

D

D

V

D

N

G

D

N

G

0

R

A

S

1

R

A

S

2

R

A

S

K

C

S

I

D

S

O

D

S

N

S

C

T

N

I

A

O

I

P

G

A

D

S

_

D

X

T

L

C

S

_

D

X

R

D

N

G

D

2

M

W

P

Copyright © 2010 MStar Semiconductor, Inc. All rights reserved.

- 4 -

11/24/2010

AVDD_ANA

BIN0/PBIN0

SOG0

GIN0/YIN0

RGBINM0

RIN0/PRIN0

HSYNCIN

VSYNCIN

AGND

BIN1/PBIN1

RGBINM1

GIN1/YIN1

SOG1

RIN1/PRIN1

VCOM0

CVBS1/SC0

CVBS2/SY0

CVBS3/SC1

CVBS4/SY1

GND

DPWM_IFB

DPWM_QOR

VDDP

CP_N

CP_P

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

Mstar Confidential for 深圳市江启科技有限公司 Internal Use Only �

Small Size LCD TV Processor with Video Decoder

Preliminary Data Sheet Version 0.1

MST703

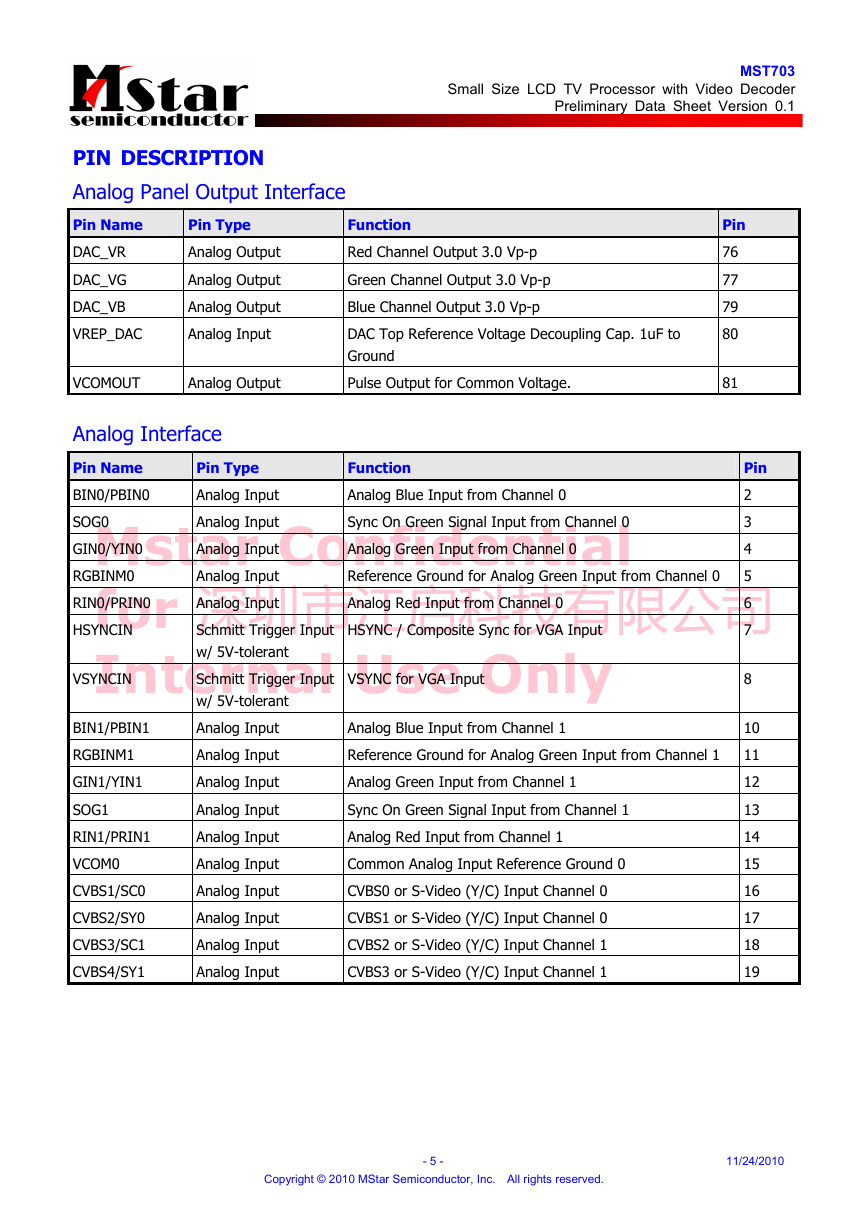

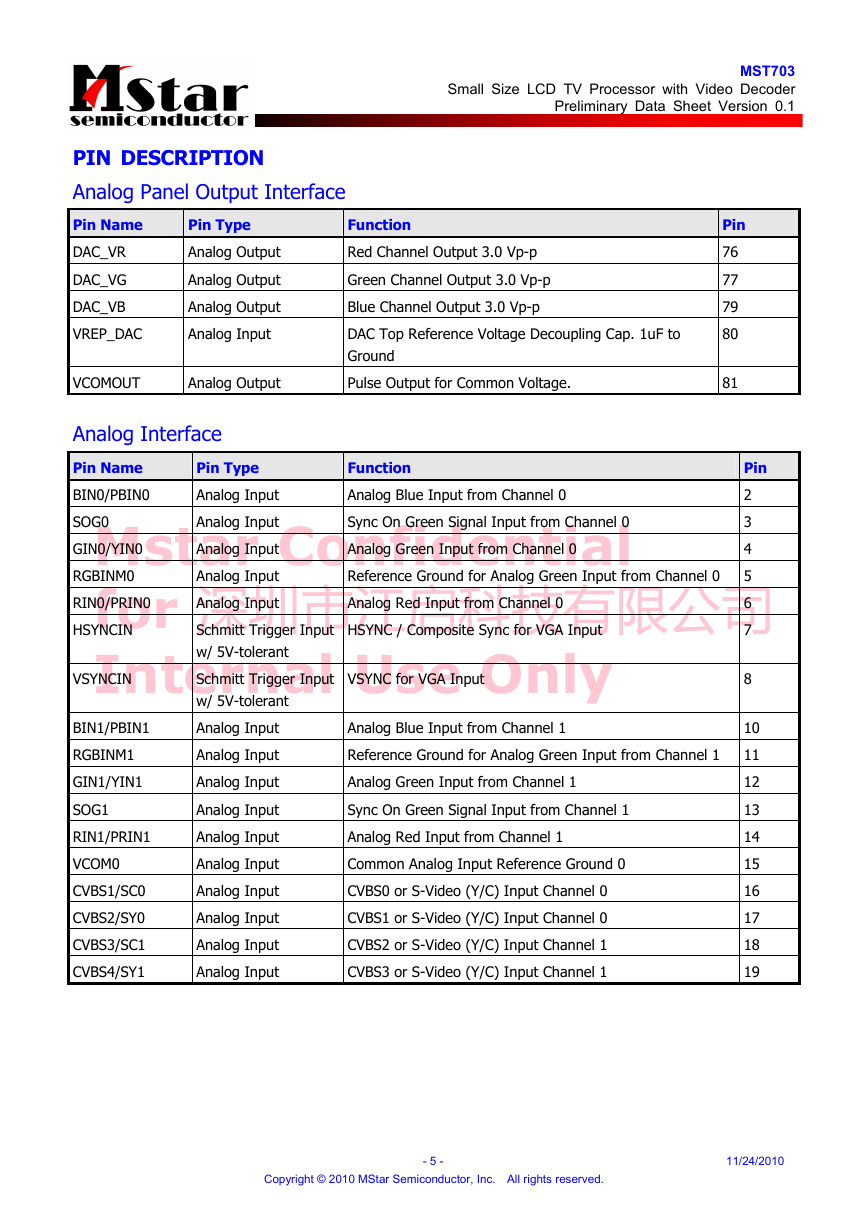

PIN DESCRIPTION

Analog Panel Output Interface

Pin Name

DAC_VR

DAC_VG

DAC_VB

VREP_DAC

Pin Type

Analog Output

Analog Output

Analog Output

Analog Input

Analog Output

Function

Red Channel Output 3.0 Vp-p

Green Channel Output 3.0 Vp-p

Blue Channel Output 3.0 Vp-p

DAC Top Reference Voltage Decoupling Cap. 1uF to

Ground

Pulse Output for Common Voltage.

Pin

76

77

79

80

81

VCOMOUT

Analog Interface

Pin Name

BIN0/PBIN0

SOG0

GIN0/YIN0

RGBINM0

RIN0/PRIN0

HSYNCIN

VSYNCIN

BIN1/PBIN1

RGBINM1

GIN1/YIN1

SOG1

RIN1/PRIN1

VCOM0

CVBS1/SC0

CVBS2/SY0

CVBS3/SC1

CVBS4/SY1

Pin Type

Analog Input

Analog Input

Analog Input

Analog Input

Analog Input

Schmitt Trigger Input

w/ 5V-tolerant

Schmitt Trigger Input

w/ 5V-tolerant

Analog Input

Analog Input

Analog Input

Analog Input

Analog Input

Analog Input

Analog Input

Analog Input

Analog Input

Analog Input

Function

Analog Blue Input from Channel 0

Sync On Green Signal Input from Channel 0

Analog Green Input from Channel 0

Reference Ground for Analog Green Input from Channel 0

Analog Red Input from Channel 0

HSYNC / Composite Sync for VGA Input

VSYNC for VGA Input

Analog Blue Input from Channel 1

Reference Ground for Analog Green Input from Channel 1

Analog Green Input from Channel 1

Sync On Green Signal Input from Channel 1

Analog Red Input from Channel 1

Common Analog Input Reference Ground 0

CVBS0 or S-Video (Y/C) Input Channel 0

CVBS1 or S-Video (Y/C) Input Channel 0

CVBS2 or S-Video (Y/C) Input Channel 1

CVBS3 or S-Video (Y/C) Input Channel 1

Pin

2

3

4

5

6

7

8

10

11

12

13

14

15

16

17

18

19

Copyright © 2010 MStar Semiconductor, Inc. All rights reserved.

- 5 -

11/24/2010

Mstar Confidential for 深圳市江启科技有限公司 Internal Use Only �

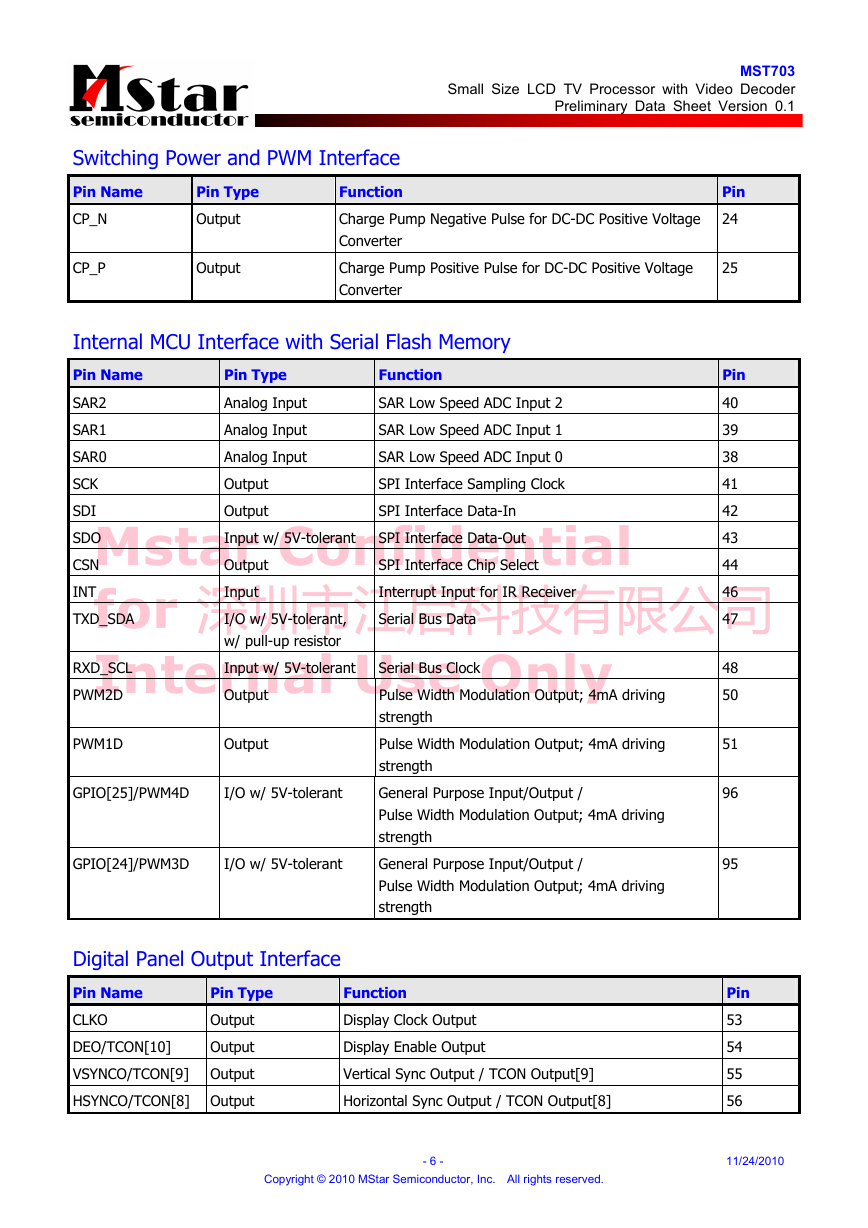

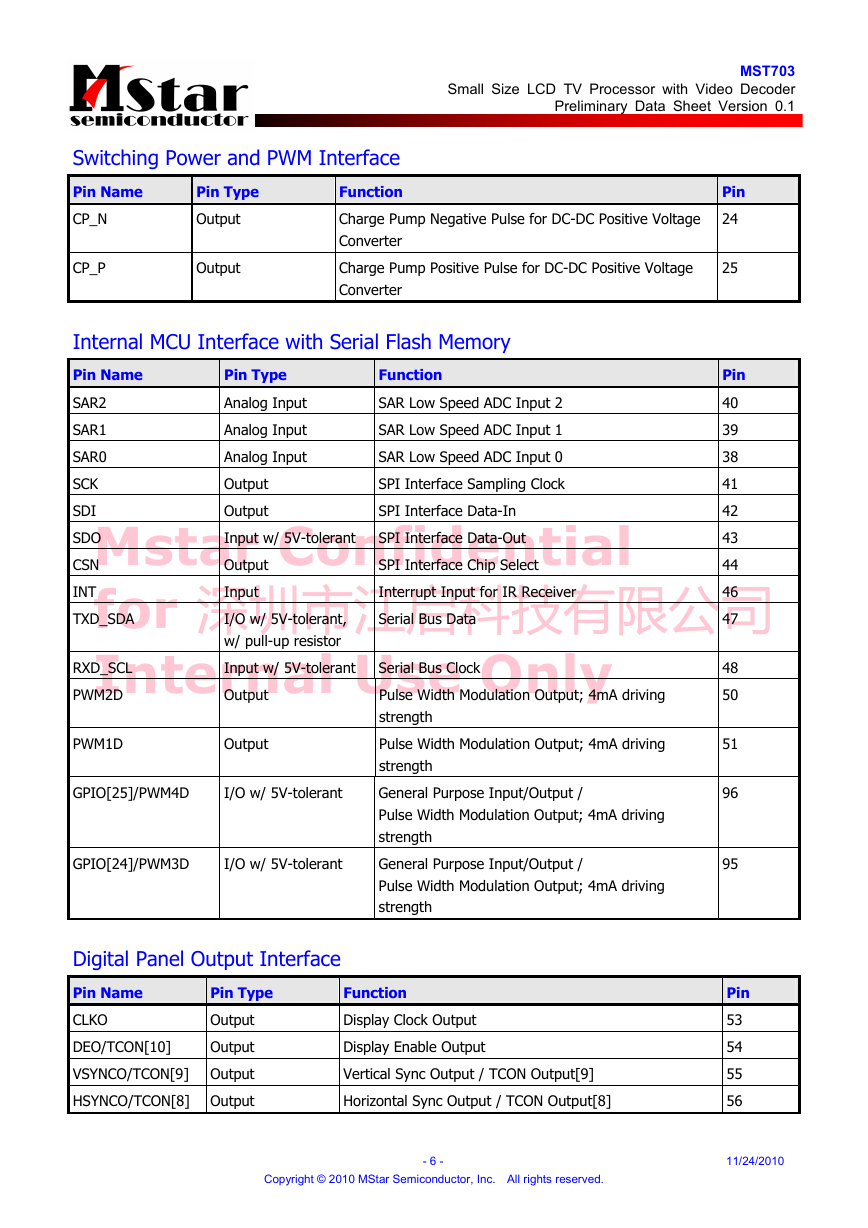

Switching Power and PWM Interface

Function

Pin Name

Charge Pump Negative Pulse for DC-DC Positive Voltage

CP_N

Converter

Charge Pump Positive Pulse for DC-DC Positive Voltage

Converter

Pin Type

Output

Output

CP_P

Internal MCU Interface with Serial Flash Memory

Pin Name

SAR2

SAR1

SAR0

SCK

SDI

SDO

CSN

INT

TXD_SDA

Function

SAR Low Speed ADC Input 2

SAR Low Speed ADC Input 1

SAR Low Speed ADC Input 0

SPI Interface Sampling Clock

SPI Interface Data-In

SPI Interface Data-Out

SPI Interface Chip Select

Interrupt Input for IR Receiver

Serial Bus Data

Pin Type

Analog Input

Analog Input

Analog Input

Output

Output

Input w/ 5V-tolerant

Output

Input

I/O w/ 5V-tolerant,

w/ pull-up resistor

Input w/ 5V-tolerant

Output

RXD_SCL

PWM2D

PWM1D

Output

GPIO[25]/PWM4D

I/O w/ 5V-tolerant

GPIO[24]/PWM3D

I/O w/ 5V-tolerant

Serial Bus Clock

Pulse Width Modulation Output; 4mA driving

strength

Pulse Width Modulation Output; 4mA driving

strength

General Purpose Input/Output /

Pulse Width Modulation Output; 4mA driving

strength

General Purpose Input/Output /

Pulse Width Modulation Output; 4mA driving

strength

Digital Panel Output Interface

Pin Type

Pin Name

Output

CLKO

Output

DEO/TCON[10]

VSYNCO/TCON[9] Output

HSYNCO/TCON[8] Output

Function

Display Clock Output

Display Enable Output

Vertical Sync Output / TCON Output[9]

Horizontal Sync Output / TCON Output[8]

Small Size LCD TV Processor with Video Decoder

Preliminary Data Sheet Version 0.1

MST703

Pin

24

25

Pin

40

39

38

41

42

43

44

46

47

48

50

51

96

95

Pin

53

54

55

56

Copyright © 2010 MStar Semiconductor, Inc. All rights reserved.

- 6 -

11/24/2010

Mstar Confidential for 深圳市江启科技有限公司 Internal Use Only �

Small Size LCD TV Processor with Video Decoder

Preliminary Data Sheet Version 0.1

MST703

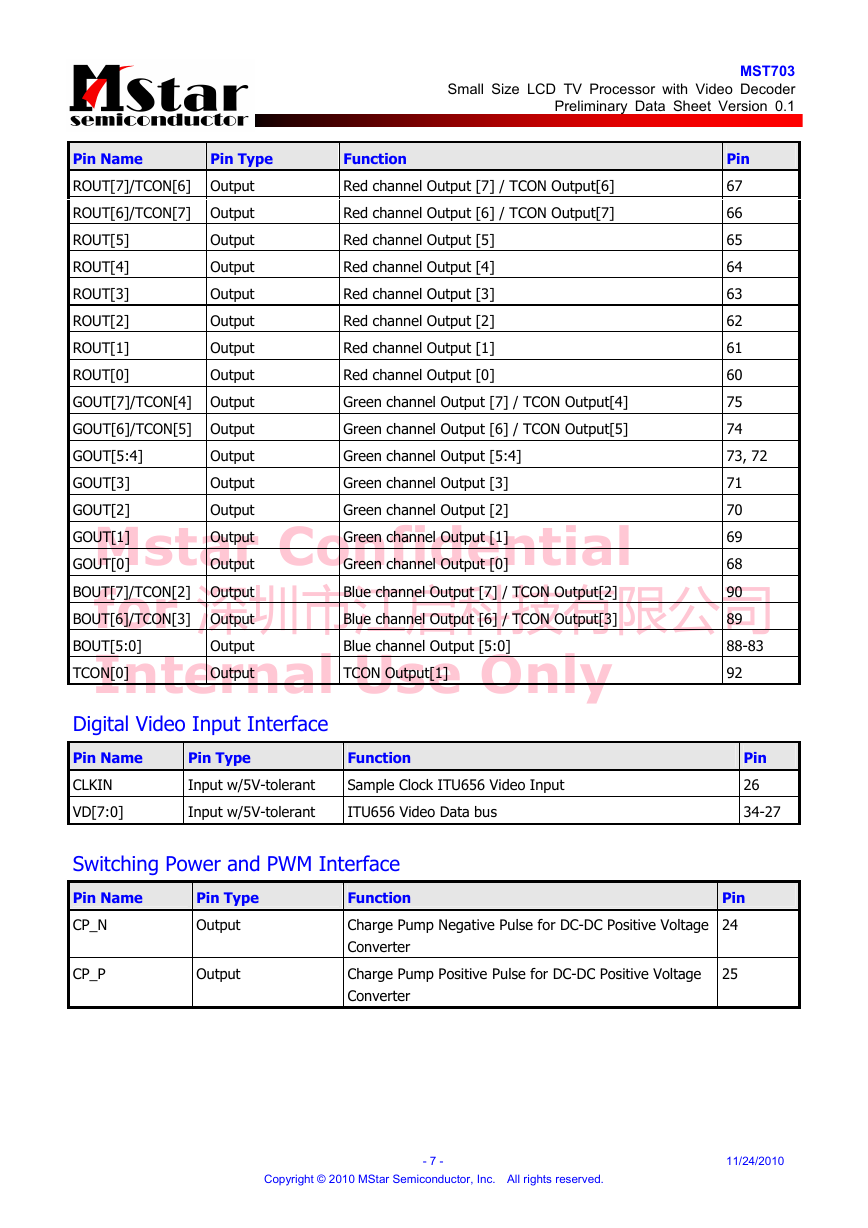

Pin Type

Function

Red channel Output [7] / TCON Output[6]

Red channel Output [6] / TCON Output[7]

Red channel Output [5]

Red channel Output [4]

Red channel Output [3]

Red channel Output [2]

Red channel Output [1]

Red channel Output [0]

Green channel Output [7] / TCON Output[4]

Green channel Output [6] / TCON Output[5]

Green channel Output [5:4]

Green channel Output [3]

Green channel Output [2]

Green channel Output [1]

Green channel Output [0]

Blue channel Output [7] / TCON Output[2]

Blue channel Output [6] / TCON Output[3]

Blue channel Output [5:0]

TCON Output[1]

Pin Name

ROUT[7]/TCON[6] Output

ROUT[6]/TCON[7] Output

Output

ROUT[5]

ROUT[4]

Output

Output

ROUT[3]

ROUT[2]

Output

Output

ROUT[1]

ROUT[0]

Output

GOUT[7]/TCON[4] Output

GOUT[6]/TCON[5] Output

Output

GOUT[5:4]

GOUT[3]

Output

Output

GOUT[2]

GOUT[1]

Output

GOUT[0]

Output

BOUT[7]/TCON[2] Output

BOUT[6]/TCON[3] Output

Output

BOUT[5:0]

TCON[0]

Output

Digital Video Input Interface

Pin Name

CLKIN

VD[7:0]

Switching Power and PWM Interface

Function

Pin Name

CP_N

Charge Pump Negative Pulse for DC-DC Positive Voltage

Converter

Charge Pump Positive Pulse for DC-DC Positive Voltage

Converter

Function

Sample Clock ITU656 Video Input

ITU656 Video Data bus

Pin Type

Input w/5V-tolerant

Input w/5V-tolerant

Pin Type

Output

Output

CP_P

Pin

67

66

65

64

63

62

61

60

75

74

73, 72

71

70

69

68

90

89

88-83

92

Pin

26

34-27

Pin

24

25

Copyright © 2010 MStar Semiconductor, Inc. All rights reserved.

- 7 -

11/24/2010

Mstar Confidential for 深圳市江启科技有限公司 Internal Use Only �

Pin Type

I/O w/ 5V-tolerant

I/O w/ 5V-tolerant

I/O w/ 5V-tolerant

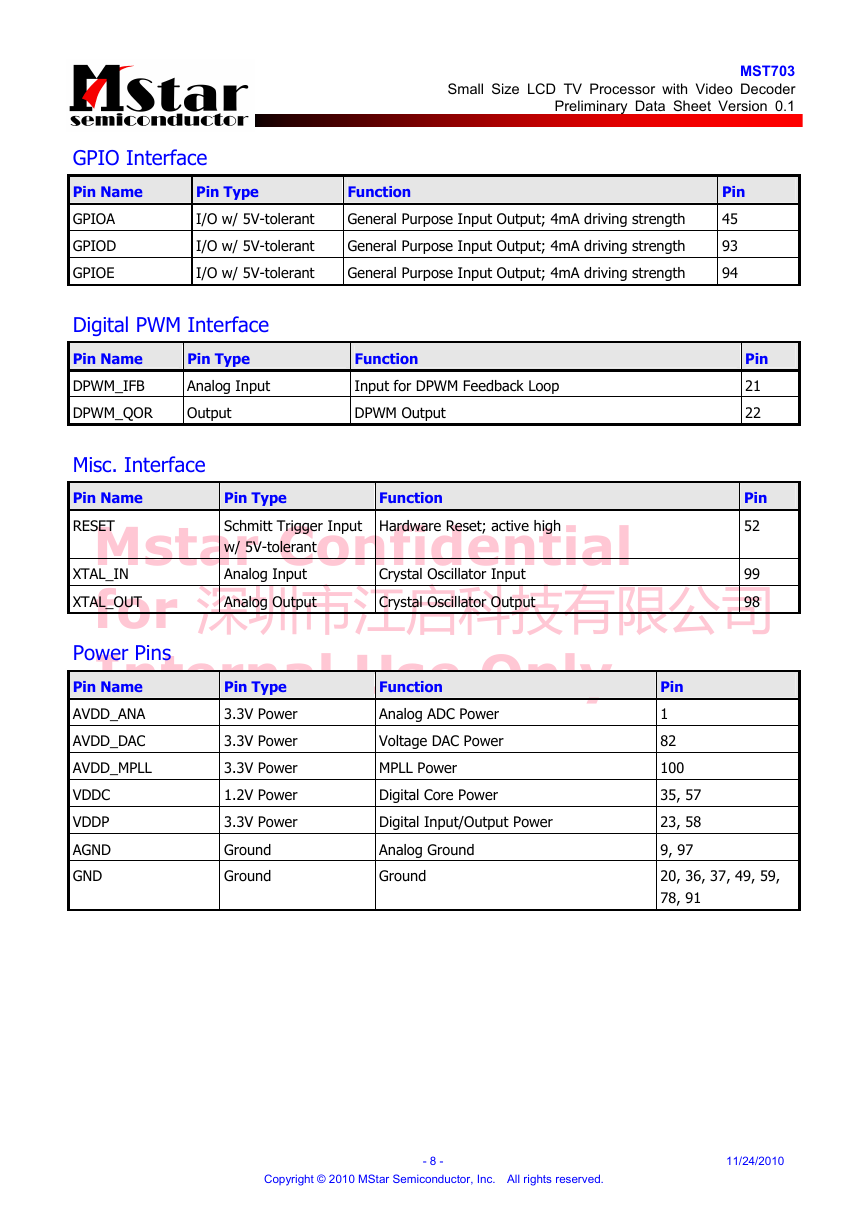

GPIO Interface

Pin Name

GPIOA

GPIOD

GPIOE

Digital PWM Interface

Pin Name

DPWM_IFB

DPWM_QOR

Misc. Interface

Pin Name

RESET

Pin Type

Analog Input

Output

Pin Type

Schmitt Trigger Input

w/ 5V-tolerant

Analog Input

Analog Output

Pin Type

3.3V Power

3.3V Power

3.3V Power

1.2V Power

3.3V Power

Ground

Ground

XTAL_IN

XTAL_OUT

Power Pins

Pin Name

AVDD_ANA

AVDD_DAC

AVDD_MPLL

VDDC

VDDP

AGND

GND

Copyright © 2010 MStar Semiconductor, Inc. All rights reserved.

- 8 -

Small Size LCD TV Processor with Video Decoder

Preliminary Data Sheet Version 0.1

MST703

Function

General Purpose Input Output; 4mA driving strength

General Purpose Input Output; 4mA driving strength

General Purpose Input Output; 4mA driving strength

Pin

45

93

94

Function

Input for DPWM Feedback Loop

DPWM Output

Function

Hardware Reset; active high

Crystal Oscillator Input

Crystal Oscillator Output

Function

Analog ADC Power

Voltage DAC Power

MPLL Power

Digital Core Power

Digital Input/Output Power

Analog Ground

Ground

Pin

21

22

Pin

52

99

98

Pin

1

82

100

35, 57

23, 58

9, 97

20, 36, 37, 49, 59,

78, 91

11/24/2010

Mstar Confidential for 深圳市江启科技有限公司 Internal Use Only �

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc