R

针对 Spartan-3E FT256 BGA 封装的四层和六层

高速 PCB 设计

XAPP489 (v1.0) 2006 年 10 月 31 日

应用指南: Spartan-3E 系列

提要

简介

本应用指南针对 FT256 1 mm BGA 封装的 Spartan™-3E FPGA,讨论了低成本、四至六层、

大批量印刷电路板 (PCB) 的布局问题,同时探讨高速信号和信号完整性 (SI) 因素对低层数 PCB

布局的影响。本应用指南的读者为设计工程师、管理人员和 PCB 布局人员,他们对与 SI 相关

的设计问题应当已经有所了解。本应用指南主要讲述 FT256 封装的 Spartan-3E 器件,但这些

信息也适用于同等的 FG256 封装,其中包含的通用指南可用于优化其他器件和封装的电路板

布局。

左右 PCB 成本的主要因素有两个:制造能力和产量。设计低成本 PCB 的规则取决于 PCB 生产

设备能按最低价格制造出什么。这一现实情况还决定着在既保持低成本又适于大批量制造的电

路中可实现的 PCB 层数。遗憾的是,市场对增加可编程逻辑的封装引脚数的需求意味着更小

的形状因数,因此加大了对 PCB 布局成本的压力。尽管如此,如果使用 FT256 1 mm 球栅阵列

(BGA) 封装的 Spartan-3E FPGA,仍然能以尽量低的成本设计出四层电路板。

如果用外来设计规则 (如 1 mils 迹线与间隔)设计电路板,则可选的制造方案有限,且成本高

昂。一密耳即千分之一英寸,亦称一英毫,等于 0.0254 毫米。某些北美厂家或许能够用这些

规则制造电路板,但将此种 PCB 制造工艺搬到亚洲的主流生产设备上却不大可能大幅度降低

成本。随着产量的提高,有更多厂家乐于制造电路板以降低成本,但是,达到可接受的成本所

需的时间可能比产品的寿命还要长。本应用指南即针对这一情况提出能改进制造方案和降低成

本的一些解决办法。

尽量降低成本的

PCB 设计规则

表 1 所示为不同制造地点大量生产不同层数 PCB 的制造成本。层越多,制造成本越高;具体

成本因产量和市场条件而异。

表 1: PCB 制造成本

制造地点

美国国内

亚洲

成本 (美元 / 平方英尺)(1)

2 层

0.18

0.13

4 层

0.22

0.16

6 层

0.24

0.17

注:

1. 这是 2004 年中期估算的成本,假定板材利用率为 100%,未包括不可用面积 (如划线截去的面积)。

© 2006 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at http://www.xilinx.com/legal.htm. All other

trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this

feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you

may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any

warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

XAPP489 (v1.0) 2006 年 10 月 31 日

www.xilinx.com/cn

1

�

球栅间距、引出路径和扇出端

R

表 2 所列为业界广泛接受、能尽量降低制造成本的制造规则。例如,小迹线的公差难以控制;

而设计迹线宽度不小于 5 mils 的 PCB (如表 2 所示)可尽量降低制造成本。

表 2: 有助于尽量降低成本的制造规则

特征尺寸

BGA 球焊盘直径

迹线宽度

间隔

过孔外径

过孔外径

英制 (mils)

公制 (mm)

15

5

5

23

12

0.381

0.127

0.127

0.584

0.305

球栅间距、引出

路径和扇出端

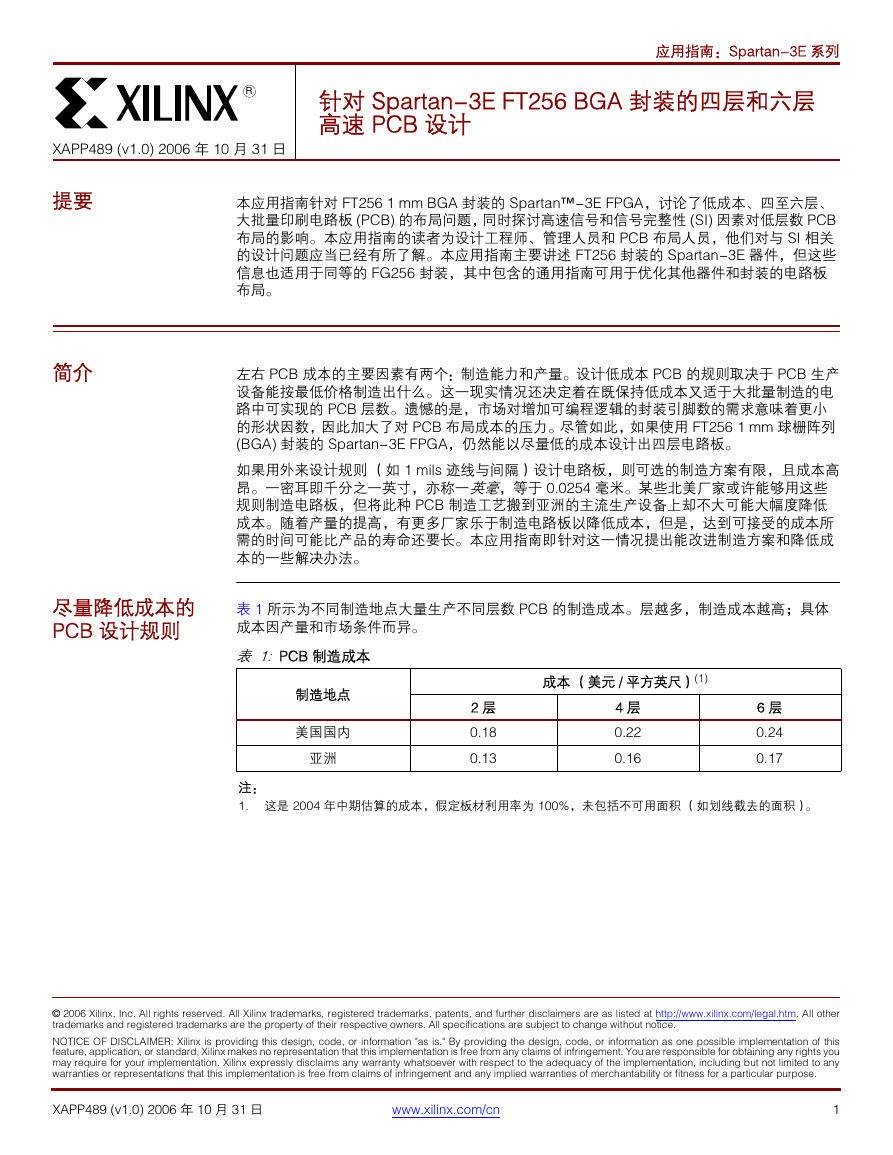

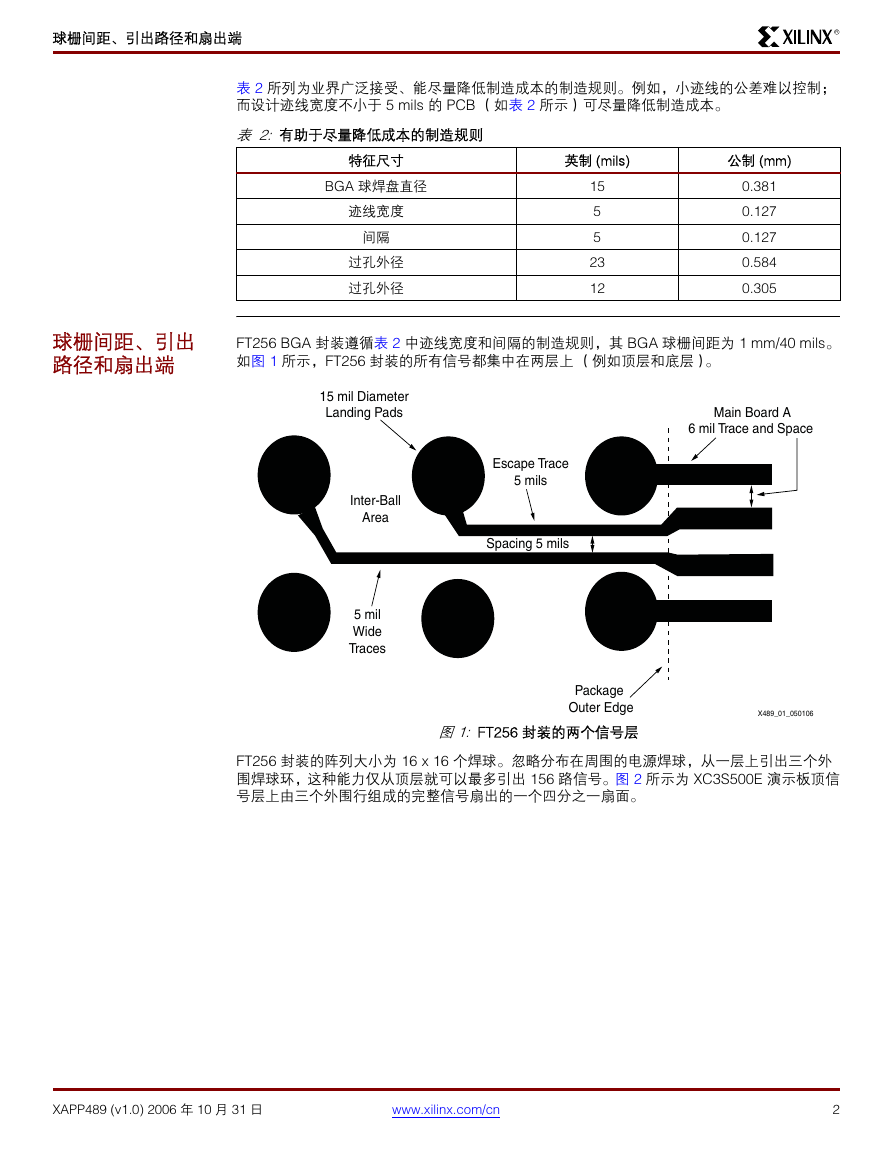

FT256 BGA 封装遵循表 2 中迹线宽度和间隔的制造规则,其 BGA 球栅间距为 1 mm/40 mils。

如图 1 所示,FT256 封装的所有信号都集中在两层上 (例如顶层和底层)。

15 mil Diameter

Landing Pads

Main Board A

6 mil Trace and Space

Escape Trace

5 mils

Spacing 5 mils

Inter-Ball

Area

5 mil

Wide

Traces

Package

Outer Edge

X489_01_050106

图 1: FT256 封装的两个信号层

FT256 封装的阵列大小为 16 x 16 个焊球。忽略分布在周围的电源焊球,从一层上引出三个外

围焊球环,这种能力仅从顶层就可以最多引出 156 路信号。图 2 所示为 XC3S500E 演示板顶信

号层上由三个外围行组成的完整信号扇出的一个四分之一扇面。

XAPP489 (v1.0) 2006 年 10 月 31 日

www.xilinx.com/cn

2

�

球栅间距、引出路径和扇出端

R

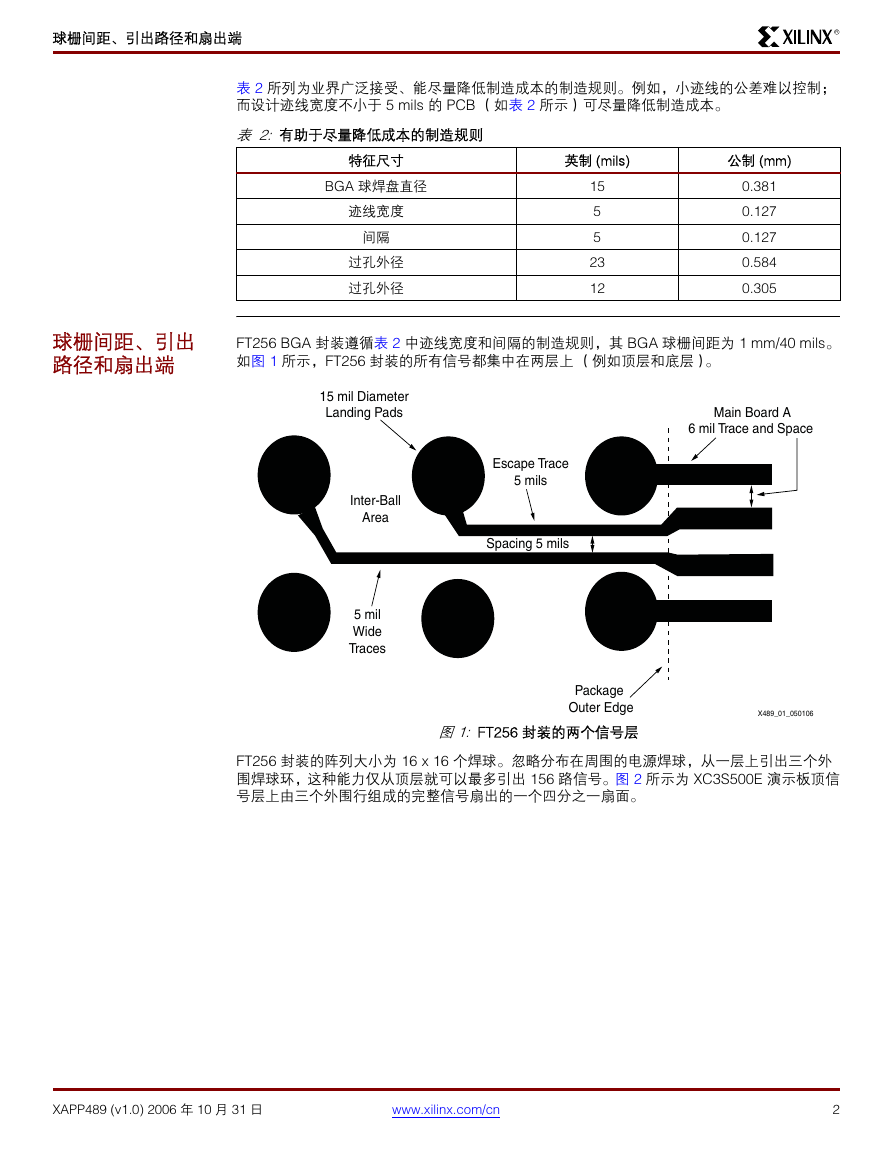

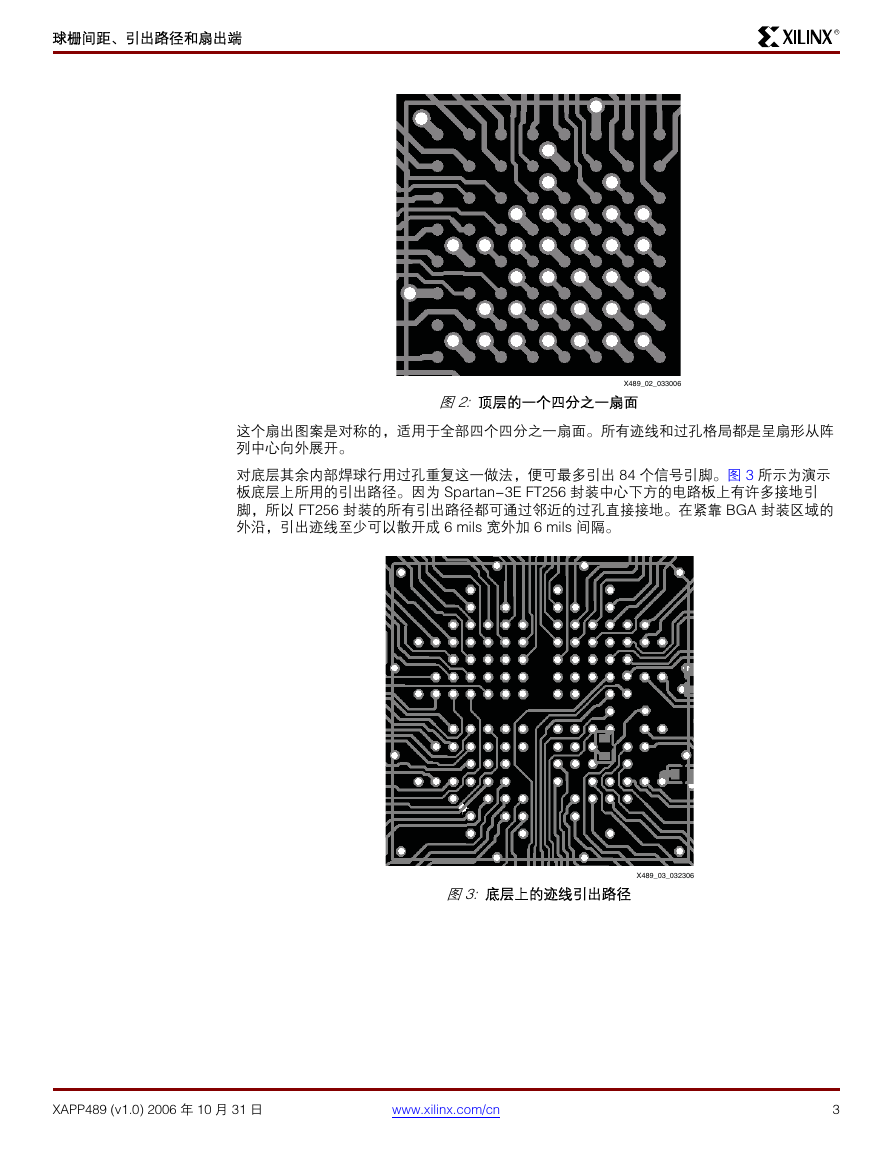

图 2: 顶层的一个四分之一扇面

X489_02_033006

这个扇出图案是对称的,适用于全部四个四分之一扇面。所有迹线和过孔格局都是呈扇形从阵

列中心向外展开。

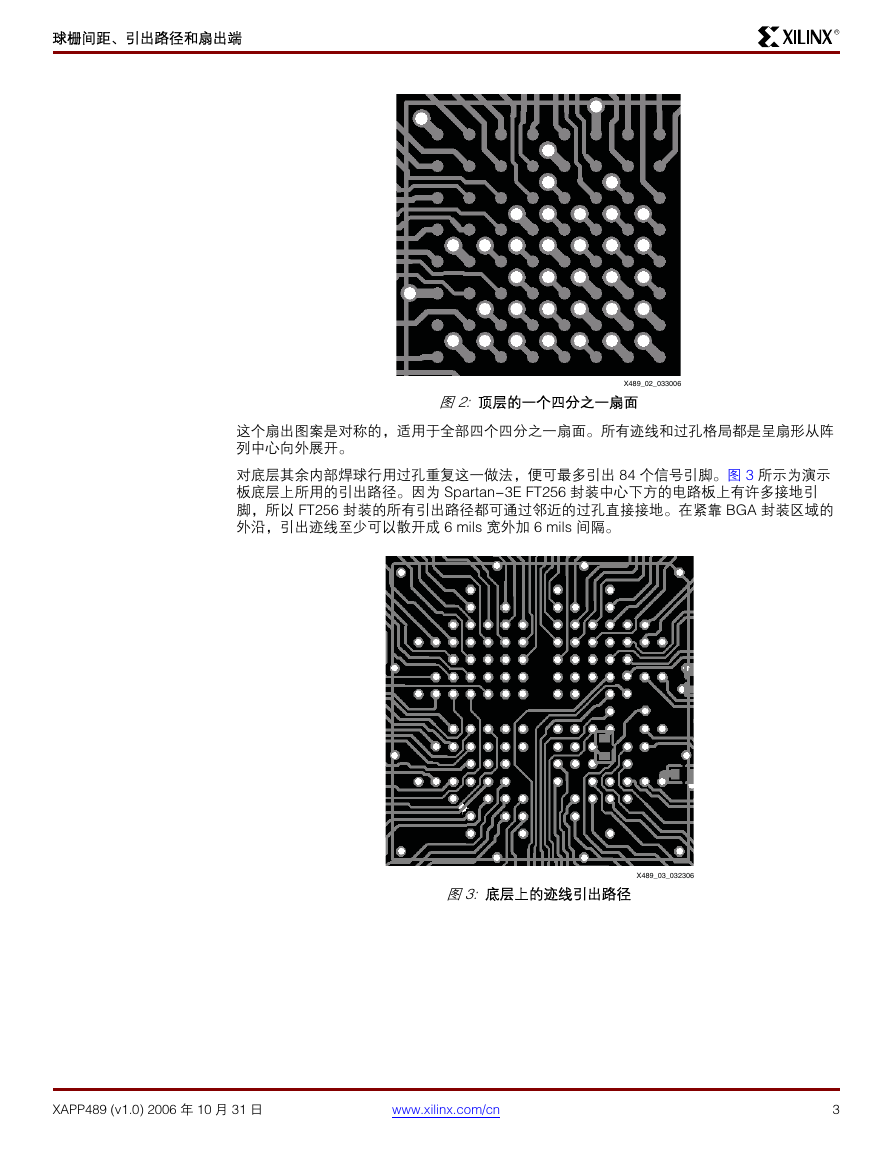

对底层其余内部焊球行用过孔重复这一做法,便可最多引出 84 个信号引脚。图 3 所示为演示

板底层上所用的引出路径。因为 Spartan-3E FT256 封装中心下方的电路板上有许多接地引

脚,所以 FT256 封装的所有引出路径都可通过邻近的过孔直接接地。在紧靠 BGA 封装区域的

外沿,引出迹线至少可以散开成 6 mils 宽外加 6 mils 间隔。

图 3: 底层上的迹线引出路径

X489_03_032306

XAPP489 (v1.0) 2006 年 10 月 31 日

www.xilinx.com/cn

3

�

过孔位置

过孔位置

R

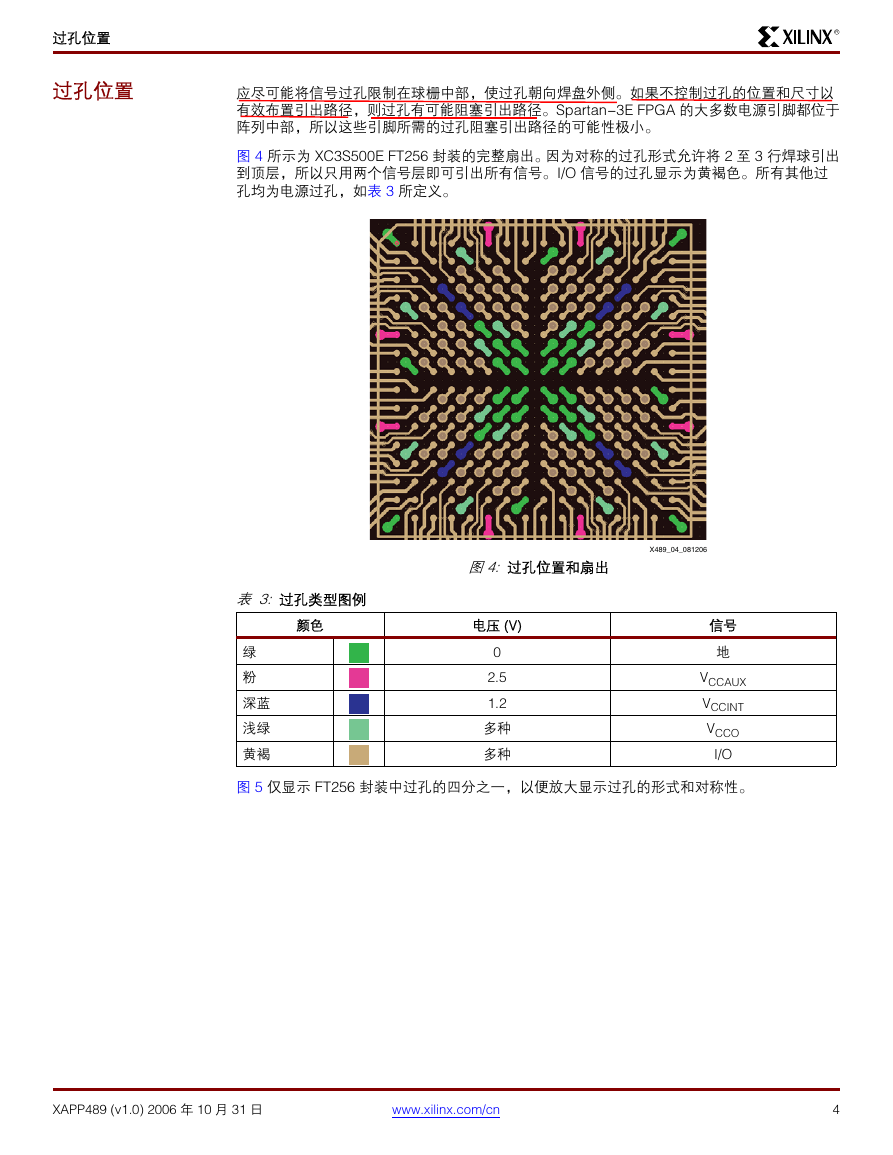

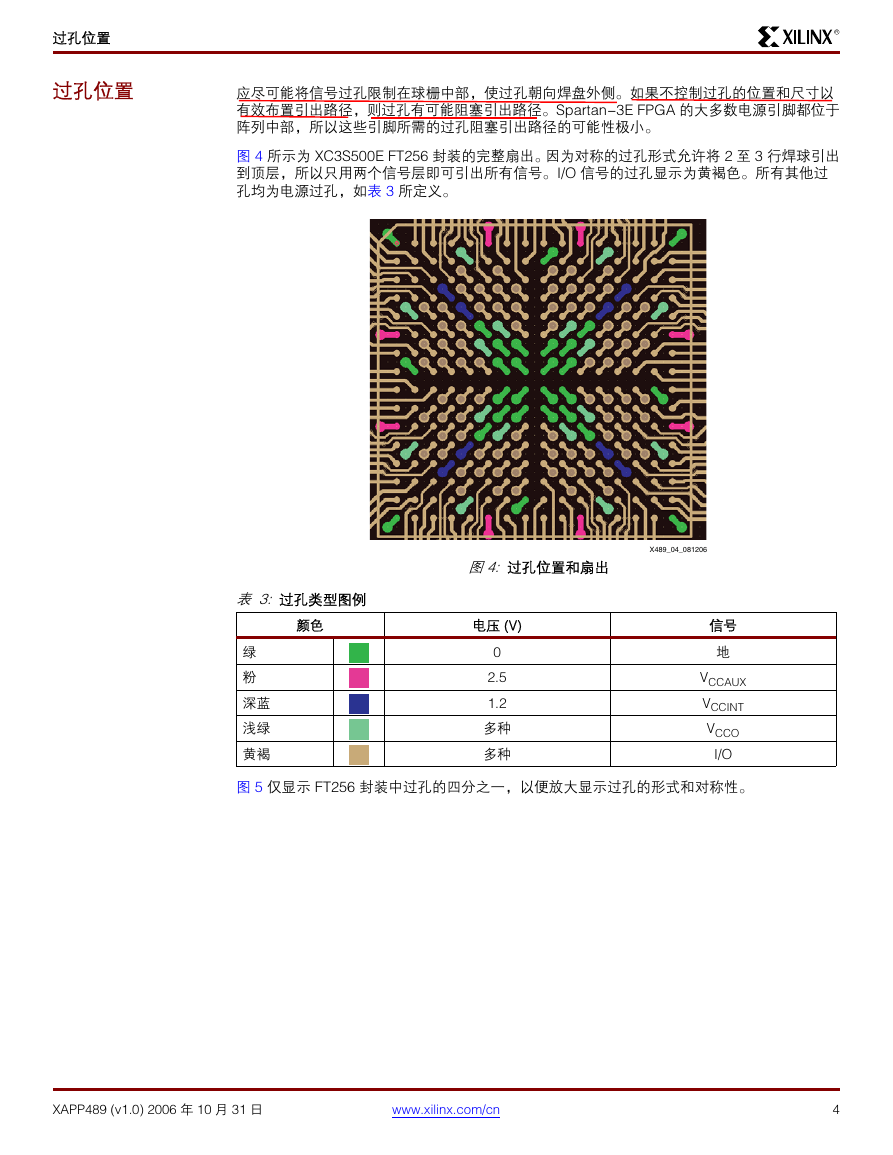

应尽可能将信号过孔限制在球栅中部,使过孔朝向焊盘外侧。如果不控制过孔的位置和尺寸以

有效布置引出路径,则过孔有可能阻塞引出路径。Spartan-3E FPGA 的大多数电源引脚都位于

阵列中部,所以这些引脚所需的过孔阻塞引出路径的可能性极小。

图 4 所示为 XC3S500E FT256 封装的完整扇出。因为对称的过孔形式允许将 2 至 3 行焊球引出

到顶层,所以只用两个信号层即可引出所有信号。I/O 信号的过孔显示为黄褐色。所有其他过

孔均为电源过孔,如表 3 所定义。

图 4: 过孔位置和扇出

X489_04_081206

表 3: 过孔类型图例

颜色

电压 (V)

绿

粉

深蓝

浅绿

黄褐

0

2.5

1.2

多种

多种

信号

地

VCCAUX

VCCINT

VCCO

I/O

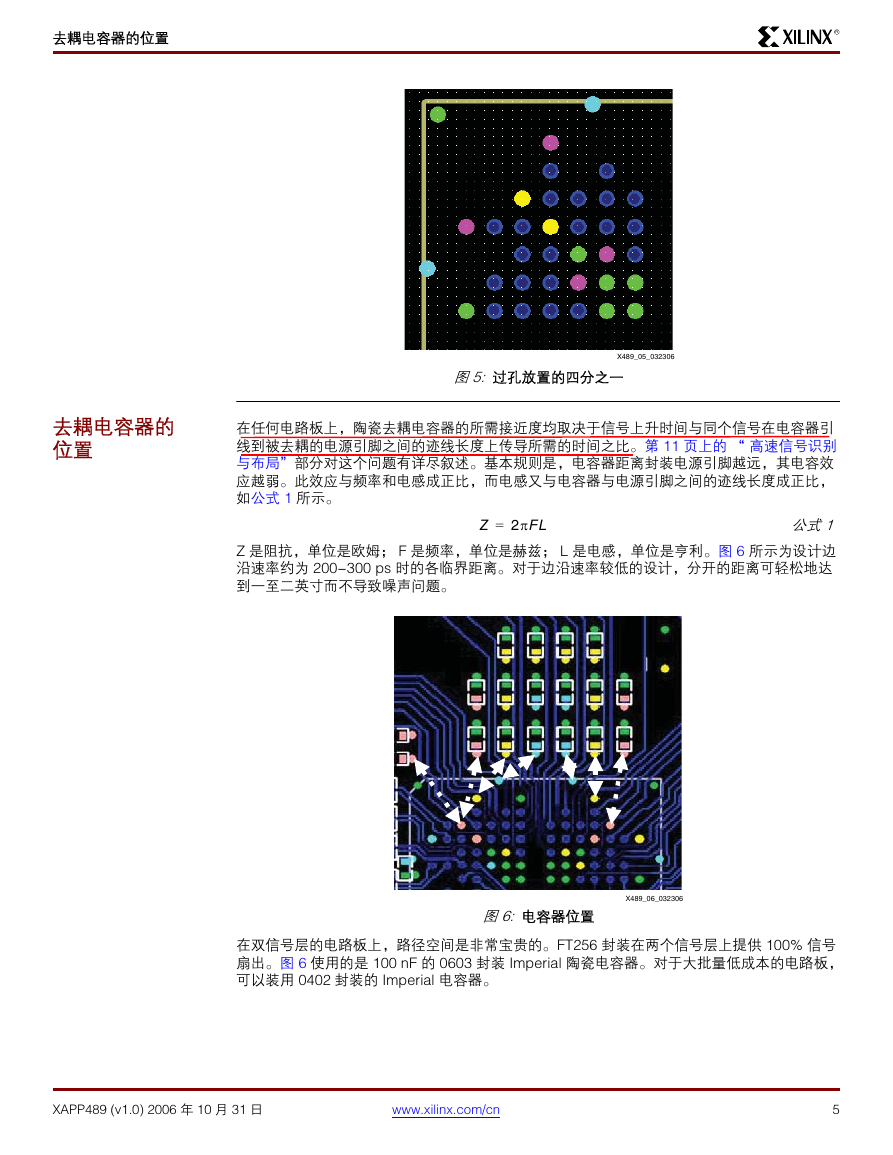

图 5 仅显示 FT256 封装中过孔的四分之一,以便放大显示过孔的形式和对称性。

XAPP489 (v1.0) 2006 年 10 月 31 日

www.xilinx.com/cn

4

�

去耦电容器的位置

R

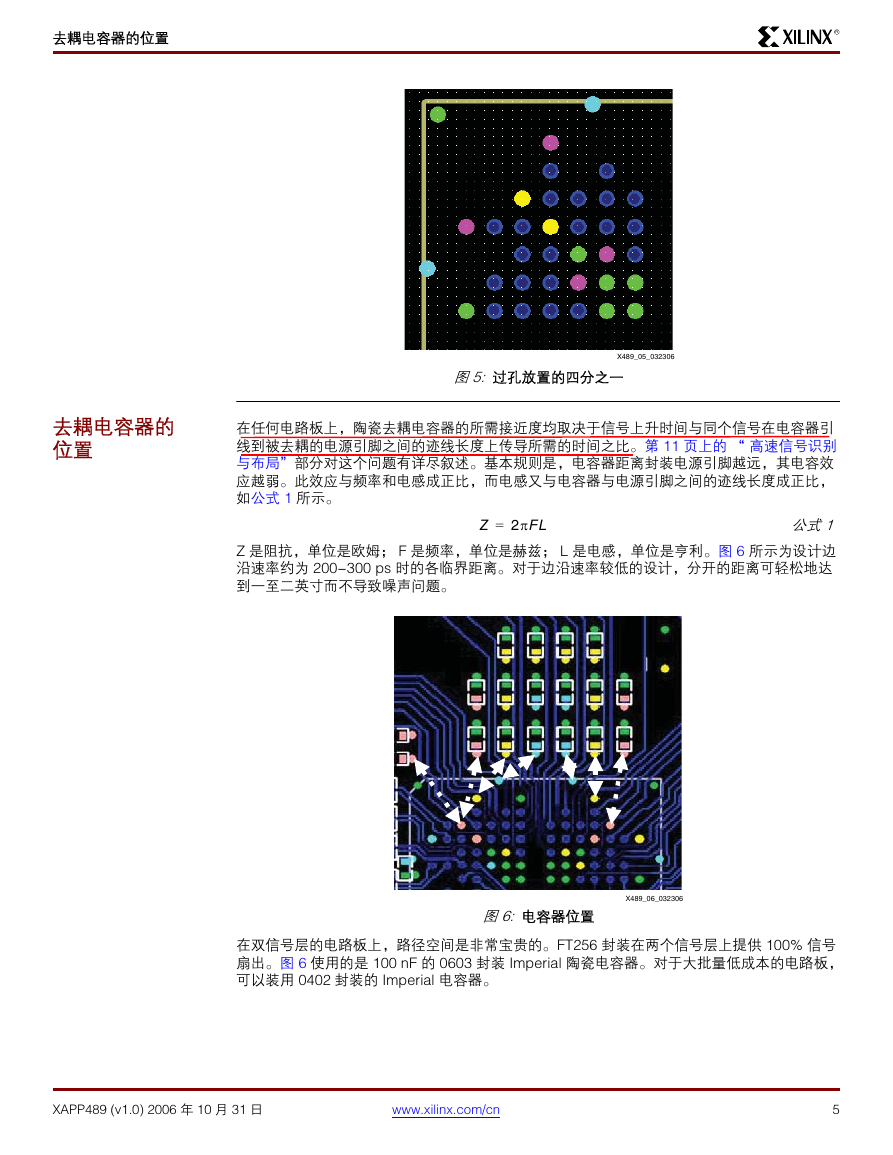

图 5: 过孔放置的四分之一

X489_05_032306

去耦电容器的

位置

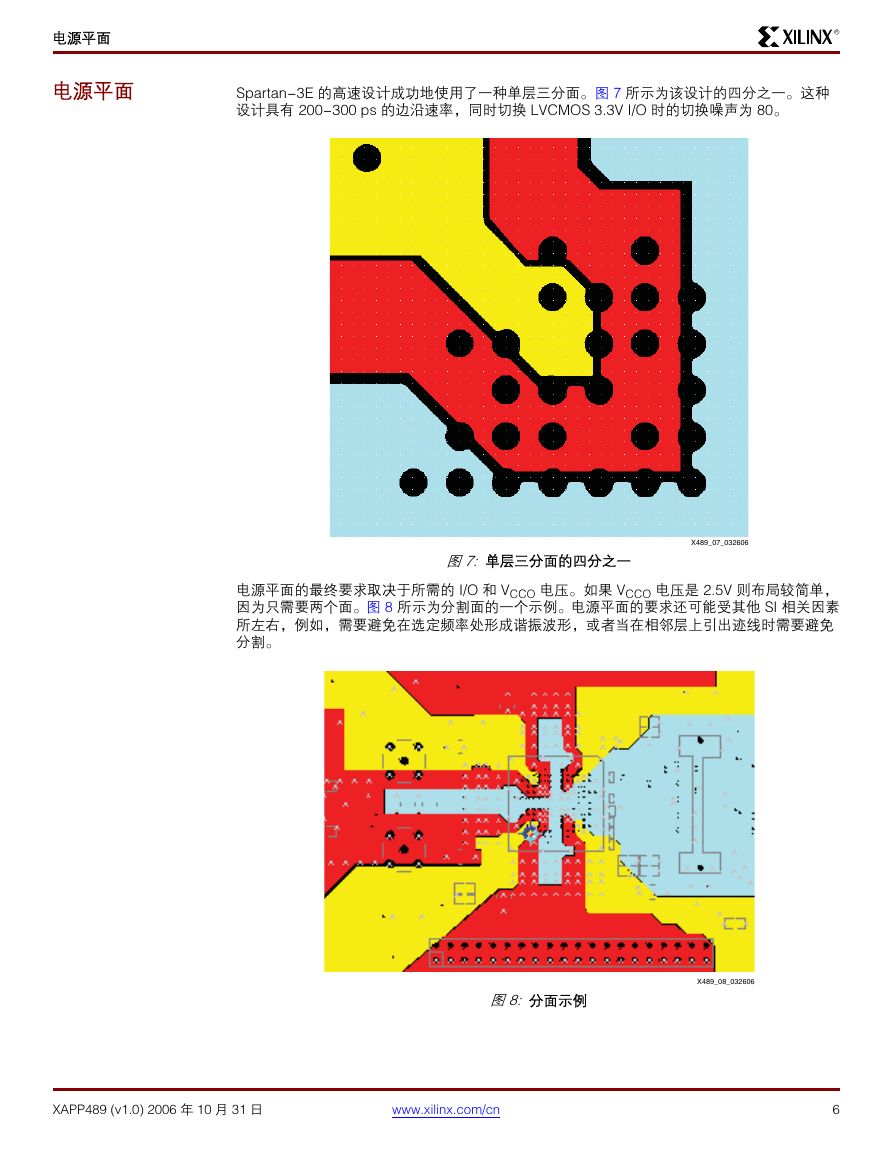

在任何电路板上,陶瓷去耦电容器的所需接近度均取决于信号上升时间与同个信号在电容器引

线到被去耦的电源引脚之间的迹线长度上传导所需的时间之比。第 11 页上的 “ 高速信号识别

与布局”部分对这个问题有详尽叙述。基本规则是,电容器距离封装电源引脚越远,其电容效

应越弱。此效应与频率和电感成正比,而电感又与电容器与电源引脚之间的迹线长度成正比,

如公式 1 所示。

Z

=

2πFL

公式1

Z 是阻抗,单位是欧姆; F 是频率,单位是赫兹; L 是电感,单位是亨利。图 6 所示为设计边

沿速率约为 200-300 ps 时的各临界距离。对于边沿速率较低的设计,分开的距离可轻松地达

到一至二英寸而不导致噪声问题。

图 6: 电容器位置

X489_06_032306

在双信号层的电路板上,路径空间是非常宝贵的。FT256 封装在两个信号层上提供 100% 信号

扇出。图 6 使用的是 100 nF 的 0603 封装 Imperial 陶瓷电容器。对于大批量低成本的电路板,

可以装用 0402 封装的 Imperial 电容器。

XAPP489 (v1.0) 2006 年 10 月 31 日

www.xilinx.com/cn

5

�

电源平面

电源平面

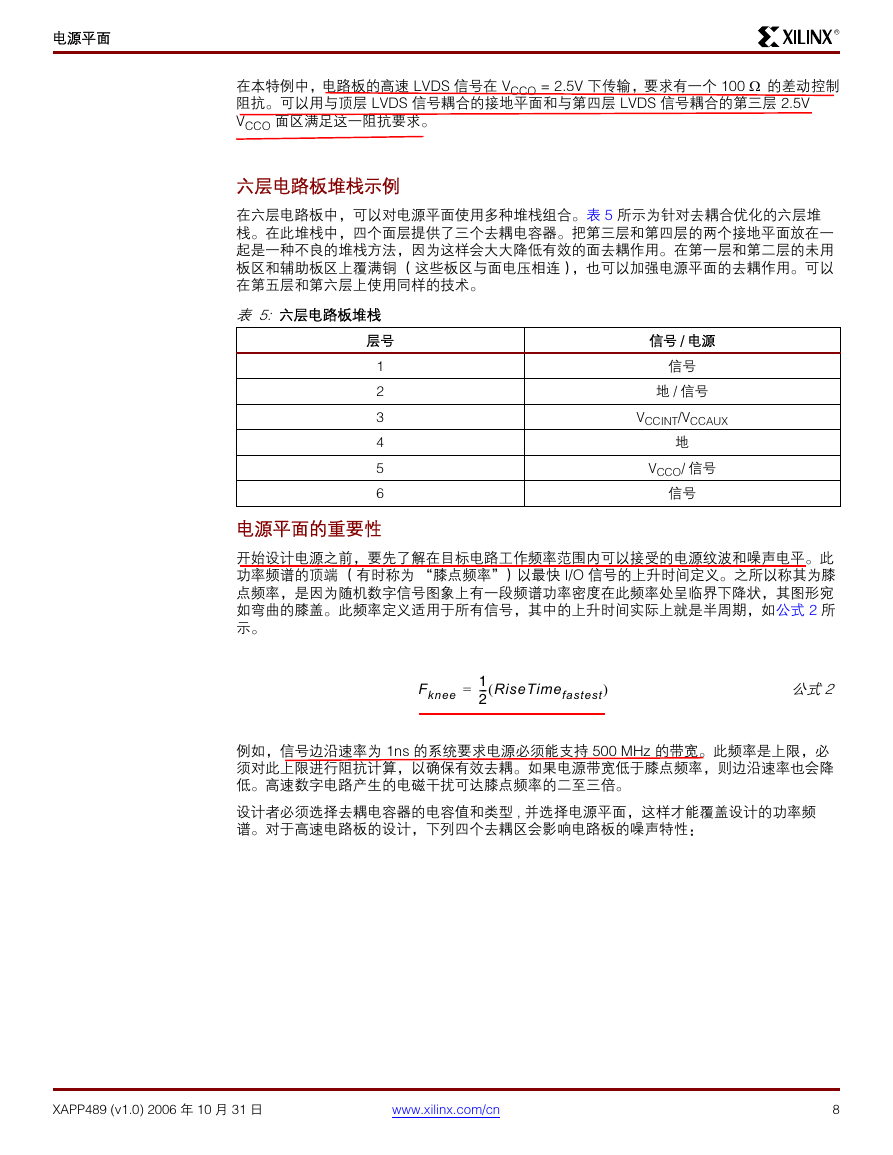

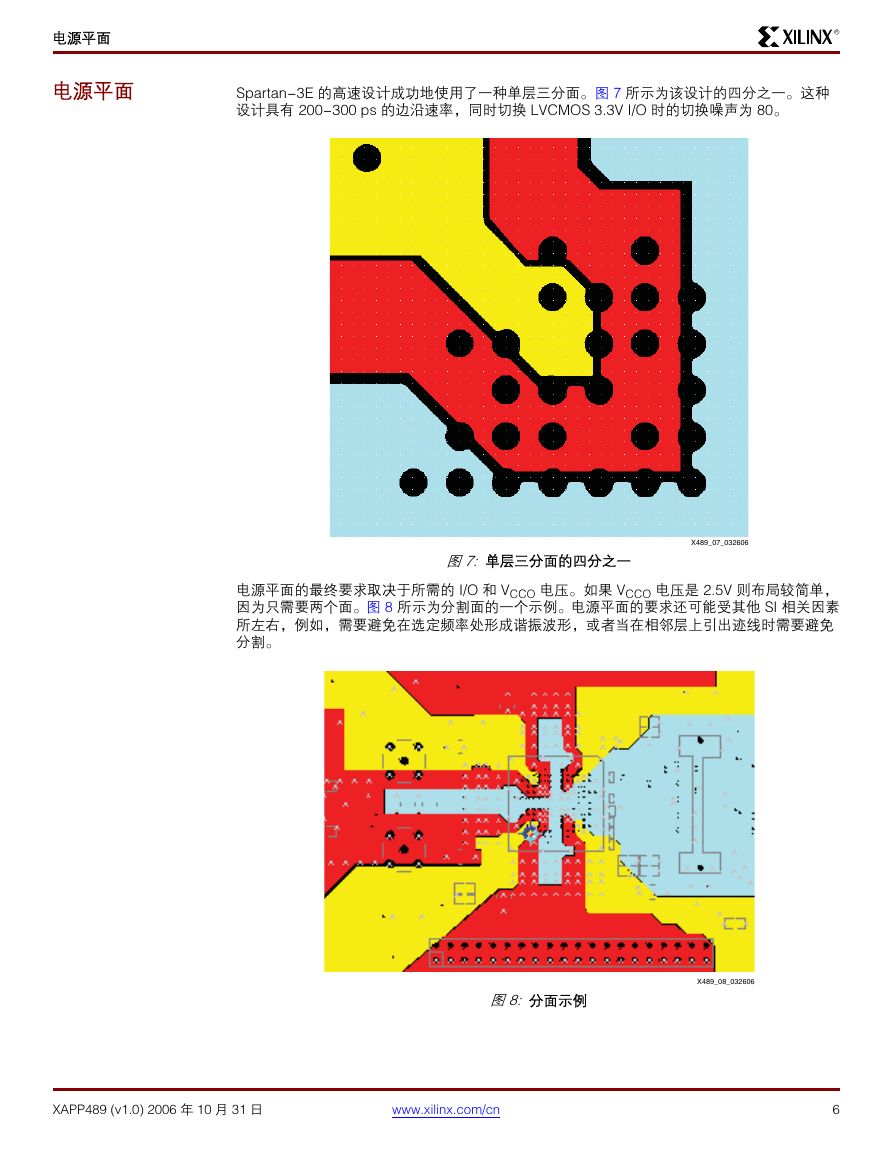

Spartan-3E 的高速设计成功地使用了一种单层三分面。图 7 所示为该设计的四分之一。这种

设计具有 200-300 ps 的边沿速率,同时切换 LVCMOS 3.3V I/O 时的切换噪声为 80。

R

图 7: 单层三分面的四分之一

X489_07_032606

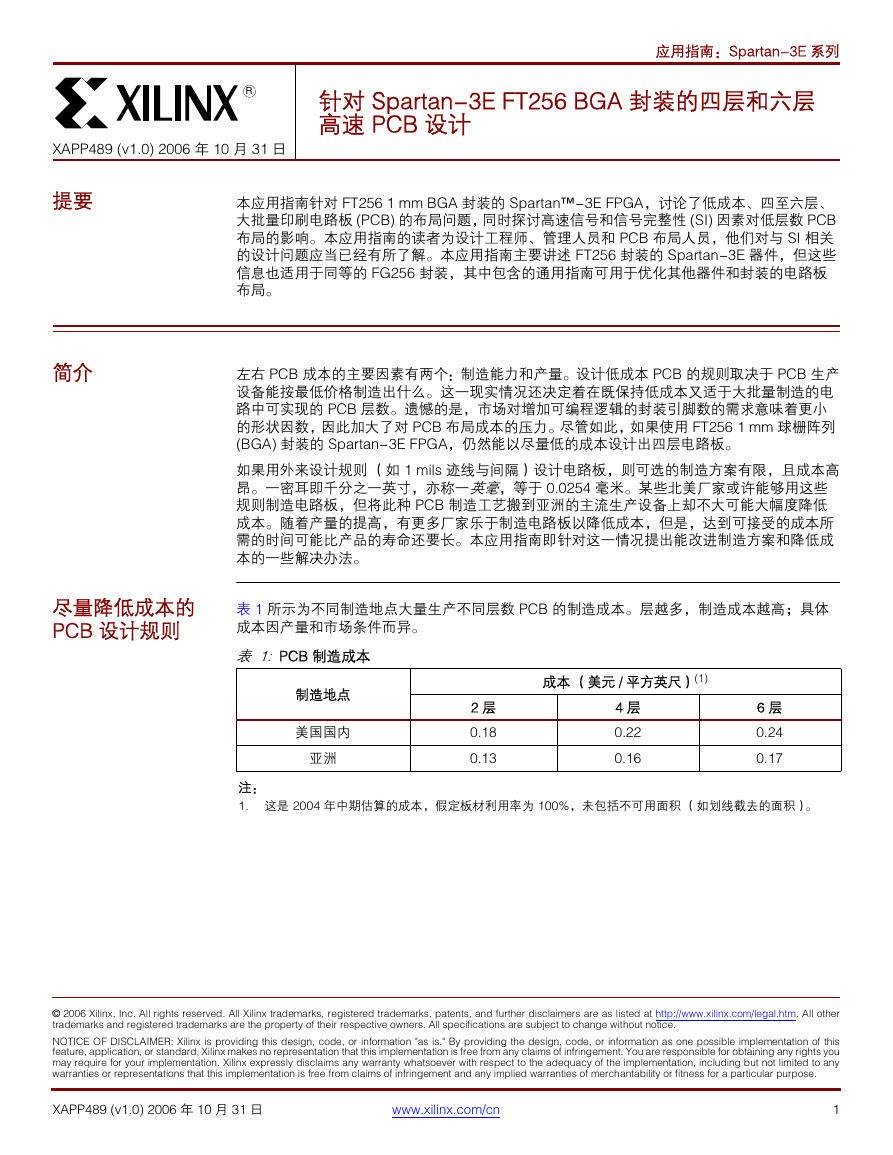

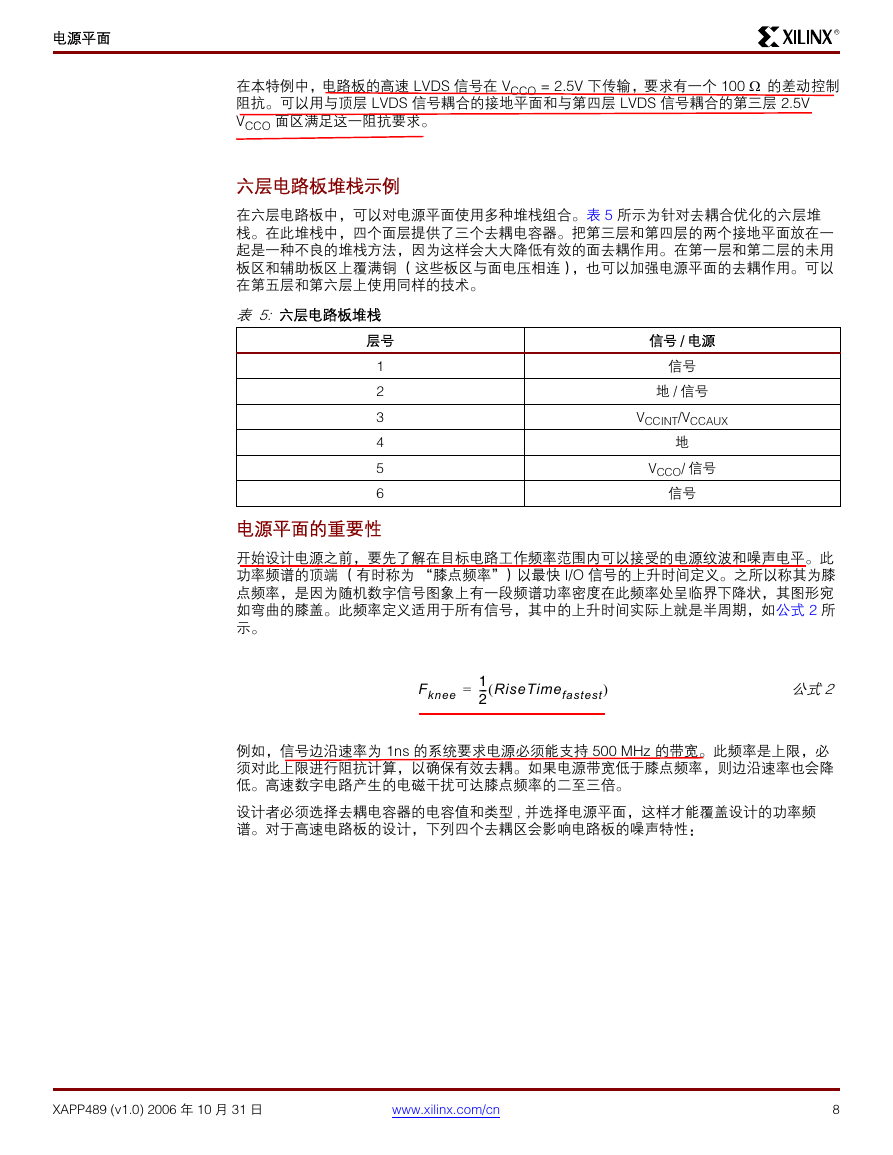

电源平面的最终要求取决于所需的 I/O 和 VCCO 电压。如果 VCCO 电压是 2.5V 则布局较简单,

因为只需要两个面。图 8 所示为分割面的一个示例。电源平面的要求还可能受其他 SI 相关因素

所左右,例如,需要避免在选定频率处形成谐振波形,或者当在相邻层上引出迹线时需要避免

分割。

图 8: 分面示例

X489_08_032606

XAPP489 (v1.0) 2006 年 10 月 31 日

www.xilinx.com/cn

6

�

电源平面

R

各面区应尽可能连续而无间断。在图 8 中,浅蓝色和红色面区显然是连续的。图 9 所示为电路

板的放大图,其中的黄色面区也可以看成是连续的。

图 9: 连续的黄色面区

X489_09_040306

图 10 所示为此电路板上所用的实心接地平面。

图 10: 接地平面

X489_10_040306

四层电路板堆栈示例

对于低成本四层电路板,可按表 4 所述对图 7 到图 10 所示的各电源平面进行堆栈操作。

表 4: 四层电路板堆栈

层号

1

2

3

4

信号 / 电源

信号

地

VCCINT/VCCAUX/VCCO

信号

XAPP489 (v1.0) 2006 年 10 月 31 日

www.xilinx.com/cn

7

�

电源平面

R

在本特例中,电路板的高速 LVDS 信号在 VCCO = 2.5V 下传输,要求有一个 100 Ω 的差动控制

阻抗。可以用与顶层 LVDS 信号耦合的接地平面和与第四层 LVDS 信号耦合的第三层 2.5V

VCCO 面区满足这一阻抗要求。

六层电路板堆栈示例

在六层电路板中,可以对电源平面使用多种堆栈组合。表 5 所示为针对去耦合优化的六层堆

栈。在此堆栈中,四个面层提供了三个去耦电容器。把第三层和第四层的两个接地平面放在一

起是一种不良的堆栈方法,因为这样会大大降低有效的面去耦作用。在第一层和第二层的未用

板区和辅助板区上覆满铜 (这些板区与面电压相连),也可以加强电源平面的去耦作用。可以

在第五层和第六层上使用同样的技术。

表 5: 六层电路板堆栈

层号

1

2

3

4

5

6

信号 / 电源

信号

地 / 信号

VCCINT/VCCAUX

地

VCCO/ 信号

信号

电源平面的重要性

开始设计电源之前,要先了解在目标电路工作频率范围内可以接受的电源纹波和噪声电平。此

功率频谱的顶端 (有时称为 “膝点频率”)以最快 I/O 信号的上升时间定义。之所以称其为膝

点频率,是因为随机数字信号图象上有一段频谱功率密度在此频率处呈临界下降状,其图形宛

如弯曲的膝盖。此频率定义适用于所有信号,其中的上升时间实际上就是半周期,如公式 2 所

示。

Fknee

=

1

--- RiseTimefastest

(

2

)

公式2

例如,信号边沿速率为 1ns 的系统要求电源必须能支持 500 MHz 的带宽。此频率是上限,必

须对此上限进行阻抗计算,以确保有效去耦。如果电源带宽低于膝点频率,则边沿速率也会降

低。高速数字电路产生的电磁干扰可达膝点频率的二至三倍。

设计者必须选择去耦电容器的电容值和类型 , 并选择电源平面,这样才能覆盖设计的功率频

谱。对于高速电路板的设计,下列四个去耦区会影响电路板的噪声特性:

XAPP489 (v1.0) 2006 年 10 月 31 日

www.xilinx.com/cn

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc