IPQ8064 Network Processor

Preliminary Device Specification

80-Y5080-3 Rev. B

December 19, 2013

Confidential and Proprietary – Qualcomm Atheros, Inc.

NO PUBLIC DISCLOSURE PERMITTED – Please report postings of this document on public servers or web

sites to: DocCtrlAgent@qualcomm.com.

Restricted Distribution: Not to be distributed to anyone who is not an employee of either Qualcomm or its

subsidiaries without the express approval of Qualcomm’s Configuration Management.

Not to be used, copied, reproduced, or modified in whole or in part, nor its contents revealed in any manner to others

without the express written permission of Qualcomm Atheros, Inc.

Qualcomm is a registered trademark of QUALCOMM Incorporated. Atheros is a registered trademark of Qualcomm

Atheros, Inc. All other registered and unregistered trademarks are the property of QUALCOMM Incorporated,

Qualcomm Atheros, Inc., or their respective owners and used with permission. Registered marks owned by

QUALCOMM Incorporated and Qualcomm Atheros, Inc. are registered in the United States and may be registered in

other countries. CDMA2000 is a registered trademark and/or certification mark of the Telecommunications Industry

Association (TIA-USA), used under license. ARM is a registered trademark of ARM Limited.

This technical data may be subject to U.S. and international export, re-export, or transfer (“export”) laws. Diversion

contrary to U.S. and international law is strictly prohibited.

Qualcomm Atheros, Inc.

1700 Technology Drive

San Jose, CA 95110

U.S.A.

© 2013 Qualcomm Atheros, Inc.

�

Revision history

Revision

Date

A

B

September 2013

December 2013

Description

Initial release

1. Remove unused MDIO and MDC signals from GPIO table.

2. Clarify the QFPROM footnote in the Power-On Sequence table.

3. PCIE1_CLK_REQ should be PCIE1_CLK_REQ_N

4. Add order number.

5. Add Electrical Specifications.

6. Remove Boot_Config option 00.

7. Specified the supported audio formats

80-Y5080-3 Rev. B

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Confidential and Proprietary – Qualcomm Atheros, Inc.

2

�

Contents

1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1

IPQ8064 introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

IPQ8064 features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.2

1.2.1 Architecture and processing units . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.2.2 Ethernet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.2.3 Dedicated peripheral interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.2.4 Programmable peripheral interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Terms and acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Special marks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.3

1.4

2.1

2.2

2.3

2 Pin Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

I/O parameter definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

IPQ8064 Pin map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.3.1 Power supply pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.3.2 Ground pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.3.3 No-connect and reserved pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.3.4 Clocks and reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.3.5 Memory support functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.3.6 PCI Express (PCIe) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.3.7 JTAG interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.3.8 QSGMII, SGMII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.3.9 RGMII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.3.10 Secure Digital Card (SDC1 and SDC3 Interfaces) . . . . . . . . . . . . . . . . . . . . . . 34

2.3.11 Sense Lines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.3.12 Serial ATA (SATA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.3.13 Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

2.3.14 USB 3.0/2.0 PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

2.3.15 USB HSIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.3.16 Pulse-code modulation (PCM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.3.17 Boot configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.3.18 EBI2 NAND flash interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

2.3.19 General Serial Bus Interface (GSBI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2.3.20 Multiple I2S interface (MI2S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

80-Y5080-3 Rev. B

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Confidential and Proprietary – Qualcomm Atheros, Inc.

3

�

IPQ8064 Network Processor Preliminary Device Specification

Contents

2.3.21 SPDIF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.3.22 Transport Stream Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.3.23 GPIO Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.2

3.3

Power sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4 Mechanical Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.1 Device physical dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.2

Part marking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

4.3 Device ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

4.4 Device moisture-sensitivity level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.5

Thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

80-Y5080-3 Rev. B

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Confidential and Proprietary – Qualcomm Atheros, Inc.

4

�

IPQ8064 Network Processor Preliminary Device Specification

Contents

Figures

Figure 1-1 IPQ8064 functional block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 4-1 Flip-chip package cut-away diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 4-2 19x19 mm package details (top and side views) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 4-3 19x19 mm package details (bottom view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 4-4 IPQ8064 marking (top view, not to scale) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 4-5 Device identification code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

80-Y5080-3 Rev. B

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Confidential and Proprietary – Qualcomm Atheros, Inc.

5

�

IPQ8064 Network Processor Preliminary Device Specification

Contents

Tables

Table 1-1 GMAC configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 1-2 Terms and acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 1-3 Special marks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2-1 I/O description (pad type) parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 2-2 IPQ8064 BGA519 Pin assignments (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 2-3 IPQ8064 BGA519 Pin assignments (upper left quadrant) . . . . . . . . . . . . . . . . . . . . . 20

Table 2-4 IPQ8064 BGA519 Pin assignments (upper right quadrant) . . . . . . . . . . . . . . . . . . . . 21

Table 2-5 IPQ8064 BGA519 Pin assignments (lower left quadrant) . . . . . . . . . . . . . . . . . . . . . 22

Table 2-6 IPQ8064 BGA519 Pin assignments (lower right quadrant) . . . . . . . . . . . . . . . . . . . . 23

Table 2-7 Power supply pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 2-8 Ground pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 2-9 No-connect and reserved pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 2-10 Clocks and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 2-11 PCDDR3 External Bus Interface Channel 0 (2 CS) . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 2-12 PCI Express (PCIe) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 2-13 PCIe test clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 2-14 PCIe Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 2-15 PCIe hot-plug signals and GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 2-16 Primary JTAG Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 2-17 GMAC configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 2-18 QSGMII, SGMII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 2-19 RGMII (dedicated 2.5 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 2-20 RGMII2 (muxed 1.8 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 2-21 Secure Digital Card 1 (SDC1) Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 2-22 Secure Digital Card 3 (SDC3) Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 2-23 Sense Lines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 2-24 Serial ATA (SATA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 2-25 SATA test clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 2-26 Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 2-27 USB 3.0/2.0 PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 2-28 USB test clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 2-29 USB HSIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 2-30 PCM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 2-31 Boot configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 2-32 Fast boot device selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 2-33 EBI2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 2-34 GSBI Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 2-35 General Serial Bus Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 2-36 MI2S . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 2-37 SPDIF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 2-38 Transport Stream Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

80-Y5080-3 Rev. B

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Confidential and Proprietary – Qualcomm Atheros, Inc.

6

�

IPQ8064 Network Processor Preliminary Device Specification

Contents

Table 2-39 GPIO Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 3-1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 3-2 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 3-3 PVS for VDDC_APC* . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 3-4 Power-on sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 4-1 19x19 mm package notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 4-2 IPQ8064 marking line definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 4-3 Thermal Resistance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

80-Y5080-3 Rev. B

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Confidential and Proprietary – Qualcomm Atheros, Inc.

7

�

1 Introduction

1.1 IPQ8064 introduction

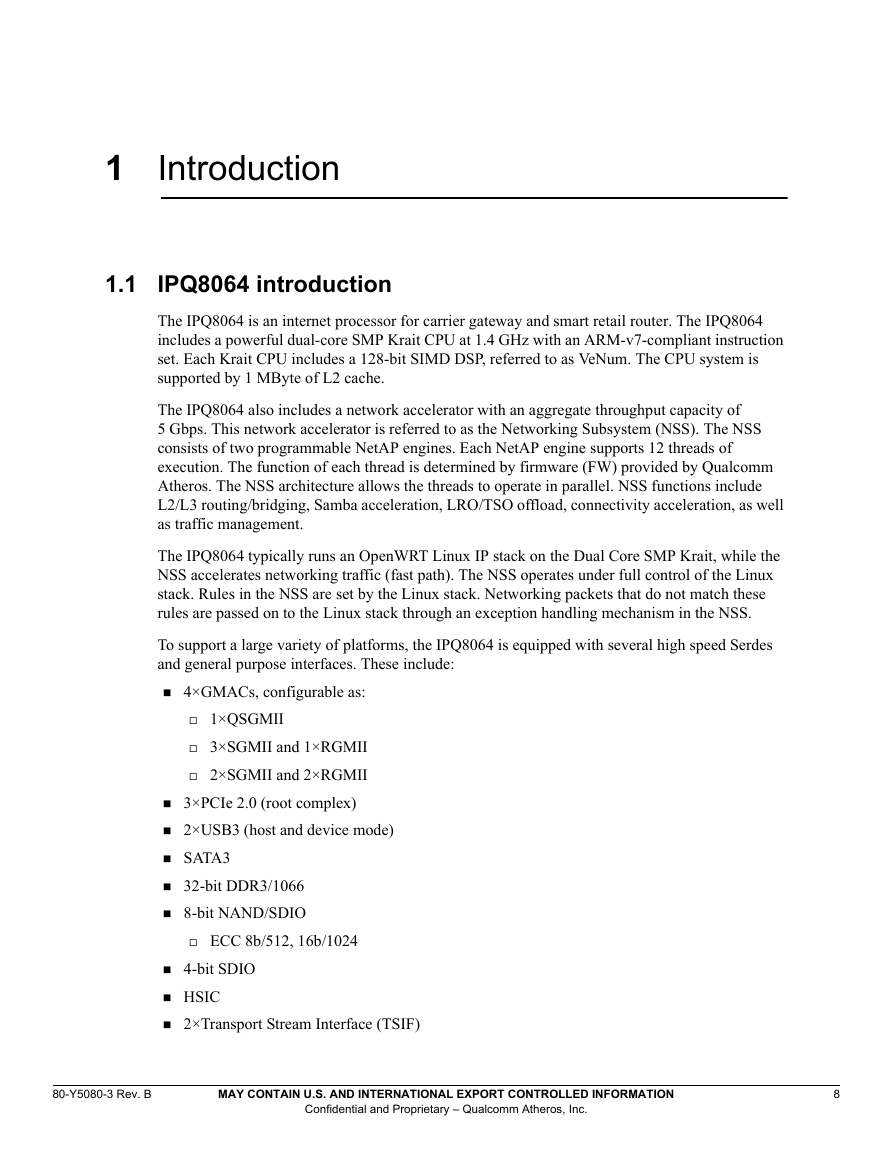

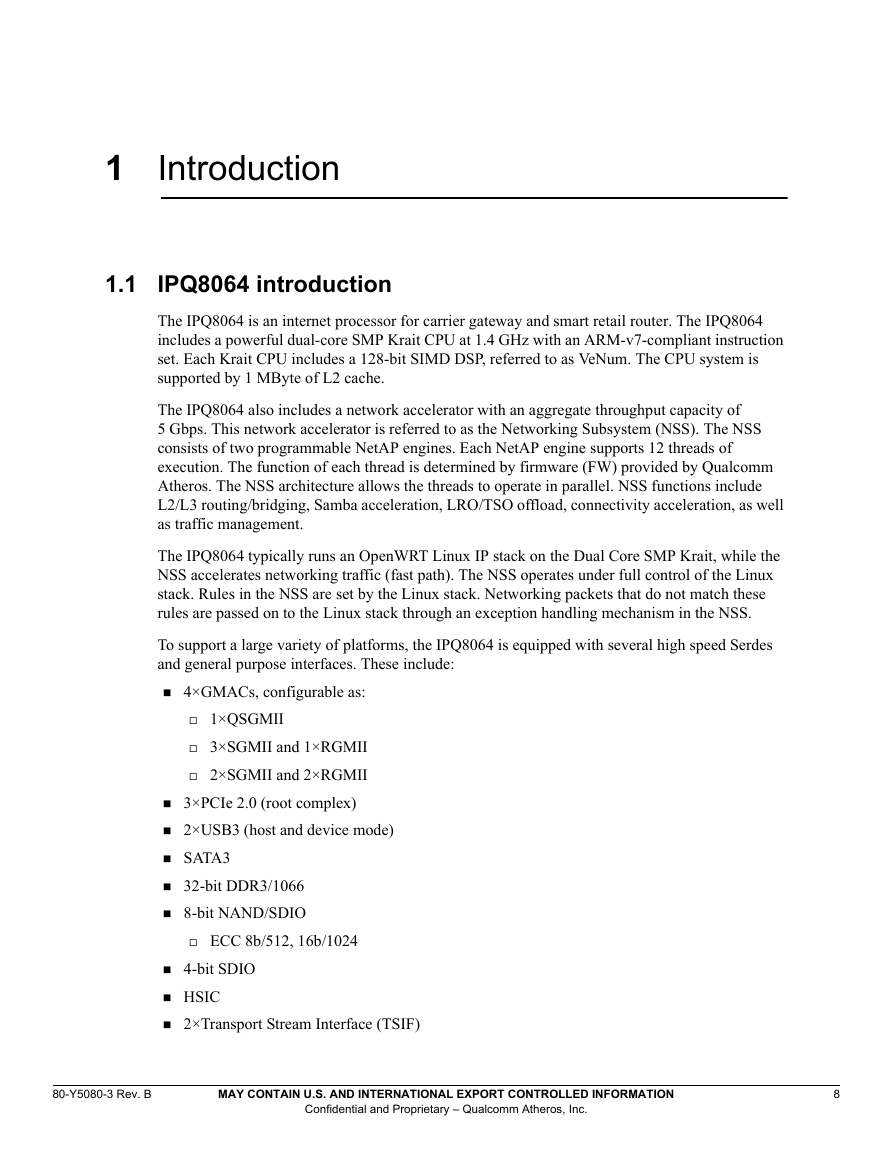

The IPQ8064 is an internet processor for carrier gateway and smart retail router. The IPQ8064

includes a powerful dual-core SMP Krait CPU at 1.4 GHz with an ARM-v7-compliant instruction

set. Each Krait CPU includes a 128-bit SIMD DSP, referred to as VeNum. The CPU system is

supported by 1 MByte of L2 cache.

The IPQ8064 also includes a network accelerator with an aggregate throughput capacity of

5 Gbps. This network accelerator is referred to as the Networking Subsystem (NSS). The NSS

consists of two programmable NetAP engines. Each NetAP engine supports 12 threads of

execution. The function of each thread is determined by firmware (FW) provided by Qualcomm

Atheros. The NSS architecture allows the threads to operate in parallel. NSS functions include

L2/L3 routing/bridging, Samba acceleration, LRO/TSO offload, connectivity acceleration, as well

as traffic management.

The IPQ8064 typically runs an OpenWRT Linux IP stack on the Dual Core SMP Krait, while the

NSS accelerates networking traffic (fast path). The NSS operates under full control of the Linux

stack. Rules in the NSS are set by the Linux stack. Networking packets that do not match these

rules are passed on to the Linux stack through an exception handling mechanism in the NSS.

To support a large variety of platforms, the IPQ8064 is equipped with several high speed Serdes

and general purpose interfaces. These include:

4×GMACs, configurable as:

1×QSGMII

3×SGMII and 1×RGMII

2×SGMII and 2×RGMII

3×PCIe 2.0 (root complex)

2×USB3 (host and device mode)

SATA3

32-bit DDR3/1066

8-bit NAND/SDIO

ECC 8b/512, 16b/1024

4-bit SDIO

HSIC

2×Transport Stream Interface (TSIF)

80-Y5080-3 Rev. B

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Confidential and Proprietary – Qualcomm Atheros, Inc.

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc