www.hkaco.com 虹科电子科技有限公司

ETHERCAT 从站开发指导-含软件和硬件选型介绍

第一节:EtherCAT 基本概念

第二节:如何选择硬件方案(以伺服驱动器为例)

第三节:如何选择软件代码

第一节 EtherCAT 基本概念

EtherCAT 一般设计要求(针对 uC+ESC 的方案):

硬件上:主控制器 uC+ESC(可选各供应商的 EtherCAT 从站控制器)

操作系统:无特殊要求,根据产品性能决定,也可以不用操作系统

软件上:需要完成主控制器 uC 对 EtherCAT 报文的通讯,ESC 一般带开发包可完成移植。

难点:如何实现 uC 与 ESC 之间的数据交互。

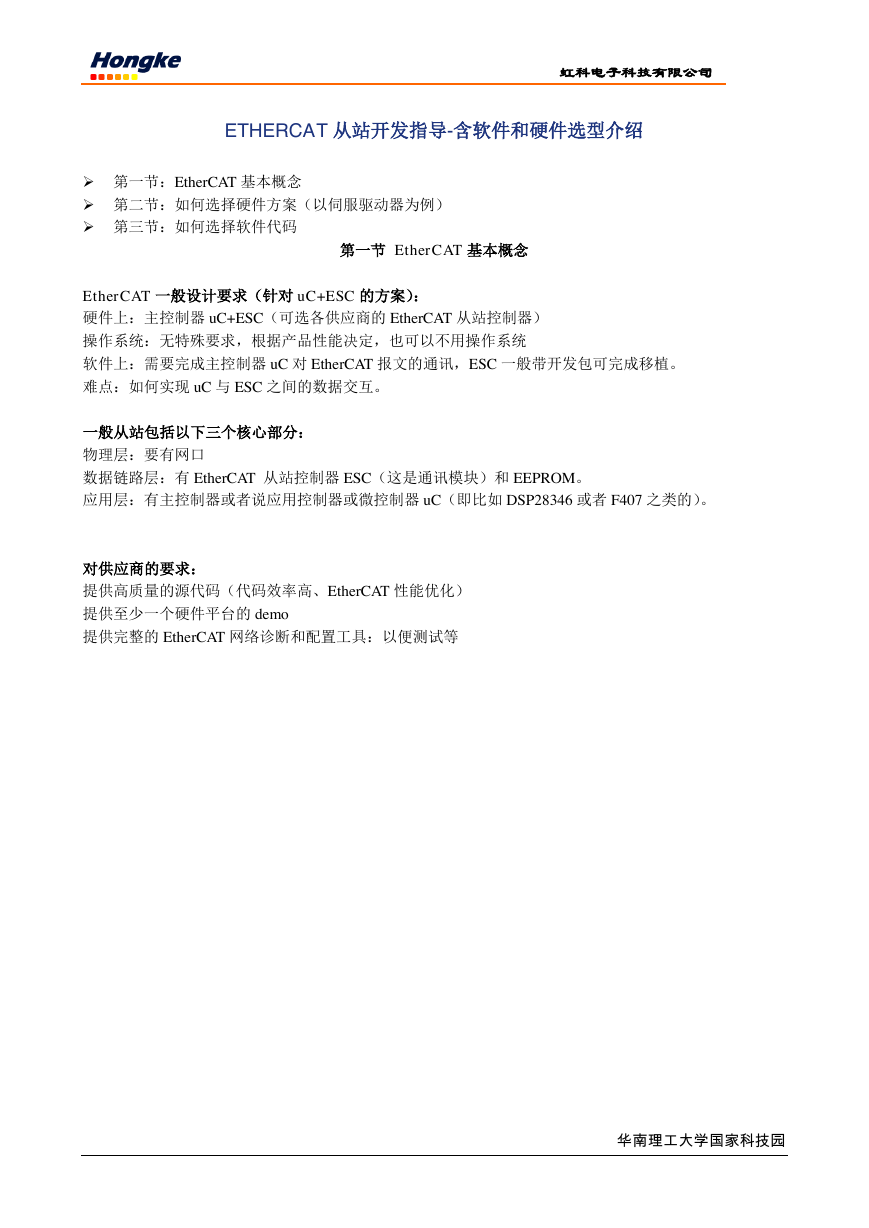

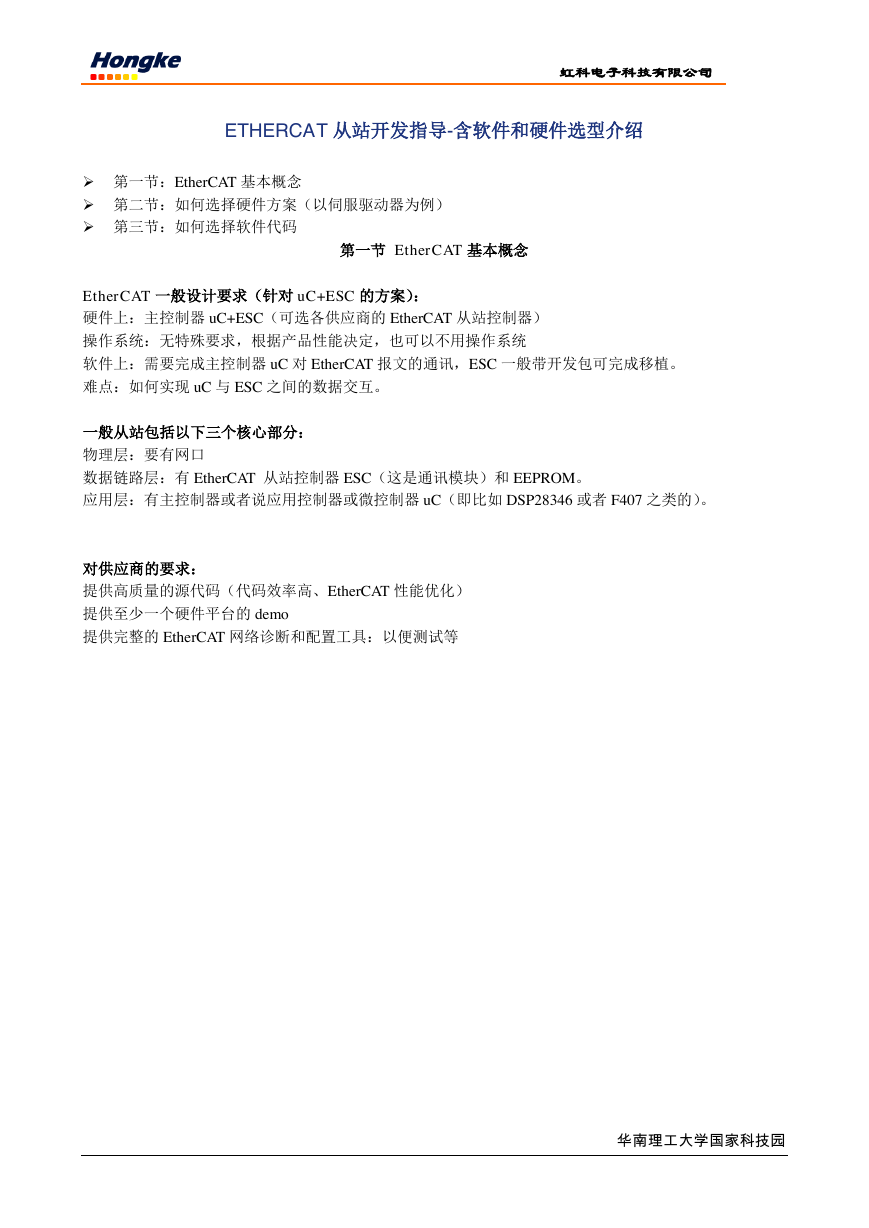

一般从站包括以下三个核心部分:

物理层:要有网口

数据链路层:有 EtherCAT 从站控制器 ESC(这是通讯模块)和 EEPROM。

应用层:有主控制器或者说应用控制器或微控制器 uC(即比如 DSP28346 或者 F407 之类的)。

对供应商的要求:

提供高质量的源代码(代码效率高、EtherCAT 性能优化)

提供至少一个硬件平台的 demo

提供完整的 EtherCAT 网络诊断和配置工具:以便测试等

华南理工大学国家科技园

�

www.hkaco.com 虹科电子科技有限公司

ESC 即 EtherCAT 从站控制器可以通过 FPGA(Field Programmable Gate Array)或者 ASIC (Application Specific

Integrated Circuit)来完成。

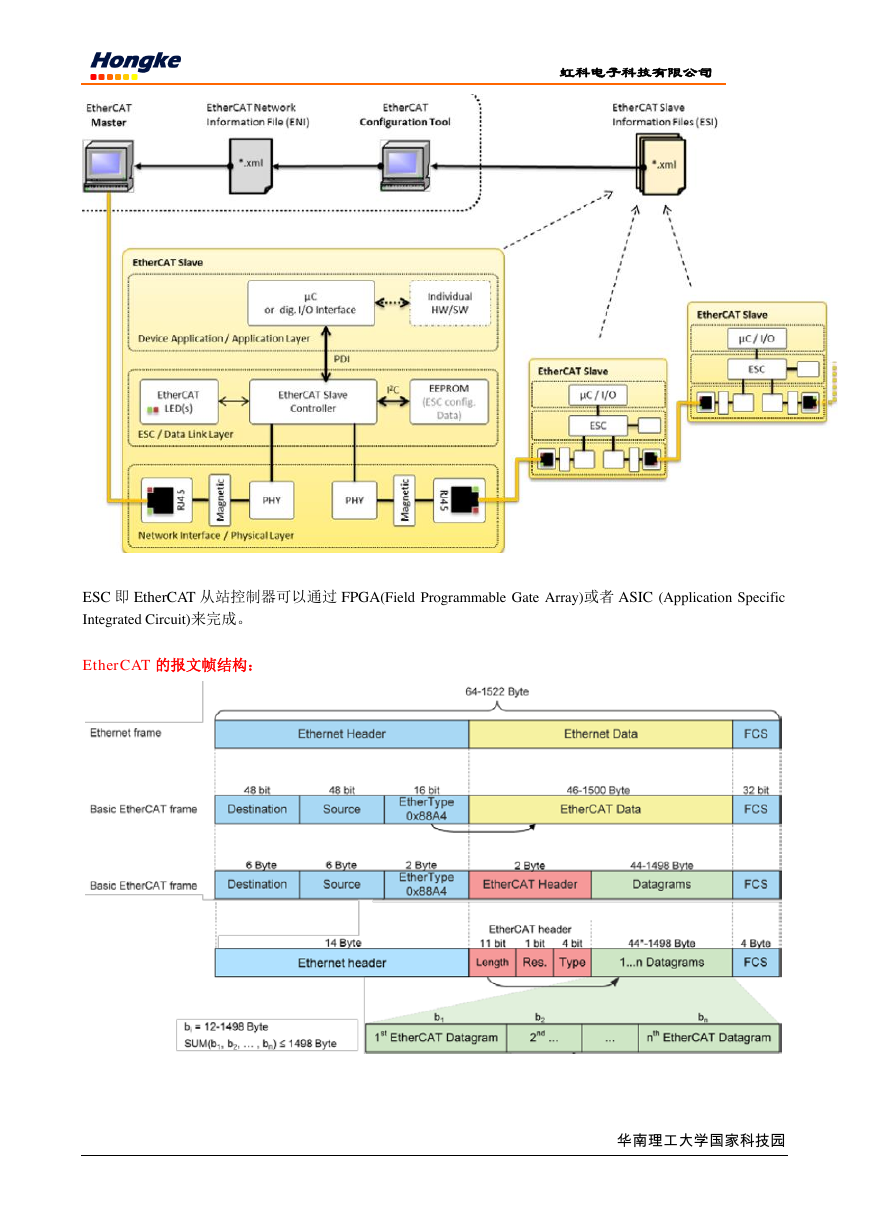

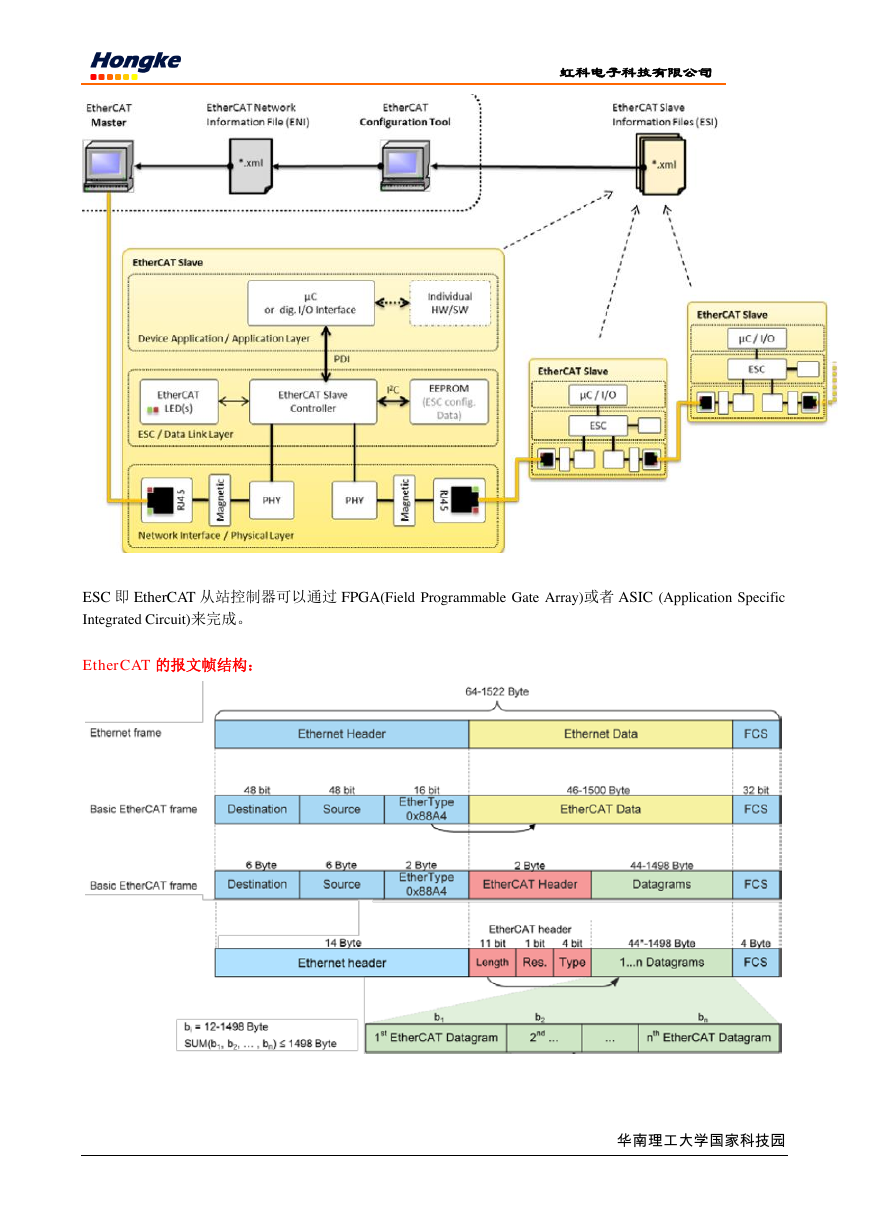

EtherCAT 的报文帧结构:

华南理工大学国家科技园

�

www.hkaco.com 虹科电子科技有限公司

ESC 即 EtherCAT 从站控制器可以通过 FPGA(Field Programmable Gate Array)或者 ASIC (Application Specific

Integrated Circuit)来完成。

EtherCAT 通讯的速度和性能 与 主控制器(比如 DSP28346)软件程序的性能 互不影响。

关于 PDI:ESC 上的 PDI- Process Data Interface 过程数据接口有这几种情况:

i. Up to 32 Bit digital I/O :32 位的数字量 IO

ii. Serial Peripheral Interface (SPI) :SPI 总线

iii. 8/16-bit synchronous/asynchronous Microcontroller Interface (MCI) :8/16 位的同步/异步微控制器接口

MCI

iv. With FPGA: specific on-board-bus (Avalon on Altera devices resp. OPB on Xilinx devices) :带 FPGA 的:特

定的 on-board-bus

过程数据和参数是通过 ESC 上的 DPRAM 来交互的。为了保证数据的一致性,ESC 硬件上会有一些机制:

比如同步管理器等。

关于 IP 核:从站 IP 核也是属于 ESC 的一种形态,也相当于是 ESC 的一种,可以理解为 IP 核只是替代了

ET1100/ET1200。IP 核的功能还是实现了一个从站控制器,处理数据链路,同步事件等硬件事件。就算使

用了 IP 核来实现 ESC,这也仅仅实现了硬件的接口功能,软件协议并没有加载。还是需要 KPA 协议栈来

完成从站协议。

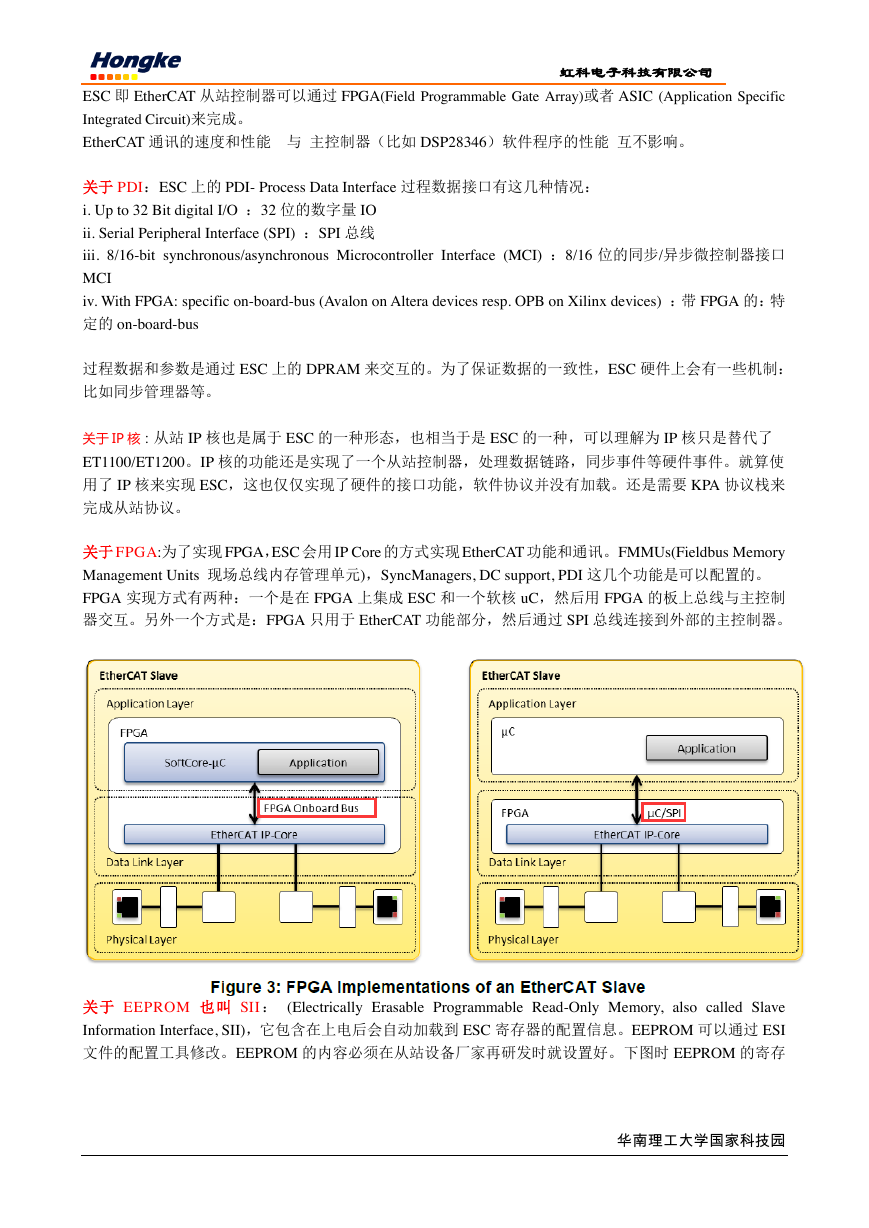

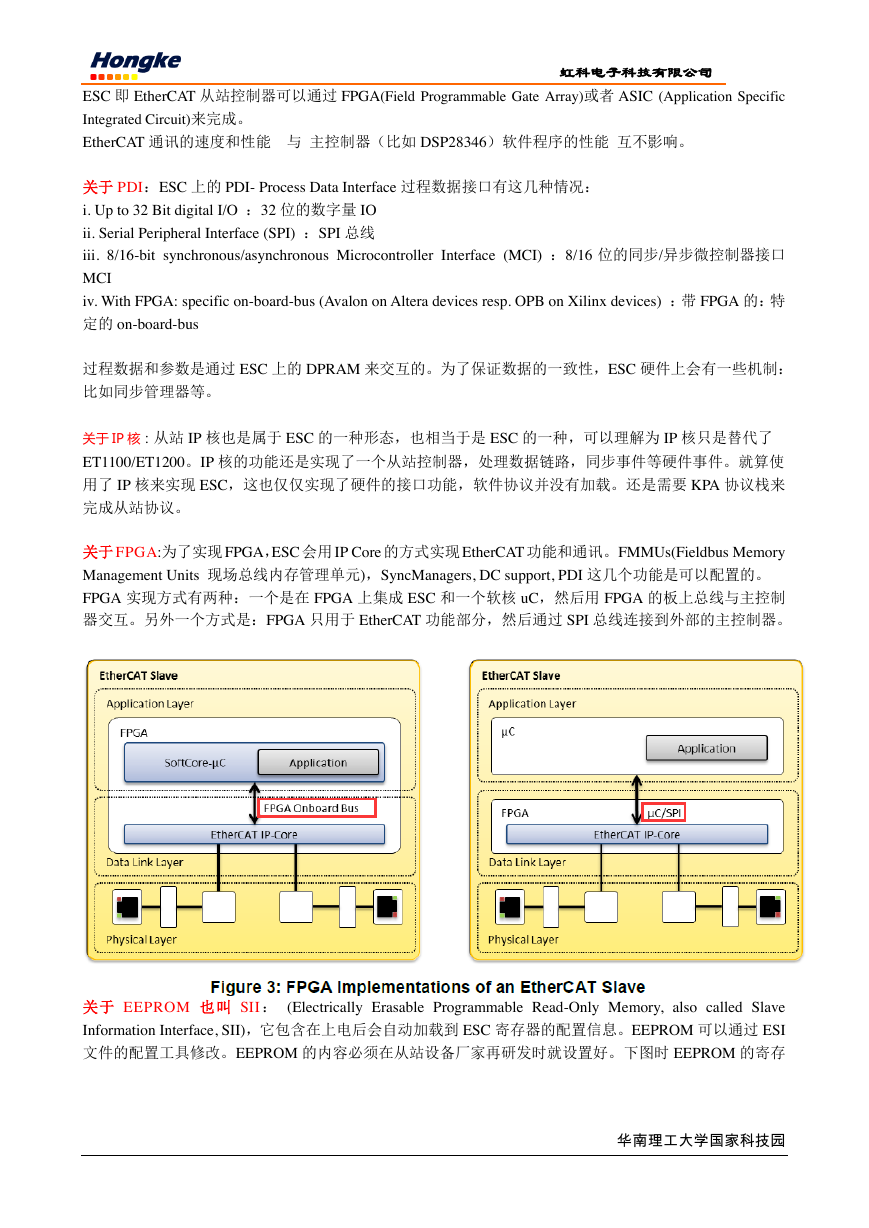

关于 FPGA:为了实现 FPGA,ESC 会用 IP Core 的方式实现 EtherCAT 功能和通讯。 FMMUs(Fieldbus Memory

Management Units 现场总线内存管理单元),SyncManagers, DC support, PDI 这几个功能是可以配置的。

FPGA 实现方式有两种:一个是在 FPGA 上集成 ESC 和一个软核 uC,然后用 FPGA 的板上总线与主控制

器交互。另外一个方式是:FPGA 只用于 EtherCAT 功能部分,然后通过 SPI 总线连接到外部的主控制器。

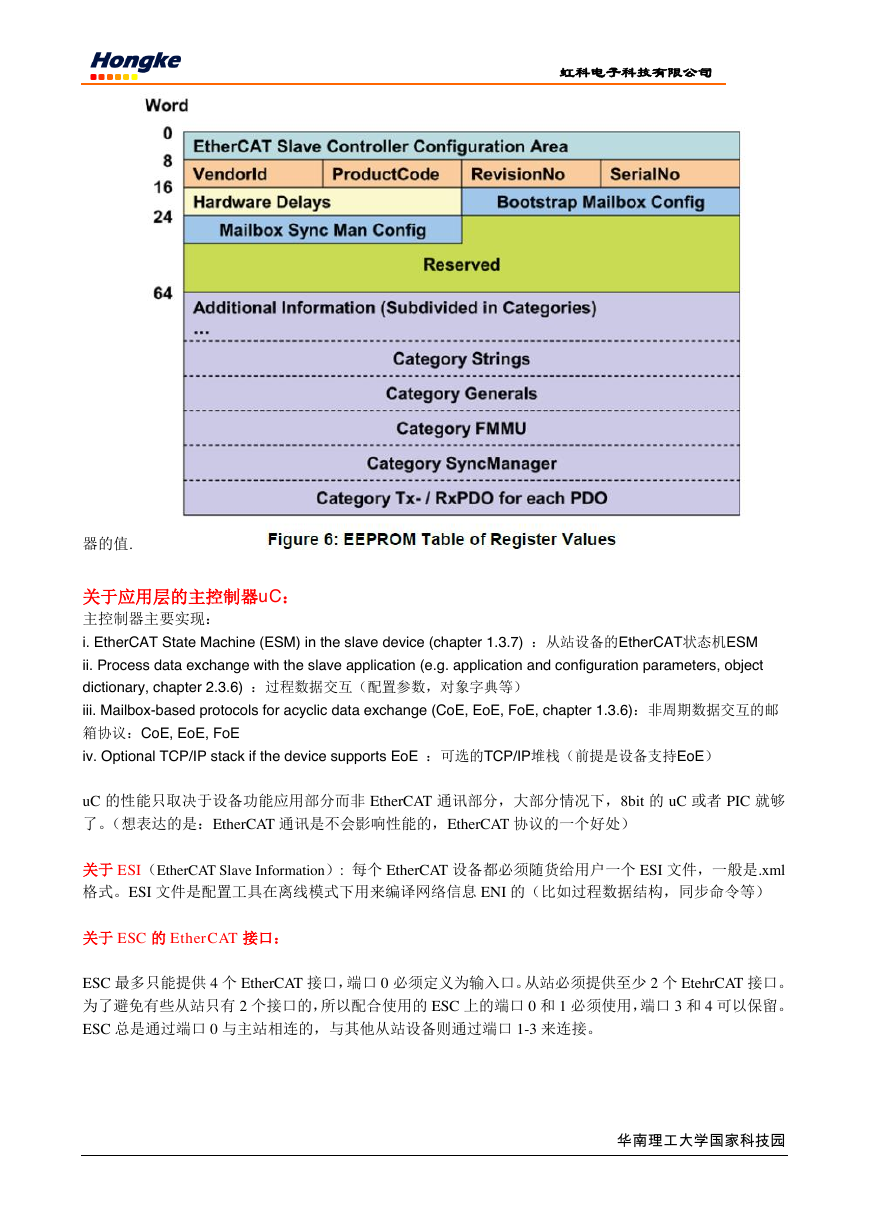

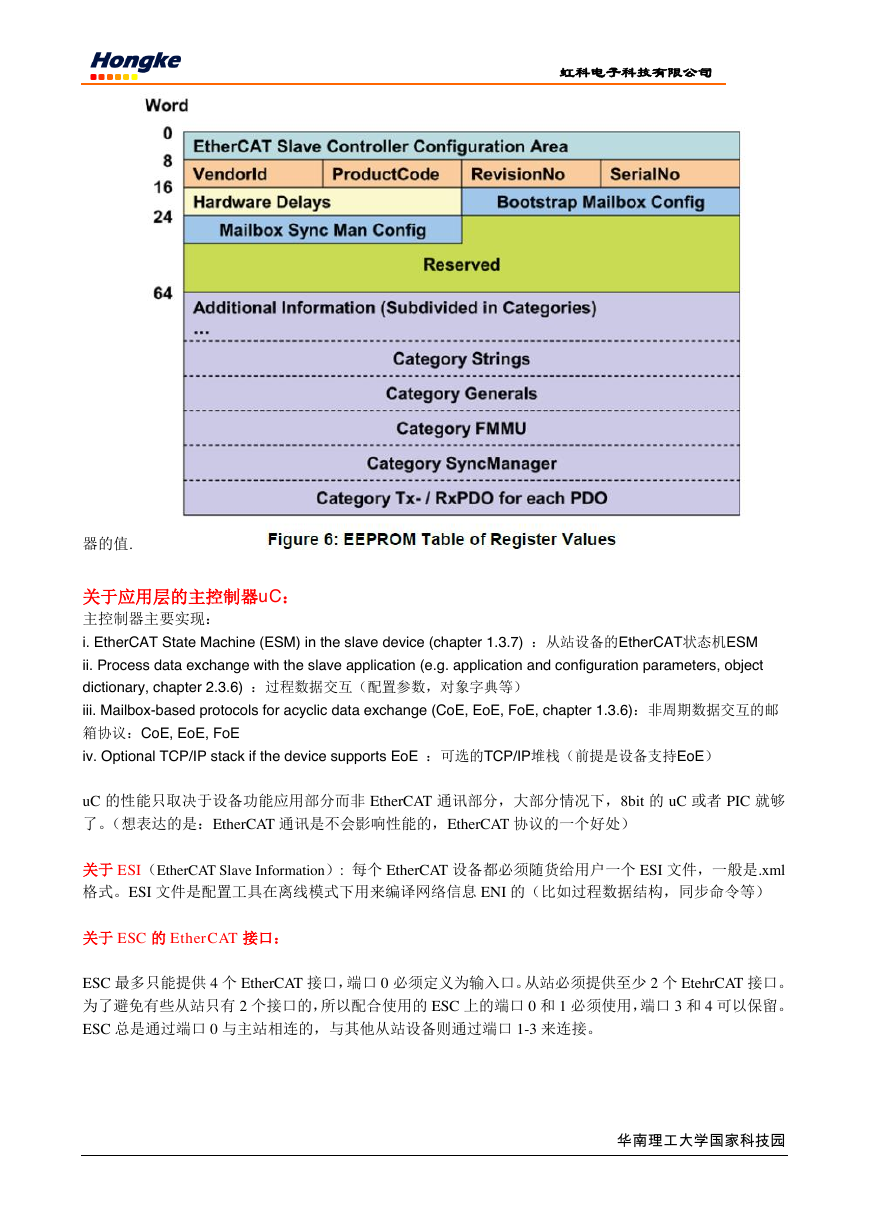

关于 EEPROM 也叫 SII: (Electrically Erasable Programmable Read-Only Memory, also called Slave

Information Interface, SII),它包含在上电后会自动加载到 ESC 寄存器的配置信息。EEPROM 可以通过 ESI

文件的配置工具修改。EEPROM 的内容必须在从站设备厂家再研发时就设置好。下图时 EEPROM 的寄存

华南理工大学国家科技园

�

www.hkaco.com 虹科电子科技有限公司

器的值.

关于应用层的主控制器uC:

主控制器主要实现:

i. EtherCAT State Machine (ESM) in the slave device (chapter 1.3.7) :从站设备的EtherCAT状态机ESM

ii. Process data exchange with the slave application (e.g. application and configuration parameters, object

dictionary, chapter 2.3.6) :过程数据交互(配置参数,对象字典等)

iii. Mailbox-based protocols for acyclic data exchange (CoE, EoE, FoE, chapter 1.3.6):非周期数据交互的邮

箱协议:CoE, EoE, FoE

iv. Optional TCP/IP stack if the device supports EoE :可选的TCP/IP堆栈(前提是设备支持EoE)

uC 的性能只取决于设备功能应用部分而非 EtherCAT 通讯部分,大部分情况下,8bit 的 uC 或者 PIC 就够

了。(想表达的是:EtherCAT 通讯是不会影响性能的,EtherCAT 协议的一个好处)

关于 ESI(EtherCAT Slave Information): 每个 EtherCAT 设备都必须随货给用户一个 ESI 文件,一般是.xml

格式。ESI 文件是配置工具在离线模式下用来编译网络信息 ENI 的(比如过程数据结构,同步命令等)

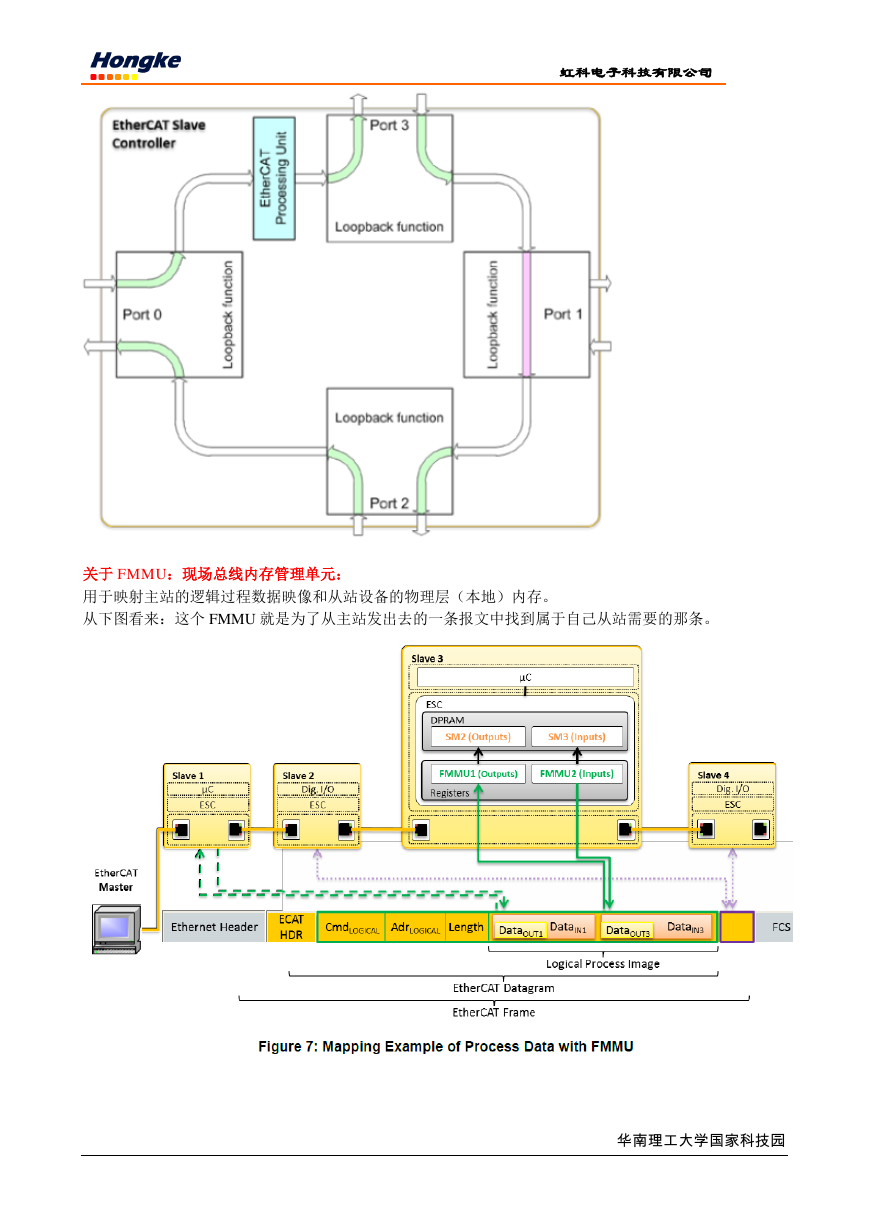

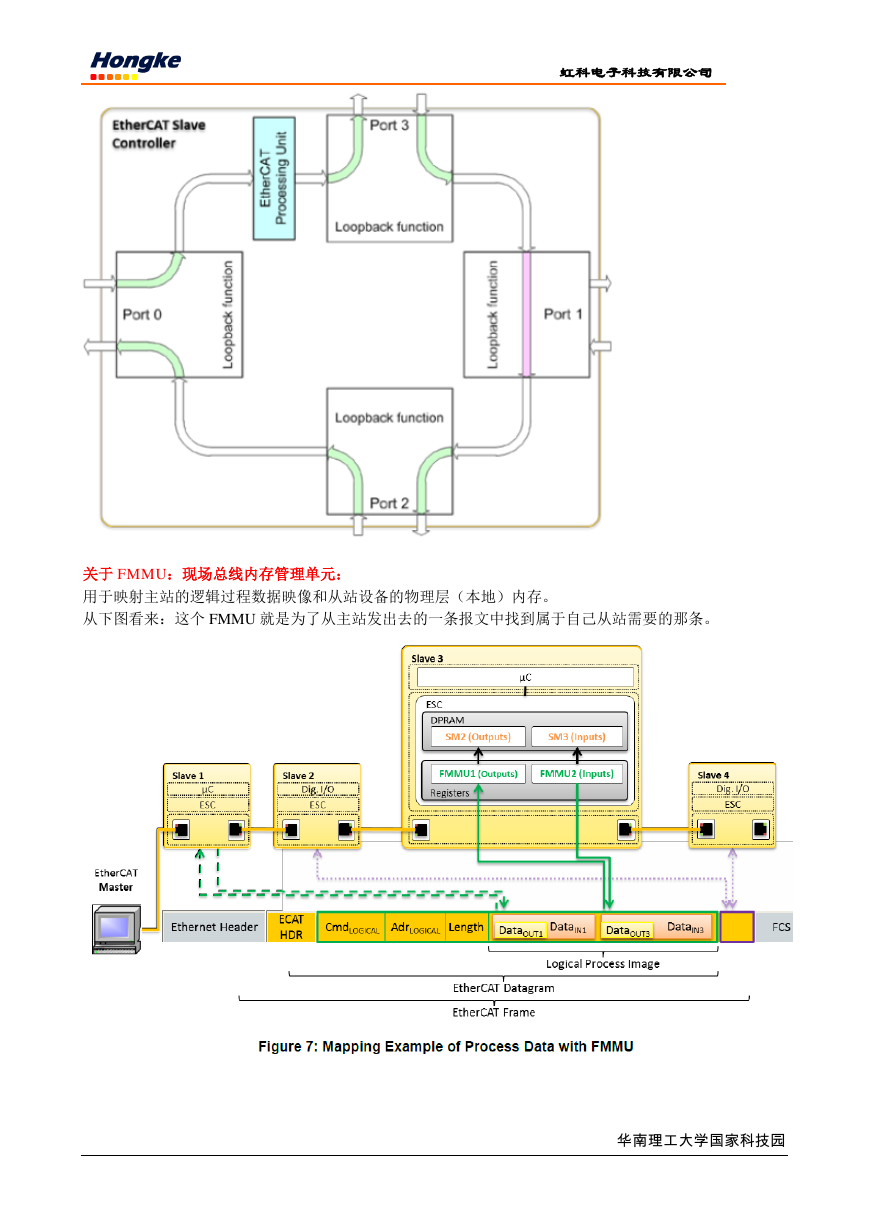

关于 ESC 的 EtherCAT 接口:

ESC 最多只能提供 4 个 EtherCAT 接口,端口 0 必须定义为输入口。从站必须提供至少 2 个 EtehrCAT 接口。

为了避免有些从站只有 2 个接口的,所以配合使用的 ESC 上的端口 0 和 1 必须使用,端口 3 和 4 可以保留。

ESC 总是通过端口 0 与主站相连的,与其他从站设备则通过端口 1-3 来连接。

华南理工大学国家科技园

�

www.hkaco.com 虹科电子科技有限公司

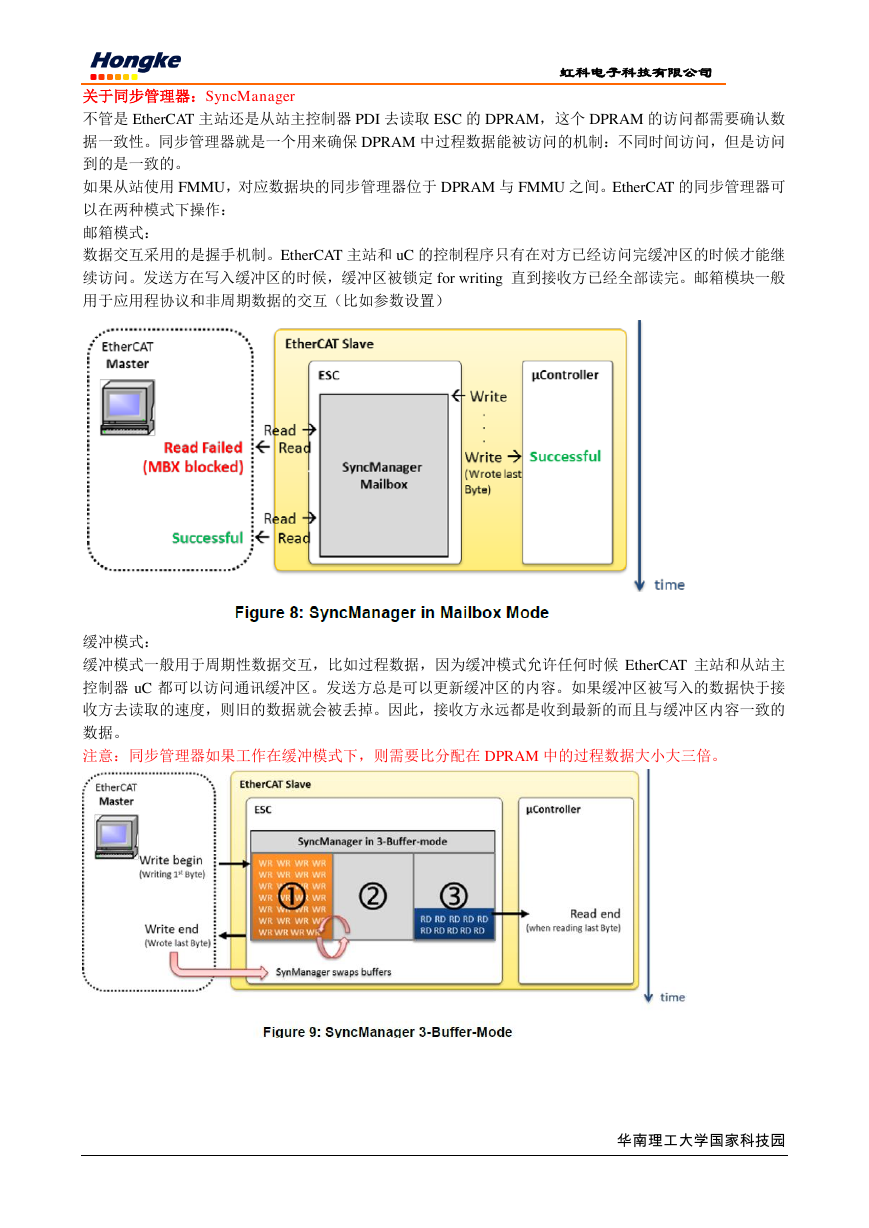

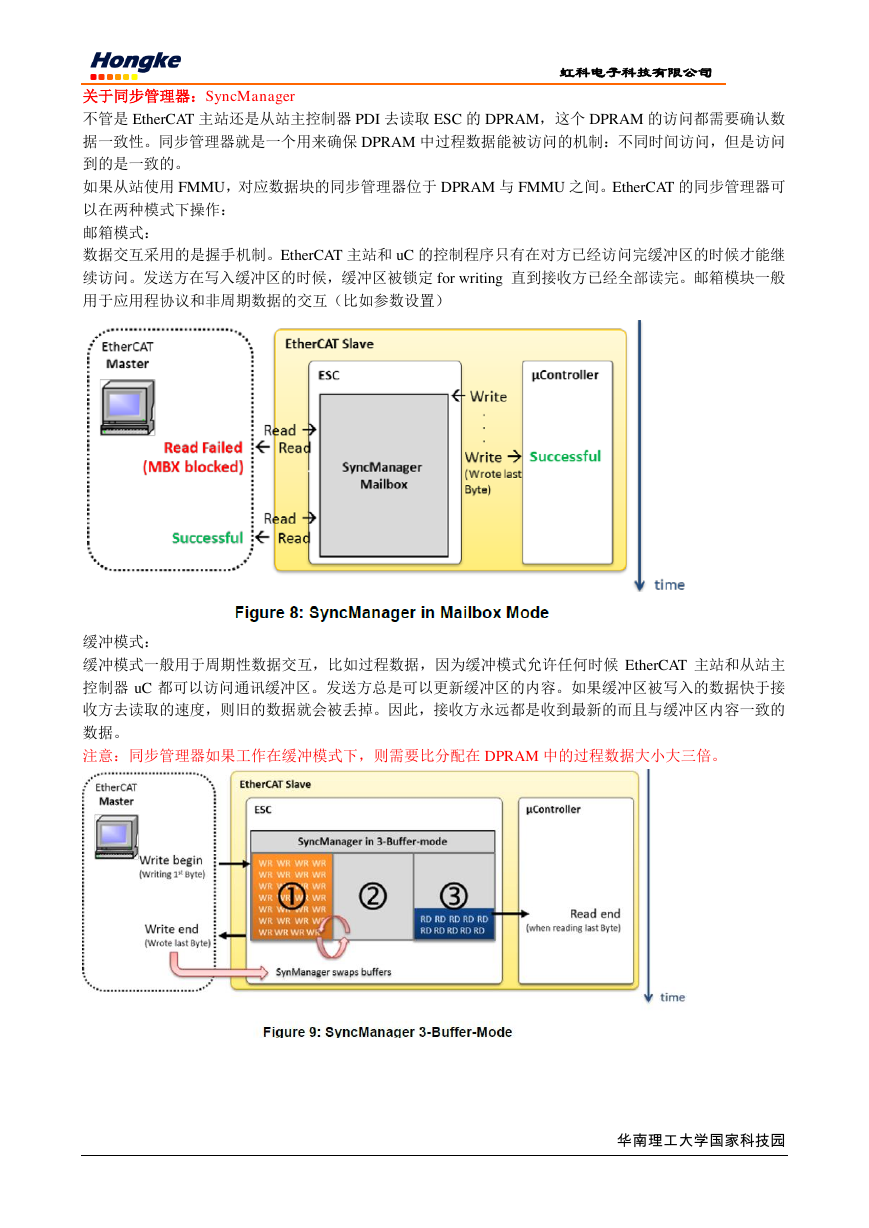

关于 FMMU:现场总线内存管理单元:

用于映射主站的逻辑过程数据映像和从站设备的物理层(本地)内存。

从下图看来:这个 FMMU 就是为了从主站发出去的一条报文中找到属于自己从站需要的那条。

华南理工大学国家科技园

�

www.hkaco.com 虹科电子科技有限公司

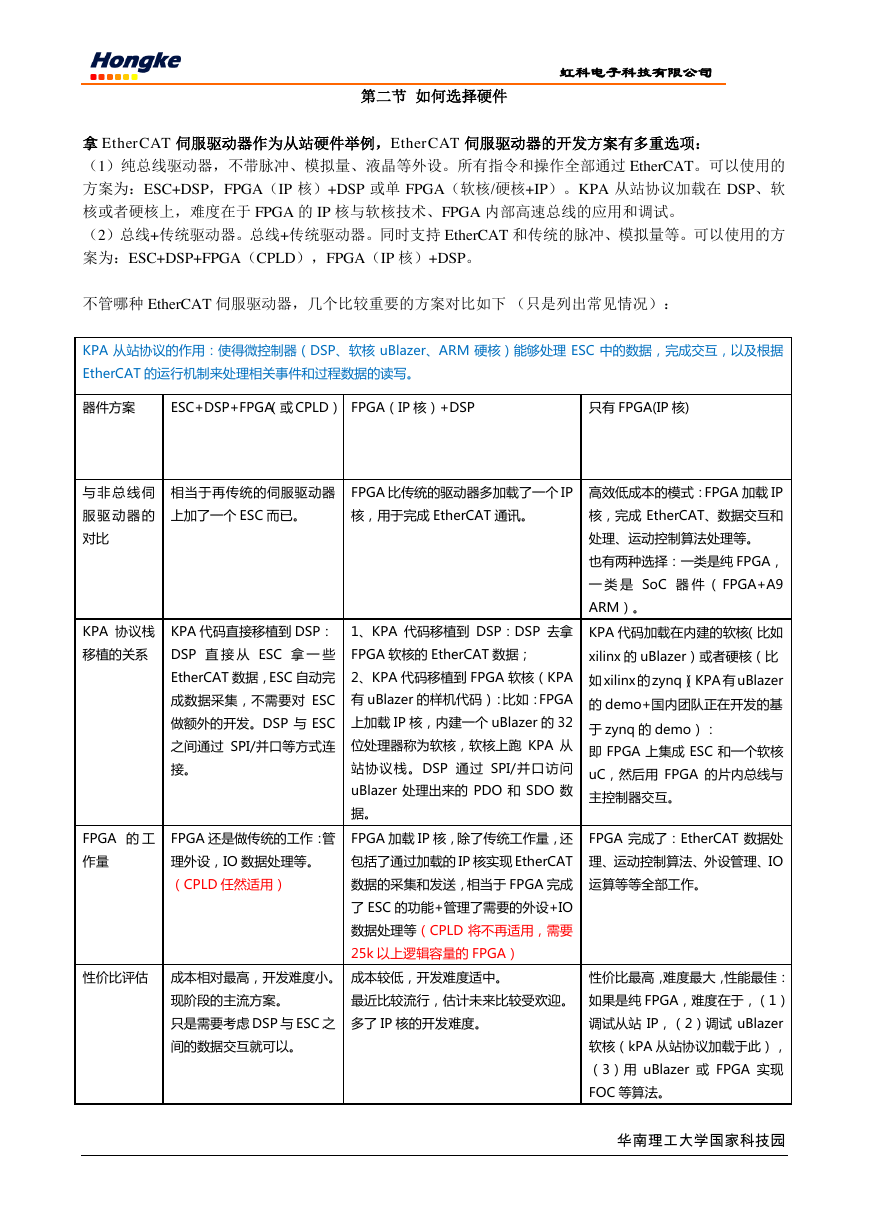

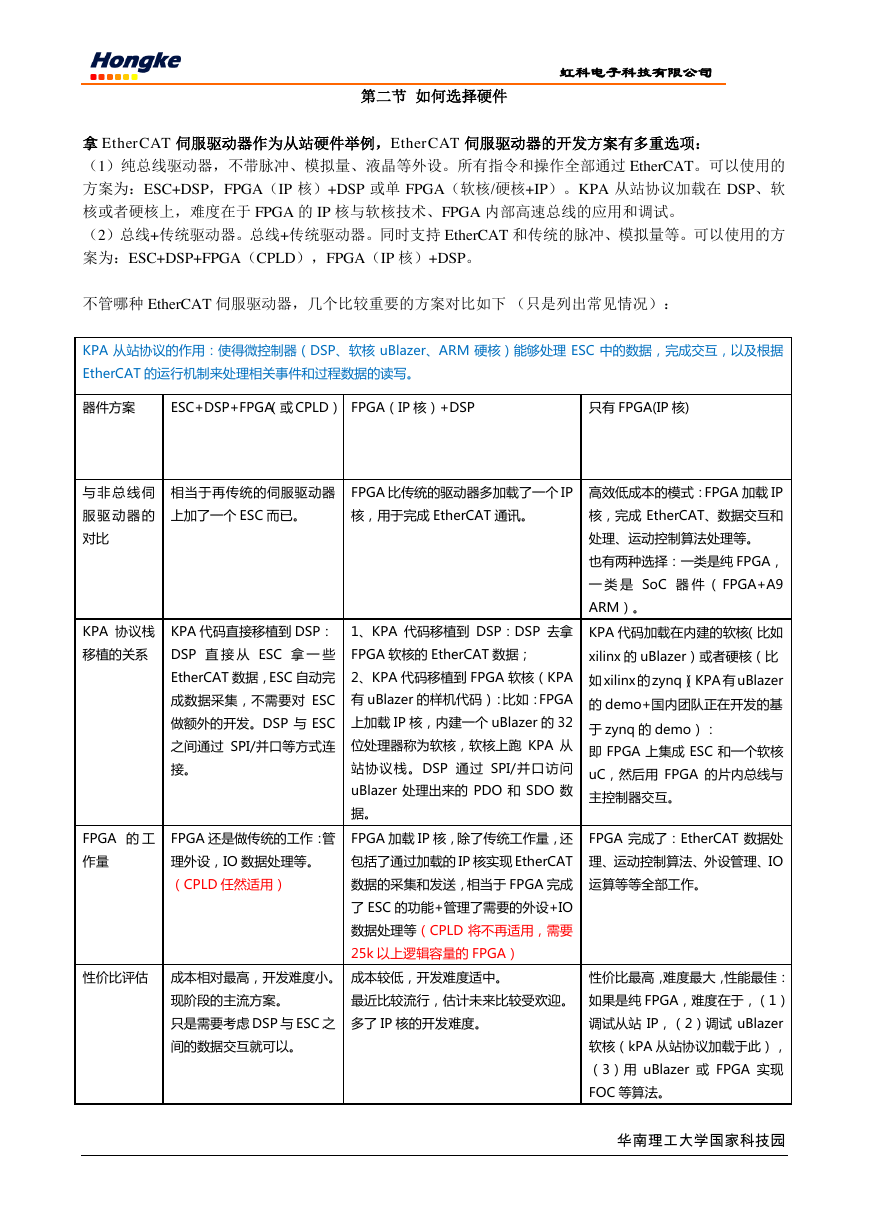

关于同步管理器:SyncManager

不管是 EtherCAT 主站还是从站主控制器 PDI 去读取 ESC 的 DPRAM,这个 DPRAM 的访问都需要确认数

据一致性。同步管理器就是一个用来确保 DPRAM 中过程数据能被访问的机制:不同时间访问,但是访问

到的是一致的。

如果从站使用 FMMU,对应数据块的同步管理器位于 DPRAM 与 FMMU 之间。EtherCAT 的同步管理器可

以在两种模式下操作:

邮箱模式:

数据交互采用的是握手机制。EtherCAT 主站和 uC 的控制程序只有在对方已经访问完缓冲区的时候才能继

续访问。发送方在写入缓冲区的时候,缓冲区被锁定 for writing 直到接收方已经全部读完。邮箱模块一般

用于应用程协议和非周期数据的交互(比如参数设置)

缓冲模式:

缓冲模式一般用于周期性数据交互,比如过程数据,因为缓冲模式允许任何时候 EtherCAT 主站和从站主

控制器 uC 都可以访问通讯缓冲区。发送方总是可以更新缓冲区的内容。如果缓冲区被写入的数据快于接

收方去读取的速度,则旧的数据就会被丢掉。因此,接收方永远都是收到最新的而且与缓冲区内容一致的

数据。

注意:同步管理器如果工作在缓冲模式下,则需要比分配在 DPRAM 中的过程数据大小大三倍。

华南理工大学国家科技园

�

www.hkaco.com 虹科电子科技有限公司

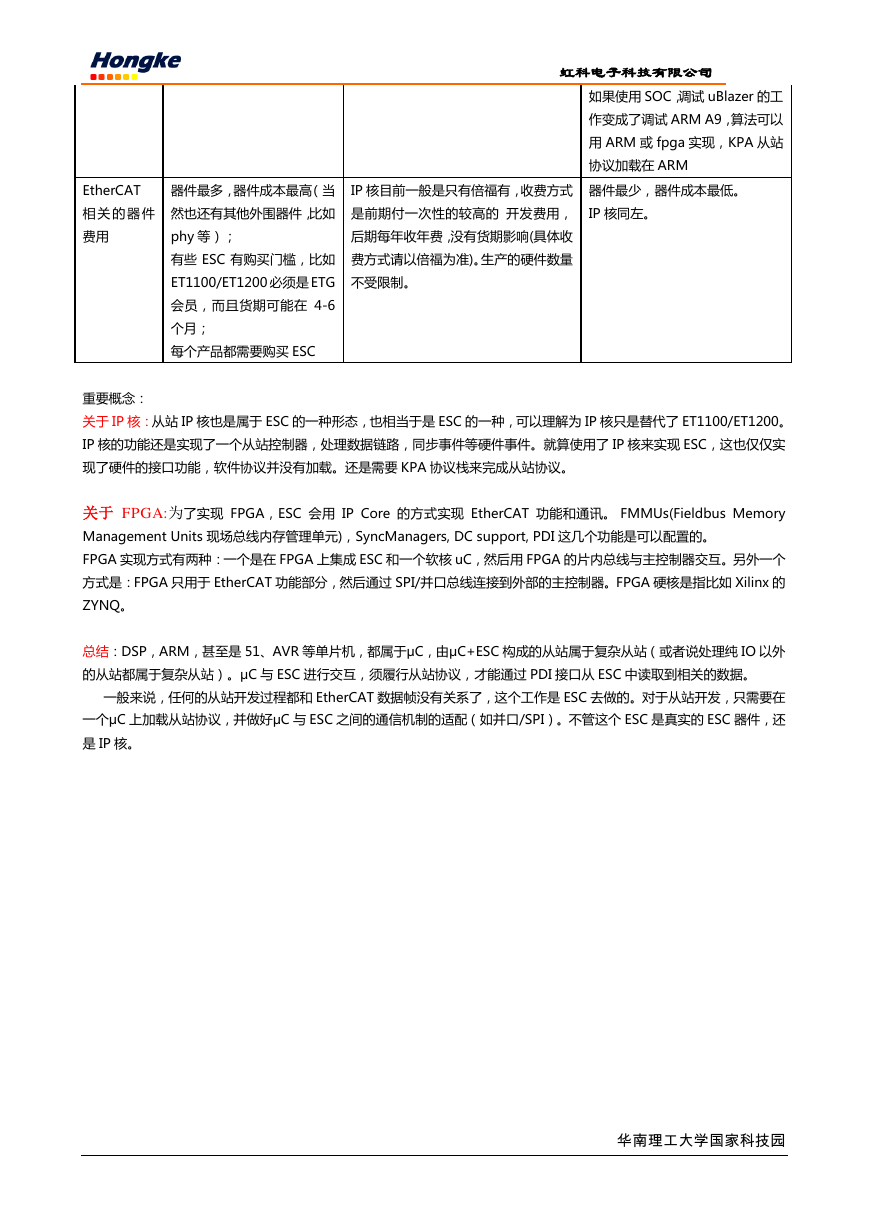

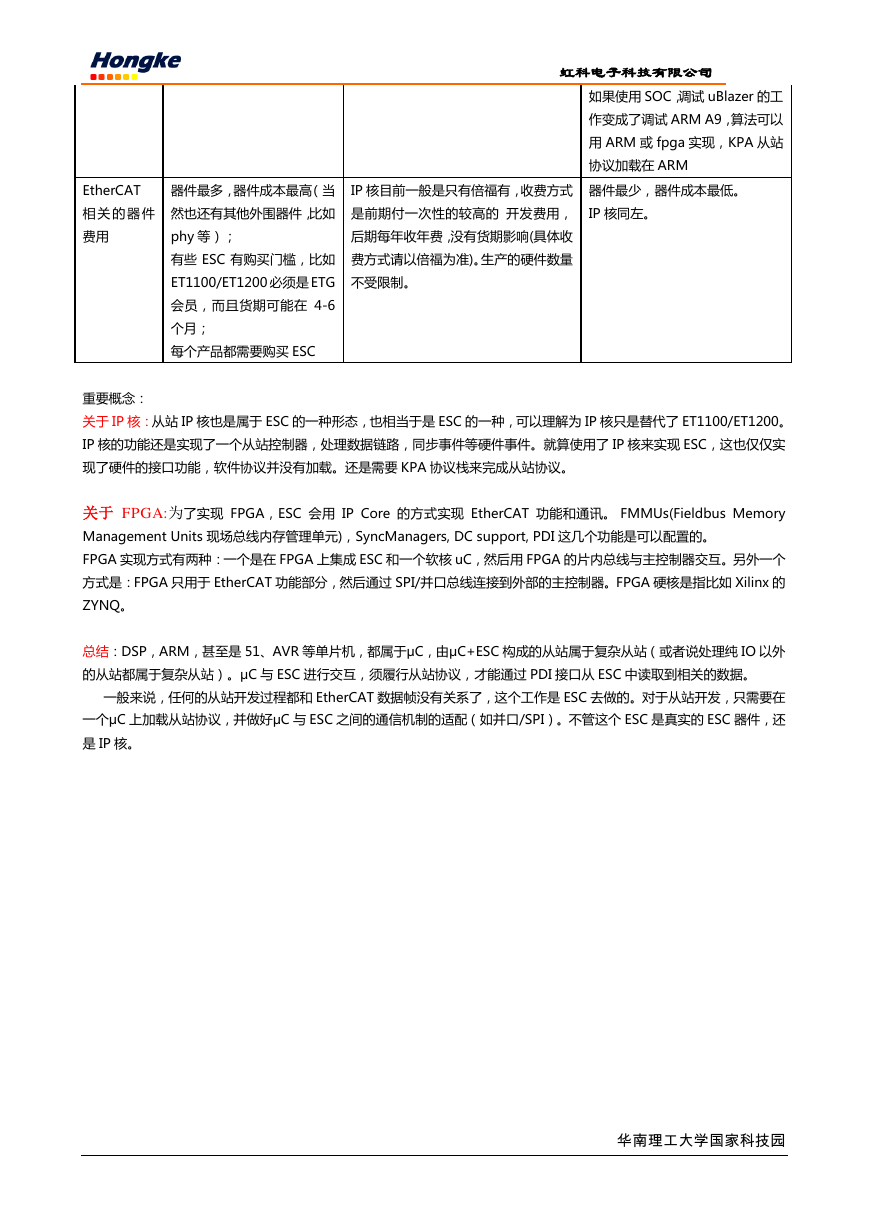

第二节 如何选择硬件

拿 EtherCAT 伺服驱动器作为从站硬件举例,EtherCAT 伺服驱动器的开发方案有多重选项:

(1)纯总线驱动器,不带脉冲、模拟量、液晶等外设。所有指令和操作全部通过 EtherCAT。可以使用的

方案为:ESC+DSP,FPGA(IP 核)+DSP 或单 FPGA(软核/硬核+IP)。KPA 从站协议加载在 DSP、软

核或者硬核上,难度在于 FPGA 的 IP 核与软核技术、FPGA 内部高速总线的应用和调试。

(2)总线+传统驱动器。总线+传统驱动器。同时支持 EtherCAT 和传统的脉冲、模拟量等。可以使用的方

案为:ESC+DSP+FPGA(CPLD),FPGA(IP 核)+DSP。

不管哪种 EtherCAT 伺服驱动器,几个比较重要的方案对比如下 (只是列出常见情况):

KPA 从站协议的作用:使得微控制器(DSP、软核 uBlazer、ARM 硬核)能够处理 ESC 中的数据,完成交互,以及根据

EtherCAT 的运行机制来处理相关事件和过程数据的读写。

器件方案

ESC+DSP+FPGA(或 CPLD) FPGA(IP 核)+DSP

只有 FPGA(IP 核)

与 非 总 线 伺

相当于再传统的伺服驱动器

FPGA 比传统的驱动器多加载了一个 IP

高效低成本的模式:FPGA 加载 IP

服 驱 动 器 的

上加了一个 ESC 而已。

核,用于完成 EtherCAT 通讯。

核,完成 EtherCAT、数据交互和

对比

处理、运动控制算法处理等。

也有两种选择:一类是纯 FPGA,

一 类 是 SoC 器 件 ( FPGA+A9

ARM)。

KPA 协议栈

KPA 代码直接移植到 DSP:

1、KPA 代码移植到 DSP:DSP 去拿

KPA 代码加载在内建的软核(比如

移植的关系

DSP 直 接 从 ESC 拿 一 些

FPGA 软核的 EtherCAT 数据;

EtherCAT 数据,ESC 自动完

2、KPA 代码移植到 FPGA 软核(KPA

成数据采集,不需要对 ESC

有 uBlazer 的样机代码):比如:FPGA

做额外的开发。DSP 与 ESC

上加载 IP 核,内建一个 uBlazer 的 32

之间通过 SPI/并口等方式连

位处理器称为软核,软核上跑 KPA 从

接。

站协议栈。DSP 通过 SPI/并口访问

uBlazer 处理出来的 PDO 和 SDO 数

据。

xilinx 的 uBlazer)或者硬核(比

如 xilinx 的 zynq)(KPA 有 uBlazer

的 demo+国内团队正在开发的基

于 zynq 的 demo):

即 FPGA 上集成 ESC 和一个软核

uC,然后用 FPGA 的片内总线与

主控制器交互。

FPGA 的 工

FPGA 还是做传统的工作:管

FPGA 加载 IP 核,除了传统工作量,还

FPGA 完成了:EtherCAT 数据处

作量

理外设,IO 数据处理等。

包括了通过加载的 IP 核实现 EtherCAT

理、运动控制算法、外设管理、IO

(CPLD 任然适用)

数据的采集和发送,相当于 FPGA 完成

运算等等全部工作。

了 ESC 的功能+管理了需要的外设+IO

数据处理等(CPLD 将不再适用,需要

25k 以上逻辑容量的 FPGA)

性价比评估 成本相对最高,开发难度小。

成本较低,开发难度适中。

性价比最高,难度最大,性能最佳:

现阶段的主流方案。

最近比较流行,估计未来比较受欢迎。

如果是纯 FPGA,难度在于,(1)

只是需要考虑 DSP 与 ESC 之

多了 IP 核的开发难度。

调试从站 IP,(2)调试 uBlazer

间的数据交互就可以。

软核(kPA 从站协议加载于此),

(3)用 uBlazer 或 FPGA 实现

FOC 等算法。

华南理工大学国家科技园

�

www.hkaco.com 虹科电子科技有限公司

如果使用 SOC,调试 uBlazer 的工

作变成了调试 ARM A9,算法可以

用 ARM 或 fpga 实现,KPA 从站

协议加载在 ARM

EtherCAT

器件最多,器件成本最高(当

IP 核目前一般是只有倍福有,收费方式

器件最少,器件成本最低。

相 关 的 器 件

然也还有其他外围器件,比如

是前期付一次性的较高的 开发费用,

IP 核同左。

费用

phy 等);

后期每年收年费,没有货期影响(具体收

有些 ESC 有购买门槛,比如

费方式请以倍福为准)。生产的硬件数量

ET1100/ET1200 必须是 ETG

不受限制。

会员,而且货期可能在 4-6

个月;

每个产品都需要购买 ESC

重要概念:

关于 IP 核:从站 IP 核也是属于 ESC 的一种形态,也相当于是 ESC 的一种,可以理解为 IP 核只是替代了 ET1100/ET1200。

IP 核的功能还是实现了一个从站控制器,处理数据链路,同步事件等硬件事件。就算使用了 IP 核来实现 ESC,这也仅仅实

现了硬件的接口功能,软件协议并没有加载。还是需要 KPA 协议栈来完成从站协议。

关于 FPGA:为了实现 FPGA,ESC 会用 IP Core 的方式实现 EtherCAT 功能和通讯。 FMMUs(Fieldbus Memory

Management Units 现场总线内存管理单元),SyncManagers, DC support, PDI 这几个功能是可以配置的。

FPGA 实现方式有两种:一个是在 FPGA 上集成 ESC 和一个软核 uC,然后用 FPGA 的片内总线与主控制器交互。另外一个

方式是:FPGA 只用于 EtherCAT 功能部分,然后通过 SPI/并口总线连接到外部的主控制器。FPGA 硬核是指比如 Xilinx 的

ZYNQ。

总结:DSP,ARM,甚至是 51、AVR 等单片机,都属于μC,由μC+ESC 构成的从站属于复杂从站(或者说处理纯 IO 以外

的从站都属于复杂从站)。μC 与 ESC 进行交互,须履行从站协议,才能通过 PDI 接口从 ESC 中读取到相关的数据。

一般来说,任何的从站开发过程都和 EtherCAT 数据帧没有关系了,这个工作是 ESC 去做的。对于从站开发,只需要在

一个μC 上加载从站协议,并做好μC 与 ESC 之间的通信机制的适配(如并口/SPI)。不管这个 ESC 是真实的 ESC 器件,还

是 IP 核。

华南理工大学国家科技园

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc