DDS 模块设计

DDS 模块的设计是本系统的重点,也是本章阐述的重点。DDS 模块主要是围绕芯片

AD9854 进行设计的,设计要求既要满足性能指标,还要求优化电路,减小电路面积,否则

13 路 DDS 共同存在会使系统体积显得较大。下面先介绍 AD9854 的基本特性。

4.2.1 AD9854 介绍

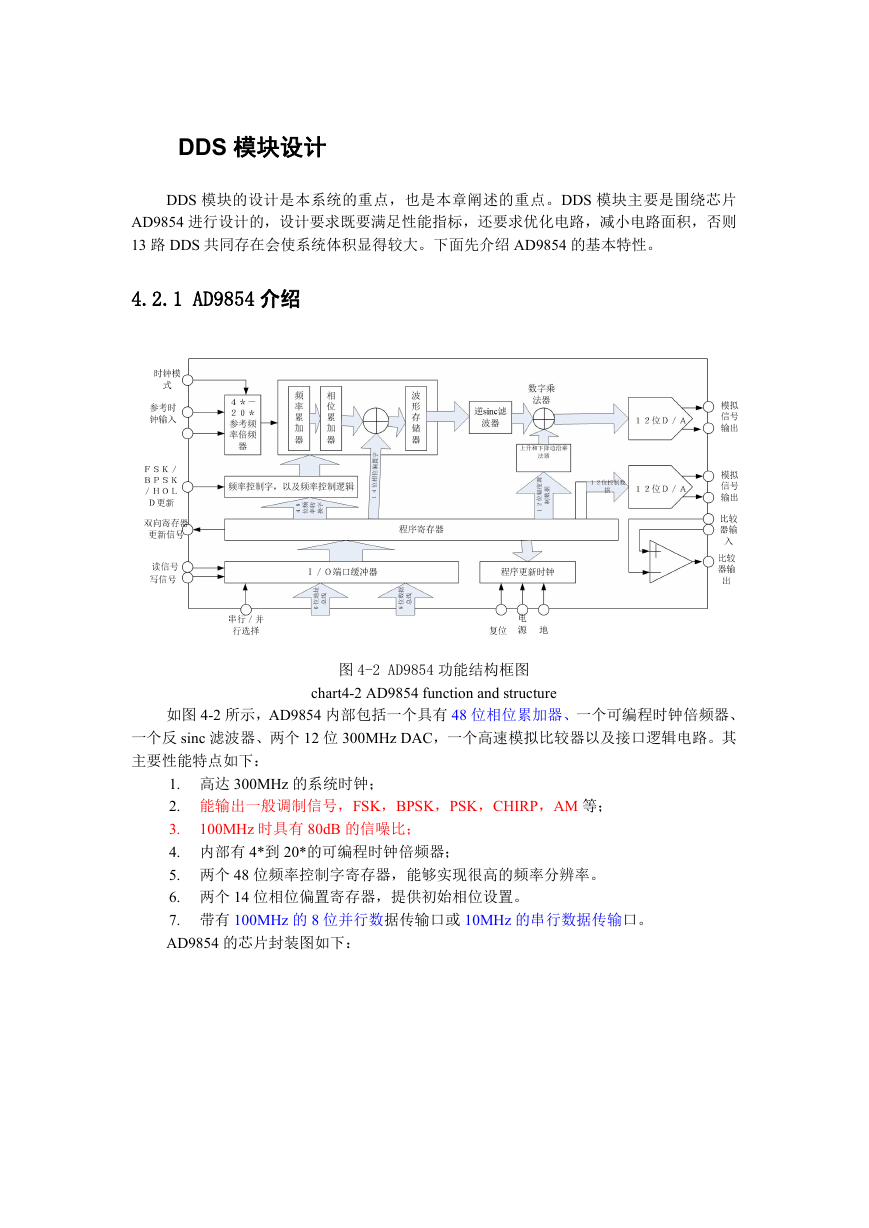

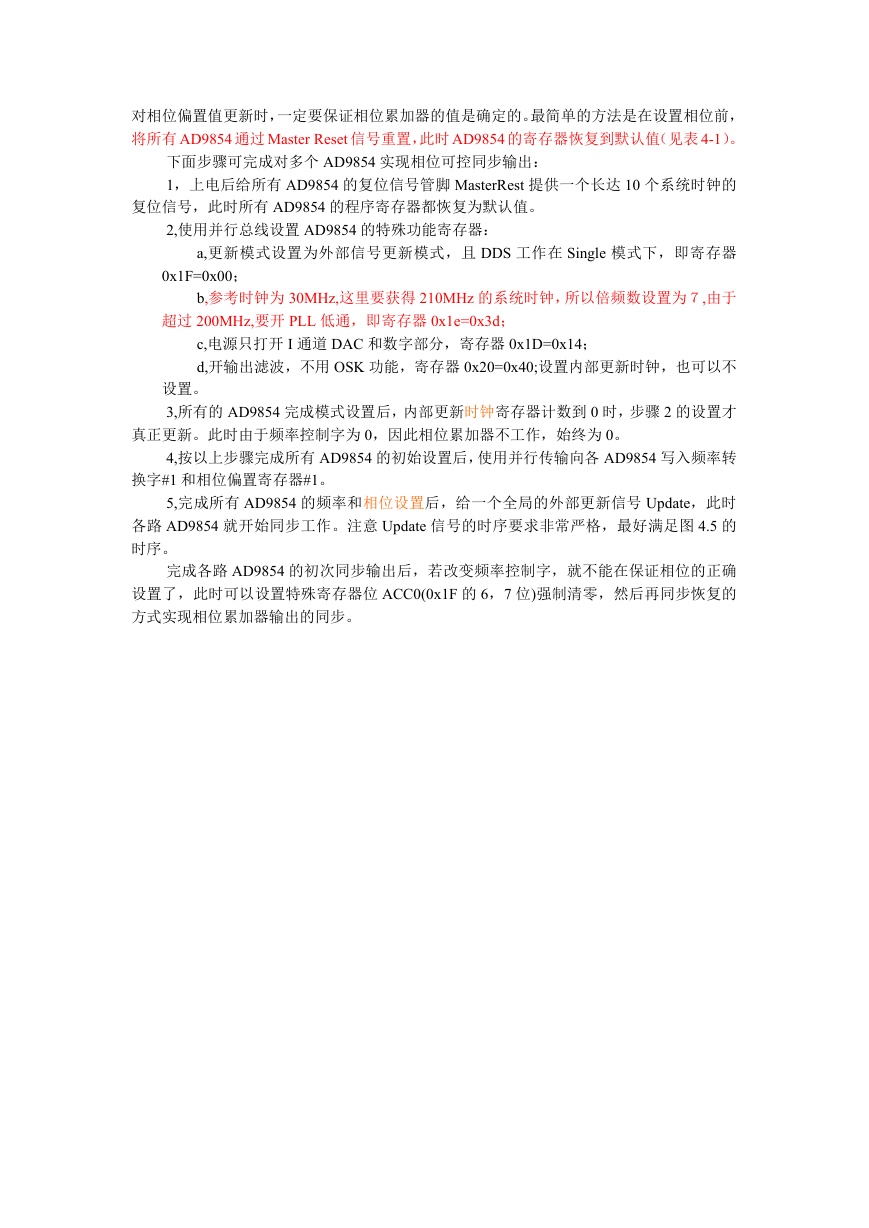

图 4-2 AD9854 功能结构框图

chart4-2 AD9854 function and structure

如图 4-2 所示,AD9854 内部包括一个具有 48 位相位累加器、一个可编程时钟倍频器、

一个反 sinc 滤波器、两个 12 位 300MHz DAC,一个高速模拟比较器以及接口逻辑电路。其

主要性能特点如下:

100MHz 时具有 80dB 的信噪比;

1. 高达 300MHz 的系统时钟;

2. 能输出一般调制信号,FSK,BPSK,PSK,CHIRP,AM 等;

3.

4. 内部有 4*到 20*的可编程时钟倍频器;

5. 两个 48 位频率控制字寄存器,能够实现很高的频率分辨率。

6. 两个 14 位相位偏置寄存器,提供初始相位设置。

7. 带有 100MHz 的 8 位并行数据传输口或 10MHz 的串行数据传输口。

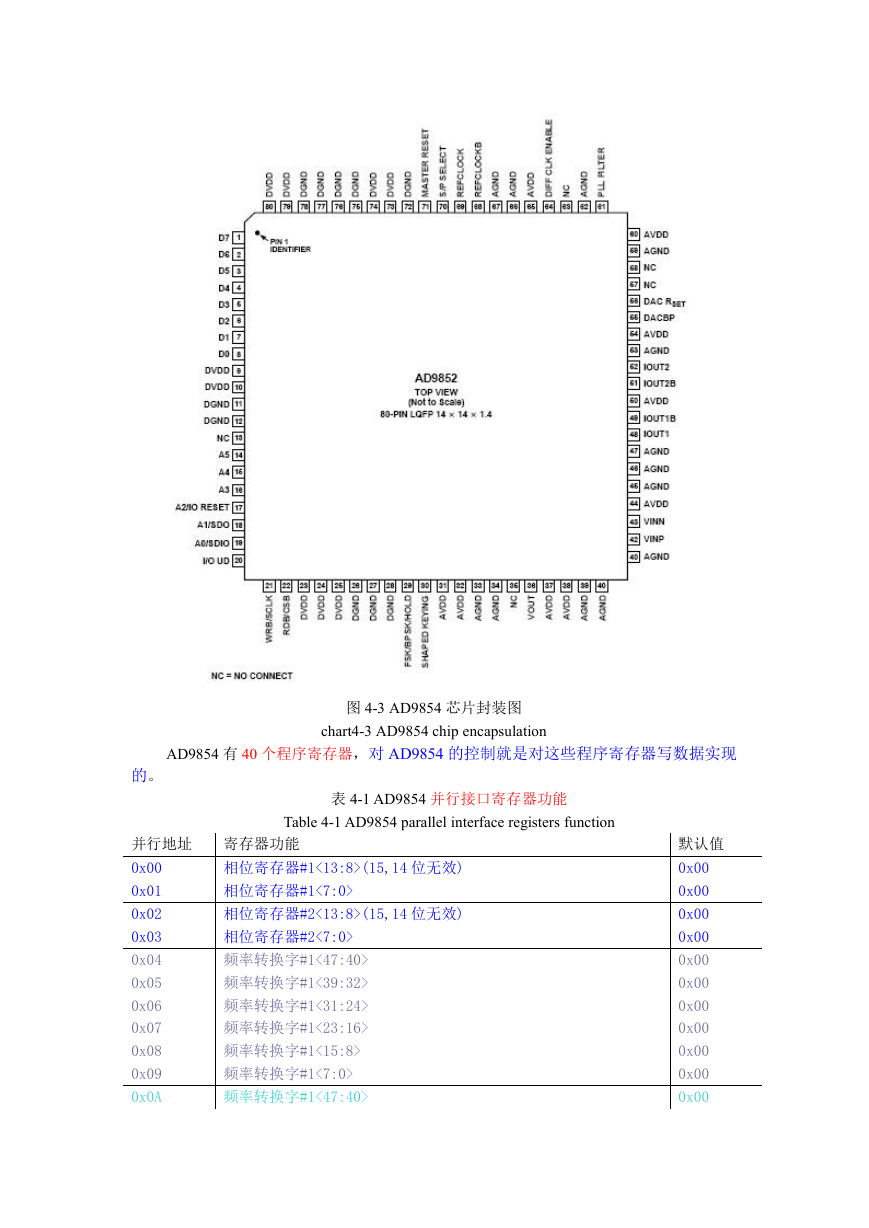

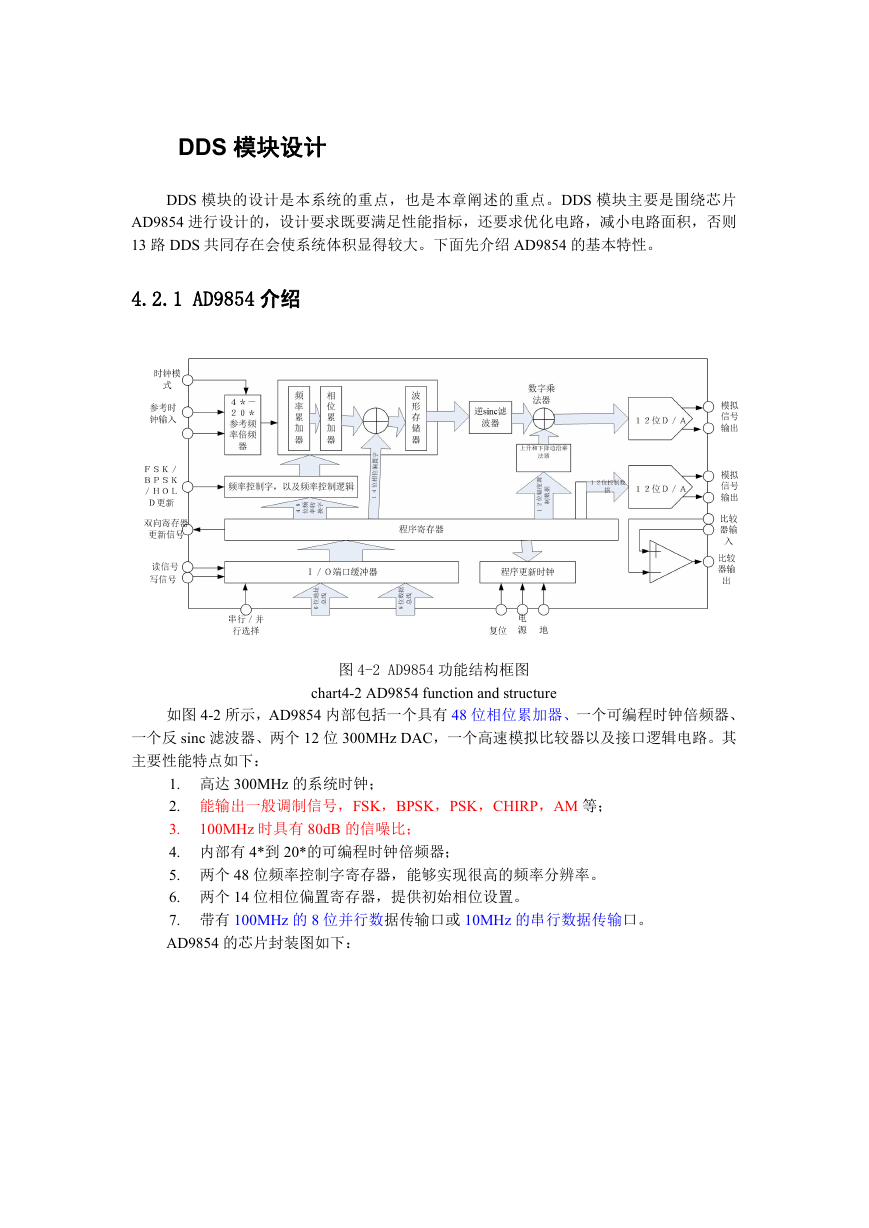

AD9854 的芯片封装图如下:

�

图 4-3 AD9854 芯片封装图

chart4-3 AD9854 chip encapsulation

AD9854 有 40 个程序寄存器,对 AD9854 的控制就是对这些程序寄存器写数据实现

的。

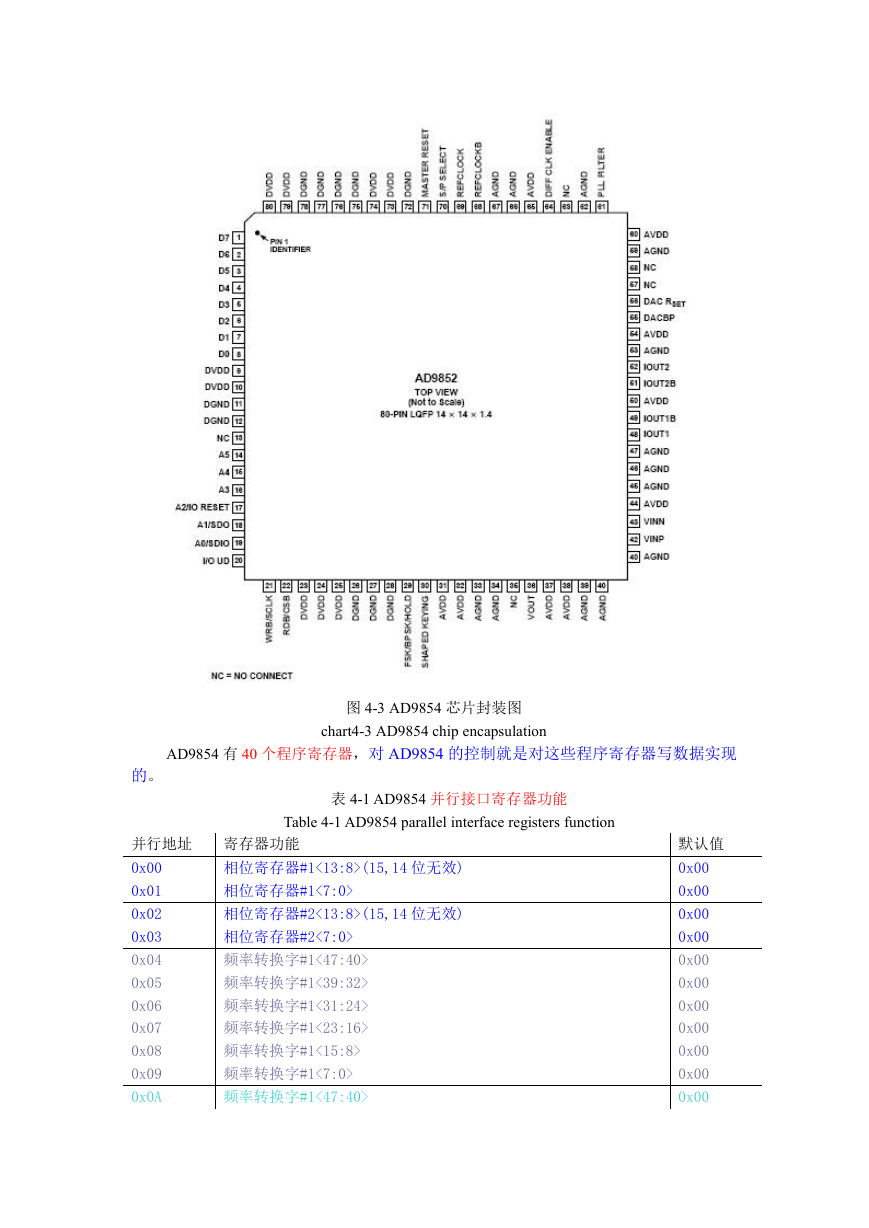

表 4-1 AD9854 并行接口寄存器功能

Table 4-1 AD9854 parallel interface registers function

并行地址

寄存器功能

0x00

0x01

0x02

0x03

0x04

0x05

0x06

0x07

0x08

0x09

0x0A

相位寄存器#1<13:8>(15,14 位无效)

相位寄存器#1<7:0>

相位寄存器#2<13:8>(15,14 位无效)

相位寄存器#2<7:0>

频率转换字#1<47:40>

频率转换字#1<39:32>

频率转换字#1<31:24>

频率转换字#1<23:16>

频率转换字#1<15:8>

频率转换字#1<7:0>

频率转换字#1<47:40>

默认值

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

�

0x0B

0x0C

0x0D

0x0E

0x0F

0x10

0x11

0x12

0x13

0x14

0x15

0x16

0x17

0x18

0x19

0x1A

0x1B

0x1C

0x1D

0x1E

0x1F

0x20

0x21

0x22

0x23

0x24

0x25

0x26

0x27

频率转换字#1<39:32>

频率转换字#1<31:24>

频率转换字#1<23:16>

频率转换字#1<15:8>

频率转换字#1<7:0>

三角频率字<47:40>

三角频率字<39:32>

三角频率字<31:24>

三角频率字<23:16>

三角频率字<15:8>

三角频率字<7:0>

更新时钟计数器<31:24>

更新时钟计数器<23:16>

更新时钟计数器<15:8>

更新时钟计数器<7:0>

边沿速率计数器<19:16>(23,22,21,20 不起作用)

边沿速率计数器<15:8>

边沿速率计数器<7:0>

节电控制

时钟倍频控制器

DDS 模式控制与累加器清零控制

传输模式,和 OSK 控制

输出幅度乘法器 I<11:8>(15,14,13,12 不起作用)

输出幅度乘法器 I<7:0>

输出幅度乘法器 Q<11:8>(15,14,13,12 不起作用)

输出幅度乘法器 Q<7:0>

输出边沿变化率控制器<7:0>

QDAC,Q 通道 D/A 输入<11:8>

QDAC,Q 通道 D/A 输入<7:0>

表 4-2 AD9854 控制寄存器功能

地址 7

0x1D

0x1E

0x1F

N

N

ACC1

清零

0x20

N

6

N

PLL 范

围

ACC2

清零

开输出

滤波

Table 5-2 AD9854 control registers function

1

5

4

3

2

N

比较器 0

PLL 低

通

Triang

le

OSK 使

能

倍频

4位

N

OSK 模

式

倍频

3位

模式

位 2

N

控制

DAC

倍频

2位

模式

位 2

N

I 通道

DAC

倍频

1位

模式位

2

串行地

位字节

优先

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x40

0x00

0x00

0x00

0x00

0x64

0x20

0x20

0x00

0x00

0x00

0x00

0x80

0x00

0x00

默认值

0x00

0x64

0x01

0x20

0

数字

部分

倍频

0位

内部

更新

SDO 有

效

通过并行总线将数据写入程序寄存器时,实际上只是暂存在 I/O 缓冲区中,只有提供

更新信号,这些数据才会更新到程序寄存器。AD9854 提供两种更新方式,内部更新和外部

更新。内部更新通过更新时钟计数器完成,当计数器计自减为零后会产生一个内部更新信号;

�

外部更新需要在外部更新管脚上给与一个高电平脉冲。默认的更新模式为内部更新,可以通

过设置控制寄存器 0x1F 的 0 位进行修改。

4.4.2 多 AD9854 应用原理与方法

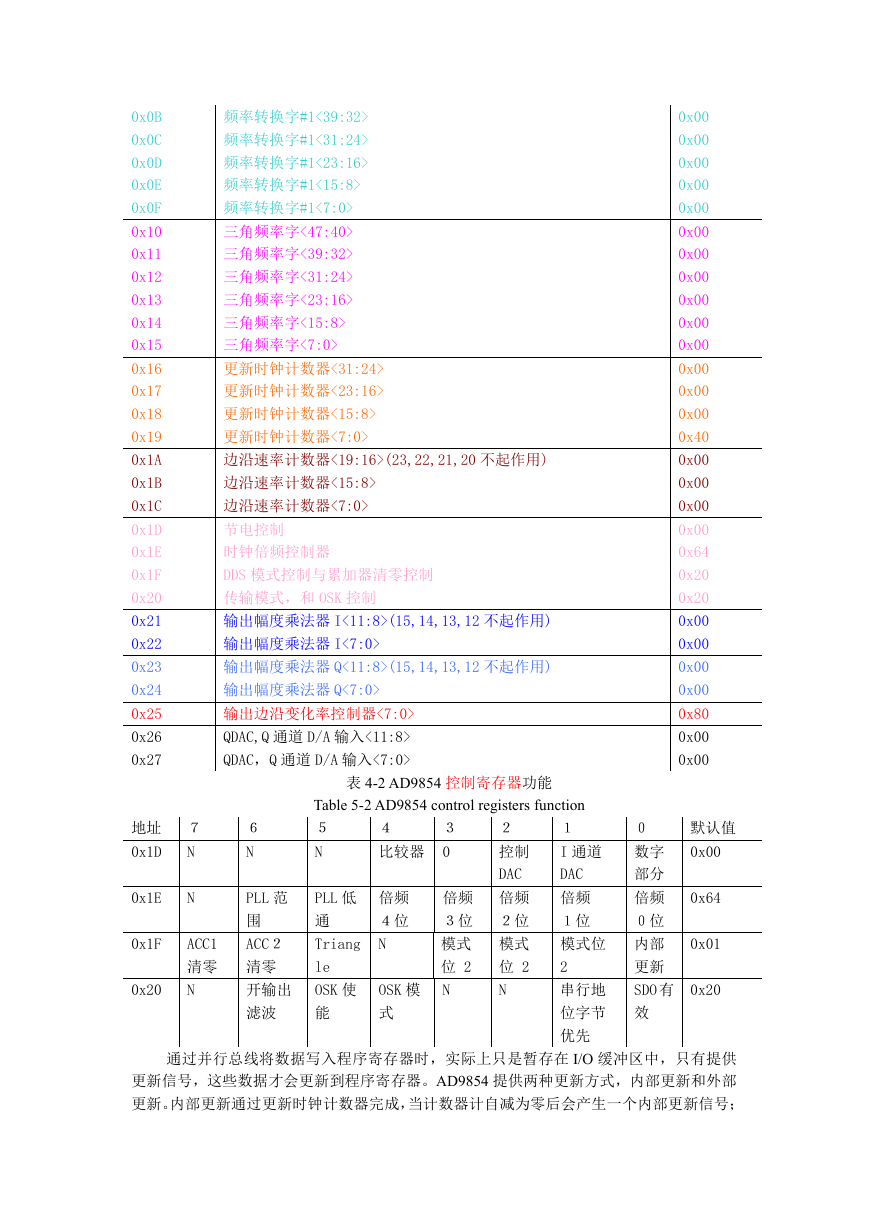

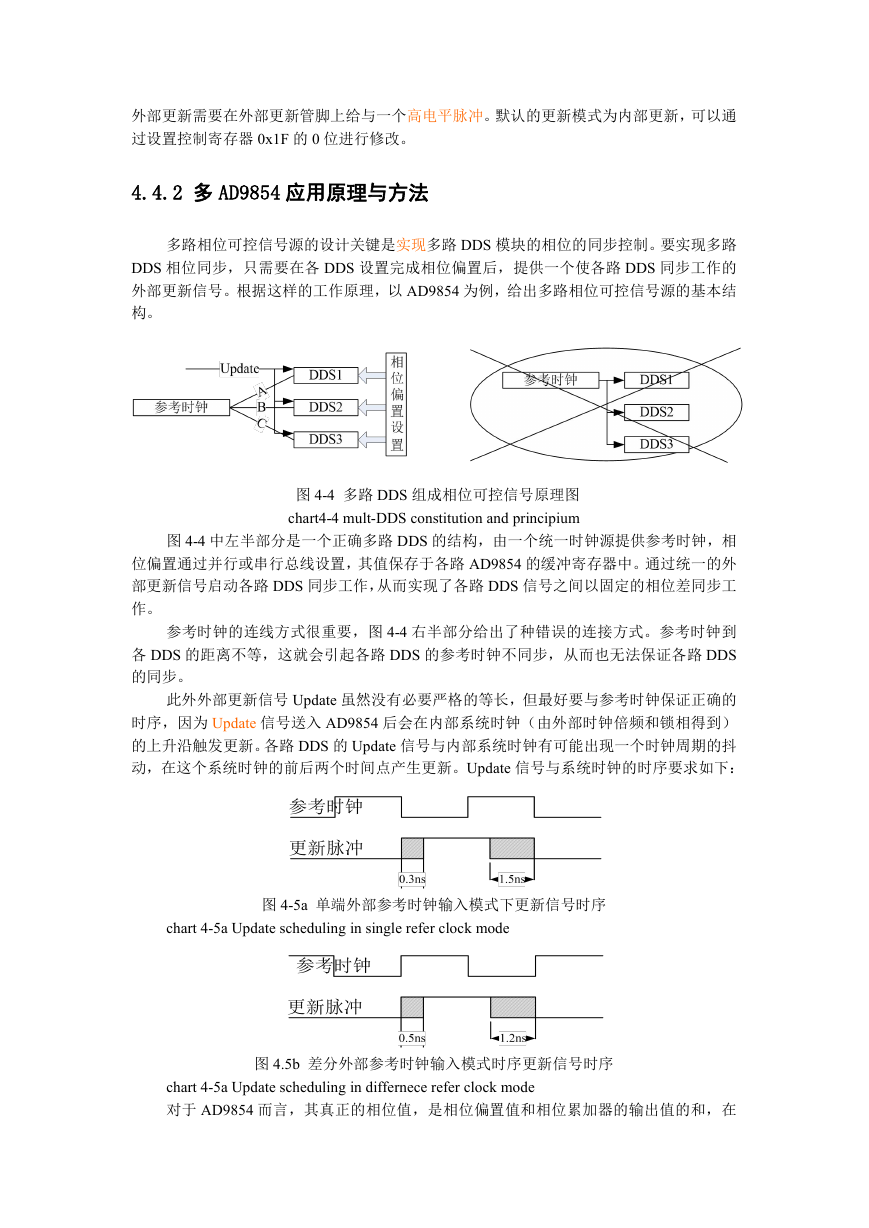

多路相位可控信号源的设计关键是实现多路 DDS 模块的相位的同步控制。要实现多路

DDS 相位同步,只需要在各 DDS 设置完成相位偏置后,提供一个使各路 DDS 同步工作的

外部更新信号。根据这样的工作原理,以 AD9854 为例,给出多路相位可控信号源的基本结

构。

图 4-4 多路 DDS 组成相位可控信号原理图

chart4-4 mult-DDS constitution and principium

图 4-4 中左半部分是一个正确多路 DDS 的结构,由一个统一时钟源提供参考时钟,相

位偏置通过并行或串行总线设置,其值保存于各路 AD9854 的缓冲寄存器中。通过统一的外

部更新信号启动各路 DDS 同步工作,从而实现了各路 DDS 信号之间以固定的相位差同步工

作。

参考时钟的连线方式很重要,图 4-4 右半部分给出了种错误的连接方式。参考时钟到

各 DDS 的距离不等,这就会引起各路 DDS 的参考时钟不同步,从而也无法保证各路 DDS

的同步。

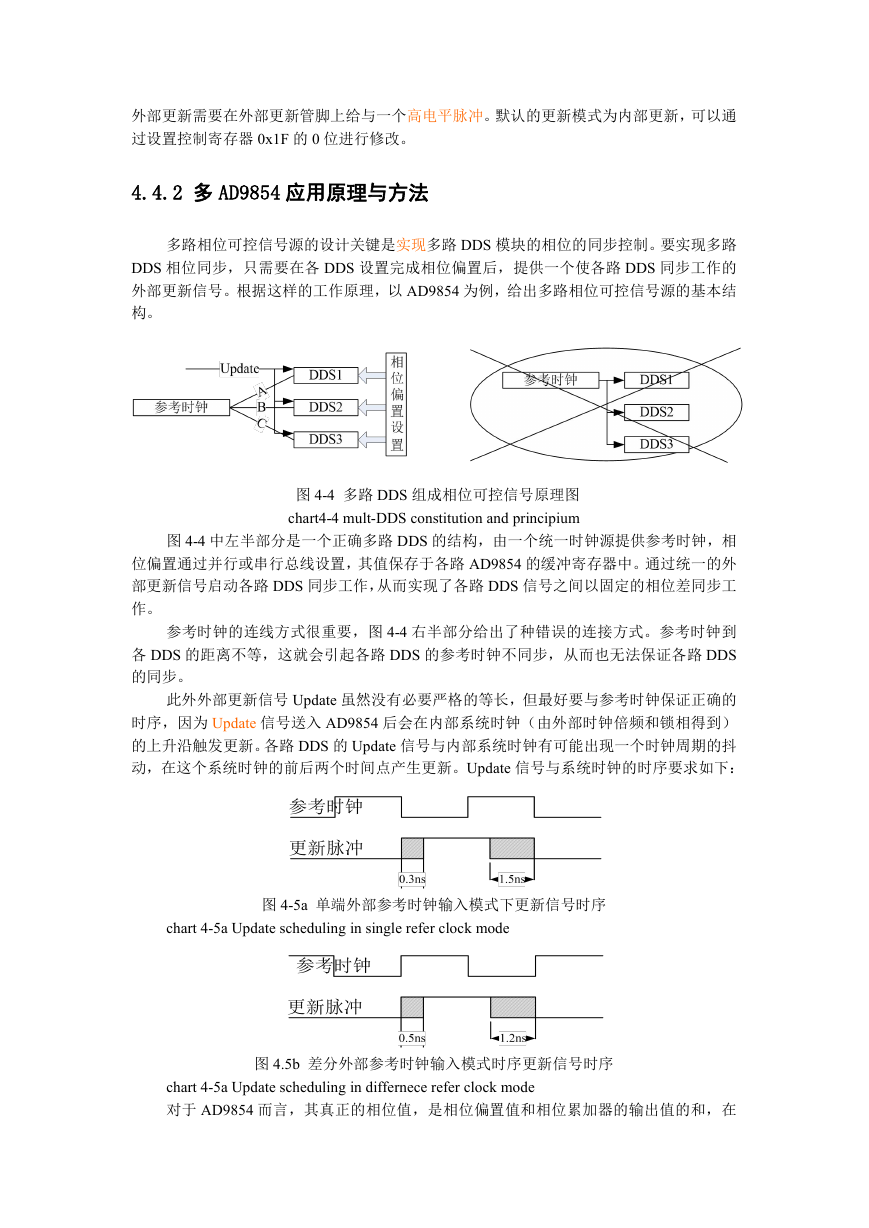

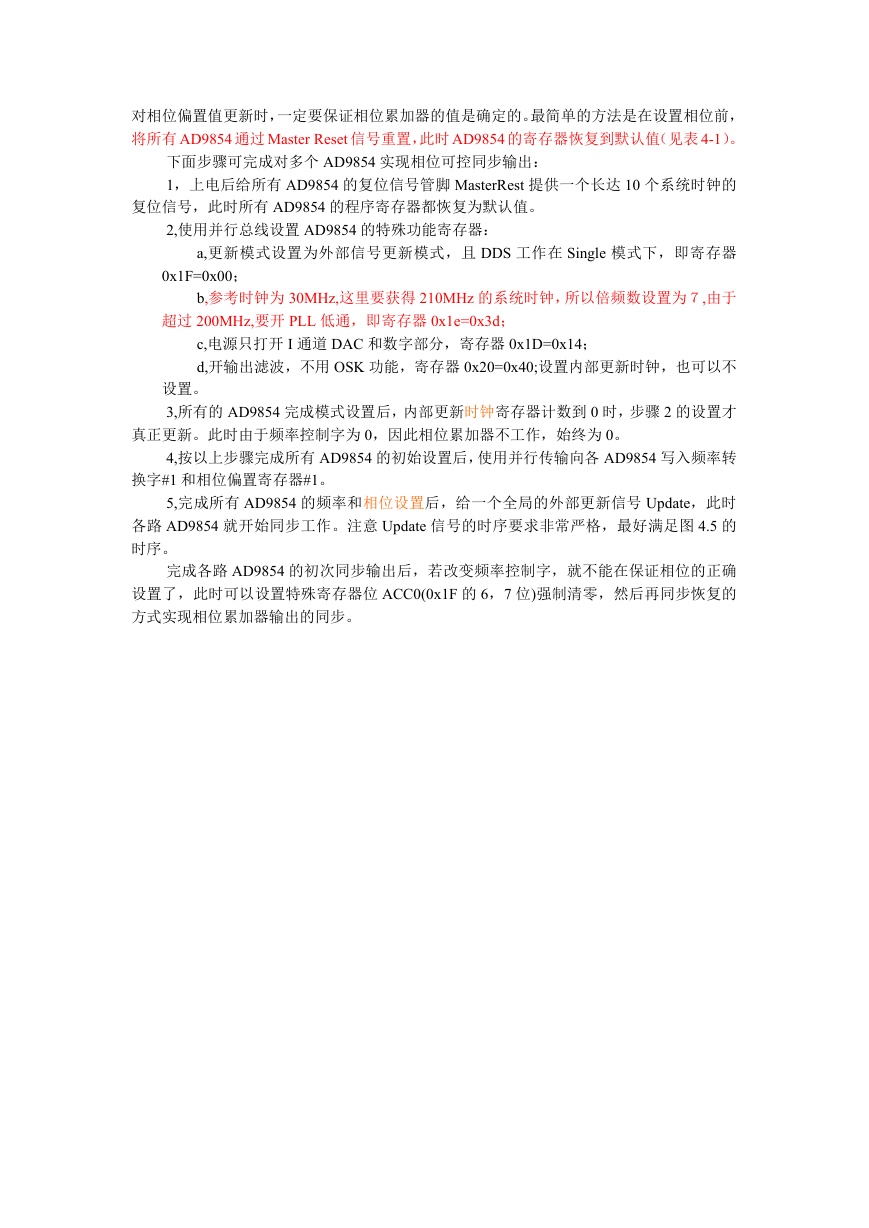

此外外部更新信号 Update 虽然没有必要严格的等长,但最好要与参考时钟保证正确的

时序,因为 Update 信号送入 AD9854 后会在内部系统时钟(由外部时钟倍频和锁相得到)

的上升沿触发更新。各路 DDS 的 Update 信号与内部系统时钟有可能出现一个时钟周期的抖

动,在这个系统时钟的前后两个时间点产生更新。Update 信号与系统时钟的时序要求如下:

图 4-5a 单端外部参考时钟输入模式下更新信号时序

chart 4-5a Update scheduling in single refer clock mode

图 4.5b 差分外部参考时钟输入模式时序更新信号时序

chart 4-5a Update scheduling in differnece refer clock mode

对于 AD9854 而言,其真正的相位值,是相位偏置值和相位累加器的输出值的和,在

�

对相位偏置值更新时,一定要保证相位累加器的值是确定的。最简单的方法是在设置相位前,

将所有 AD9854 通过 Master Reset 信号重置,此时 AD9854 的寄存器恢复到默认值(见表 4-1)。

下面步骤可完成对多个 AD9854 实现相位可控同步输出:

1,上电后给所有 AD9854 的复位信号管脚 MasterRest 提供一个长达 10 个系统时钟的

复位信号,此时所有 AD9854 的程序寄存器都恢复为默认值。

2,使用并行总线设置 AD9854 的特殊功能寄存器:

a,更新模式设置为外部信号更新模式,且 DDS 工作在 Single 模式下,即寄存器

0x1F=0x00;

b,参考时钟为 30MHz,这里要获得 210MHz 的系统时钟,所以倍频数设置为7,由于

超过 200MHz,要开 PLL 低通,即寄存器 0x1e=0x3d;

c,电源只打开 I 通道 DAC 和数字部分,寄存器 0x1D=0x14;

d,开输出滤波,不用 OSK 功能,寄存器 0x20=0x40;设置内部更新时钟,也可以不

设置。

3,所有的 AD9854 完成模式设置后,内部更新时钟寄存器计数到 0 时,步骤 2 的设置才

真正更新。此时由于频率控制字为 0,因此相位累加器不工作,始终为 0。

4,按以上步骤完成所有 AD9854 的初始设置后,使用并行传输向各 AD9854 写入频率转

换字#1 和相位偏置寄存器#1。

5,完成所有 AD9854 的频率和相位设置后,给一个全局的外部更新信号 Update,此时

各路 AD9854 就开始同步工作。注意 Update 信号的时序要求非常严格,最好满足图 4.5 的

时序。

完成各路 AD9854 的初次同步输出后,若改变频率控制字,就不能在保证相位的正确

设置了,此时可以设置特殊寄存器位 ACC0(0x1F 的 6,7 位)强制清零,然后再同步恢复的

方式实现相位累加器输出的同步。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc